Parlons de la conception des vias - pour l'électronique sérieuse, leur qualité est très importante. Au début de l'article, j'ai mis en évidence les facteurs affectant l'intégrité du signal, puis j'ai montré des exemples de calcul et de réglage de l'impédance des vias simples et différentiels.

Bonjour à tous, mon nom est Vyacheslav. Je développe des cartes de circuits imprimés depuis 5 ans, et pendant ce temps, j'ai non seulement lu beaucoup de règles et de recommandations pour le traçage, mais j'ai également trouvé la source et travaillé avec elles.

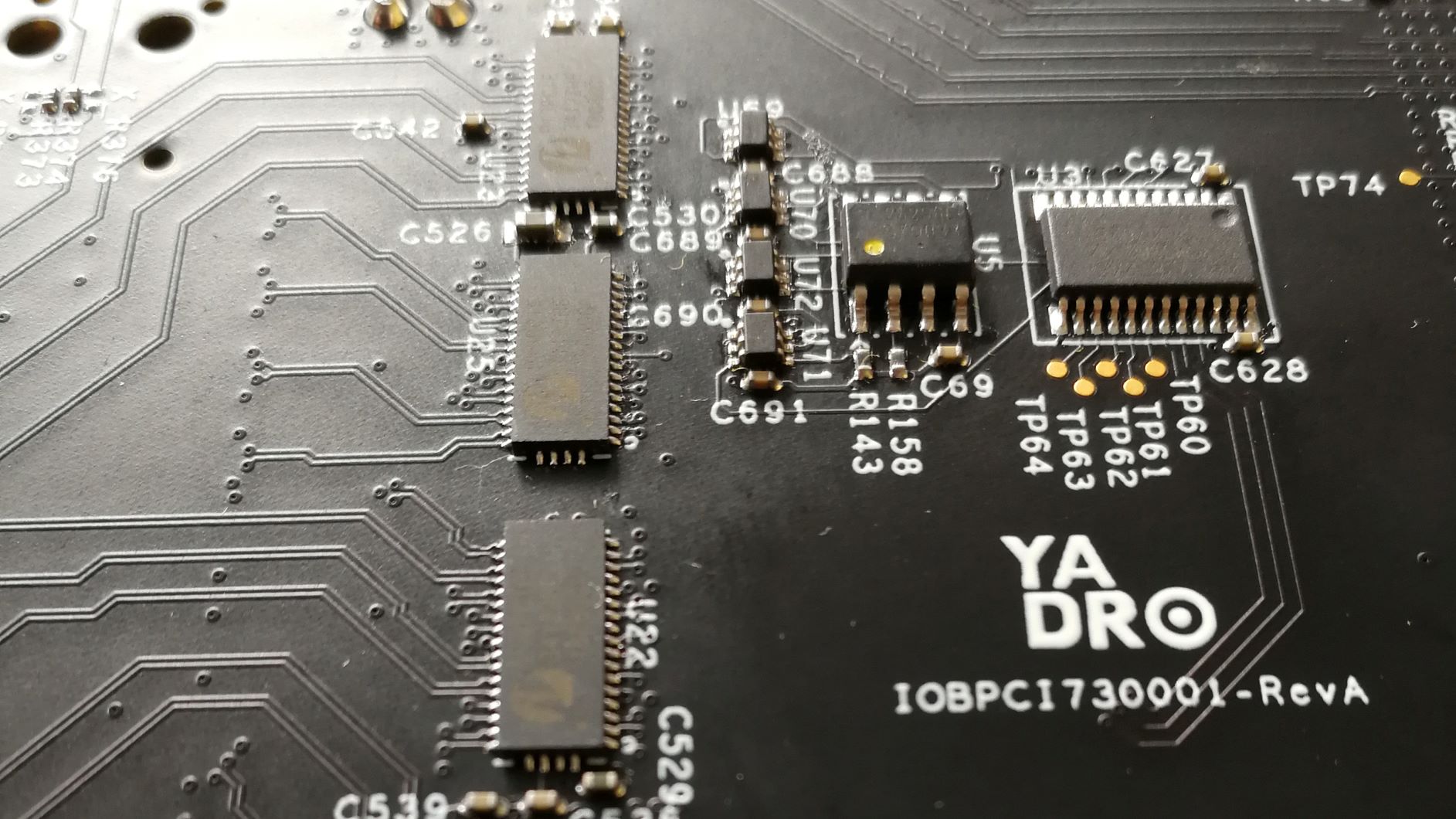

Dans les systèmes informatiques complexes que YADRO développe, les signaux à grande vitesse sur le chemin de l'émetteur au récepteur couvrent des distances importantes, passant par plusieurs cartes et effectuant des dizaines de transitions intercouches. Dans de telles conditions, chaque vias négligemment conçu apportera une petite contribution à la dégradation du signal et, par conséquent, l'interface peut ne pas fonctionner.

Intégrité du signal

Les vias (ci-après p / o, via anglais) sont des hétérogénéités dans la ligne de transmission. Comme d'autres hétérogénéités, elles gâchent le signal. Cet effet est faiblement prononcé aux basses fréquences, mais augmente considérablement avec l'augmentation de la fréquence. Souvent, les développeurs prêtent peu d'attention à la structure des vias: ils peuvent être copiés à partir d'un projet "voisin", issus d'une fiche technique, ou non spécifiés du tout en CAO (le réglage par défaut).

Avant d'utiliser la structure calculée, il faut comprendre pourquoi elle a été faite comme ça? La répétition aveugle ne peut que nuire.

L'intégrité du signal dans le canal lors du passage à travers des vias est principalement affectée par les facteurs suivants:

- réflexion du signal due aux changements d'impédance des ondes;

- dégradation du signal due à la capacité et à l'inductance parasites;

- les réflexions d'une partie inutilisée de semi-plastique lors du passage à la couche intérieure (ci-après dénommée talon de l'anglais via talon);

- diaphonie (pourparlers croisés anglais);

- interférence dans les bus électriques.

Examinons plus en détail les causes de ces effets et les méthodes pour les éliminer.

Facteur 1. Impédance d'onde p / o

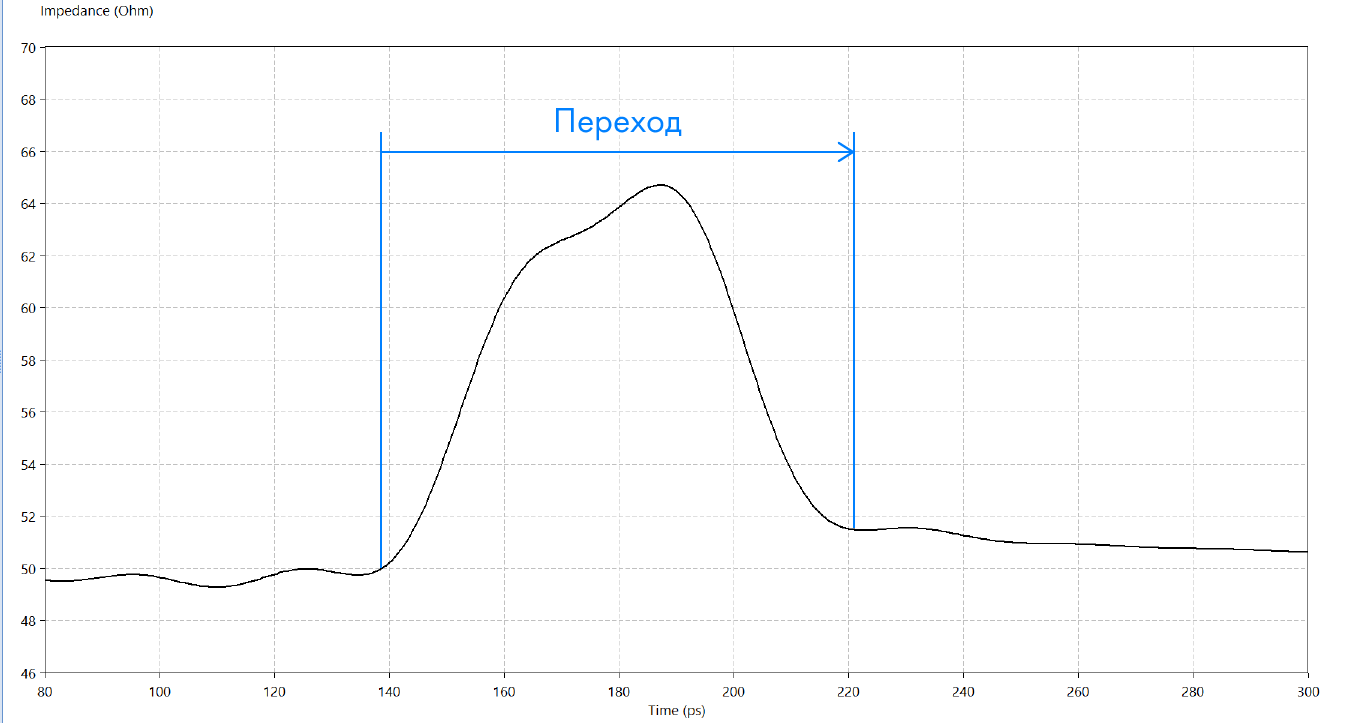

Dans une carte idéalement conçue, l'impédance ne change pas tout au long du trajet, y compris lors du passage à une autre couche. En réalité, cela ressemble généralement à ceci:

Figure 1. Changement d'impédance des ondes lors de la transition vers une autre couche.

Figure 1. Changement d'impédance des ondes lors de la transition vers une autre couche.Plus les résistances aux ondes sont adaptées, moins le signal sera réfléchi. Comment influencer cela?

Considérez la structure de p / o sur la carte [1].

Figure 2. Structure p / o sur la carte.

Figure 2. Structure p / o sur la carte.En modifiant les éléments p / o, nous modifions la résistance aux ondes de la transition. Notre objectif est de faire correspondre l'impédance de la structure de transition avec l'impédance des conducteurs pour minimiser les réflexions. Examinons comment l'impédance change lorsque les éléments de la structure p / o changent.

Facteur 2. Inductance et capacité parasites

Les conducteurs sur une carte de circuit imprimé peuvent être fabriqués avec une résistance aux ondes située dans une large plage, mais le plus souvent, elle est de 50 Ohms. D'une part, cela est dû à la continuité historique: l'impédance de 50 ohms a été normalisée pour les câbles coaxiaux en tant que compromis entre le niveau de charge du conducteur et la perte d'énergie du signal. D'un autre côté, un conducteur de 50 ohms est facile à fabriquer sur une carte standard.

Pour le développeur, il est important non pas tant la valeur spécifique de la résistance aux vagues que sa constance sur toute la ligne de transmission.

Afin de créer une ligne de transmission avec une valeur fixe d'impédance d'onde, le développeur sélectionne la largeur de la piste et la distance à la couche de référence, c'est-à-dire modifie la capacité linéaire et l'inductance de la ligne de transmission à une

certaine valeur.

En p / o, la composante inductive est assez importante. En première approximation, il faut, dans un cadre raisonnable, minimiser autant que possible l'inductance parasite, puis changer les paramètres p / o pour atteindre une capacité

donnée , et donc une impédance.

Une diminution excessive de la capacité d'une demi-onde entraînera une augmentation locale de l'impédance et, par conséquent, des réflexions du signal.

Facteur 3. Via le talon

Que se passe-t-il lorsqu'un signal passe à travers un trou traversant?

Figure 3. Trou de transition avec talon, résonance à ¼ de longueur d'onde.

Figure 3. Trou de transition avec talon, résonance à ¼ de longueur d'onde.Dans notre exemple, le signal se propage de haut en bas à partir de la couche supérieure. Après avoir atteint la couche de signal interne, le signal est séparé: la partie se déplace le long du chemin sur la couche interne, et la partie continue de descendre le long des vias, puis elle est réfléchie par la couche inférieure. Une fois que le signal réfléchi a atteint la couche intérieure, il est à nouveau séparé, la pièce se déplace le long du chemin et la pièce retourne à la source.

Le signal réfléchi sera additionné à l'original et le déformera, ce qui s'exprimera en rétrécissant la fenêtre sur le diagramme de l'œil et en augmentant le niveau de perte d'insertion (Eng. Insertion Loss).

Dans le pire des cas, le segment TD sera égal à 1/4 de la longueur d'onde du signal, puis le signal réfléchi atteindra le chemin sur la couche intérieure avec un retard de la moitié de la période, chevauchant le signal d'origine en antiphase.

Lors de l'analyse de l'intégrité, il est recommandé de considérer la bande passante avec une largeur de 5 fréquences de Nyquist. Une bonne approximation serait considérée comme un talon acceptable, donnant une résonance à 7 harmoniques et plus [2].

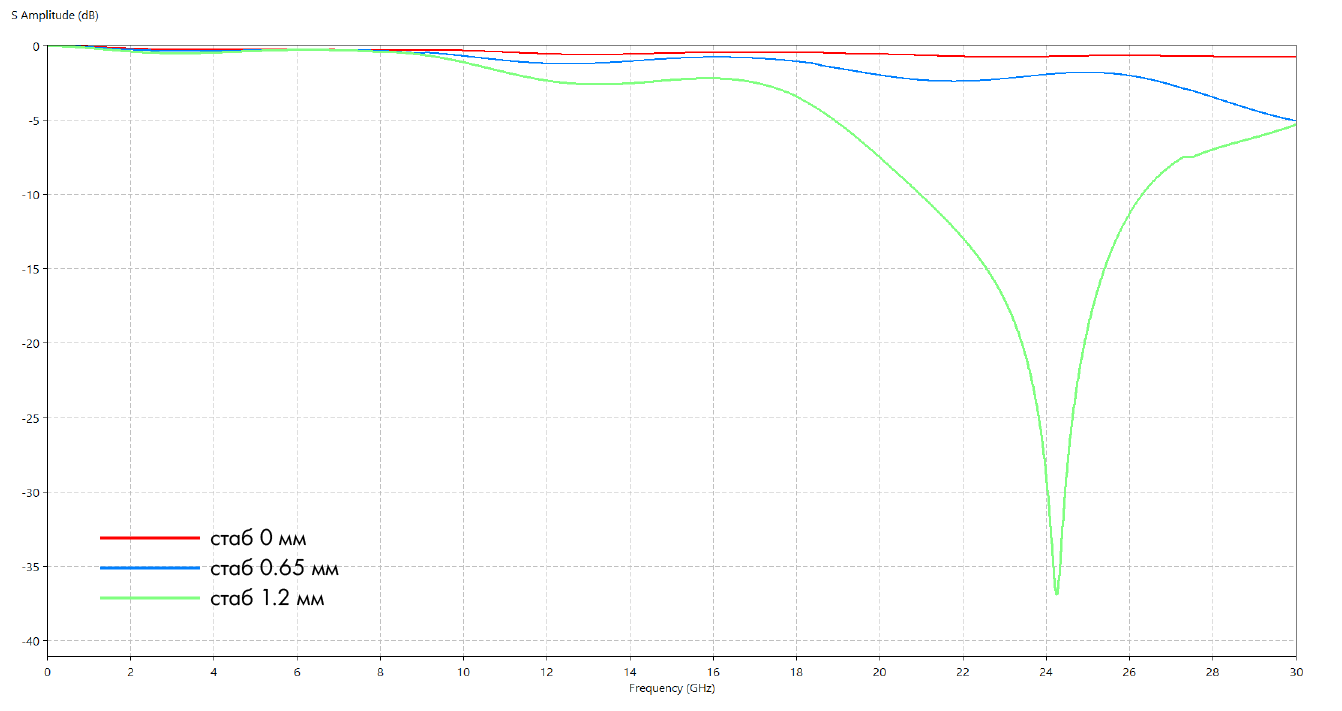

Figure 4. Graphique du niveau de perte d'insertion pour p / o avec des talons de 0, 0,65, 1,2 mm.

Figure 4. Graphique du niveau de perte d'insertion pour p / o avec des talons de 0, 0,65, 1,2 mm.La figure 4 montre une énorme résonance à des fréquences autour de 24 GHz. Nous pouvons conclure que si notre signal fonctionne à une fréquence de 2-3 GHz, nous pouvons nous permettre de ne pas éliminer le stub, car dans les 7 harmoniques «tout est calme».

Vous pouvez évaluer rapidement la criticité du talon dans

la calculatrice Polar :

Figure 5. Image de polarinstruments.com . Une longueur de tronçon de 2,5 mm est acceptable pour les signaux avec des temps de montée supérieurs à 500 ps.

Figure 5. Image de polarinstruments.com . Une longueur de tronçon de 2,5 mm est acceptable pour les signaux avec des temps de montée supérieurs à 500 ps.Les formules données dans [2] donnent un résultat légèrement plus précis. Ils prennent en compte la géométrie p / o et permettent de calculer la correction de la constante diélectrique du diélectrique le long de l'axe Z.

Vous pouvez éliminer le talon en utilisant l'opération de «backdrilling» (English Backdrilling) ou en utilisant des micro-transitions (vias anglais aveugles et enterrés). Le choix dépend des caractéristiques du projet. Le forage inversé est plus facile et moins cher. Après la fabrication de la planche, avec un foret de plus grand diamètre, le talon est percé à une profondeur prédéterminée. Le développeur doit définir une indentation supplémentaire de la topologie dans la zone de forage et le fabricant peut également spécifier les exigences de forage dans la documentation de conception. Les systèmes de CAO modernes prennent en charge cette fonctionnalité.

Les micro-jonctions sont principalement destinées aux cartes haute densité (HDI en anglais), mais dans certains cas, elles peuvent être utilisées en nivelant le coût élevé du refus de forer en arrière et en réduisant le nombre de couches sur la carte. Lors du développement de cartes HDI, il y a quelques points à garder à l'esprit:

- chaque nouveau type de paie augmente le coût de la commission;

- Pour le forage au laser, des préimprégnés optimisés spéciaux sont utilisés, dont les propriétés peuvent varier;

- la métallisation des trous borgnes augmente l'épaisseur du cuivre sur les couches internes.

Il est fortement recommandé de convenir à l'avance de la structure de la carte avec le fabricant.

Facteur 4. Diaphonie

Diaphonie - transmission de signaux indésirables d'une ligne à l'autre. Ce transfert se produit car deux conducteurs étroitement espacés ont un couplage capacitif et inductif.

La nature de la diaphonie des conducteurs de signaux et des contacts est légèrement différente.

Le signal n'a pas de couche de référence dans le n / a, les courants de retour circulent le long du n / a adjacent, formant une grande boucle. Diaphonie de signaux dans le n / a en raison de la composante inductive.

Le plus grand effet sur la minimisation de la diaphonie peut être obtenu en augmentant la distance entre p / o. Cependant, souvent le topologue n'a pas beaucoup d'espace.

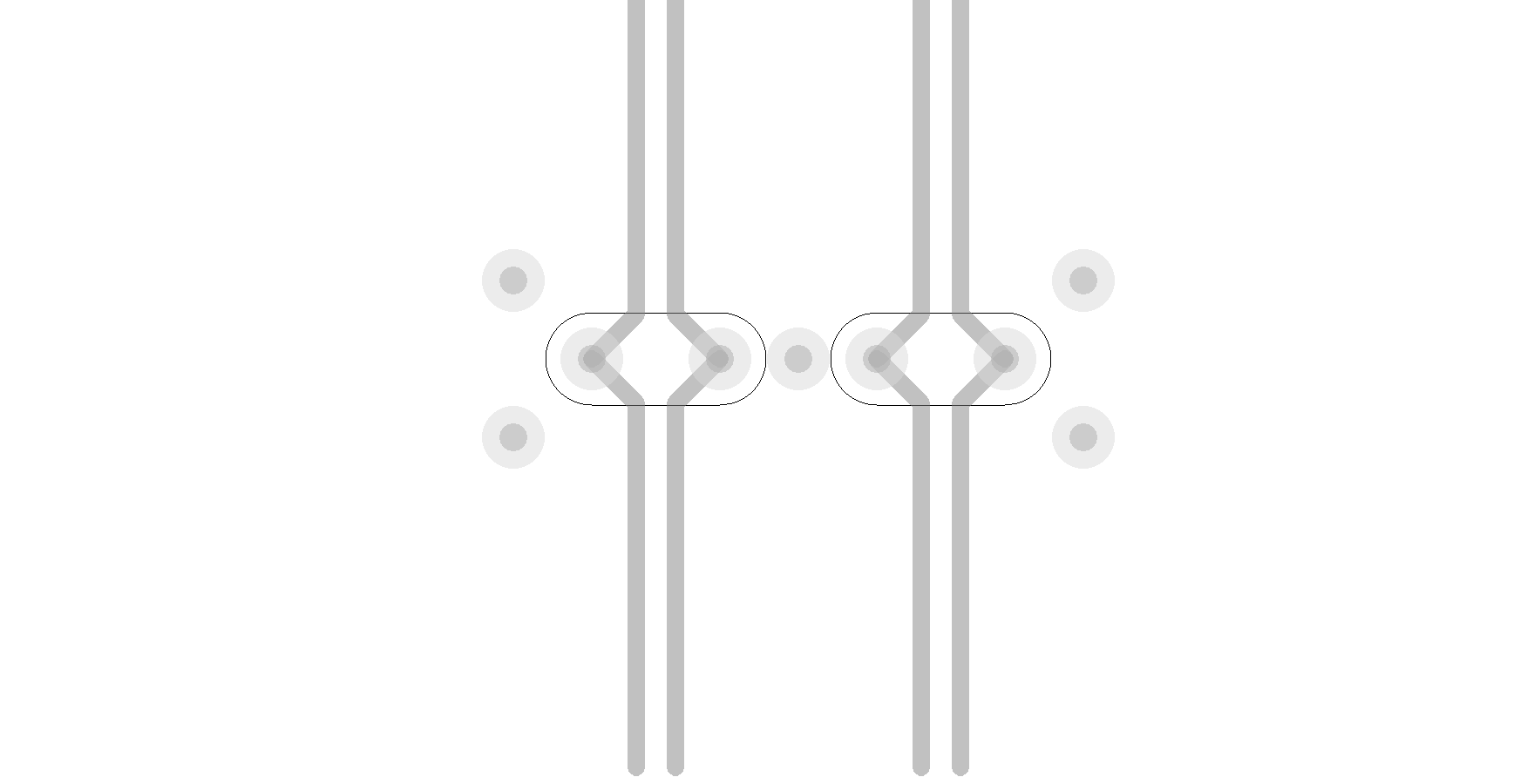

La convergence de p / o dans la paire différentielle réduit non seulement la zone occupée, mais a également un effet positif sur l'immunité au bruit [3].

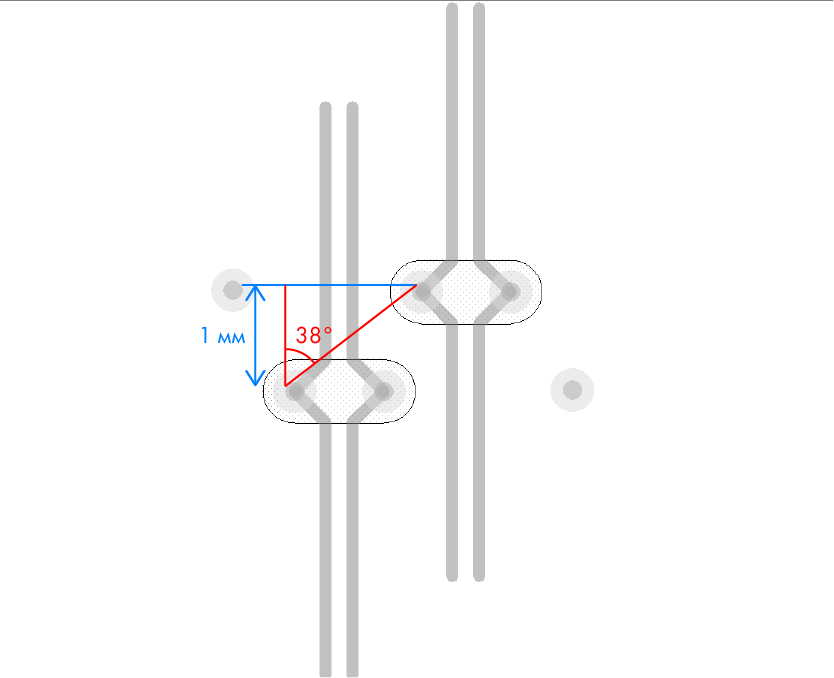

Une façon courante de minimiser la diaphonie entre les signaux adjacents p / o est de placer un blindage p / o entre eux. Avec cette méthode, il sera nécessaire de conduire des signaux par incréments d'environ 2 mm (figure 6). S'il n'y a pas assez d'espace, vous pouvez utiliser un pas plus petit avec un décalage (modèle anglais décalé), comme dans la figure 7. En utilisant la simulation, vous pouvez sélectionner l'angle de décalage idéal [4].

Figure 6. Réduction de la diaphonie à l'aide d'un demi-fil de blindage.

Figure 6. Réduction de la diaphonie à l'aide d'un demi-fil de blindage. Figure 7. Réduction de la diaphonie à l'aide d'un décalage diagonal en «damier».

Figure 7. Réduction de la diaphonie à l'aide d'un décalage diagonal en «damier».La diaphonie peut également être réduite par des méthodes exotiques, par exemple, par un long tronçon (en raison du déplacement de l'équilibre inductif-capacitif p / o) [5]. De plus, les interférences peuvent être réduites au stade de la conception du boîtier de la puce [6].

Facteur 5. Interférence du bus d'alimentation

En plus des circuits de signaux adjacents, la qualité du signal peut être affectée par les interférences des couches internes.

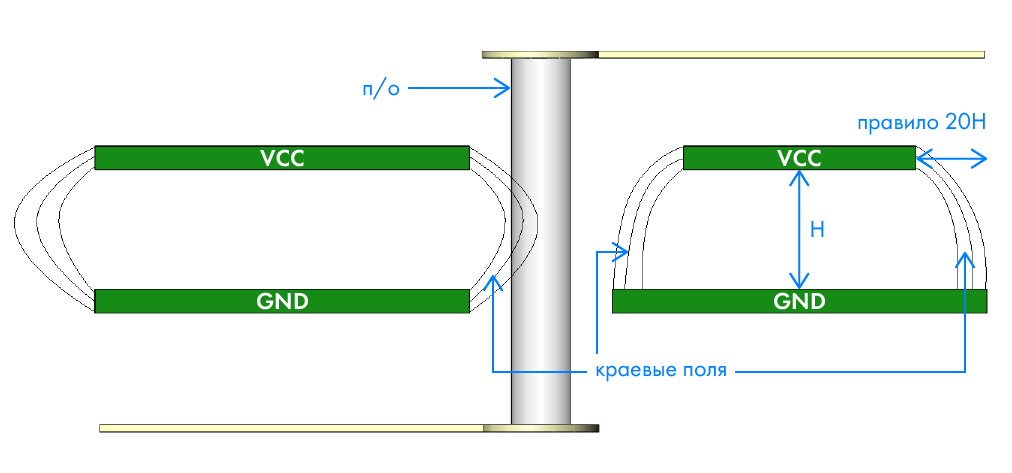

De grands courants peuvent circuler à travers les sites d'essais alimentaires. En raison de l'augmentation de l'inductance aux bords des polygones, les courants qui circulent forment des champs de bord (champs de franges anglaises) le long de toutes les limites du polygone, y compris les découpes. Les champs de périphérie sont une source de rayonnement électromagnétique (émission à émission par le front) dans l'espace. Pour réduire l'émission de rayonnement électromagnétique, la règle 20H est appliquée (figure 8), qui consiste à rétrécir la zone d'alimentation par rapport à la zone terrestre.

Figure 8. Champs Edge et règle 20H.

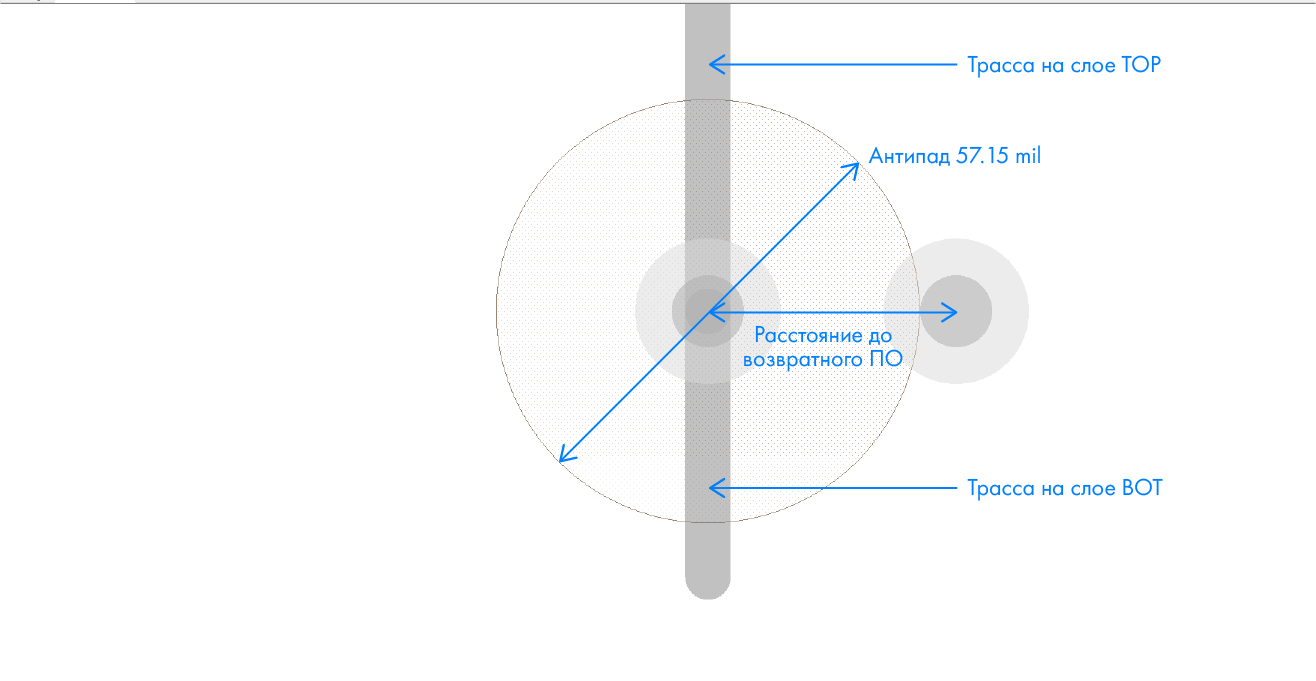

Figure 8. Champs Edge et règle 20H.Pour protéger le p / o des interférences, si possible, il est nécessaire d'augmenter l'antipad au niveau des gammes d'aliments. La règle de 20H pour le p / o est difficile à fournir et, inutilement, un anti-chute d'un diamètre d'environ 2 mm est généralement recommandé (figure 9).

Figure 9. Anti-goutte amélioré sur les couches alimentaires

Figure 9. Anti-goutte amélioré sur les couches alimentairesCalcul de l'impédance des vias simples

Sur la base des connaissances sur l'effet des éléments p / o sur l'impédance, nous pouvons concevoir notre p / o idéal. Un bon début est de calculer l'impédance dans la calculatrice.

Les ingénieurs de

conception de circuits imprimés aiment les calculatrices comme la

boîte à outils de conception de circuits imprimés Saturn et le

Polar Instruments Si9000e . Les deux vous permettent de calculer rapidement l'impédance d'un seul p / o.

Le résultat obtenu dans ces calculatrices est très différent les uns des autres. Cela est dû au fait que ces outils ont une approche différente.

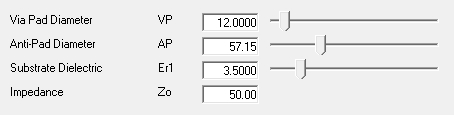

Polar calcule l'impédance dans un plan à deux dimensions, où la ligne d'alimentation traverse la plage de puissance. Les formules de calcul ne sont pas données. Il a été expérimentalement établi que le calcul est effectué selon la formule d'impédance du câble coaxial:

Figure 10. Image de polarinstruments.com

Figure 10. Image de polarinstruments.comL'illustration montre une valeur plutôt faible de la constante diélectrique Er1, par rapport à la norme. Cela est dû à l'hétérogénéité de la structure diélectrique: elle est constituée de résine (Er 3.2) et de filaments de fibre de verre (Er 6.1), et a donc une constante diélectrique moyenne d'environ 4.1. Cette valeur peut varier assez localement. Ainsi, la résine règne près de la sous-surface, par conséquent, la constante diélectrique est recalculée vers le bas [7].

Saturne PCB calcule l'impédance par la formule:

Lorsque la longueur p / o change, les valeurs d'inductance et de capacité changent de manière disproportionnée, l'impédance change. Impédance d'exactement la même longueur de p / o 1,6 mm, la carte de circuit imprimé Saturne calcule 128 Ohms! (Figure 11)

Figure 11. Calcul du logiciel dans la boîte à outils de conception de PCB Saturn.

Figure 11. Calcul du logiciel dans la boîte à outils de conception de PCB Saturn.La question se pose immédiatement: qui croire?

Nous simulons dans un solveur tridimensionnel de champs électromagnétiques (solveur 3D anglais) à quoi il ressemblera sur une véritable carte à 8 couches de 1,6 mm d'épaisseur (figure 12)

Figure 12. La structure de la transition entre les couches avec un trou pour le courant de retour.

Figure 12. La structure de la transition entre les couches avec un trou pour le courant de retour.Dans notre cas, l'impédance est d'environ 70 ohms. En approximant le retour p / o, vous pouvez obtenir une diminution de 5 ohms supplémentaires. Après avoir «joué» avec la taille de l'antipad, vous pouvez ajuster assez précisément l'impédance à la valeur cible (Figure 13).

Figure 13. L'impédance du circuit avec demi-onde sur le diagramme temporel.

Figure 13. L'impédance du circuit avec demi-onde sur le diagramme temporel.Dans le domaine fréquentiel, les «meilleurs» paramètres sont exprimés dans une valeur inférieure du coefficient de réflexion de l'entrée (figure 14).

Figure 14. Paramètres de p / o unique dans le domaine fréquentiel.

Figure 14. Paramètres de p / o unique dans le domaine fréquentiel.Le calcul Polar était plus proche du résultat. Peut-être, afin d'obtenir un résultat adéquat dans le PCB Saturne, des corrections sont nécessaires. Si quelqu'un a une expérience positive de calcul de l'impédance à Saturne, partagez les commentaires!

Calcul de l'impédance des vias différentiels

Le calcul du p / o différentiel est similaire au simple, sauf que maintenant nous n'avons pas de calculatrice: les outils ci-dessus ne prennent pas en compte le p / o différentiel. De plus, nous pouvons maintenant modifier en plus le pas de p / o dans le différentiel. couple.

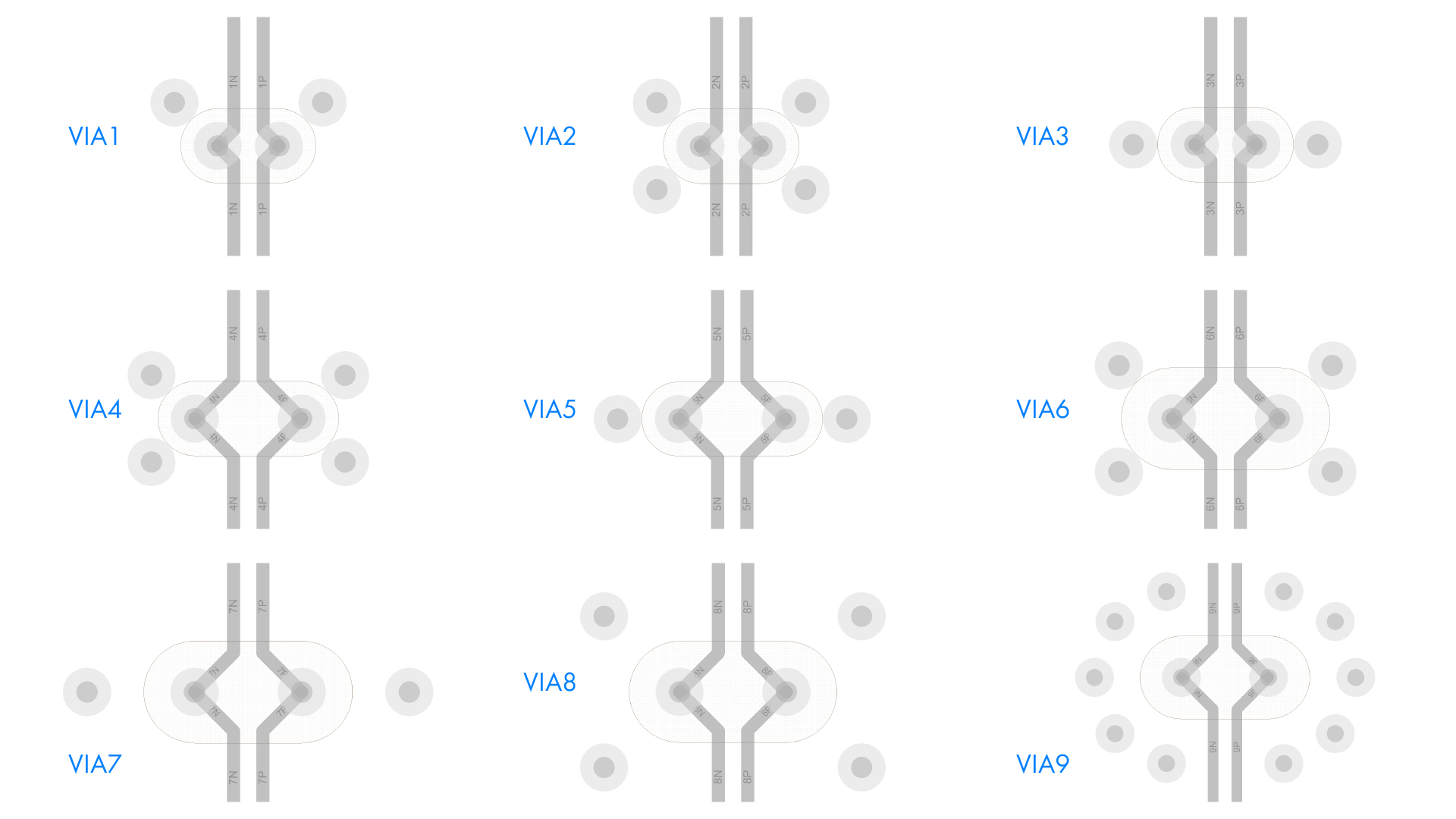

Prenez la même structure: une planche 8 couches de 1,6 mm d'épaisseur. Considérez 9 configurations du logiciel (Figure 15).

Les 3 premiers p / o ont des espaces de 0,125 mm et ne diffèrent que par l'emplacement des trous pour le courant de retour. Tous les p / o à partir de 4 ont un pas de 1 mm. Les P / o à partir de 6 ont une anti-chute accrue (0,250 mm) et se distinguent par l'indentation des trous pour le courant de retour.

Figure 15. vias.

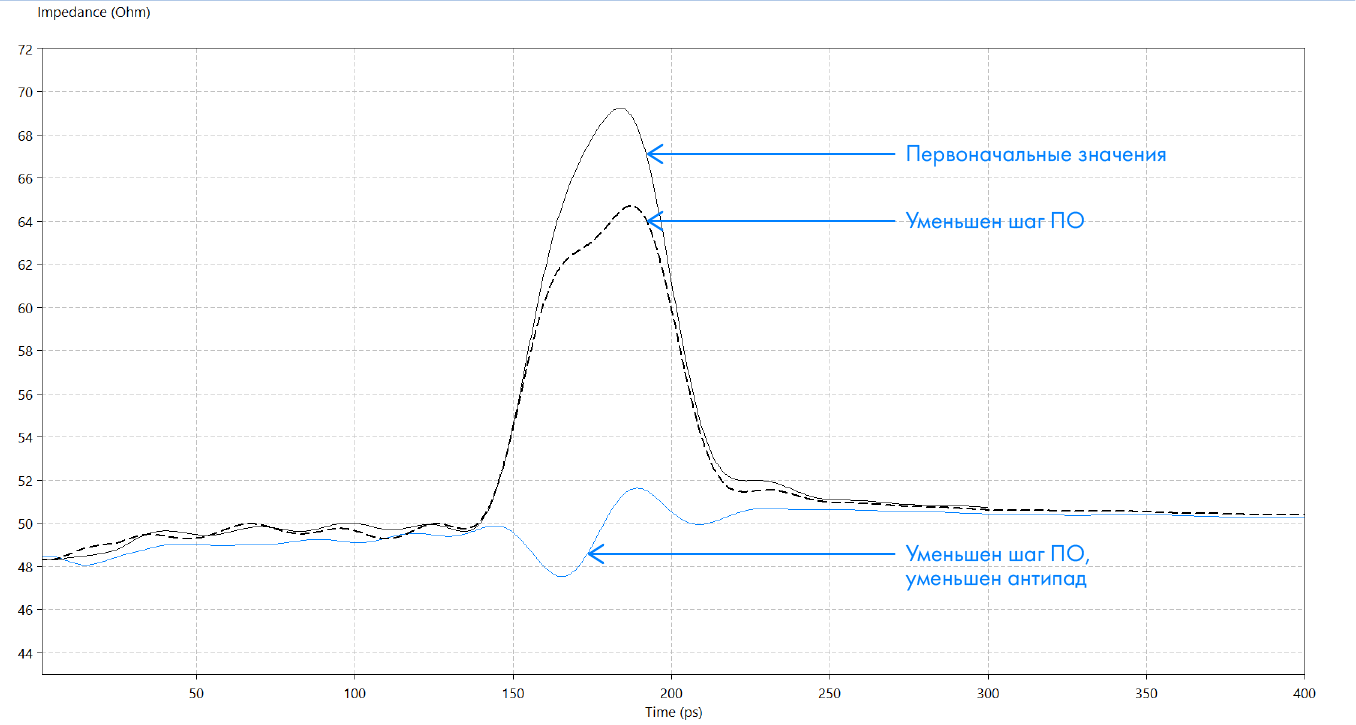

Figure 15. vias.Considérez le graphique d'impédance (figure 16).

Figure 16. Impédance p / o dans le domaine temporel.

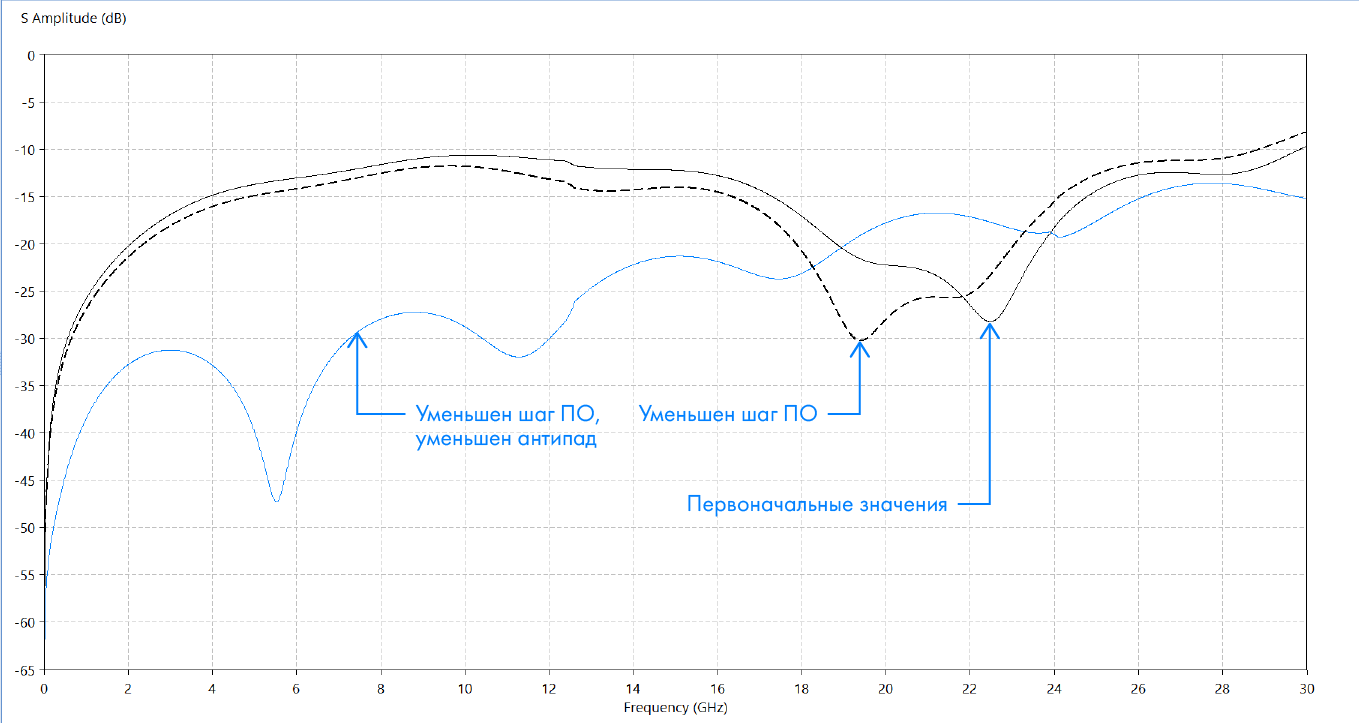

Figure 16. Impédance p / o dans le domaine temporel.Sur le graphique, la "bosse" est clairement visible, ce qui correspond à la section verticale de la demi-coquille - le "verre" (en anglais Via barrel).

Après avoir examiné la dépendance en fréquence du coefficient de réflexion VIA1-3 (figure 17), nous constatons que malgré de bonnes performances à la fréquence cible de 6 GHz, il existe une résonance à des fréquences plus basses. Il est préférable d'améliorer via7-9, et si cela ne fonctionne pas, puis via4-5 pour réduire la "bosse" due au décalage des graphiques vers la droite.

Figure 17. Le coefficient de réflexion de l'entrée p / o.

Figure 17. Le coefficient de réflexion de l'entrée p / o.Réduisez l'anti-chute dans VIA9 pour obtenir des espaces de 0,125 mm. Pour VIA4, nous réduisons le pas p / o à 0,75 mm et considérons le résultat obtenu (figure 18).

Figure 18. Comparaison de l'impédance du p / o modifié.

Figure 18. Comparaison de l'impédance du p / o modifié.Dans le domaine fréquentiel, un décalage du graphique du coefficient de réflexion de l'entrée vers la droite est visible (figure 19).

Figure 19. Comparaison du coefficient de réflexion du logiciel modifié.

Figure 19. Comparaison du coefficient de réflexion du logiciel modifié.Recommandations finales

Vias dans les cartes de circuits imprimés est une structure complexe et hétérogène. Pour le calcul correct des paramètres, des solveurs 3D coûteux, des compétences et des coûts de temps importants sont nécessaires.

S'il n'est pas possible d'éviter l'utilisation de transitions de signaux critiques vers d'autres couches, il faut tout d'abord évaluer le degré d'influence des inhomogénéités apparues sur l'intégrité des signaux. Si l'hétérogénéité est électriquement courte (le temps de retard est inférieur à 1/6 du front), le talon résonne à des fréquences en dehors de la bande passante - il n'y a aucun intérêt à perdre du temps et de l'argent à optimiser.

Dans une première approximation, il est pratique d'utiliser des structures prêtes à l'emploi à partir de fiches techniques ou de tableaux précédents, mais n'oubliez pas les caractéristiques du projet en cours.

Les calculatrices vous permettent d'évaluer rapidement les paramètres du logiciel, mais elles utilisent des modèles très simplifiés qui affectent négativement le résultat.

Les références- Chin, T. Paires différentielles: quatre choses que vous devez savoir sur les vias. Extrait de la communauté TI E2E: https://e2e.ti.com/blogs_/b/analogwire/archive/2015/06/10/differential-pairs-four-things-you-need-to-know-about-vias#

- Simonovich, B. Via des talons démystifiés. Extrait des notes de conception de Bert Simonovich: https://blog.lamsimenterprises.com/2017/03/08/via-stubs-demystified/

- Démystifier les vias dans la conception de circuits imprimés à haute vitesse. Récupéré de la technologie Keysight: https://www.keysight.com

- K. Aihara, J. Buan, A. Nagao, T. Takada et CC Huang, «Minimiser la diaphonie différentielle des vias pour la transmission de données à grande vitesse», dans Proc. 14th Elect. Effectuez. Electron Packages et systèmes, Portland, OR, oct. 2014.

- CM Nieh et J. Park, «Far-end Crosstalk Cancellation using Via Stub for DDR4 Memory Channel», dans Proc. 63rd Electronics Components and Technology Conference, Las Vegas, NV, mai 2013, pp. 2035-2040.

- H. Kanno, H. Ogura et K. Takahashi, «Boîtier polymère à cristaux liquides montable en surface avec inductance de fil de compensation de transition verticale jusqu'à la bande V», dans IEEE MTT-S Int. Micro-ondes Symp. Dig., Philadelphie, PA, juin 2003, pp. 1159-1162.

- Via le calcul d'impédance Pad / Anti-Pad. Extrait des instruments polaires https://www.polarinstruments.com/support/si/AP8178.html