De nos jours, il existe plusieurs types de mémoire, chacun étant utilisé pour une tâche particulière. Ils s'acquittent assez bien de leurs tâches, mais il existe un certain nombre de lacunes qui ne permettent d'appeler aucune de ces options de mémoire universelle. Si nous ajoutons ici le problème de la croissance colossale de données partout dans le monde et la soif de l'humanité pour la conservation de l'énergie, alors il est nécessaire de créer quelque chose de complètement nouveau. Aujourd'hui, nous allons rencontrer une étude dans laquelle les scientifiques ont introduit un nouveau type de mémoire qui combine les avantages de la mémoire flash et de la mémoire DRAM. Quels sont les «atouts» de cette innovation, quelles technologies ont été utilisées pour la créer et quelles sont les perspectives? Nous en apprenons à travers le rapport du groupe de recherche. Allons-y.

Base d'étude

Il existe de nombreux types de mémoire, et tous ont été créés pour une tâche spécifique: SRAM (mémoire statique à accès aléatoire) pour le cache, DRAM (mémoire dynamique à accès aléatoire) pour la mémoire active, mémoire flash pour le stockage de données, etc. Cependant, comme prévu, chacun des types de mémoire ci-dessus a ses propres défauts personnels.

Par exemple, la mémoire flash, qui est une collection de transistors MOS (semi-conducteur à oxyde métallique) avec une grille flottante (FG) pour stocker la charge. Les données sont présentées dans un mode de réalisation tel que la quantité de charge contenue dans le FG, qui est isolée par des couches d'oxyde.

L'inconvénient, selon les scientifiques, est que pour l'enregistrement et l'effacement, une tension suffisamment élevée est requise pour le contrôle par un obturateur de contrôle (CG), généralement d'environ ± 20 V

2 . Ce processus est lent et le mécanisme de défaillance induit par une surtension entraîne une réduction de la durée de vie de l'appareil.

Malgré ce inconvénient, il y a un avantage plutôt impressionnant - les données sont lues en vérifiant la conductivité du canal, qui nécessite très peu de tension. Pour cette raison, les données restent intactes, ce qui est appelé lecture non destructive.

La DRAM, à son tour, est beaucoup plus rapide que la mémoire flash, c'est pourquoi elle est utilisée pour ainsi dire pour les processus informatiques actifs. L'inconvénient de la DRAM est que les données sont perdues des cellules lors de leur lecture. De plus, des fuites de charge des condensateurs utilisés pour stocker les données se produisent.

SRAM est également un type de mémoire assez rapide et les données ne sont pas aussi perdues que dans la DRAM. Cependant, en règle générale, 6 transistors par cellule sont utilisés, c'est-à-dire que vous avez besoin de beaucoup d'espace sur la puce.

Après avoir présenté les lacunes décrites ci-dessus des types de mémoire classiques, les scientifiques soulignent l'importance de trouver une option alternative ou hybride qui sera exempte de tels problèmes, tout en combinant tous les avantages de leurs prédécesseurs.

Dans ce travail, les chercheurs présentent à leur attention leur vision d'un nouveau type de mémoire - un nouveau dispositif de mémoire basse tension, semi-conducteur, à base de charge et non volatile de forme compacte, fonctionnant à température ambiante. Les chercheurs ont surnommé leur progéniture une «mémoire universelle» (simple, mais de bon goût).

Le dispositif est une mémoire à grille flottante, créée sur la base d'hétérostructures InAs / AlSb / GaSb, où InAs est utilisé à la fois comme grille flottante et comme canal sans transitions.

Les scientifiques ont fourni des résultats de simulation et de test réels pour un prototype unicellulaire.

Résultats de recherche

Image n ° 1

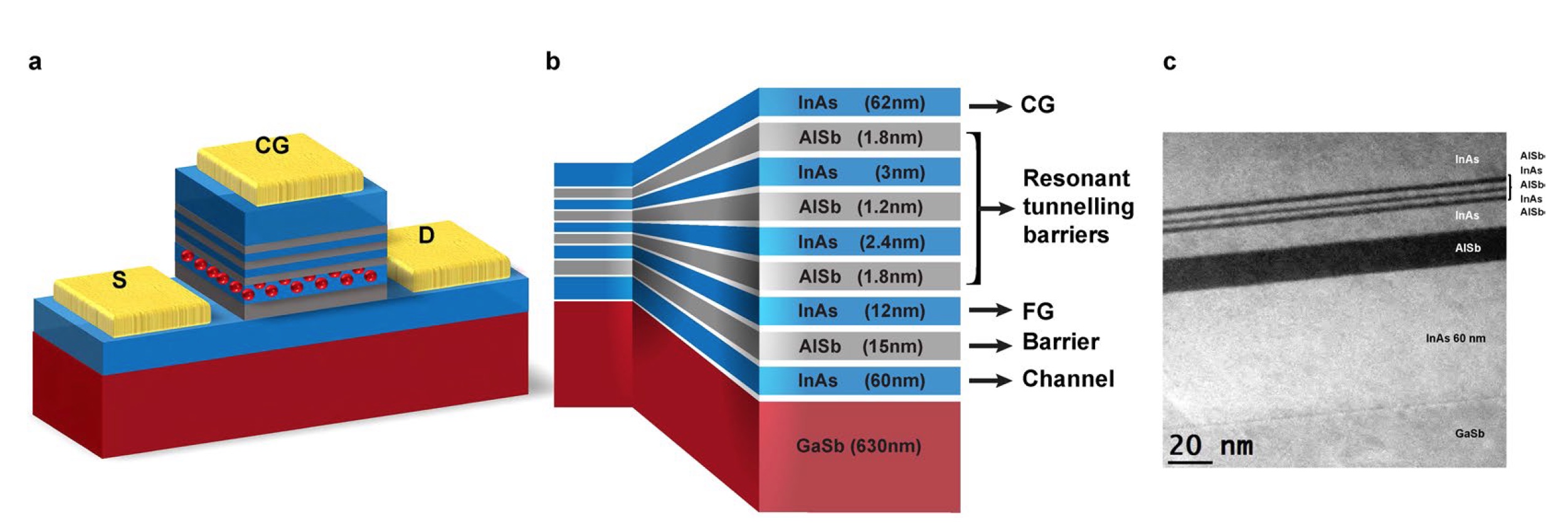

Image n ° 1L'image ci-dessus montre une vue schématique d'un appareil et une image d'un PREM (microscope électronique à transmission).

Comme dans le cas de la mémoire flash, dans cet appareil, la charge est stockée dans FG, mais en même temps il n'y a pas de barrières d'oxyde. Au lieu de cela, un décalage de la bande de conduction dans la famille de semi-conducteurs dite 6.1-Å a été utilisé. Autrement dit, le dispositif sous-jacent à la cellule de mémoire ressemble plus à un transistor à mobilité électronique élevée (HEMT) qu'à un transistor MOS. InAs forme un canal qui ne contient pas de transitions. Cependant, le dopage n a été utilisé afin de compenser le dopage de fond involontaire et de conserver les lacunes de Ga dans le GaSb sous-jacent. Ces deux tâches créent naturellement des couches de type p.

La jonction pn * est la zone de contact de deux semi-conducteurs avec différents types de conductivité - p (trou) et n (électronique).

Image n ° 2

Image n ° 2Le graphique

2a montre l'alignement simulé des bandes d'énergie, ainsi que la densité d'électrons et de trous dans les couches en l'absence de biais. Les données théoriques, ainsi que la simulation, démontrent que la bande de conduction InAs est inférieure à la bande de valence GaSb à l'interface InAs et GaSb. Et cela conduit au transfert d'électrons de la couche GaSb à la couche InAs, après quoi les trous restent dans GaSb.

Le trou * est une liaison de valence non remplie, se manifestant comme une charge positive égale à la charge d'un électron.

Les électrons / trous accumulés sont visibles à l'interface entre InAs et GaSb, mais les électrons dans le canal InAs ne sont pas connectés à l'interface InAs / GaSb, et leur densité est observée dans tout InAs. La conductivité de l'ensemble du canal est dominée par les électrons dans InAs, qui auront une mobilité plus élevée et une densité plus élevée que les trous dans GaSb.

Le FG interne de la couche d'InAs est isolé du canal InAs par une barrière AlSb (15 nm). Dans le même temps,

des puits quantiques InAs double

* et trois barrières AlSb agissent comme une barrière de résonance tunnel entre FG et CG InAs avec dopage n.

Puits quantique * - limite le mouvement des particules dans la dimension bidimensionnelle (au lieu de tridimensionnelle), car elles ne peuvent se déplacer que dans une couche plate.

Par conséquent, dans le dispositif à l'étude, les électrons stockés dans le FG de la couche d'InAs sont isolés par un écart anormalement grand dans la bande de conduction avec AlSb. Cela signifie que vous pouvez obtenir un système de limitation de charge, qui aura un temps de stockage à température ambiante égal à 1014 ans.

L'aspect le plus important du fonctionnement du dispositif à l'étude est le fait que deux puits quantiques (QW1 et QW2) dans la barrière à effet tunnel à trois résonances ont des épaisseurs différentes, c'est-à-dire que des états limités avec des énergies différentes se produisent (

2a ). Puisque QW2 est plus mince que QW1, le seul niveau d'énergie disponible pour les électrons dans QW2 a une énergie plus élevée que l'équivalent dans QW1. De plus, l'état dans QW1 a une énergie significativement plus élevée que l'état dans la région CG voisine. Cela empêche la tunnelisation électronique directe entre CG et FG, et la barrière de transfert d'électrons de CG à FG (ou vice versa) est déterminée par un décalage de la bande de conduction InAs / AlSb de 2,1 eV, c'est-à-dire que la charge ne circulera pas vers / depuis FG.

Les états excité au sol et primaire dans la grille flottante (FG) sont situés bien en dessous des états énergétiques à l'intérieur des deux QW. Par conséquent, lorsqu'aucune tension n'est appliquée, les électrons sont bloqués à l'intérieur du FG, c'est-à-dire la barrière à effet tunnel à trois résonances devient insurmontable pour les électrons vers / depuis FG. Ainsi, la non-volatilité est atteinte.

Si une tension insignifiante est appliquée à la grille de commande (CG), il est alors possible d'ajuster le couplage des états d'énergie à l'intérieur de la barrière de résonance tunnel, ce qui permettra aux électrons de passer librement de (

2b ) ou (

2c ) la grille flottante.

Au cours des expériences, toutes les opérations de lecture, d'écriture et d'effacement ont été effectuées dans plusieurs cellules (taille d'obturation 10 x 10 μm) dans une boîte sombre protégée contre les décharges électrostatiques à température ambiante. Toutes les opérations, y compris l'enregistrement et l'effacement, ont été effectuées avec un décalage ≤ 2,6 V, ce qui est environ un ordre de grandeur inférieur à celui nécessaire pour un fonctionnement complet avec une cellule de mémoire flash, soulignent les chercheurs. L'effacement a été effectué en décalant la grille de commande (V

E CG-S ) de +2,5 ou +2,6 V entre le CG et la source, ce qui a conduit à l'état "0".

La figure

2b montre un alignement simulé des bandes d'énergie obtenues avec une tension d'effacement de +2,6 V. Dans de telles circonstances, le niveau d'énergie des électrons calculé dans QW1 est inférieur au niveau dans QW2, tandis que les deux sont en dessous du premier état excité et sont proches du niveau d'énergie état fondamental dans FG. Le résultat est un effacement, c'est-à-dire un flux d'électrons de FG à CG suivi d'une déplétion de FG. Le même principe fonctionne pour l'opération d'écriture: V

W CG-S = -V

E CG-S pour augmenter la charge en FG (état «1»).

Le graphique

2c est une zone d'énergie simulée lorsque le décalage de la porte de contrôle est utilisé pour l'enregistrement des données: V

W CG-S = −2,6 V. Dans ce cas, les niveaux d'énergie dans QW1 et QW2 coïncident pratiquement, ce qui conduit à un fort couplage de ces états, à l'effet tunnel résonnant et au flux électrons de CG à FG.

En raison du couplage capacitif, la conductivité du canal dépend de la quantité de charge stockée dans le FG, par conséquent, les données sont lues en mesurant le courant grille-source à une tension grille-source fixe.

Augmentation de la charge en FG, c'est-à-dire l'état "1", réduit la charge dans le canal, ce qui entraîne une diminution de sa conductivité. Dans le cas de l'état "0", le processus inverse se produit. Les données peuvent être lues sans aucune polarisation vers CG, mais la tension est nécessaire pour la sélection individuelle des appareils dans un réseau de cellules. De plus, la tension devrait générer un champ électrique à travers la barrière résonnante à effet tunnel, ce qui permettra de transférer la charge de / vers FG. Pour accomplir ces tâches, seulement ~ 2,5 V. est requis.

Caractéristiques de la mémoire universelle

Lors des tests pratiques, la lecture a été effectuée avec un décalage nul par CG et V

SD = 1,0 V. Cependant, selon les scientifiques, il était possible d'appliquer moins de tension pour une lecture réussie.

Image n ° 3

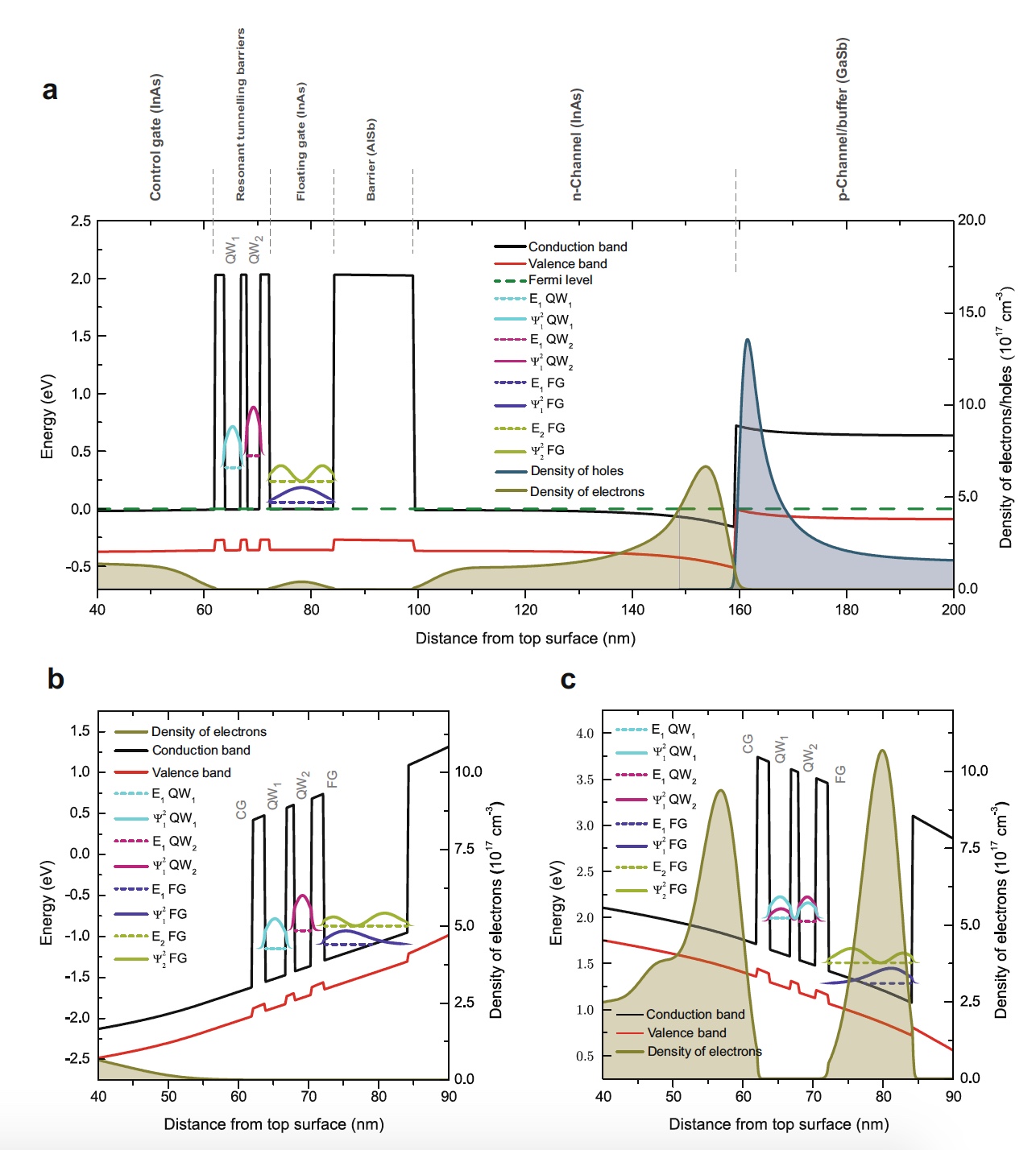

Image n ° 3La figure

3a montre le processus d'effacement-lecture-écriture-lecture. La caractéristique principale de la séquence est l'opération de lecture après chaque étape d'effacement ou d'écriture.

La figure

3b montre une séquence plus compliquée dans laquelle après chaque opération d'effacement et d'écriture, il n'y a pas une opération de lecture, mais plusieurs. De cette façon, les chercheurs démontrent que l'opération de lecture est non destructive.

Entre l'état «0» et «1», il y a une nette différence dans toutes les séquences. Cependant, sur

3b, il y a des signes d'un changement symétrique vers le haut dans I

SD à mesure que le nombre d'opérations augmente. Bien que la raison de ce comportement ne soit pas claire, les scientifiques ont l'intention d'explorer cet aspect dans d'autres travaux. Mais sur

3a, cela n'est pas observé, car la tension d'effacement / écriture est légèrement inférieure.

Après plusieurs centaines d'opérations d'écriture et d'effacement, ainsi que de nombreuses opérations de lecture lors de plusieurs tests pratiques, les scientifiques n'ont trouvé aucun signe de détérioration de l'appareil.

Une caractéristique importante de tous les types de mémoire, qui sont basés sur le stockage de charge, est l'énergie de commutation déterminée par l'énergie de charge du condensateur.

La similitude des principes fondamentaux de la technologie de la mémoire flash et de la mémoire universelle à l'étude suggère une comparaison de ces deux types de mémoire. Si nous supposons que les deux appareils de ces deux types ont la même capacité avec la même taille d'obturation, alors l'énergie de commutation de la mémoire universelle sera 64 fois inférieure à celle de la mémoire flash. Ces chiffres étonnants montrent également la supériorité de la mémoire universelle sur la DRAM.

Selon des estimations théoriques, la capacité CG-FG est de l'ordre de 10

-12 F pour un appareil mesurant 10 x 10 μm, et l'énergie de commutation est d'environ 2 x 10

-12 J.Réduire la taille physique de l'appareil réduit fortement l'énergie de commutation à 10

-17 J pour un appareil de taille 20 nm, et c'est 100 fois moins que pour la DRAM, et 1000 fois moins que pour la mémoire flash. Et cela, selon les déclarations audacieuses des chercheurs, est des caractéristiques très uniques.

L'image

3c montre certaines opérations d'effacement en écriture à partir de

3b , où les différences entre l'état «0» et «1» sont visibles: les mesures de lecture consécutives après l'effacement donnent un I

SD légèrement inférieur pour l'état «0». La situation inverse est observée avec des mesures de lecture séquentielles après enregistrement, ou plutôt, I

SD est légèrement plus grande.

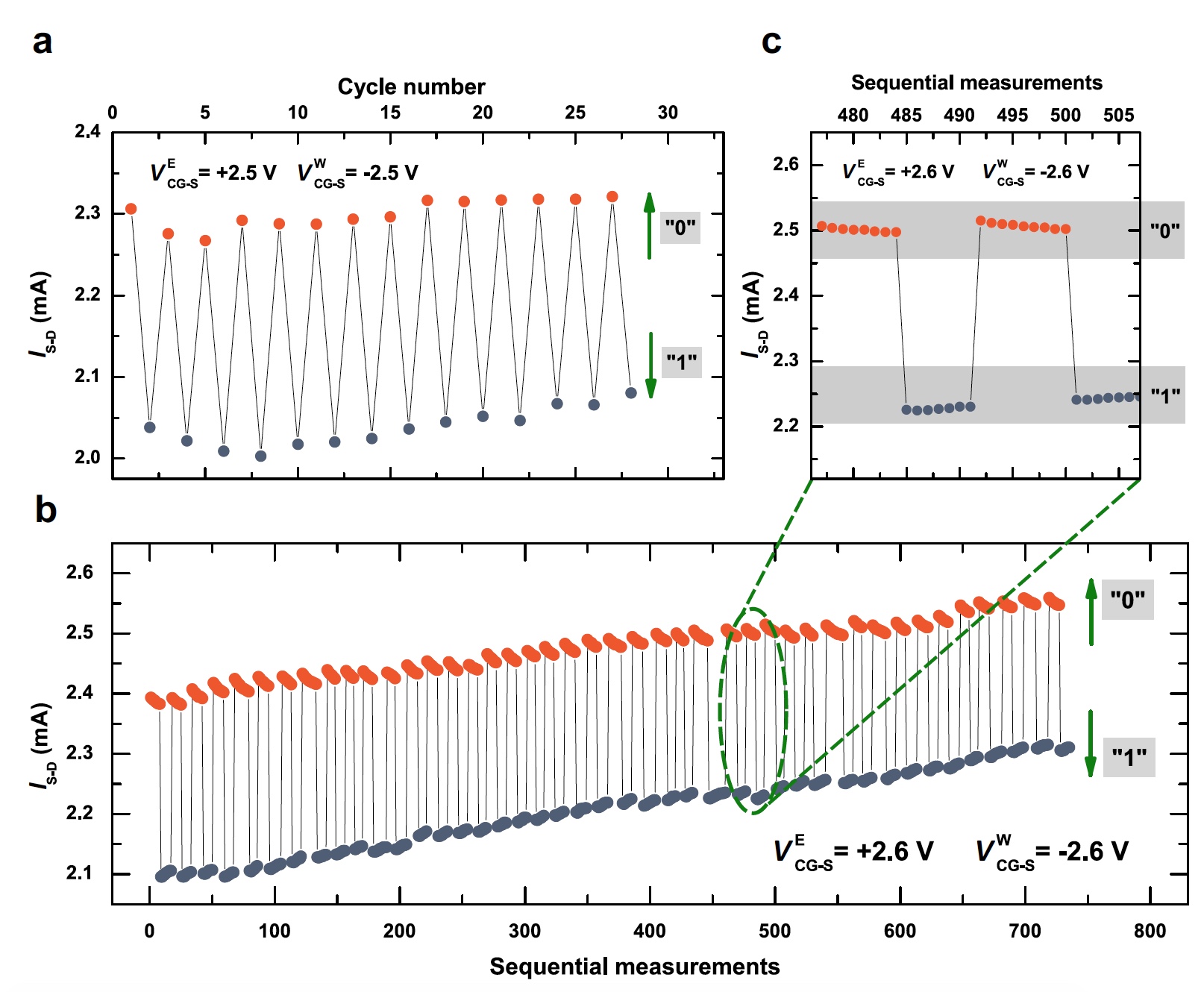

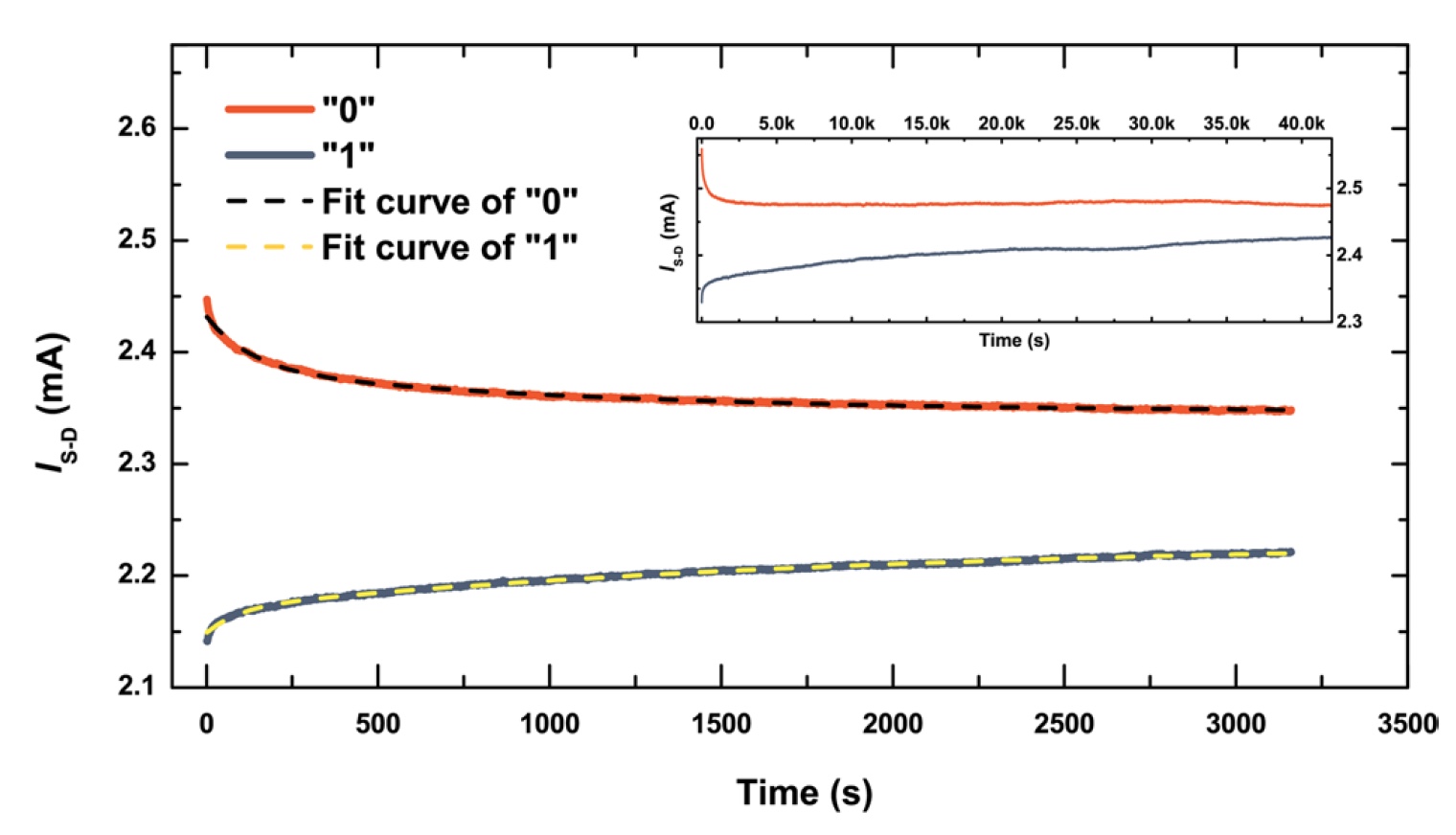

Les scientifiques attribuent cet effet à la variabilité (volatilité) des données. Pour étudier cela, les scientifiques ont effectué une séquence d'opérations de lecture sur une longue période de temps pour chaque état de la mémoire (image n ° 4).

Image n ° 4

Image n ° 4Les deux états «0» et «1» ont montré une décroissance rapide initiale, ce qui est cohérent avec ce qui est observé pendant

3 s . Mais après cela, des changements beaucoup plus lents se produisent, de sorte que pendant toute la durée de l'observation, les états correspondants «0» et «1» peuvent être clairement distingués.

Une autre expérience a également été réalisée (encart sur l'image n ° 4), qui montre la saturation limite de l'atténuation exponentielle et les états distinguables "0" et "1" dans le temps.

L'existence d'une double atténuation exponentielle signifie que plusieurs mécanismes sous-tendent la dégradation des états à la fois. Parmi les options possibles, les scientifiques distinguent le tunnelage à travers des états défectueux dans les barrières AlSb, l'excitation thermique des électrons à travers la bande interdite étroite InAs et la recombinaison avec des trous générés thermiquement.

L'évaluation de la capacité du dispositif et de la tension appliquée pour l'enregistrement / l'effacement indique qu'environ 107 électrons sont transférés de / vers la grille flottante pendant l'opération d'écriture et d'effacement. C'est beaucoup, mais pratiquement aucune influence négative n'est observée.

Pour une connaissance plus détaillée des nuances de l'étude, je vous recommande de consulter le

rapport du groupe de recherche .

Épilogue

Les scientifiques ont réussi non seulement à développer un nouveau type de mémoire, mais aussi à mener avec succès les premiers tests pratiques d'un appareil non volatil à base de charge de taille compacte à température ambiante. Les scientifiques ont également réussi à combiner la non-volatilité et la commutation à basse tension par les propriétés mécaniques quantiques d'une barrière à effet tunnel asymétrique triple résonante. Les chercheurs disent que leur appareil peut être mis à l'échelle sans perdre sa dignité.

Les temps changent, les technologies aussi. La mémoire flash, la SRAM et la DRAM occupent depuis longtemps une position dominante parmi les dispositifs de mémoire, mais cela pourrait changer si le développement de la mémoire universelle se poursuit avec le même succès que dans cette étude. Cette technologie permettra de réduire considérablement la consommation d'énergie des appareils qui en sont équipés, ainsi que d'allonger leur durée de vie et d'augmenter la productivité.

D'autres études prévues par les auteurs montreront à quel point la mémoire révolutionnaire est, si fièrement qualifiée d'universelle par les scientifiques.

Merci de votre attention, restez curieux et bonne semaine de travail, les gars!

Merci de rester avec nous. Aimez-vous nos articles? Vous voulez voir des matériaux plus intéressants? Soutenez-nous en passant une commande ou en le recommandant à vos amis, une

réduction de 30% pour les utilisateurs Habr sur un analogue unique de serveurs d'entrée de gamme que nous avons inventés pour vous: Toute la vérité sur VPS (KVM) E5-2650 v4 (6 cœurs) 10 Go DDR4 240 Go SSD 1 Gbps à partir de 20 $ ou comment diviser le serveur? (les options sont disponibles avec RAID1 et RAID10, jusqu'à 24 cœurs et jusqu'à 40 Go de DDR4).

Dell R730xd 2 fois moins cher? Nous avons seulement

2 x Intel TetraDeca-Core Xeon 2x E5-2697v3 2.6GHz 14C 64GB DDR4 4x960GB SSD 1Gbps 100 TV à partir de 199 $ aux Pays-Bas! Dell R420 - 2x E5-2430 2.2Ghz 6C 128GB DDR3 2x960GB SSD 1Gbps 100TB - à partir de 99 $! Pour en savoir plus sur la

création d'un bâtiment d'infrastructure. classe utilisant des serveurs Dell R730xd E5-2650 v4 coûtant 9 000 euros pour un sou?