Il s'agit du troisième article d'une série sur la conception des processeurs. Dans le premier article, nous avons examiné l'architecture d'un ordinateur et expliqué son fonctionnement à un niveau élevé. Le deuxième article a parlé de la conception et de la mise en œuvre de certains composants de la puce. Dans la troisième partie, nous apprendrons comment les conceptions architecturales et les circuits électriques deviennent des puces physiques.

Comment transformer un tas de sable en un processeur moderne? Voyons cela.

Partie 1: Bases de l'architecture informatique (architectures de jeux d'instructions, mise en cache, pipelines, hyperthreading)

Partie 2: Processus de conception CPU (circuits électriques, transistors, éléments logiques, synchronisation)

Partie 3: Disposition et fabrication physique de la puce (VLSI et fabrication de silicium)

Partie 4: Tendances actuelles et orientations futures importantes en architecture informatique (mer d'accélérateurs, intégration tridimensionnelle, FPGA, Near Memory Computing)

Comme mentionné précédemment, les processeurs et toutes les autres logiques numériques sont composés de transistors. Un transistor est un interrupteur à commande électrique qui peut être mis sous et hors tension en appliquant ou en déconnectant une tension de grille. Nous avons dit qu'il existe deux types de transistors: les appareils nMOS passent le courant lorsque l'obturateur est activé et les appareils pMOS passent le courant lorsque l'obturateur est éteint. La structure de base du processeur est constituée de transistors en silicium. Le silicium est un

semi -

conducteur , car il occupe une position intermédiaire - il ne conduit pas complètement le courant, mais ce n'est pas un isolant.

Pour transformer une tranche de silicium en un circuit électrique pratique en ajoutant des transistors, les ingénieurs de production utilisent un processus appelé

dopage . Le dopage est le processus consistant à ajouter des impuretés soigneusement sélectionnées au substrat de silicium de base pour modifier sa conductivité. Le but est de changer le comportement des électrons afin de pouvoir les contrôler. Il existe deux types de transistors, et donc, deux types principaux de dopage.

Le processus de fabrication d'une plaque avant de placer les puces dans le boîtier.Si nous ajoutons un nombre précisément contrôlé d'éléments donneurs d'électrons, tels que l'arsenic, l'antimoine ou le phosphore, nous pouvons créer une région de type n. Puisque la région de la plaque sur laquelle ces éléments sont déposés a maintenant un excès d'électrons, il se charge négativement. De là est venu le nom du type (n - négatif) et la lettre "n" dans nMOS. En ajoutant des éléments accepteurs d'électrons tels que le bore, l'indium ou le gallium au silicium, nous pouvons créer une région de type p qui est chargée positivement. De là est venue la lettre «p» dans le type p et pMOS (p - positif). Les processus spécifiques pour ajouter ces impuretés au silicium sont appelés

implantation et

diffusion ioniques ; nous ne les considérerons pas dans l'article.

Maintenant que nous pouvons contrôler la conductivité électrique des différentes parties de la tranche de silicium, nous pouvons combiner les propriétés de plusieurs zones pour créer des transistors. Les transistors utilisés dans les circuits intégrés et appelés MOSFET (Transistors à effet de champ à oxyde métallique semiconducteur, structures MOS, structures conductrices à oxyde métallique) ont quatre connexions. Le courant que nous contrôlons circule entre la source et le drain. Dans un dispositif à canal n, le courant pénètre généralement dans le drain et quitte la source, tandis que dans un dispositif à canal p, il s'écoule généralement de la source et quitte le drain. Une grille est un interrupteur utilisé pour activer et désactiver un transistor. Enfin, l'appareil possède un corps de transistor (Body), qui ne s'applique pas au processeur, nous ne le considérerons donc pas.

La structure physique de l'onduleur en silicium. Les zones de couleurs différentes ont des propriétés de conductivité différentes. Remarquez comment les différents composants en silicium correspondent au schéma de droite.Les détails techniques du fonctionnement des transistors et de l'interaction des zones individuelles sont le contenu de l'ensemble du cours collégial, nous n'aborderons donc que les bases. Une bonne analogie avec leur travail est un pont-levis sur une rivière. Les voitures - les électrons dans le transistor - veulent circuler d'un côté à l'autre de la rivière, c'est la source et le drain du transistor. Prenons l'exemple du dispositif nMOS: lorsque l'obturateur n'est pas chargé, le pont-levis est levé et les électrons ne peuvent pas traverser le canal. Lorsque nous abaissons le pont, nous formons une route sur la rivière et les voitures peuvent se déplacer librement. La même chose se produit dans le transistor. La charge de la grille forme un canal entre la source et le drain, permettant au courant de circuler.

Pour un contrôle précis de l'emplacement des différentes régions p et n sur le silicium, des fabricants comme Intel et TSMC utilisent un processus appelé

photolithographie . Il s'agit d'un processus en plusieurs étapes extrêmement complexe et les entreprises dépensent des milliards de dollars pour l'améliorer afin de créer des transistors plus petits, plus rapides et plus économes en énergie. Imaginez une imprimante ultra-précise que vous pouvez utiliser pour dessiner des motifs en silicium pour chaque zone.

Le processus de fabrication des transistors sur une puce commence par une tranche de silicium propre (substrat). Il est chauffé dans un four pour créer une fine couche de dioxyde de silicium à la surface de la plaque. Ensuite, un polymère photorésistif photosensible est appliqué au dioxyde de silicium. En éclairant le polymère avec une lumière de certaines fréquences, nous pouvons exposer le polymère dans les zones où nous voulons effectuer l'alliage. Il s'agit de l'étape de lithographie, et elle est similaire à la façon dont les imprimantes appliquent l'encre sur des zones spécifiques de la page, uniquement à plus petite échelle.

La plaque est gravée à l'acide fluorhydrique pour dissoudre la silice aux endroits où le polymère a été retiré. Ensuite, la résine photosensible est retirée, ne laissant que la couche d'oxyde en dessous. Désormais, des ions dopants peuvent être appliqués sur la plaque, qui ne sont implantés que dans des endroits où l'oxyde est absent.

Ce processus de masquage, de formation et de dopage est répété des dizaines de fois pour construire lentement chaque niveau d'éléments dans un semi-conducteur. Après avoir terminé le niveau de silicium de base, vous pouvez créer des composés métalliques sur le dessus qui connectent différents transistors. Un peu plus tard, nous parlerons davantage de ces composés et couches de métallisation.

Bien entendu, les fabricants de puces n'effectuent pas le processus de création de transistors sous un seul. Lors de la conception d'une nouvelle puce, ils génèrent des masques pour chaque étape du processus de fabrication. Ces masques contiennent les emplacements de chaque élément du milliard de transistors de la puce. Plusieurs puces sont regroupées et fabriquées ensemble sur la même puce.

Après avoir fabriqué la plaque, elle est coupée en cristaux individuels, qui sont placés

dans le cas. Chaque plaque peut contenir des centaines ou même plus de puces. Habituellement, plus la puce est puissante, plus le cristal sera grand et moins le fabricant pourra obtenir de puces de chaque plaque.

Vous pourriez penser que nous avons juste besoin de produire d'énormes puces super-puissantes avec des centaines de cœurs, mais c'est impossible. Actuellement, le facteur le plus sérieux entravant la création de puces toujours plus grandes est les défauts du processus de fabrication. Les puces modernes contiennent des milliards de transistors et si au moins une partie d'un transistor est cassée, alors la puce entière peut être jetée. À mesure que la taille des processeurs augmente, la probabilité de dysfonctionnement d'une puce augmente.

Les entreprises cachent soigneusement la productivité des processus de fabrication de leurs puces, mais elle peut être approximativement estimée à 70-90%. Les entreprises fabriquent généralement des puces avec une marge car elles savent que certaines pièces ne fonctionneront pas. Par exemple, Intel peut concevoir une puce à 8 cœurs, mais la vendre uniquement en tant que 6 cœurs, car elle s'attend à ce qu'un ou deux cœurs soient cassés. Les puces à défauts inhabituellement faibles sont généralement mises de côté pour la vente à un prix plus élevé. Ce processus est appelé

binning .

L'un des paramètres de commercialisation les plus importants associés à la fabrication de puces est la taille des éléments. Par exemple, Intel maîtrise un processus de 10 nanomètres, AMD utilise un processus de 7 nanomètres pour certains GPU et TSMC a commencé à travailler sur un processus de 5 nanomètres. Mais que signifient tous ces chiffres? Traditionnellement, la taille d'un élément est appelée la distance minimale entre le drain et la source du transistor. Dans le processus de développement technologique, nous avons appris à réduire les transistors afin que de plus en plus d'entre eux tiennent sur une seule puce. À mesure que les transistors diminuent, ils deviennent également de plus en plus rapides.

En regardant ces chiffres, il est important de se rappeler que certaines entreprises peuvent ne pas fonder la taille du processus de fabrication sur une distance standard, mais sur d'autres valeurs. Cela signifie que des processus de tailles différentes dans différentes entreprises peuvent en fait conduire à la création de transistors de même taille. D'un autre côté, tous les transistors d'un processus de fabrication séparé n'ont pas la même taille. Les concepteurs peuvent décider, dans un souci de compromis, de rendre certains transistors plus grands que d'autres. Un petit transistor sera plus rapide, car il faut moins de temps pour charger et décharger son obturateur. Cependant, les petits transistors ne peuvent contrôler qu'un très petit nombre de sorties. Si un élément logique gère quelque chose qui nécessite beaucoup d'énergie, par exemple, une broche de sortie, alors il faudra faire beaucoup plus. De tels transistors de sortie peuvent être de plusieurs ordres de grandeur plus importants que les transistors logiques internes.

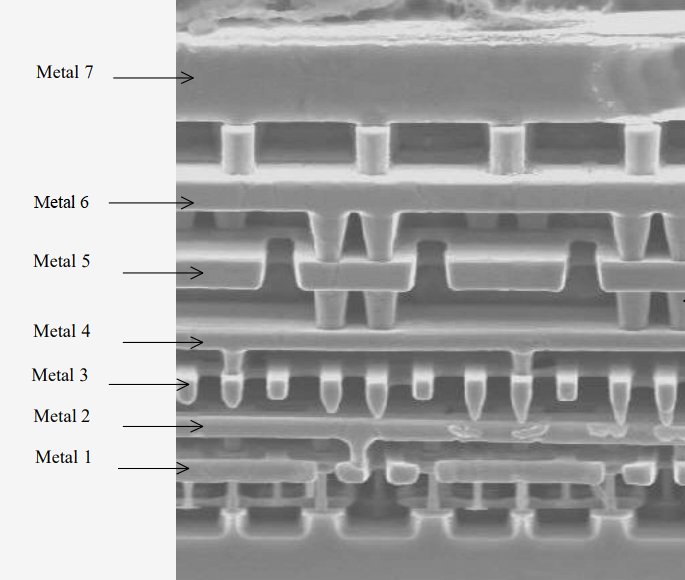

Cependant, la conception et la fabrication de transistors ne représentent que la moitié de la puce. Nous avons besoin de conducteurs pour tout connecter selon le schéma. Ces composés sont créés en utilisant des couches de placage au-dessus des transistors. Imaginez un carrefour à plusieurs niveaux avec des entrées, des sorties et un tas de routes qui se croisent. C'est exactement ce qui se passe à l'intérieur de la puce, mais à une échelle beaucoup plus petite. Différents processeurs ont différentes quantités de couches de liaison métalliques sur les transistors. Les transistors sont réduits et de plus en plus de couches de métallisation sont nécessaires pour acheminer tous les signaux. Il est rapporté que dans le futur, la technologie de traitement TMSC à 5 nanomètres utilisera 15 couches. Imaginez un carrefour vertical à 15 niveaux - cela vous donnera une idée de la complexité du routage à l'intérieur de la puce.

L'image du microscope ci-dessous montre une grille formée de sept couches de métallisation. Chaque calque est plat et lorsqu'il monte, les calques deviennent plus grands pour aider à réduire la traînée. Entre les couches, il y a de minuscules cylindres métalliques appelés cavaliers, qui sont utilisés pour passer à un niveau supérieur. En règle générale, chaque couche change de direction par rapport à la couche en dessous pour réduire la capacité indésirable. Des couches de métallisation impaires peuvent être utilisées pour créer des joints horizontaux et même des joints pour des joints verticaux.

Vous pouvez comprendre que la gestion de tous ces signaux et couches de métallisation devient très rapidement extrêmement complexe. Pour aider à résoudre ce problème, des programmes informatiques sont utilisés pour positionner et connecter automatiquement les transistors. Selon la complexité de la conception, les programmes peuvent même traduire les fonctions d'un code C de haut niveau jusqu'aux emplacements physiques de chaque conducteur et transistor. En règle générale, les concepteurs de puces permettent aux ordinateurs de générer automatiquement l'essentiel d'une conception, puis d'étudier et d'optimiser manuellement les pièces critiques individuelles.

Lorsque les entreprises souhaitent créer une nouvelle puce, elles commencent le processus de conception avec les cellules standard fournies par le fabricant de puces. Par exemple, Intel ou TSMC fournit aux concepteurs des éléments de base tels que des éléments logiques ou des cellules de mémoire. Les concepteurs peuvent combiner ces cellules standard dans n'importe quelle puce qu'ils souhaitent produire. Ensuite, ils sont envoyés à l'usine - un endroit où le silicium brut est converti en puces de travail - circuits électriques des transistors de puces et des couches de métallisation. Ces circuits se transforment en masques, qui sont utilisés dans le processus de fabrication décrit ci-dessus. Ensuite, nous verrons à quoi pourrait ressembler le processus de conception d'une puce extrêmement simple.

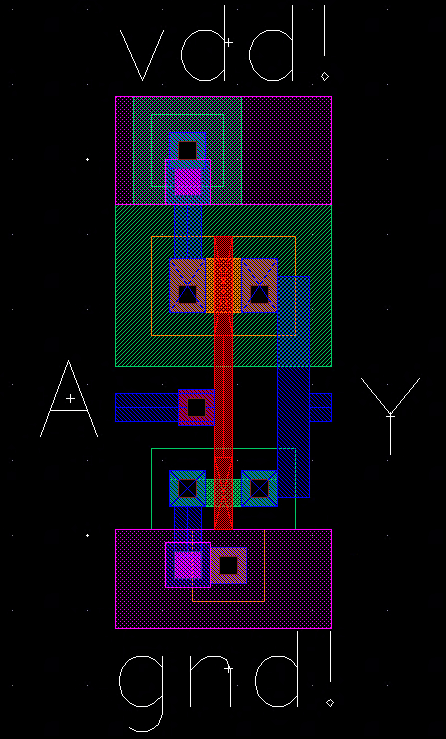

Nous voyons d'abord le circuit inverseur, qui est une cellule standard. Le rectangle vert ombré en haut est le transistor pMOS et le rectangle vert transparent en bas est le transistor nMOS. Le conducteur vertical rouge est une grille en polysilicium, les zones bleues sont la métallisation 1 et les zones violettes sont la métallisation 2. L'entrée A entre à gauche et la sortie Y sort à droite. Les connexions d'alimentation et de masse sont effectuées en haut et en bas sur la métallisation 2.

Combinant plusieurs éléments logiques, nous avons obtenu un module arithmétique simple à 1 bit. Cette conception peut ajouter, soustraire et effectuer des opérations logiques avec deux entrées 1 bit. Les conducteurs bleus ombrés qui montent sont des couches de métallisation 3. Des carrés légèrement plus grands aux extrémités des conducteurs sont des cavaliers reliant les deux couches.

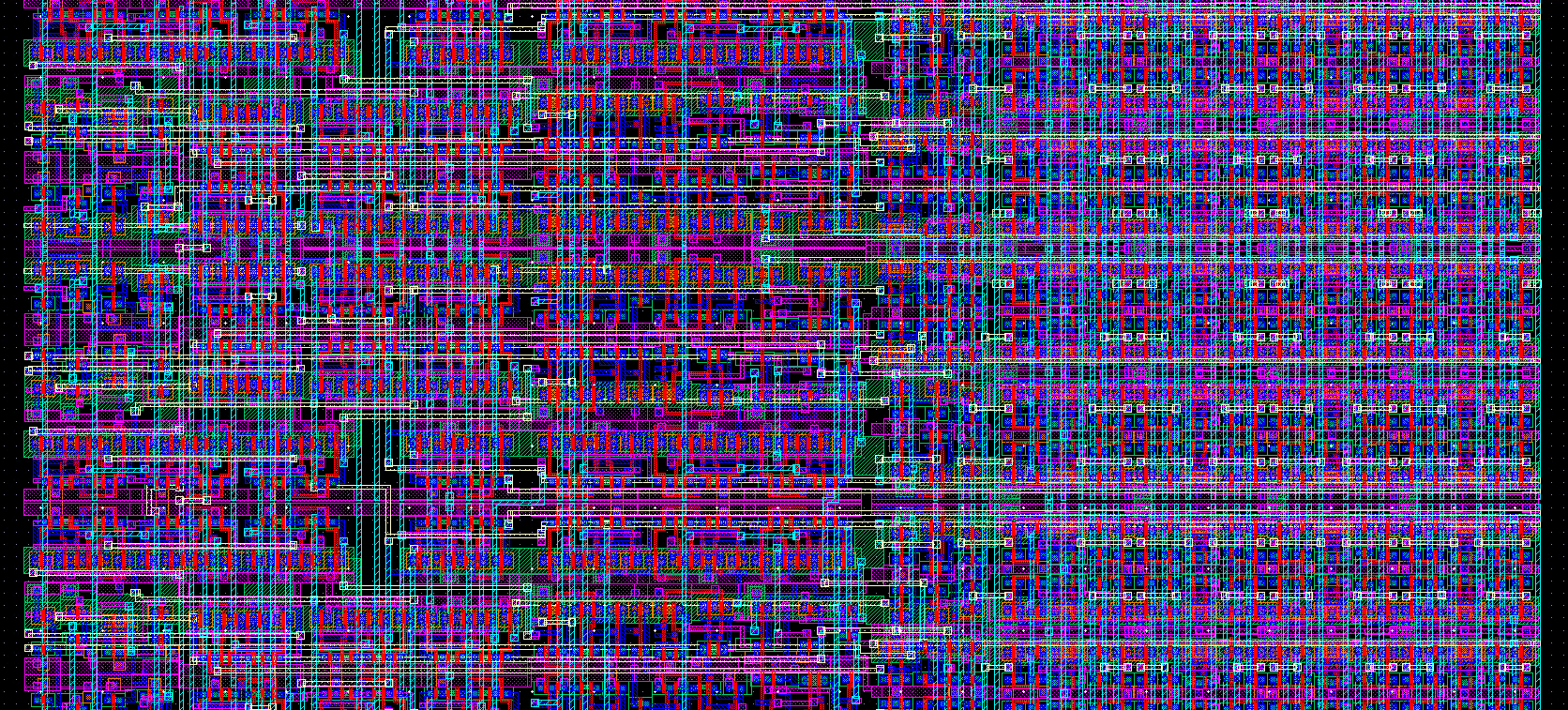

Enfin, combinant de nombreuses cellules et environ 2 000 transistors ensemble, nous avons obtenu un simple processeur 4 bits avec 8 octets de RAM sur quatre couches de métallisation. En voyant à quel point c'est compliqué, vous ne pouvez qu'imaginer à quel point il est difficile de concevoir un processeur 64 bits avec des mégaoctets de cache, plusieurs cœurs et plus de 20 étages de pipeline. Étant donné que les processeurs modernes hautes performances ont jusqu'à 5 à 10 milliards de transistors et une douzaine de couches de métallisation, il ne serait pas exagéré de dire qu'ils sont littéralement des millions de fois plus complexes que notre exemple.

Cela nous fait comprendre pourquoi le nouveau processeur est une technologie si chère et pourquoi AMD et Intel lancent de nouveaux produits depuis si longtemps. Pour qu'une nouvelle puce passe d'une planche à dessin au marché, il faut généralement de 3 à 5 ans. Cela signifie que les puces modernes les plus rapides sont basées sur des technologies qui ont déjà plusieurs années, et que pendant de nombreuses années, nous ne verrons pas de puces avec un niveau de technologie de fabrication moderne.

Dans le quatrième et dernier article de la série, nous reviendrons sur la sphère physique et examinerons les tendances actuelles de l'industrie. Que développent les chercheurs pour accélérer encore plus la prochaine génération d'ordinateurs?