J'ai décidé d'écrire cette note sur Habré en russe et en anglais afin de diffuser un lien vers celle-ci dans les forums et les groupes en anglais et en russe. Le texte russe n'est pas une traduction de l'anglais et vice versa - je viens d'écrire une note deux fois (je déteste traduire). Ceux qui veulent critiquer mon anglais sont immédiatement envoyés à la fin du post, où ils seront choqués par mon accent dans une vidéo de longues heures. Je vois mon accent non pas comme un bug, mais comme une fonctionnalité. Nous savons tous que de nombreux Américains trouvent, par exemple, un accent britannique nasopharyngé attrayant. Il est temps de donner le même statut à un accent russe sévère. Pour ce faire, autant de Russes que possible doivent faire des discours lors de divers événements internationaux. Notre mot de passe est «years mi Speak From May Hart».

Mais d'abord sur l'exposition.

Des millions de consommateurs de gadgets à travers le monde regardent le Consumer Electronics Show (CES), qui se déroule à Las Vegas en janvier. Ils, qui n'ont jamais su ce qu'est un déclencheur D, soutiennent que quatre gigahertz valent mieux que trois dans les derniers processeurs d'AMD et de Qualcomm. Mais il y a une exposition centrée non pas sur les consommateurs, mais sur les développeurs d'électronique. Cette exposition s'appelle la Design Automation Conference (DAC), et certaines années elle a également lieu à Las Vegas, mais pas en décembre, mais en juin.

Des millions d'amateurs de gadgets regardent chaque année le Consumer Electronics Show (CES) qui se déroule à Las Vegas en janvier. Ces gens, qui n'ont jamais appris la fonction d'une bascule D et comment le timing statique est calculé, discutent des fréquences gigahertz après avoir lu les derniers articles du magazine Wired qu'ils perçoivent comme une publication technique. Mais il y a une autre conférence, non pas pour les consommateurs, mais pour les créateurs d'électronique. Cette conférence s'appelle la Design Automation Conference (DAC) et elle a également lieu à Las Vegas, mais pas tous les ans, et non pas en janvier, mais en juin.

L'industrie de l'électronique de conception (EDA) fabrique des logiciels pour les concepteurs de matériel. EDA est contrôlée par trois grandes sociétés: Synopsys, Cadence et Mentor Graphics (qui fait désormais partie de Siemens). Synopsys et Cadence disposent d'un ensemble complet de produits, nécessaires pour concevoir et simuler une puce numérique à plusieurs niveaux. Le flux de conception, appelé RTL2GDSII, part de la spécification et du codage du comportement du cycle du circuit dans le langage de description matérielle (Verilog ou VHDL), procède à la synthèse de cette description dans un graphique d'éléments logiques (netlist), puis continue à placer la netlist dans un physique plan de la puce et routage des fils sur puce pour connecter les cellules standard, les blocs de construction des ASIC (Application-Specific Integrated Circuits).

Trois grandes entreprises dominent l'industrie de l'automatisation de la conception électronique: Synopsys, Cadence et Mentor Graphics (que Siemens a acheté il y a quelques années). Synopsys et Cadence ont créé un logiciel qui couvre l'intégralité de l'itinéraire de conception RTL2GDSII. J'ai brièvement décrit cette voie dans mon

précédent article du CAD il y a quatre ans:

Au cours des 25 à 30 dernières années, la conception du microcircuit est le plus souvent écrite dans le langage de description de l'équipement Verilog (en Europe et chez les militaires - VHDL), après quoi un programme spécial (synthèse logique) transforme la conception en un graphique de fils et de primitives logiques, un autre programme (analyse de synchronisation statique) indique au concepteur si elle s'inscrit dans le budget de vitesse, et le troisième programme (lieu et itinéraire) présente cette conception sur le site de la puce.

Quand la conception passe par toutes les étapes: codage sur un veril, débogage, vérification, synthèse, analyse temporelle statique, planning, place-n-route, extraction de parasites, etc. - il se trouve un fichier appelé GDSII, qui est envoyé à l'usine, et l'usine cuit des chips. Les usines les plus célèbres de ce type appartiennent à Taiwan Semiconductor Manufacturing Company ou TSMC.

John Sanguinetti, un gourou de Verilog depuis les années 1980. John était le fondateur d'une société appelée Chronologic Simulation qui, dans les années 1990, a créé VCS, un simulateur de code compilé Verilog. Ce simulateur est désormais une propriété de Synopsys. VCS est utilisé par la majorité des grandes sociétés électroniques. VCS a rapporté à Synopsys des milliards de dollars de revenus.

Aux côtés de la salle d'exposition se trouve John Sanguinetti, un des premiers gourous du verilogue des années 80 et fondateur de Chronologic Simulation. Cette société a donné au monde le simulateur rapide Verilog Compiled Code Simulator (VCS), qui est maintenant la propriété de Synopsys. Ce simulateur est utilisé par la plupart des grands développeurs de puces. VCS rapporte des milliards de dollars à Synopsys:

Mentor Graphics fait maintenant partie de Siemens, la troisième plus grande société EDA. Contrairement à Synopsys et Cadence, Mentor Graphics ne dispose pas d'une gamme complète d'outils RTL2GDSII. Ses deux sources de revenus les plus reconnues proviennent de Calibre, un ensemble d'outils de vérification de la conception physique, et de Veloce, un émulateur matériel. Calibre inclut par exemple un outil qui vérifie les règles de conception géométrique (largeur, espacement, enceinte) sur les "plans" finaux de la puce. Veloce utilise des puces de type FPGA qui

simulent très rapidement l'émulation de conceptions Verilog.

Mentor Graphics, troisième entreprise du secteur EDA, est devenue fin 2016 une filiale de Siemens. Contrairement à Synopsis et Keydens, Mentor ne dispose pas de toute la chaîne de programmes couvrant la route RTL2GDSII. Le logiciel Calibre, qui effectue des vérifications au stade final de la conception des micropuces, et l'émulateur Veloce (prononcé Velochi) constituent deux sources de revenus majeures pour Mentor. Un exemple de vérification dans Calibre est la distance minimale entre les pistes sur la puce

afin qu'il n'y ait pas d'effets d'antenne .

UPD: corrigé sur la base du commentaire de l' amartologie : L'antenne en est généralement une autre. Il se produit lorsqu'une piste devient si grande qu'elle commence à fonctionner comme une antenne, recevant un signal à la fréquence des oscillations du plasma pour la gravure pendant la production.Et l'émulateur Veloce utilise des ASIC en forme de FPGA pour

simuler rapidement

des émulations de circuits décrits au niveau logique, c'est-à-dire sur le veril.

En plus des projets Calibre et Veloce très rentables, Mentor a toujours eu un grand nombre d'autres projets, produits, services, formations et programmes éducatifs. Par exemple, Mentor cultive le domaine de la vérification fonctionnelle, une partie extrêmement importante du flux de travail de conception numérique.

En plus de projets très rentables tels que Calibre et Veloce, Mentor a de nombreux autres projets, produits, services, projets de recherche et programmes éducatifs. Par exemple, chez Mentor, ils sont engagés dans la vérification fonctionnelle, une partie critique du processus de production:

Un certain nombre de petites entreprises, dont Doulos, Willamette HDL et Sunburst Design, vendent des formations sur la vérification du matériel aux grandes et moyennes entreprises d'électronique. Une telle niche existe parce que les universités n'enseignent pas correctement l'art de la vérification fonctionnelle et n'adoptent pas de nouvelles technologies, telles que System Verilog, UVM, la vérification formelle utilisant des assertions simultanées, le stimulus portable, etc. dans leur programme depuis des décennies. Même Stanford ne l'a pas dans leur programme d'études pour autant que je sache de parler avec leurs diplômés.

La vérification fonctionnelle alimente plusieurs petites entreprises qui vendent des formations SystemVerilog et UVM à de grandes entreprises à des prix très élevés, comme quelques milliers de dollars par personne. Il s'agit notamment de Doulos, Willamette HDL, Sunburst Design et autres:

Une autre petite entreprise appelée Verific. Ils n'ont qu'une poignée de personnes, mais ils réussissent très bien dans leur créneau. Verific vend des analyseurs SystemVerilog adoptés par d'importantes sociétés EDA, grandes et petites.

Voici une autre petite entreprise, seulement quelques personnes, mais très prospère du genre appelée Verific. Elle vend l'analyseur Verilog, que de nombreuses sociétés EDA utilisent:

Le fondateur de Verific donne une interview à un site Web populaire de l'EDA appelé EDA Cafe. Il existe plusieurs autres sites Web populaires de l'EDA, notamment deepchip.com de John Cooley, mais je n'ai pas rencontré John Cooley au sol du CAD cette fois.

Voici le fondateur de Verific donnant une interview à EDA Cafe, un site Web populaire dans l'industrie:

Parlons maintenant du FPGA.

Parlons maintenant des FPGA, ils sont PPVM (ils vont me corriger maintenant), ils sont FPGA.

Ce que c'est, j'ai aussi brièvement décrit dans mon

précédent article du CAD il y a quatre ans:

Dans la version la plus simple, un FPGA est constitué d'une matrice de cellules homogènes, chacune pouvant être transformée en fonction à l'aide de multiplexeurs connectés aux bits de la mémoire de configuration. Une cellule peut devenir une porte ET avec quatre entrées et une sortie, une autre - un registre à un bit, etc. Nous chargeons une séquence de bits de la mémoire dans la mémoire de configuration - et le circuit électronique donné est formé dans le FPGA, qui peut être un processeur, un contrôleur d'affichage, etc.

Les FPGA / FPGA ne sont pas des processeurs; en «programmant» des FPGA (remplissant la mémoire de configuration des FPGA), vous créez un circuit électronique (matériel), tandis que lorsque vous programmez un processeur (matériel fixe), vous glissez une chaîne d'instructions de programme séquentielles écrites dedans (logiciel).

Xilinx et Altera, qui font désormais partie d'Intel, sont les deux plus grands producteurs de FPGA.

Les deux plus grandes sociétés qui produisent des FPGA sont Xilinx et Altera, qui font désormais partie d'Intel:

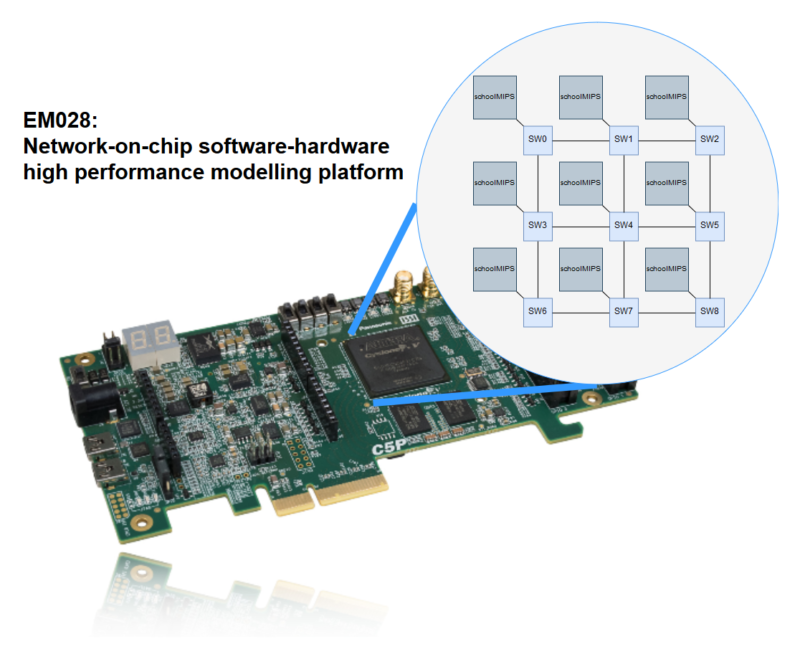

Cette semaine, Intel recueille des votes pour le premier tour du concours Innovate FPGA. L'une des entrées russes utilise un maillage de petits cœurs de processeur schoolMIPS.

schoolMIPS implémente un sous-ensemble de l'architecture MIPS. Il existe en plusieurs variantes, dont le cycle unique sans mémoire de données (la plus simple), une version avec interruptions, une version en pipeline, etc:

Soit dit en passant, Intel vote cette semaine au concours Innovate FPGA, auquel participent

également des équipes russes . L'un des projets est le

prototype de système de multitraitement basé sur NoC . Il s'agit d'un prototype de réseau sur une puce avec un grand nombre de nœuds basé sur des processeurs par Stanislav Zhelnio

sparf (basé sur le livre de Harris & Harris "Digital Synthesis and Computer Architecture")

https://github.com/MIPSfpga/schoolMIPS . Fait un étudiant de 4 ans au MIEM NRU HSE:

Le monde des FPGA n'est pas limité à Xilinx et Altera / Intel. Il existe plusieurs fournisseurs beaucoup plus petits, comme Lattice et Microsemi / Actel, et même de petites entreprises qui ne conçoivent pas les puces finales elles-mêmes octroient des licences de conception de blocs de cellules FPGA à des sociétés ASIC. Une application utile serait de créer un coprocesseur reconfigurable connecté à un noyau CPU haute fréquence fixe. Une autre application est la sécurité: certaines entreprises veulent cacher leurs secrets dans une logique reconfigurable plutôt que de montrer la disposition de leur logique fixe à un chercheur motivé au microscope électronique et beaucoup de temps.

Mais il y a moins d'acteurs dans le monde FPGA, par exemple, voici deux sociétés qui accordent une licence pour la conception de blocs FPGA qui peuvent être intégrés dans des circuits fixes multi-run pour leur donner de la flexibilité.

Chaque DAC a plusieurs fournisseurs de cartes FPGA. Pas les vendeurs de cartes étudiantes bon marché comme Digilent et Terasic, qui commencent à partir de 55 $, mais les cartes FPGA pour le prototypage ASIC qui peuvent coûter 30 000 $, 100 000 $ ou plus.

Le DAC est traditionnellement fréquenté par les fabricants de cartes FPGA. Ils ne vendent pas de cartes étudiantes bon marché pour 55 dollars, mais des cartes FPGA sérieuses pour 55 millions de dollars et plus. Leur client n'est pas un étudiant, mais une équipe de développement ASIC sévère qui utilise de grandes cartes pour le prototypage.

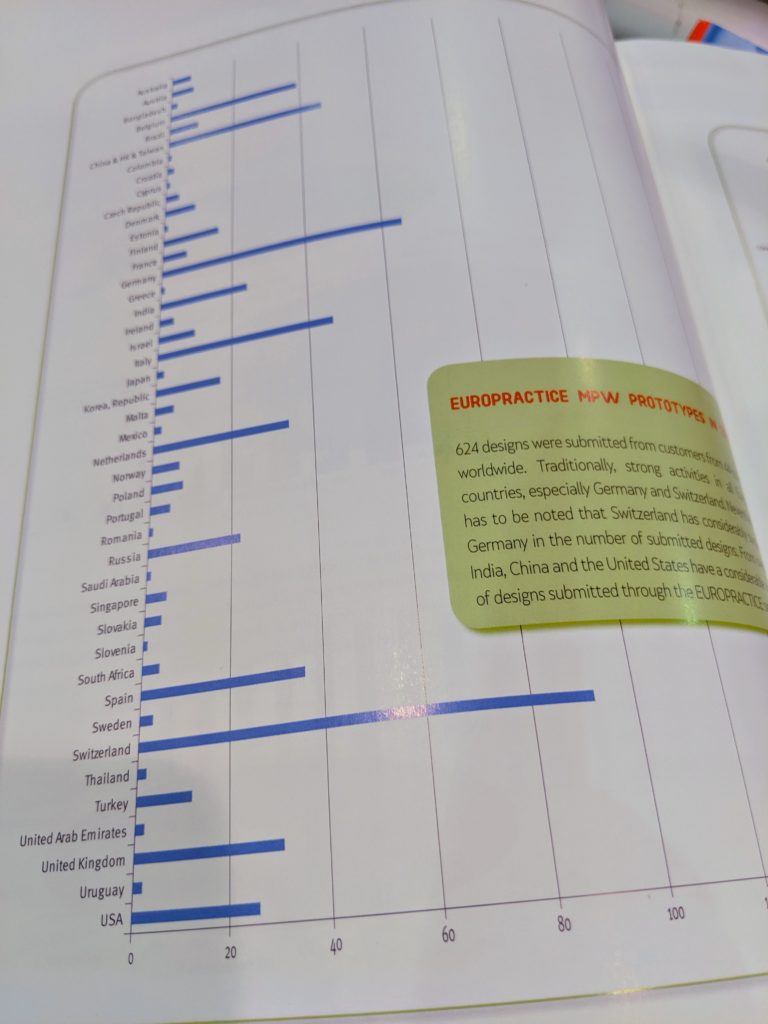

Et si un chercheur faisait une preuve de concept en utilisant FPGA et voulait maintenant fabriquer son propre ASIC? Une commande commerciale typique pour fabriquer un ASIC nécessite généralement le paiement initial de ~ 300 000 $ à ~ 3 000 000 $ selon la technologie du processus. Cependant, il existe des sociétés spécialisées, Europractice en Europe et MOSIS aux États-Unis, qui vendent des services de «navette» en petite quantité, ou des services de wafer multi-projets (MPW), à partir de seulement 3000 $ pour la technologie 180 nm ou seulement des dizaines de milliers de dollars pour quelque chose de moderne, comme 28nm.

Mais que se passe-t-il si un étudiant ou une entreprise exigeante veut fabriquer un véritable ASIC dans une usine et qu'il y a peu ou pas d'argent? Ou, sinon désolé, s'agit-il d'une puce de test ou d'un très petit lot? Pour ce faire, il existe en Amérique une société MOSIS, et en Europe - Europractice. Quelques milliers de dollars - et vous avez entre les mains la puce que vous avez conçue pour des technologies telles que 180 nanomètres. Quelques dizaines de milliers - et vous avez entre les mains votre puce sur une technologie plus récente, par exemple 28 nanomètres, comme le cinquième iPhone. Je note que pour la production commerciale de masse, le paiement initial à l'usine va de centaines de milliers de dollars pour les anciennes technologies à deux ou trois millions pour les nouvelles.

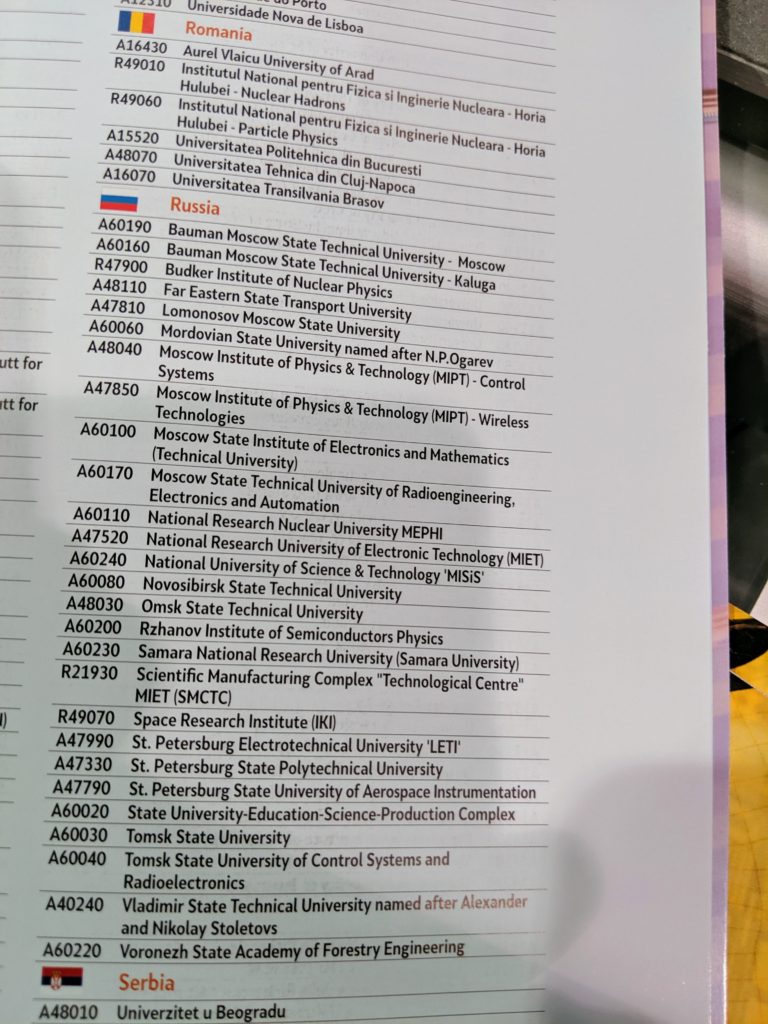

Il est intéressant de noter qu'Europractice a des clients en Russie, même à Omsk. Admettez qui conçoit les ASIC à Omsk.

Europractice a un certain nombre de sociétés russes, y compris quelqu'un à Omsk:

Il y a des entreprises avec des modèles commerciaux qui me sont quelque peu mystérieux. Par exemple, je ne comprends pas comment cette société ci-dessous peut survivre sur un plugin de niche Eclipse. Je suppose qu'ils obtiennent la plupart des revenus en vendant certains services de consultation.

Il y a des entreprises dont je ne comprends pas comment elles gagnent. Par exemple, celui-ci vend un plugin Eclipse très niche. Certes, ils ne vivent pas de lui, mais d'une sorte de consultation.

Une autre entreprise de niche au modèle commercial non évident. Ils traduisent une description des registres visibles par logiciel en logique de colle Verilog et autres fichiers d'interface. Je suppose que cette entreprise peut avoir un gros client de type Cisco qui s'est accroché à leur technologie depuis longtemps et les paie depuis.

Une autre entreprise de niche avec un modèle commercial non évident. Ils traduisent la description des registres disponibles pour le programmeur en fichiers verilog et interface. Ils ont probablement un client majeur tel que Cisco, qui, il y a plusieurs années, est tombé amoureux de leur outil et a depuis payé depuis qu'il est décevant d'embaucher un client pour gérer son ingénieur.

Un gentleman mélancolique de Huawei a décrit leurs réalisations en matière de puces réseau. Huawei est évidemment dépendant des outils américains EDA, encore plus que du marché Android et des cœurs CPU ARM. Ils représentent beaucoup d'argent et le nombre d'experts techniques nécessaires pour développer un équivalent du compilateur Synopsys IC est beaucoup plus important, à mon avis, que les ressources nécessaires pour concevoir un concurrent haut de gamme pour les cœurs ARM.

Un représentant de Huawei s'est également assis à l'exposition avec une expression de tristesse vive sur son visage. Je note que si le gouvernement américain force les sociétés américaines EDA à interdire les Chinois, la situation chinoise sera bien pire qu'elle ne l'est maintenant, car il est techniquement plus difficile de cloner Synopsys IC Compiler que les cœurs de processeur ARM et Android Market.

Depuis 1998, chaque DAC comptait au moins une entreprise développant un autre compilateur C-to-Verilog. En 1998, c'était

ma propre startup . Cette année, c'est quelqu'un d'autre:

Depuis 1998, il y a au moins une entreprise sur DAC qui compile C dans Verilog. En 1998, une telle entreprise était ma propre startup. Cette année, quelqu'un d'autre:

Ce monsieur gagne sa vie en vendant des solutions contre le soi-disant "Zakladki" (un terme russe, un pluriel de "Zakladka"). Je lui ai expliqué le sens du terme et il a convenu que c'est ce qu'il vend.

Voici un compagnon qui crée des signets d'analyseurs vivants dans les processeurs:

J'ai amené au DAC ma fille étudiante afin qu'elle puisse voir comment papa gagne sa vie:

J'ai amené ma fille à Las Vegas pour qu'elle puisse voir comment les gens gagnent de l'argent dans le dur monde industriel de l'industrie électronique et j'ai réalisé que les dollars de papa ne poussaient pas sur les arbres:

Fête après l'exposition:

A la fête après l'exposition:

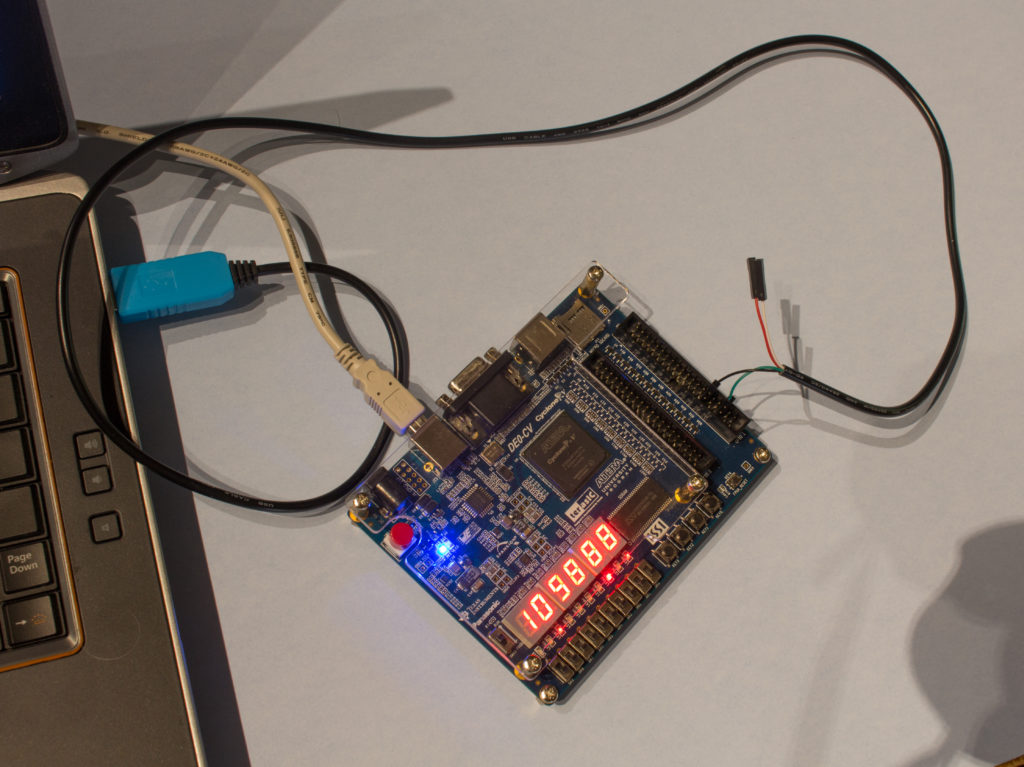

Après l'exposition, j'ai fait la journée des développeurs ouverts MIPS avec mes collègues de Wave Comnputing. Nous avons obtenu un certain nombre de personnes de certaines des entreprises ci-dessus + mes amis russes de

VivEng , un service de conception de signaux mixtes de la Silicon Valley en Californie, qui avait également des clients à Zelenograd, une Silicon Valley russe. Nous avons d'abord fait une

présentation , puis les participants ont fait quelques exercices sur les cartes Digilent Nexys4 DDR et Terasic DE10-Lite FPGA.

Ensuite, avec mes collègues, j'ai dirigé le séminaire MIPS Open. Des camarades de certaines des entreprises décrites y ont assisté, notamment ceux qui octroient des licences aux outils FPGA et EDA intégrés, vendent des services de production, dispensent une formation à la vérification et fabriquent également des puces en tant que telles. Et aussi mes anciens amis de la société russe

VivEng . Mes collègues et moi avons montré

ces diapositives , après quoi les participants ont essayé des exemples sur les FPGA Digilent Nexys4 DDR et Terasic DE10-Lite.

Pour répéter les résultats, vous pouvez télécharger et combiner deux packages:

Si vous souhaitez reproduire les résultats, vous pouvez procéder comme suit:

- Accédez à https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide .

- Téléchargez le package standard MIPSfpga 2.0.

- Accédez à https://github.com/MIPSfpga/mipsfpga-plus .

- git clone github.com/MIPSfpga/mipsfpga-plus.git

- Copiez les fichiers RTL principaux du package MIPS Open FPGA dans le sous-répertoire core du package MIPSfpga + - voir les instructions dans https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core

Intel FPGA Quartus Prime Lite Edition ou Xilinx Vivado, ainsi que la chaîne d'outils Codescape GCC Bare Metal doivent être installés sur votre ordinateur. Après cela, vous pouvez suivre les instructions des diapositives:

Vous devez avoir Intel FPGA Quartus Prime Lite Edition ou Xilinx Vivado installé sur votre système, ainsi que Codescape GCC Bare Metal Toolchain. Après cela, vous pouvez suivre les instructions des diapositives:

- cd your_git_directory / boards / board_directory (par exemple de10_lite ou nexys4_ddr)

- faire toute la charge

- Appuyez sur reset (ou KEY 0 sur certaines cartes) pour réinitialiser le processeur.

- Le programme codé en dur par défaut devrait commencer à fonctionner.

- cd your_git_directory / programmes / 00_counter (ou autre programme)

- faire le programme enregistrer uart

- Si l'ordinateur utilise une connexion série autre que ttyUSB0 (par défaut), alors:

- rendre le programme enregistré uart UART = 1 (ou 2, 3, etc.)

- Le programme téléchargé via USB-vers-UART est maintenant en cours d'exécution.

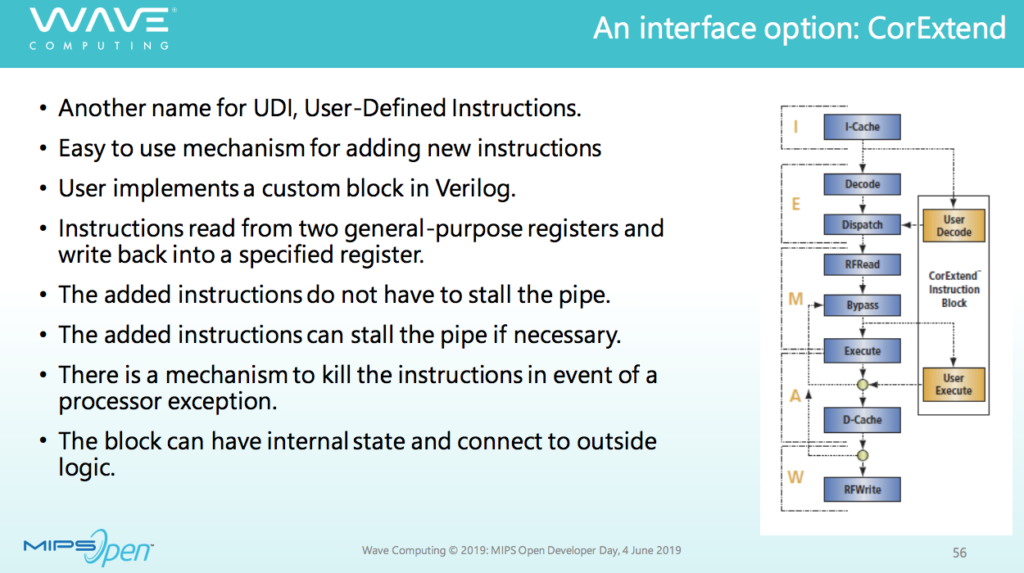

Dans la présentation, j'ai montré comment intégrer un bloc dans le processeur qui décode et exécute des instructions supplémentaires au système principal de commandes qui peuvent être déterminées par le concepteur du système sur une puce. Le bloc peut être synthétisé et devenir une partie du microcircuit ou être configuré dans le FPGA / FPGA.

Des instructions supplémentaires se déplacent le long du pipeline du processeur avec les principales. Ils reçoivent des données de registres généraux visibles par le programmeur et peuvent renvoyer le résultat au registre. Ces instructions peuvent également enregistrer un état dans le coprocesseur. Ils peuvent être supprimés par des exceptions si une exception se produit, par exemple, dans le pipeline suivant cette instruction:

La présentation contient une explication détaillée, comment ajouter des instructions de processeurs définies par l'utilisateur au cœur du processeur MIPS microAptiv UP et le synthétiser avec une carte SoC pour FPGA simple:

Extrait de code matériel Verilog à partir de l'exemple de texte. Ce code implémente, au niveau de transfert de registre (RTL), une instruction spécialisée pour le calcul d'un réseau neuronal convolutionnel:

Un fragment d'un module CorExtend personnalisé qui implémente une instruction définie par l'utilisateur (UDI) pour un cas particulier de calcul de réseau neuronal:

Demain, je m'envole pour la Russie pour aider avec un autre séminaire, pas pour les professionnels de l'électronique et de l'EDA, mais pour les enfants intéressés à explorer des carrières dans la conception microélectronique numérique. Pour ce voyage, j'ai créé un simple vidéoprocesseur 2D intégré au noyau MIPS Open FPGA, ainsi qu'un exemple de jeu uniquement matériel (sans CPU ni logiciel) pour VGA. Les enfants aiment les jeux et je vais utiliser la conception de jeux pour leur enseigner les bases de la méthodologie RTL:

Et lundi prochain

, le 8 juillet, j'enseignerai les bases du développement de circuits numériques pour les écoliers de Zelenograd .

Pour lui, j'ai écrit des exemples d'implémentation de graphiques sprite simples sur FPGA. Un circuit synthétisé à partir de Verilogue dessine des sprites sur un écran VGA.

Voici un exemple de travail dans un matériel propre (

codes sources sur github ). Une variante du combat naval, où un satellite torpille rouge chasse une croix bleue ennemie:

Et voici un exemple d'une combinaison de matériel et de logiciel - un hommage des sprites.

Partie matérielle et

partie logicielle :

Oui, et j'ai promis de prononcer mes discours à Las Vegas. En voici une pièce:

Vue sur le Strip de Las Vegas quand il fait nuit mais il n'y a pas encore de foule:

Et la vue sur la rue sur le Strip, quand c'est déjà le soir, mais il n'y a pas encore de foule:

Pendant deux jours à Las Vegas, je n'ai pas eu la chance de jouer, alors j'ai joué avec 1 $ lorsque notre avion de retour à San Jose embarquait à l'aéroport de Las Vegas:

Pendant tout ce temps, je n'ai jamais joué à Las Vegas, car j'ai fait le tour de l'exposition et parlé de sujets électroniques, puis j'ai organisé un séminaire. Mais en montant dans l'avion, j'ai quand même noté, perdu un dollar: