Les processus de fabrication intermédiaires, différents types de transistors et de nombreuses autres options ajoutent de l'incertitude au processus de fabrication de l'électronique.

Les fabricants d'électronique se préparent pour la prochaine vague de processus de fabrication de pointe, mais leurs clients seront confus avec un tas d'options déroutantes - que ce soit pour développer des puces en utilisant la technologie de processus de 5 nm, attendre 3 nm ou choisir quelque chose entre les deux.

Le chemin vers 5 nm est bien défini, contrairement à 3 nm. Après cela, le paysage devient confus alors que les usines ajoutent des processus de fabrication intermédiaires, tels que 6 nm et 4 nm. Le passage à l'un de ces processus techniques est très coûteux et les avantages ne sont pas toujours évidents.

Une autre source de préoccupation est la diminution de la base manufacturière. Dans le cas des procédés techniques les plus avancés, le choix des fabricants est restreint. Il y avait plusieurs grands fabricants dans l'industrie, mais au fil du temps, ce domaine s'est rétréci en raison d'une forte augmentation des coûts et d'une diminution de la base d'utilisateurs. En général, moins il y a de fabricants, moins il y a d'options de technologie et de prix.

Aujourd'hui, Samsung et TSMC sont les

deux seuls fabricants à utiliser des processus technologiques de 7 nm ou moins, bien que cela puisse changer. Intel et la société chinoise SMIC développent des processus de fabrication avancés. Intel, qui n'est pas le plus grand acteur dans le domaine de la production commerciale, rencontre des problèmes avec le développement de la technologie des procédés 10 nm. Et il n'est pas clair si SMIC parviendra à distribuer 7 nm, car ce sujet est encore au stade de la recherche et du développement (la même chose se produit avec Intel avec la technologie de processus 10 nm).

En ce qui concerne les processus de fabrication plus avancés, Samsung et TSMC travaillent avec 7 nm en utilisant des transistors finFET, et les deux fabricants vont continuer à 5 nm. Contrairement aux transistors plans traditionnels, les finFET sont des structures tridimensionnelles avec de meilleures performances et moins de fuites.

Ensuite, à 3 nm, Samsung passera de finFET à la nouvelle architecture de transistors FET nanosheet, qui est un développement de la technologie finFET. TSMC n'a pas encore dévoilé ses plans pour 3 nm, laissant de nombreux clients dans les limbes. TSMC, selon les sources, pèse une variété d'options, y compris les nanocouches, les nanofils et les finFET forcés. Intel, TSMC et d'autres travaillent également sur de nouvelles formes d'emballages avancés comme options possibles pour la réduction d'échelle.

Cependant, à 3 nm, la taille de la technologie des transistors peut aller dans différentes directions. finFET peut toujours jouer, mais cette technologie a besoin de quelques percées. Apparemment, l'industrie devra se préparer à la transition vers la nouvelle architecture de la technologie de processus 3 nm et la prochaine technologie de processus intermédiaire à 2 nm, à en juger par les plans de développement d'une organisation travaillant dans ce domaine.

"Le 5 nm est encore finFET", a déclaré Naoto Horiguchi, directeur de programme chez Imec. - Disons qu'à 3 nm, nous entrerons dans une période de transition de finFET à d'autres architectures. Nous pensons que ce seront des nanocouches. »

Les transistors FET nanocouches sont liés à l'architecture des transistors à grille tout autour (GAA). Et ce n'est pas la seule option. «L'industrie est très conservatrice. Ses participants vont essayer de tout presser, du finFET à la limite », a déclaré Horiguchi. - Au processus de fabrication de 3 nm, nous avons la possibilité d'utiliser finFET. Mais nous devrons faire plusieurs innovations finFET, l'améliorer en général. »

Les fabricants de puces resteront-ils sur la technologie de traitement 7 nm, migreront-ils vers 5 nm, 3 nm ou vers l'intermédiaire? 7 nm offre des performances suffisantes pour presque toutes les applications, ce processus durera donc longtemps. Dehors, il existe plusieurs options hautes performances, et elles coûtent toutes plus cher. Et nous verrons si ces technologies ont le temps d'apparaître à temps.

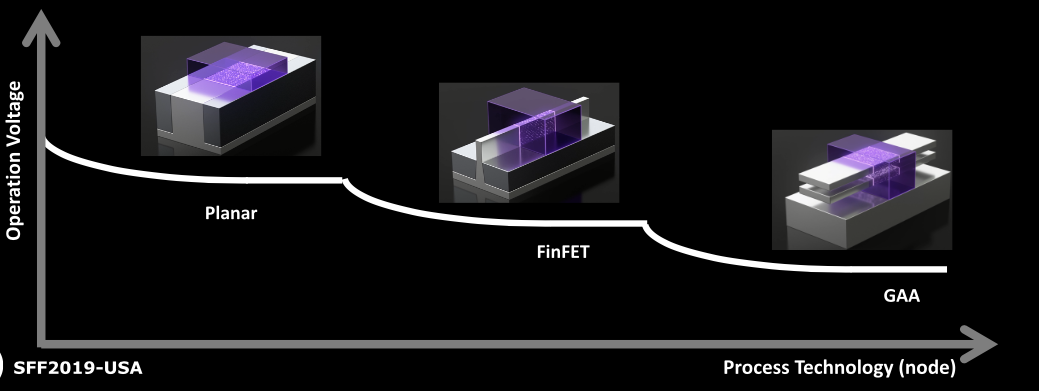

La tension de fonctionnement de divers processus de fabrication est des transistors plans, des finFET et des nanocouches FET.

La tension de fonctionnement de divers processus de fabrication est des transistors plans, des finFET et des nanocouches FET.Ruine de production

La puce se compose de nombreux transistors servant d'interrupteurs. Pendant de nombreuses décennies, les progrès des circuits intégrés ont été conformes à la loi de Moore, selon laquelle la densité des transistors sur un appareil double en 18 à 24 mois.

Dans un rythme similaire, les fabricants ont introduit de nouveaux procédés technologiques avec une densité de transistors plus élevée, ce qui a permis à l'industrie de réduire le coût des puces en termes de nombre de transistors. À chaque processus de fabrication, les fabricants ont mis à l'échelle les spécifications des transistors 0,7 fois, ce qui permet à l'industrie d'augmenter sa productivité de 40% avec la même consommation d'énergie et une réduction de surface double.

L'industrie des circuits intégrés a suivi cette formule et a prospéré. Depuis les années 1980, il a ouvert la voie à des PC rapides à prix réduits.

En 2001, il y avait déjà au moins 18 fabricants avec des usines où ils pouvaient fabriquer des puces à 130 nm, ce qui à l'époque était un processus technique avancé, selon IBS. Ensuite, plusieurs autres nouveaux fabricants sont apparus, fabriquant des puces sur mesure dans les usines d'autres personnes. De plus, la fabrication de puces était pratiquée pour les laboratoires qui les avaient développées, mais n'avaient pas leur propre production.

À la fin de la décennie, le coût de production et les processus de fabrication ont augmenté. Incapables de faire face à l'augmentation des prix, de nombreux fabricants de puces sont passés au modèle fab lite. Ils ont produit des puces à la maison et le reste a été externalisé.

Au fil du temps, moins de fabricants de puces ont fabriqué des appareils avancés dans leurs propres installations. Certains se sont complètement débarrassés de la production ou ont quitté cette entreprise.

Cependant, dans les années 2000, un modèle économique d'ateliers de silicium est apparu. Les ateliers sont restés à la traîne d'Intel et d'autres sociétés technologiques, mais ont permis aux sociétés de conception d'accéder à divers processus.

Le prochain changement majeur s'est produit au stade 20 nm, lorsque les transistors planaires traditionnels ont heurté un mur et ont rencontré

un effet de canal court . En réponse, Intel est passé à la technologie de transistor de nouvelle génération, finFET, à 22 nm en 2011. Les ateliers sont passés au finFET à 16/14 nm.

FinFET présente plusieurs avantages par rapport aux transistors plans. «Dans ce schéma, le transistor entier s'étend verticalement de sorte que le canal s'élève au-dessus du substrat, et la valve s'enroule autour de trois côtés de l'ailette. La zone de contact accrue de la vanne permet un meilleur contrôle du courant de fuite », écrivent Matt Kogorno et Toshihiko Miyashita d'Applied Materials. Kogorno est le directeur de la gestion globale des produits et Miyashita est le technologue en chef.

FinFET est également des dispositifs plus complexes, il est plus difficile de les produire et de les mettre à l'échelle pour chaque processus technique ultérieur. En conséquence, le coût de la R&D est monté au ciel. Alors maintenant, le rythme d'un changement de processus à part entière est passé de 18 mois à 2,5 ans ou plus.

Les prix des circuits intégrés continuent également d'augmenter. Le coût de développement d'un appareil planaire à 28 nm varie de 10 à 35 millions de dollars, selon Gartner. À titre de comparaison, le coût de conception d'un système à puce unique (SoC) à 7 nm varie de 120 millions de dollars à 420 millions de dollars.

«Le coût de développement dépend fortement de la complexité du SoC», a déclaré Samuel Wen, analyste chez Gartner. - Les deux tiers vont au développement de la puce. Le reste est le développement de sous-marins, le coût des masques et l'amélioration de la production. Au fil du temps, le coût de la conception diminue également. »

Cependant, les tendances des prix ont changé le paysage du monde des circuits intégrés. Au fil du temps, moins d'entreprises peuvent se permettre de payer pour la conception de puces pour les processus de fabrication les plus avancés. Beaucoup d'entre eux comptent sur des ateliers pour les problèmes de production.

Une diminution du nombre de clients et une augmentation du coût de production ont influencé le paysage des ateliers de production de puces avancées. Par exemple, il reste cinq fabricants / ateliers sur le marché des 16/14 nm: GlobalFoundries, Intel, Samsung, TSMC et UMC. SMIC travaille également avec finFET sur une technologie de processus de 14 nm.

Et à 7 nm, une autre transition s'est produite. Les processus technologiques et les coûts de production ont continué de croître et le retour sur investissement était déjà en cause. En conséquence, GlobalFoundries et UMC ont cessé l'année dernière d'essayer de développer une technologie de traitement à 7 nm. Les deux sociétés continuent d'opérer sur le marché des 16/14 nm.

En essayant de se développer davantage, Samsung et TSMC se précipitent à pleine vitesse jusqu'au virage de 7 nm et au-delà. Après plusieurs retards, Intel prévoit de lancer la production à 10 nm à la mi-2019 et à 7 g - d'ici 2021. Le SMIC, quant à lui, ne promet aucun délai.

Mais tous les clients des ateliers n'ont pas besoin de processus de fabrication avancés. Il existe un marché florissant pour les puces de 28 nm. "Tout dépend des caractéristiques du produit", a expliqué Ven of Gartner. - Certains produits nécessitent des performances maximales. Les développeurs peuvent toujours utiliser des processus techniques obsolètes. Et les puces pour les applications qui ne nécessitent pas de hautes performances peuvent vivre sur les processus de fabrication N-1 et N-2. »

D'autres le font écho. «Combien d'entreprises peuvent se permettre le dernier silicium aujourd'hui d'un point de vue économique? Leur nombre diminue. Dans les marchés exigeant des performances extrêmement élevées, un tel besoin sera toujours. Mais dans la chaîne d'approvisionnement, en termes de volumes, une rupture se forme au milieu. Les clients les plus exigeants ont besoin de processus technologiques à 7, 5 et éventuellement un jour à 3 nm. Mais tout le monde a un peu ralenti », a déclaré Walter Eun, vice-président de la gestion des affaires chez UMC.

Mais dans certains cas, les puces les plus avancées sont nécessaires - ce sont les serveurs et les smartphones. Il y a aussi une mer de nouvelles startups liées aux puces IA. De nombreuses entreprises conçoivent des puces pour l'apprentissage automatique et l'apprentissage en profondeur.

«Personne ne prétend que la nécessité de compter quelque chose 10 fois plus vite qu'aujourd'hui sera toujours commercialement utile et compétitive, même sur les marchés non techniques. Toutes ces réalisations uniques de la technologie d'apprentissage en profondeur en sont la preuve. Il n'y a littéralement pas de fin aux demandes de puissance informatique toujours croissante », a déclaré Aki Fujimura, directeur de D2S.

«Les demandes de puissance de calcul ont connu plusieurs changements majeurs - au début, c'était le GPU, et plus tard - l'apprentissage en profondeur», a déclaré Fujimura. - L'apprentissage en profondeur est une technologie massive pour trouver des modèles appropriés, et la formation des réseaux de neurones est la tâche d'une optimisation cohérente. Maintenant que le monde a mis au point un mécanisme pour traiter une énorme quantité de données et les transformer en informations utiles sous la forme d'un programme capable de conclusions logiques, le nombre de calculs nécessaires croît avec la quantité de données disponibles. Et comme la quantité de données dans tous les domaines augmente de façon exponentielle, les besoins en puissance de calcul sont garantis de croître de manière significative, au moins dans le domaine du deep learning. »

Il n'est pas clair si les puces AI nécessitent des processus techniques de 5 nm ou plus, mais il y a certainement des exigences pour une augmentation de la puissance de calcul. Mais la migration vers ces processus technologiques ne devient pas un processus plus facile ou moins cher.

5 nm vs 3 nm

Entre-temps, au début de 2018, TSMC a franchi une nouvelle étape, devenant le premier fabricant au monde à utiliser la technologie de traitement à 7 nm. Samsung a ensuite rejoint la course des 7 nm. Le processus de fabrication de puces à 7 nm est principalement basé sur finFET et consiste à fabriquer des puces avec une étape de grille de 56 à 57 nm et une étape minimale de placement des conducteurs métalliques [pas métallique] à 40 nm, selon les informations d'IC Knowledge et de TEL.

Dans la première version de 7 nm, TSMC a utilisé une

lithographie par immersion à 193 nm et des motifs multiples. Cette année, TSMC promet de publier une nouvelle version de 7 nm en utilisant la lithographie ultraviolette extrême (EUV). EUV simplifie les étapes du processus, mais c'est une technologie coûteuse et elle a son propre ensemble de difficultés.

TSMC prépare sa nouvelle technologie de traitement à 5 nm pour une sortie au premier semestre 2020. La nouvelle technologie de TSMC à 5 nm sera 15% plus rapide que 7 nm et consommera 30% d'énergie en moins. La deuxième version de la technologie de traitement à 5 nm, qui sortira l'année prochaine, sera 7% plus rapide. Les deux versions utiliseront EUV.

TSMC gagne déjà des commandes à 5 nm. «De grosses commandes sont attendues d'Apple, HiSilicon et Qualcomm», a déclaré Handel Jones, directeur d'IBS. «Le volume de substrats sera de 40 000 à 60 000 par mois d'ici le quatrième trimestre 2020.»

La vitesse de transition à 5 nm pour TSMC est inférieure à 7 nm. Premièrement, 5 nm est un processus complètement nouveau, avec des outils et des brevets EDA mis à jour. De plus, c'est plus cher. En moyenne, le coût de développement d'un appareil à 5 nm varie de 210 millions de dollars à 680 millions de dollars, selon Gartner.

Certains fabricants de puces veulent s'éloigner de 7 nm sans dépenser autant d'argent que 5 nm. Par conséquent, TSMC a récemment introduit une nouvelle technologie de processus de 6 nm, qui est moins chère, mais avec quelques compromis.

"Les chiffres N6 et N5 ne semblent pas être différents, mais en fait l'écart est grand", a déclaré S. S. Wei, directeur de TSMC lors de la dernière réunion. - A N5, par rapport à N7, la densité logique est augmentée de 80%. N6 contre N7 seulement 18%. Comme vous pouvez le voir, il existe une grande différence entre la densité logique et l'efficacité des transistors. En conséquence, la consommation d'énergie globale de la puce N5 est plus faible. Le passage au N5 présente de nombreux avantages. Mais le N5 est un processus technique à part entière, et il faut du temps aux clients pour développer de nouveaux produits. La beauté de N6 est que s'ils ont déjà un projet sous N7, ils devront consacrer très peu d'efforts. Ils peuvent passer à N6 et bénéficier de certains avantages. Et selon les caractéristiques du produit et du marché, les clients décideront quoi faire. »

Pendant ce temps, Samsung a déployé 5 nm, qui apparaîtra au premier semestre 2020. Par rapport à 7 nm, la nouvelle technologie de processus de 5 nm de Samsung à finFET offre jusqu'à 25% de compactage logique et 20% de consommation d'énergie en moins, ou 10% de vitesse en plus.

Samsung a également introduit une nouvelle technologie de traitement à 6 nm, offrant aux clients une autre option. «Le 6 nm présente l'avantage de l'évolutivité avec le 7 nm et la réutilisation de la propriété intellectuelle», a déclaré Ryan Lee, vice-président du marketing pour les ateliers de Samsung. Et Samsung prévoit déjà le développement de la technologie de processus 4 nm finFET. Jusqu'à présent, il n'y a pratiquement aucune information ouverte sur cette technologie.

Après 5 nm, un certain nombre de processus de fabrication à part entière coûtent 3 nm. Mais 3 nm n'est pas pour les mauviettes. Selon IBS, le coût de développement d'un appareil pour la technologie des procédés 3 nm varie de 500 millions à 1,5 milliard de dollars. Le coût du processus de développement varie de 4 à 5 milliards de dollars, et la production - de 15 à 20 dollars. "Le coût des transistors 3 nm devrait être de 20-25% supérieur à 5 nm de la même disponibilité", a déclaré Jones d'IBS. «Nous pouvons nous attendre à une augmentation de 15% de l'efficacité et à une réduction de 25% de la consommation d'énergie par rapport au 5 nm finFET.»

Samsung est la seule entreprise à annoncer son intention de développer une technologie de traitement à 3 nm. Pour cela, l'atelier passera à l'architecture des transistors circulaires, nanocouches. TSMC n'a pas encore dévoilé ses plans, c'est pourquoi certains pensent que l'entreprise est à la traîne. "À 3 nm, Samsung est très susceptible d'entrer dans la production en volume en 2021", a déclaré Jones. «TSMC accélère le développement en essayant de suivre Samsung.»

À 3 nm, TSMC examine les FET nanocouches, les FET nanofils et même les finFET. L'une des façons d'étendre la technologie finFET consiste à utiliser des matériaux à haute mobilité dans les canaux, à savoir l'Allemagne. Les dispositifs finFET d'aujourd'hui utilisent du silicium ou du silicium-germanium (SiGe) dans les canaux. En augmentant le mélange de germanium, vous pouvez augmenter la mobilité du canal - c'est-à-dire la vitesse de passage des électrons à travers l'appareil. Et ici, le problème est la gestion des défauts.

L'extension de la technologie finFET est logique. finFET à 3 nm fournit un chemin de transition à partir de 5 nm. Cependant, il y a des problèmes. Théoriquement, la technologie finFET se retrouve dans une impasse lorsque la largeur des ailettes atteint 5 nm, ce qui est proche de l'état actuel. "Aujourd'hui, nous utilisons deux ailettes pour NMOS et trois pour PMOS dans une cellule standard", a déclaré Horiguchi d'Imec. - L'un des aspects importants de 3 nm est que nous devons passer à une architecture à une seule ailette pour les conceptions de cellules standard. Une seule nageoire devrait fonctionner assez bien. Pour étendre la technologie finFET à N3, nous avons besoin d'une technologie spéciale pour améliorer la puissance d'une seule ailette et réduire les phénomènes parasites d'arrière-plan. »

En plus de la grande mobilité de finFET, l'option suivante est GAA. En 2017, Samsung a introduit le FET Multi Bridge Channel (MBCFET) pour 3 nm. MBCFET - FET nanocouche. L'essai MBCFET de Samsung sera disponible en 2020.

Les puces nanocouches ont des avantages par rapport au finFET. Dans finFET, l'obturateur se courbe autour de l'ailette de trois côtés. Dans les nanocouches, l'obturateur est situé sur les quatre côtés de l'ailette, ce qui donne plus de contrôle sur le courant.

Par rapport à 5 nm, les FET nanocouches de Samsung offrent jusqu'à 45% d'augmentation de l'efficacité de la zone logique et une réduction de 50% de la consommation d'énergie ou une augmentation de 35% de la vitesse. «La structure finFET a ses propres limites d'évolutivité, car la tension d'alimentation ne peut pas être abaissée en dessous de 0,75 V. Notre innovation utilisant des nano-couches nous permet de réduire la tension à des valeurs inférieures à 0,7 V», a déclaré Samsung Lee.

Il existe plusieurs types de technologies GAA, notamment le FET nanocouche et le FET nanofil. GAA lui-même est la prochaine étape après finFET. Dans ce système, finFET est situé sur le côté, puis divisé en morceaux horizontaux. Les pièces forment des canaux. Le matériau d'obturation s'enroule autour de chaque couche.

Comparé au FET nanofil, un tel circuit a des canaux plus larges, c'est-à-dire une productivité et un courant d'excitation plus élevés. «Les nanocouches ont des largeurs plus efficaces», a déclaré Imec Horiguchi. «Les nanofils font beaucoup mieux avec l'électrostatique.» Mais leur section transversale est très petite. Cela ne donnera aucun avantage en termes de largeur de canal effective. "

Les architectures GAA ont plusieurs problèmes. Habituellement, ils donnent une augmentation extrêmement faible par rapport au finFET à 5 nm. Faire des puces en utilisant cette technologie est assez difficile.

«La nouvelle génération de GAA à 3 nm et moins ajoute un autre niveau de complexité à la fabrication», a déclaré Richard Gotshaw, vice-président et directeur technique, Lam Research . - À première vue, cela ressemble à une modification de finFET. Cependant, les exigences augmentent et la complexité de cette architecture GAA est nettement supérieure à celle de finFET. »Dans le processus de production de puces nanocouches, la première étape est le placement de fines couches alternées de SiGe et de silicium sur le substrat. «Nous obtenons une pile de silicium, silicium-germanium, silicium. Nous l'appelons super-réseau », a déclaré Namsun Kim, directeur de l'ingénierie d'Applied Materials, dans une récente interview. "Ayant une teneur en germanium, vous devez lui fournir une bonne couche d'isolation."Au minimum, le pack doit être composé de trois couches de SiGe et de trois silicium. Ensuite, de minuscules structures de feuilles sont appliquées au pack. Après cela, une isolation avec des rainures est formée, puis des séparateurs internes.Ensuite, les couches de SiGe sont retirées du super-réseau, laissant des couches de silicium avec un espace vide entre elles. Chaque couche de silicium forme la base de la feuille ou du canal dans le dispositif. Ensuite, vous devez appliquer un matériau avec une constante diélectrique élevée pour créer un obturateur. «Il y a une distance minimale entre les nanofils. Très petit. Le problème est d'y mettre du métal d'épaisseur de travail », a déclaré Kim.L'industrie a travaillé au fil des ans pour créer la technologie GAA, mais il y a encore quelques problèmes. "L'un des principaux est la capacité parasite", a déclaré Kim. - Si vous me demandez quels sont les principaux problèmes de la technologie GAA, alors il y en a deux. Séparateurs internes et isolation du substrat. "Et ensuite?

Combien de temps la technologie GAA ou les nanocouches sont-elles suffisantes? «Les nanocouches survivront aux deux ou trois de la prochaine technologie de processus. Les ateliers peuvent fabriquer des nanocouches sur N3. La prochaine génération est sûre. Et après cela, vous devrez peut-être modifier l'intégration des nanocouches ou de l'architecture. Mais ce sera toujours une architecture nanocouche », a déclaré Horiguchi d'Imec.L'industrie explore des moyens d'améliorer les technologies GAA et finFET dans les processus de fabrication avancés. Les dispositifs GAA offrent actuellement un léger avantage sur les finFET. Par exemple, dans la nano-puce Imec précédente, le pas de grille était de 42 nm et le pas minimum pour placer les conducteurs métalliques était de 21 nm. En comparaison, finFET à 5 nm peut avoir un pas de grille de 48 nm et un pas minimum de conducteurs métalliques de 28 nm.En laboratoire, Imec a démontré l'évolutivité d'un dispositif semi-conducteur de type p avec un double empilement de GAA et de germanium dans le canal. À l'aide d'un circuit sans extension, Imec a développé un nanofil d'une longueur de grille d'environ 25 nm. Il peut être adapté aux nanocouches. Comme pour la version précédente, la taille du fil est de 9 nm.Le germanium peut jouer un rôle dans la poursuite de l'utilisation de finFET en dehors de la technologie de traitement à 5 nm. Imec a montré Ge nFinFET avec un Gmsat / SSsat et PBTI record. Ils ont été atteints en améliorant le remplacement des matériaux diélectriques élevés.Nous verrons également si la technologie finFET peut être étendue à 3 nm. Il est également difficile de savoir si les puces nanocouches apparaîtront à temps. Il existe de nombreuses inconnues et incertitudes dans ce paysage changeant, et il n'y a pas de calendrier pour clarifier la situation.