Enfin, un

manuel sur SystemVerilog a été publié en Russie

à un niveau supérieur à celui des débutants . Le manuel décrit les technologies et techniques qui sont demandées pour des entretiens chez NVidia, Intel, AMD, Apple et d'autres sociétés électroniques: l'utilisation d'assertions simultanées et d'une couverture fonctionnelle, qui nécessitent désormais non seulement des ingénieurs de vérification, mais aussi des concepteurs de puces; l'algorithme du simulateur à cycles delta; explication sensée de l'analyse de synchronisation statique; diagrammes de communication des unités matérielles via des files d'attente matérielles; la mise en œuvre de ces communications à l'aide de machines à états finis avec des chemins de données, etc.

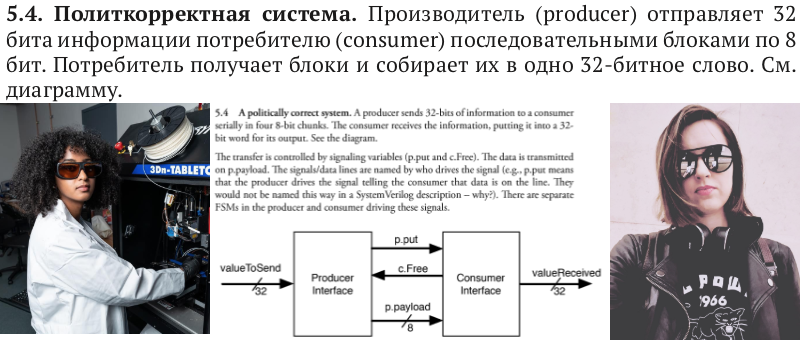

Dans le chapitre sur ce dernier, le lecteur russe peut être intrigué par la mention d'un «système politiquement correct. Qu'est-ce que cela signifierait? C'est probablement une allusion à l'

incident survenu dans le comté de Los Angeles en 2003. Les responsables de Los Angeles ont demandé aux fabricants, fournisseurs et sous-traitants de cesser d'utiliser les termes «maître / esclave» pour le matériel informatique, car l'un des employés du comté se souvenait du passé des esclaves.

Maintenant, les auteurs de la littérature technique évitent les termes maître / esclave. Les ingénieurs afro-américains travaillent également en Amérique moderne (par exemple, Sofia Mvokani du Cameroun - sur la photo de gauche), et l'utilisation d'anciens termes semble archaïque, comme par exemple les termes «pan / slave» dans la littérature technique ukrainienne ressembleraient à la place du «plomb / plomb» accepté ( «Chef / esclave» russe).

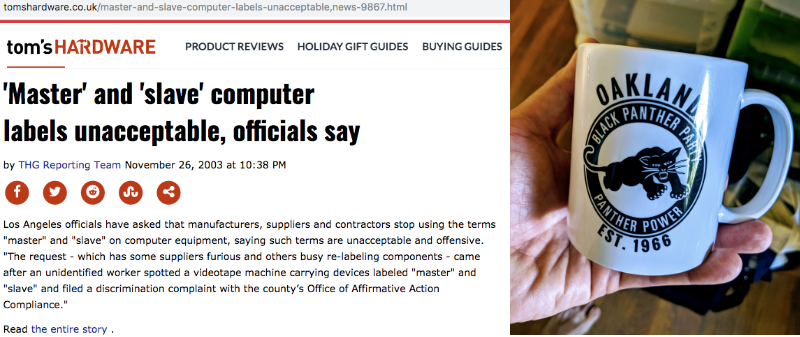

Ce n'est pas la première fois que le thème de la lutte des Afro-Américains pour les droits civils apparaît dans l'e-éducation russe. Par exemple, Tatyana Volkova, spécialiste bien connue de l'enseignement de l'électronique, porte un T-shirt avec l'emblème des «Black Panthers», le mouvement californien, qui à un moment considéré la manifestation pacifique insuffisante, et s'est engagé dans une manifestation armée.

L'image complète de l'emblème sous la peau de Tatiana Alexandrovna est sous la coupe, mais je parlerai principalement des cycles delta et des machines d'état:

Ci-dessous, une capture d'écran de l'article sur le maître / esclave et l'emblème Black Panther promis, après quoi nous passons au livre en tant que tel.

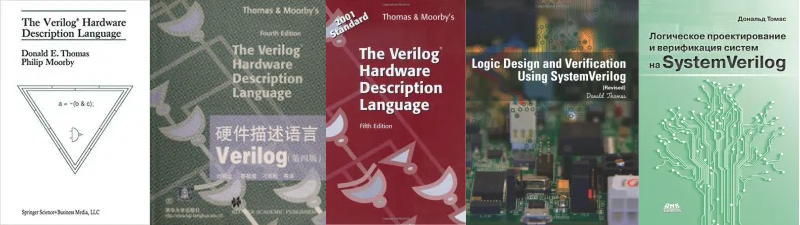

Tout d'abord, Donald Thomas, auteur du livre

«Logical Design and Verification of Systems on SystemVerilog» (2019 en russe de DMK-Press, 2016 en anglais) est le même Donald Thomas, co-auteur avec Philip Murbi, a écrit un livre 1991 Le langage de description du matériel Verilog par Donald Thomas et Philip Moorby. Puis, en 1991, de nombreuses sociétés d'électronique ont encore conçu des puces électroniques à l'ancienne, en les dessinant avec la souris sur l'écran; les technologies de synthèse logique viennent de quitter le laboratoire pour la production; les langages de description du matériel étaient considérés comme destinés à l'écriture de modèles et de tests, et non à des codes sources pour la création de circuits finaux; en plus de VHDL et Verilog fermés à cette époque, il y avait beaucoup de petits langages propriétaires tels que Abel, CUPL, PALASM; et Intel et MIPS avaient des langages de description matérielle internes.

Dans un tel environnement, le livre de Thomas et Murbi est sorti, qui est devenu le même pour les concepteurs de circuits numériques des années 1990 que le livre de Kernigan-Richie pour les programmeurs pour C, et les livres de Bjarni Straustrup pour les programmeurs C ++. Le livre a survécu à cinq éditions - de 1991 à 2002, mais pour l'ère des iPhones était clairement insuffisant. Et en 2016, Donald Thomas a décidé de rattraper son retard et a publié un nouveau livre dans lequel il décrit les principales innovations dans le langage et la méthodologie sur 25 ans. Au cours des 25 années au cours desquelles Verilog est devenu une base commune pour l'ensemble de l'industrie, des plans y sont écrits pour tout, des iPhone célèbres et des ordinateurs de contrôle de Tesla aux hélicoptères militaires russes.

Ensuite, je mettrai en évidence mes commentaires avec du texte bleu pour les séparer des images du livre.

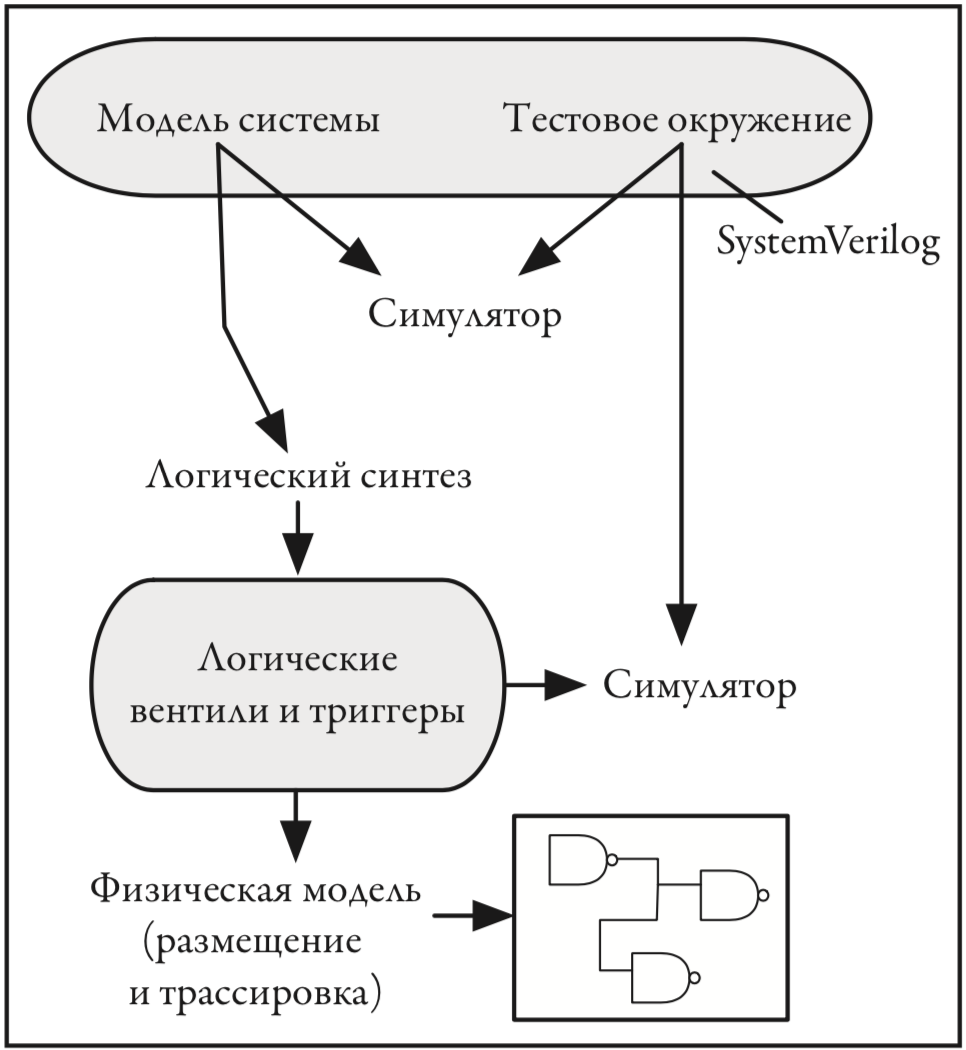

Même avant le texte principal du livre, il y a le pré-chapitre «Contexte: Conception au niveau des transferts de registres», de sorte qu'un programmeur, un écolier ou, par exemple, un amateur d'exercice avec des planches à pain, comprendra immédiatement de quoi il s'agit et comment il peut utiliser le livre. Il dit:Des systèmes numériques sont produits avec des milliards de transistors sur une puce. Un amateur, bien sûr, peut dessiner plusieurs portes logiques et les connecter avec des fils comme spécification (pour une implémentation sur une planche à pain), mais pour les projets commerciaux, c'est une histoire ancienne ... Les systèmes modernes sont spécifiés dans des langages de description matérielle tels que SystemVerilog.

En même temps, voici une image tellement simplifiée pour illustrer comment le texte sur le veril se transforme en pistes et transistors du microcircuit en usine:

Le premier mot du livre après la préface est «simulateur». Pour comprendre les langages de description du matériel, vous devez être clairement conscient que le sous-ensemble synthétisé du verilogue n'est pas un langage de programmation, mais un langage pour décrire les circuits électriques. Comme disons que HTML n'est pas un langage de programmation, mais un langage pour décrire les pages Web. Alors qu'un langage de programmation est destiné à être compilé en une chaîne d'instructions de processeur, un langage de description matérielle est destiné à être converti (en particulier) en fer de processeur en tant que tel. Dans ce cas, avant de couler dans le fer, le code dans le langage de description du matériel doit être vérifié, à quoi sert un interprète spécialisé, appelé simulateur.

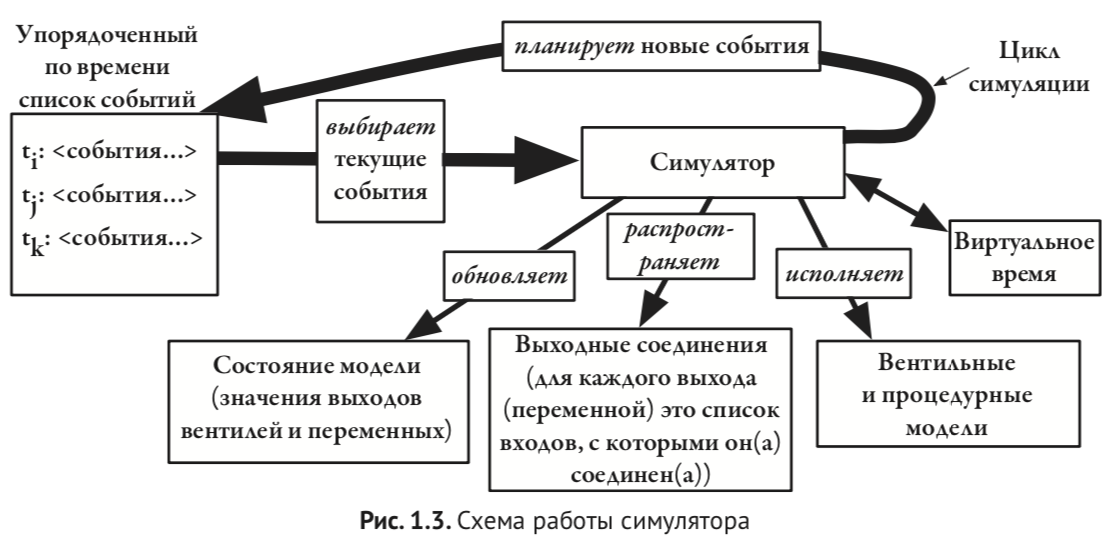

Au début du livre, Donald Thomas montre une image simplifiée du simulateur, et à la fin du livre, il le clarifie et le complète:

Le simulateur a des files d'attente d'événements et un temps simulé:

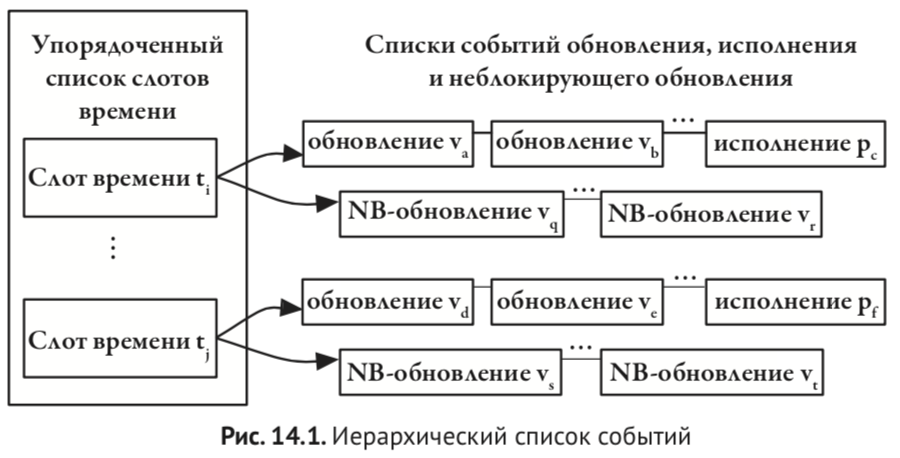

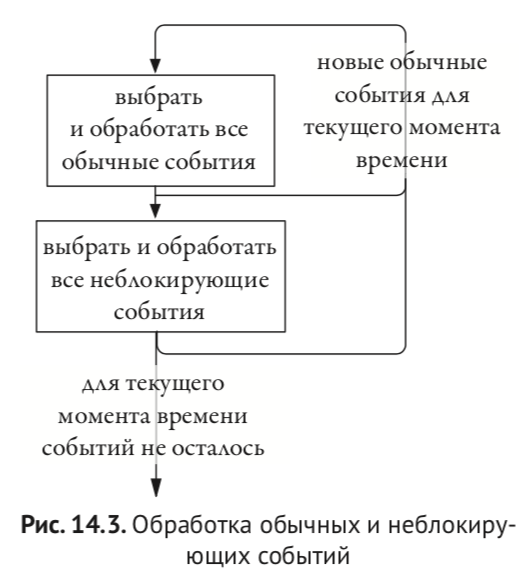

Un événement peut donner lieu à un nouvel événement, à la fois au moment actuel de la simulation (dans le cycle delta actuel) et au futur. Dans le cycle delta en cours, tous les événements générés par les affectations dites bloquantes sont traités en premier, puis les événements générés par les affectations non bloquantes sont traités. Ceci est nécessaire pour la simulation correcte de la sémantique parallèle de la propagation des signaux électriques dans le fer:

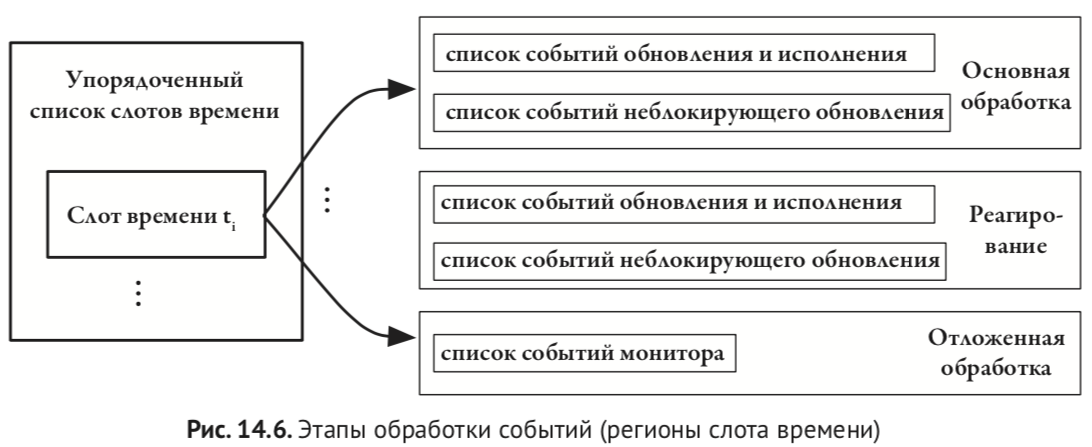

En plus du sous-ensemble synthétisé du verilogue, il existe également un sous-ensemble non synthétisé. Il est destiné à décrire l'environnement de test et les tests, et maintenant il peut être considéré comme une sorte de langage de programmation. Pour les événements et les moniteurs de l'environnement de test, des étapes supplémentaires du simulateur sont introduites:

Une connaissance précise de l'algorithme du simulateur est très utile pour éviter une variété de bogues associés à la soi-disant race (race condition). Lorsque j'interviens des ingénieurs, je leur demande toujours de donner un exemple de condition de course dans Verilog. De plus, si pour les jeunes ingénieurs RTL Design et Design Verification, ces connaissances sont très souhaitables, mais pas à tous égards nécessaires à 100%, c'est-à-dire les professions dans lesquelles l'argent est payé directement pour ces connaissances. Je parle des programmeurs qui travaillent dans les équipes Synopsys VCS, Cadence IES et Mentor ModelSim.

Synopsys et Cadence sont deux sociétés situées en Californie à moins de 15 minutes de route l'une de l'autre. Ils n'emploient que quelques milliers de personnes, mais ils contrôlent le développement des microcircuits dans le monde - à Intel, Apple, Samsung, Huawei, même dans des instituts russes secrets qui fabriquent des puces pour des équipements militaires.

Si les camarades Poutine, Rogozine et Vekselberg veulent vraiment introduire une substitution des importations en Russie, ils pourraient financer le développement du Synopsys VCS analogique russe (pour simuler le verilogue), du Synopsys Design Compiler (pour la synthèse logique du verilogue) et du Synopsys IC Compiler (pour le placement physique des résultats de la synthèse logique) ) Il y a probablement plusieurs milliers de programmeurs mathématiquement avertis en Russie.

Bien que les licences pour ces produits logiciels soient assez faciles à casser, leur utilisation sans support est difficile. Si Huawei est déconnecté de Synopsys et Cadence, ils auront en quelque sorte pire que lorsqu'ils sont déconnectés d'Android et même des cœurs ARM.

Oui, voici donc l'algorithme raffiné à la fin du livre de Donald Thomas. Si vous ne l'apprenez pas par cœur, il est inutile d'intervenir dans les groupes de simulation de Synopsys, Cadence, Siemens / Mentor, Xilinx, et ils vous demanderont de le dessiner au tableau et de vous suggérer comment optimiser un cas particulier:

Après avoir clarifié la simulation au début du livre, Donald Thomas décrit le langage SystemVerilog comme tel. Ce langage a émergé en tant que sur-ensemble Verilog en 2002, à la suite de la fusion des langages Verilog-2001, Vera et Superlog, et avec l'ajout d'idées du langage de spécification de propriété (PSL), qui ont été transformées en assertions SystemVerilog (SVA).

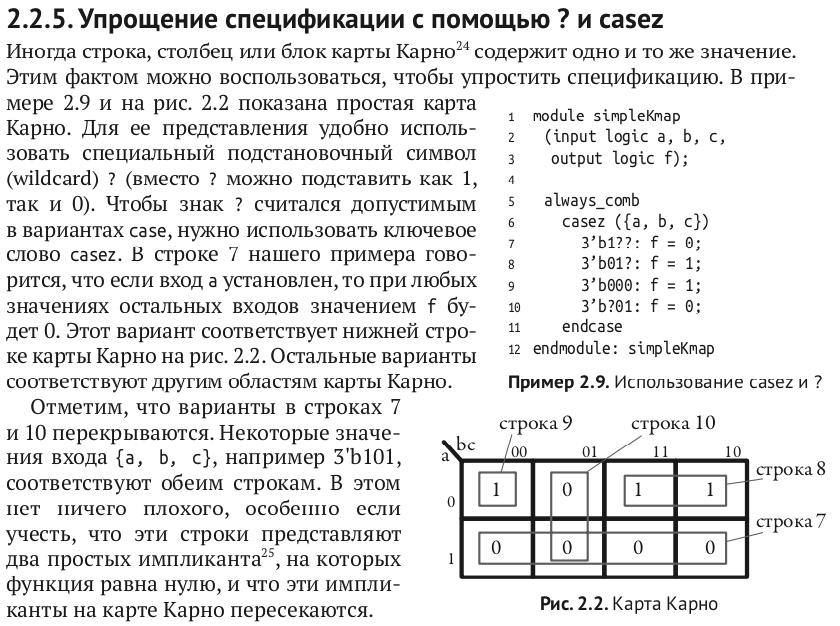

Donald Thomas estime que vous avez déjà appris les bases du design numérique quelque part, et tisse donc dans le tissu narratif diverses pièces bien connues telles que les cartes Carnot. Les cartes de Carnot ont été utilisées pour la conception manuelle des circuits dans les années 1960, après quoi cette méthode a été remplacée par l'optimisation automatique de la logique en utilisant l'algorithme Quine-McCluskey et l'optimiseur de logique automatique Espresso. Par conséquent, les cartes Carnot sont présentes dans tous les manuels universitaires sur la conception de la logique numérique, mais elles semblent flotter dans les airs. Et ici, Donald Thomas attache des cartes Carnot à la vie d'un designer sur un verilo du 21e siècle:

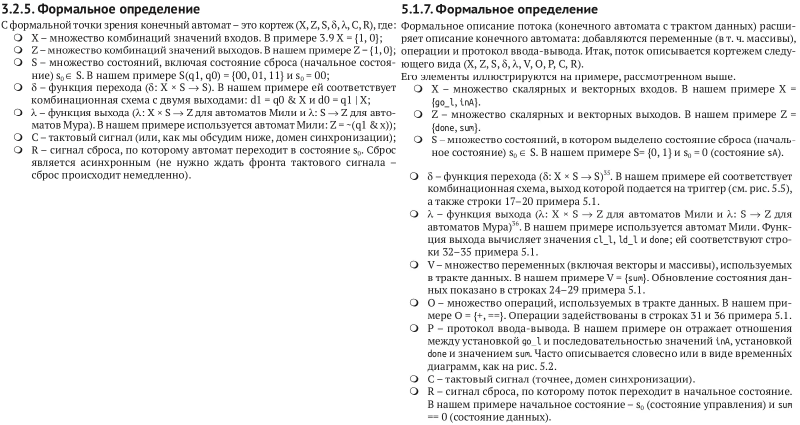

De plus, Donald Thomas écrit sur les machines à états finis et donne 1) une définition mathématique stricte; 2) diagrammes; 3) code; 4) après quoi il commence à les étendre aux machines à états finis avec un chemin de données - flux matériels; 5) après quoi ces flux commencent à interagir avec lui, à la fois selon de simples protocoles «politiquement corrects» (voir ci-dessus) et en utilisant des files d'attente matérielles.

Voici le code d'un automate simple avec un chemin de données que Thomas cite comme premier exemple:

Ensuite, Thomas a un chapitre sur l'analyse de synchronisation statique. Rien de spécial, mais plus propre que sur de nombreux sites indiens populaires, "Comment passer l'entretien avec VLSI." Et aussi plus complètement que dans certains livres sur le veril, qui rongent péniblement la syntaxe du langage, mais ne montrent pas vraiment comment l'utiliser.

Pourquoi avons-nous besoin d'une analyse temporelle statique? Dans le matériel réel, contrairement à l'illusion que le processeur montre au programmeur, chaque calcul passe par un intervalle de temps où toutes les ordures sont sur les fils - non seulement des zéros et des uns clairement calculés, mais aussi des problèmes aléatoires, c'est-à-dire des problèmes, et généralement valeurs non numériques dans la zone interdite. Par exemple, si toutes les tensions supérieures à 0,7 volts sont considérées comme une unité numérique et toutes les tensions inférieures à 0,3 volts comme un zéro numérique, 0,4 volts peuvent apparaître sur le fil.

Au final, tous les signaux du circuit suivent leur propre chemin et la situation s'installe, mais cela "au final" devrait être inférieur au cycle du signal d'horloge (horloge). Ce cycle est inversement proportionnel à la fréquence à laquelle le circuit fonctionne (gigahertz, mégahertz).

Si le résultat réglé des calculs ou des opérations logiques ne tombe pas dans le déclencheur D (élément de mémoire minimum) au moment de l'ouverture (intervalle autour du changement d'un tel signal), l'état du circuit deviendra des ordures - le satellite ou le réacteur explosera, l'iPhone cessera de répondre aux appels. Tout le concepteur d'équipement a besoin de connaître non moins ironiquement que la logique.

Pourquoi l'analyse est-elle statique? Dans les années 80, c'était dynamique - les retards ont été clarifiés grâce à la simulation. Cela s'est avéré peu fiable pour les circuits avec des centaines de milliers, des millions et des milliards de transistors, et maintenant tous les retards sont calculés statiquement, sur la base de l'analyse des trajets du signal après la synthèse.

Le signal d'horloge peut également arriver dans différentes parties de la puce avec un certain retard, ce qui ajoute une autre incertitude à cette cuisine qui doit être éliminée (heureusement, pas manuellement, mais à l'aide de programmes d'arbre de synthèse d'horloge et d'autres méthodes):

Dans le chapitre sur les flux, Thomas présente plusieurs options de base sur la façon dont les machines à états de fonctionnement parallèles avec des chemins de données peuvent échanger des informations, notamment en utilisant des tampons et des files d'attente. Comme dans la conception / le circuit lui-même, au niveau des transferts de registres, donc dans le modèle comportemental ou l'environnement de test du circuit. En lisant Thomas, il est agréable d'écrire et de déboguer des exemples vous-même pour tous les cas des protocoles décrits par lui. Le fait est qu'ils aiment écrire du code sur de tels sujets (une petite machine à états finis contrôlant, le flux de données entre deux modules, des chemins de données en pipeline ou tout simplement du code pour une file d'attente matérielle) sur un tableau noir ou sur un ordinateur lors d'un entretien de deuxième niveau dans les entreprises électroniques. Si vous pouvez écrire un exemple pour l'une des combinaisons décrites par Thomas en 20 minutes avec un code de 30 à 50 lignes, alors vous ferez bonne impression. Difficile à apprendre - facile au combat.

L'environnement de test pour les routeurs (Fig. 8.3) avec des files d'attente pour plusieurs ports est un exemple populaire utilisé pour expliquer les méthodologies de vérification. Probablement parce que certaines de ces méthodologies ont été inventées par Cisco et d'autres sociétés qui conçoivent des puces pour le matériel réseau.

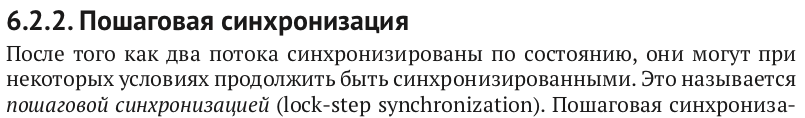

Au chapitre 6.2.2. Thomas décrit l'une des options pour l'interaction des threads - la synchronisation pas à pas (Lock-step). L'une des applications de verrouillage est les systèmes à haute fiabilité, par exemple dans l'électronique automobile. Un cas particulier: deux processeurs peuvent exécuter le même programme avec un retard de plusieurs cycles, et pendant cette exécution un circuit spécial peut vérifier qu'ils ont les mêmes résultats.

Thomas était clairement préoccupé par la fiabilité, car en plus de l'étape de verrouillage, il cite l'utilisation de CRC, un code cycliquement redondant pour détecter les erreurs de transfert de données. Dans le même temps, Thomas explique comment calculer le CRC à l'aide du LFSR, un registre à décalage à rétroaction linéaire. A la fois cela et un autre doivent être capables pour un jeune ingénieur. C’est l’avantage du livre de Thomas - même s’il ne creuse pas toujours profondément, il touche à de nombreux sujets et montre où creuser:

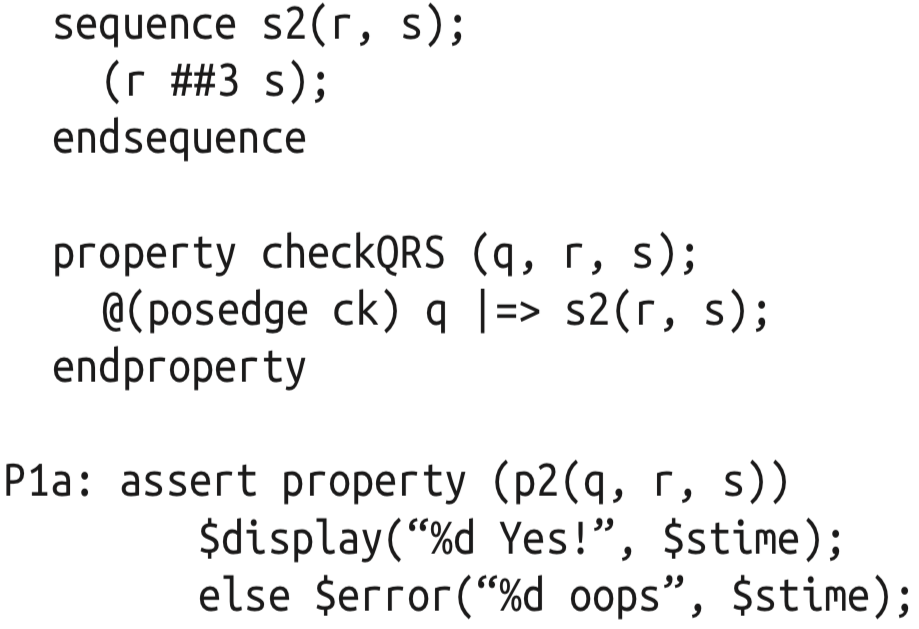

En décrivant le CRC, Thomas fait référence à un livre très intéressant et mal compris en Russie par Hacker's Delight :

Donald Thomas dans son nouveau livre aborde trois technologies qui n'étaient pas du tout dans l'ancien livre:

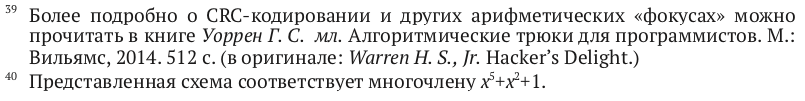

- Génération automatique de transactions pseudo-aléatoires avec des règles contraintes (transactions aléatoires contraintes / solveurs de contraintes).

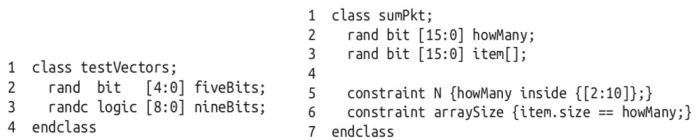

- Prise en compte de la couverture de scénarios intéressants survenant lors du bombardement d'un design par des transactions aléatoires limitées, couverture fonctionnelle.

- Le langage des énoncés de logique temporelle (assertions simultanées) et son utilisation à la fois dans la simulation et dans la preuve automatique des propriétés de conception à l'aide de programmes de vérification formels.

Ces trois technologies ne sont entrées dans l'industrie dans le bon sens qu'au 21e siècle, mais elles sont entrées assez fermement. Au début, ils étaient tous utilisés pour créer des environnements de test par des ingénieurs de vérification, mais maintenant la connaissance de la couverture fonctionnelle et du langage d'assertion temporelle (SystemVerilog Assertions - SVA) nécessite également des concepteurs. Thomas a un certain minimum qui vous aidera à ne pas être interrompu lors d'un entretien téléphonique, mais pour un vrai travail, vous devez en savoir beaucoup plus. De plus, non seulement le langage des instructions temporelles en tant que tel, mais aussi la pratique du débogage avec son aide des machines à états finis parallèles générées par le simulateur pour chaque instruction, ainsi que l'utilisation de programmes de vérification formels. La vérification formelle basée sur les assertions ces dernières années a été largement mise en œuvre au sein d'Apple, d'AMD et d'autres sociétés de ce type.

J'ai un ami qui a téléchargé

ce livre sur la langue des déclarations temporelles et l'a étudié toutes les vacances du Nouvel An au lieu d'un voyage à Hawaï avec des filles. À partir de là, vous pouvez comprendre l'importance des assertions SystemVerilog (SVA) pour la carrière et l'industrie. Certes, par souci d'exhaustivité, je dois mentionner qu'il est le fils d'émigrants de Taïwan, et ils ont une attitude plus sévère envers de telles choses que les Russes.

Voici comment Thomas gère la génération de transactions pseudo-aléatoires (une transaction avec des champs rand et leur restriction à l'aide de la construction de contrainte):

Et voici comment Thomas se rapporte à la couverture fonctionnelle - groupe de couverture / point de couverture / bacs, représentant des combinaisons de plusieurs couvertures variables (croisées), l'utilisation de bacs génériques, de plages de valeurs et de la couverture de transition dans les machines à états:

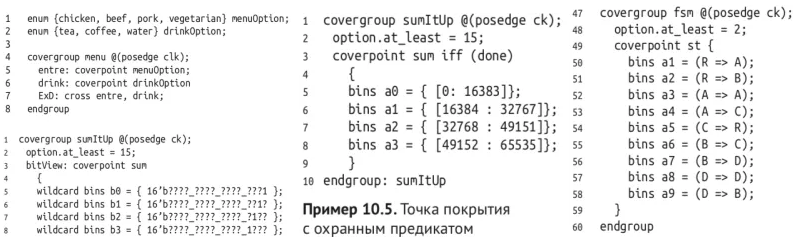

Voici un exemple de la déclaration temporelle la plus simple "si q est vrai sur le front positif du signal d'horloge, alors la séquence s2 doit être exécutée à travers le cycle, dans lequel r est d'abord vrai, et s est dans trois cycles supplémentaires":

Que lire avant et après le livre «Logical Design and Verification of Systems on SystemVerilog» de Donald Thomas?

Si vous ne comprenez rien du tout dans mon article, vous pouvez essayer de lire le livre

«Circuit numérique et architecture informatique» de David Harris et Sarah Harris . Le livre Harris & Harris peut être compris par tous ceux qui savent lire et compter, à condition que le lecteur soit motivé.

Le livre commence au niveau secondaire - tensions, nombres binaires - et se termine par la conception de son propre processeur sur le veril.Spoiler: David Harris et Sarah Harris ne sont ni mari ni femme, ni même frère et sœur. Ce ne sont que des homonymes qui ont accidentellement commencé à travailler comme enseignants dans la même université, pendant laquelle ils ont écrit un livre.Ici à gauche sur la photo est la fille Irina de Novosibirsk Academgorodok tenant l'édition anglaise de Harris & Harris, et à droite est son édition russe. Après le livre de Donald Thomas, je recommande de télécharger des articles de Cliff Cummings. Il est le plus célèbre formateur de veril pour la synthèse et la vérification. En lisant le livre de Donald Thomas, j'ai eu l'idée «plusieurs fois, ce serait bien d'insérer telle ou telle pièce de Cliff Cummings» pour être complet. Cliff prend 1000 $ à 3000 $ pour chaque étudiant aux séminaires, selon la durée du séminaire (de jour en semaine), et les sociétés d'électronique paient pour améliorer la qualité de leurs ingénieurs qui ne sont pas bien formés dans les universités. Même à Stanford, hélas, tout le monde ne l'apprend pas - j'avais un stagiaire de Stanford, je le sais de lui. Si vous téléchargez tous les articles gratuits de Cliff Cummings après avoir lu Donald Thomas, vous économiserez tout cet argent.Ces deux articles sont obligatoires - ils aiment demander partout dans l'interview:Le passage de domaine Horloge (la CDC) Conception et techniques de vérification de SystemVerilog Solution: Utilisation dela simulation et de synthèse, techniques »pour le FIFO Conception asynchrone avec comparaisons Asynchronous pointeurVoici trois articles à lire, il est souhaitable, en particulier sur la suppression des états asynchrones Reseta de transcodage de style et EFM« cas de EFM (1'b1) // synopsys parallel_case ... state [STATE_N]: ... ”, qui a longtemps été utilisé dans les puces à haute vitesse, de retour dans Sun Microsystems, et continue d'être utilisé maintenant:Techniques de conception de réinitialisation asynchrone et synchrone - Techniques decodage et de script de la deuxième partie pour les conceptions FSM avec synthèse -Optimized, Glitch-Free OutputsSynthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 EnhancementsEt voici un article curieux où vous verrez le manque de pensée du verilogue, qui est resté depuis les années 1980. Bien que maintenant, à l'ère de l'analyse de synchronisation statique, ce n'est pas si pertinent, mais les retards d'inertie et de transport sont parfois mentionnés dans la littérature et le code, et vous devez savoir comment les modéliser:Méthodes correctes pour ajouter des retards aux modèles comportementaux VerilogC'est moi avec Cliff Cummings:

Après le livre de Donald Thomas, je recommande de télécharger des articles de Cliff Cummings. Il est le plus célèbre formateur de veril pour la synthèse et la vérification. En lisant le livre de Donald Thomas, j'ai eu l'idée «plusieurs fois, ce serait bien d'insérer telle ou telle pièce de Cliff Cummings» pour être complet. Cliff prend 1000 $ à 3000 $ pour chaque étudiant aux séminaires, selon la durée du séminaire (de jour en semaine), et les sociétés d'électronique paient pour améliorer la qualité de leurs ingénieurs qui ne sont pas bien formés dans les universités. Même à Stanford, hélas, tout le monde ne l'apprend pas - j'avais un stagiaire de Stanford, je le sais de lui. Si vous téléchargez tous les articles gratuits de Cliff Cummings après avoir lu Donald Thomas, vous économiserez tout cet argent.Ces deux articles sont obligatoires - ils aiment demander partout dans l'interview:Le passage de domaine Horloge (la CDC) Conception et techniques de vérification de SystemVerilog Solution: Utilisation dela simulation et de synthèse, techniques »pour le FIFO Conception asynchrone avec comparaisons Asynchronous pointeurVoici trois articles à lire, il est souhaitable, en particulier sur la suppression des états asynchrones Reseta de transcodage de style et EFM« cas de EFM (1'b1) // synopsys parallel_case ... state [STATE_N]: ... ”, qui a longtemps été utilisé dans les puces à haute vitesse, de retour dans Sun Microsystems, et continue d'être utilisé maintenant:Techniques de conception de réinitialisation asynchrone et synchrone - Techniques decodage et de script de la deuxième partie pour les conceptions FSM avec synthèse -Optimized, Glitch-Free OutputsSynthesizable Finite State Machine Design Techniques Using the New SystemVerilog 3.0 EnhancementsEt voici un article curieux où vous verrez le manque de pensée du verilogue, qui est resté depuis les années 1980. Bien que maintenant, à l'ère de l'analyse de synchronisation statique, ce n'est pas si pertinent, mais les retards d'inertie et de transport sont parfois mentionnés dans la littérature et le code, et vous devez savoir comment les modéliser:Méthodes correctes pour ajouter des retards aux modèles comportementaux VerilogC'est moi avec Cliff Cummings: