Si vous pensiez que le «gang» d'Intel est le plus fidèle partisan

de la loi de Moore , alors vous n'avez probablement pas entendu comment Philip Wong se répand sur ce sujet. Wong, vice-président de la recherche d'entreprise à Taiwan Semiconductor Manufacturing Corp (TSMC), a fait une présentation lors d'une récente conférence Hot Chips déclarant que la loi de Moore est non seulement vivante et bien, mais avec un ensemble assez divers d'astuces technologiques, ce n'est toujours pas vrai moins de trois décennies.

"Il n'est pas mort", a-t-il déclaré aux personnes présentes à Hot Chips. "Il ne ralentit pas, il ne tousse même pas."

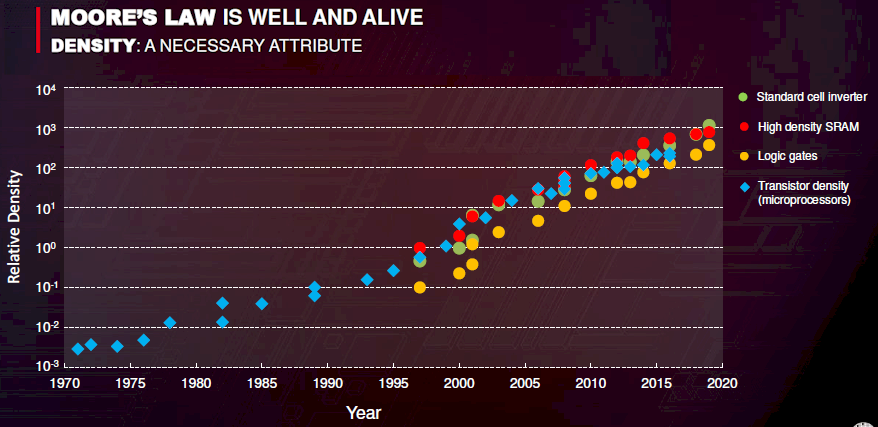

Écoutez Wong, donc la seule action nécessaire pour maintenir la loi de Moore est d'améliorer la densité. Et même s'il admet que la fréquence d'horloge a reposé sur son plafond, marquant la fin

de la loi de mise à l'échelle de Dennard , il dit que c'est la densité des transistors qui améliorera la vitesse et l'efficacité énergétique.

La loi de Moore est vivante

La loi de Moore est vivanteEn fin de compte, peu importe la densité plus élevée atteinte. Wong estime que l'essentiel est que les entreprises puissent remplir plus de transistors en un volume plus petit avec une meilleure efficacité énergétique. À court terme, cela peut être réalisé de manière ancienne et éprouvée, à savoir en améliorant la technologie de fabrication des CMOS de sorte qu'il s'avère produire des transistors avec une longueur de grille plus courte.

TSMC a déjà maîtrisé la technologie de traitement à 7 nm et se dirige vers 5 nm. Wong a déclaré que l'écosystème de développement de la technologie des processus à 5 nm est déjà prêt et que la société a déjà commencé à produire des échantillons de risque - c'est-à-dire que la technologie des processus et les outils de développement sont prêts et que les substrats de travail sont en cours de production. Lors de la dernière assemblée des actionnaires, TSMC a annoncé son intention de commencer la production de masse de puces à 5 nm au premier semestre 2020. Il s’avère que les plans de l’entreprise incluent déjà une technologie de traitement à 3 nm.

Mais toute cette technologie est basée sur

des puces

planes [plates], et Wong admet que cette approche cessera éventuellement d'évoluer. "Si nous suivons la voie de l'augmentation bidimensionnelle, nous avons déjà atteint plusieurs centaines d'atomes, et bientôt tous nos atomes s'épuiseront", a-t-il expliqué.

Mais cela ne signifie pas la fin de l'augmentation de la densité. Il a noté que certaines innovations dans l'industrie des semi-conducteurs ont soutenu un graphique de densité à la hausse, même à la fin de la mise à l'échelle de Dennard. En particulier, la technologie du silicium contraint et

du diélectrique à k élevé est apparue , puis le FInFet (Fin Field Effector Transistor), la technologie des structures tridimensionnelles, a suivi. Maintenant, pour aller au-delà de 7 nm, la technologie DTCO (Design Technology Co-Optimization) est à l'étude.

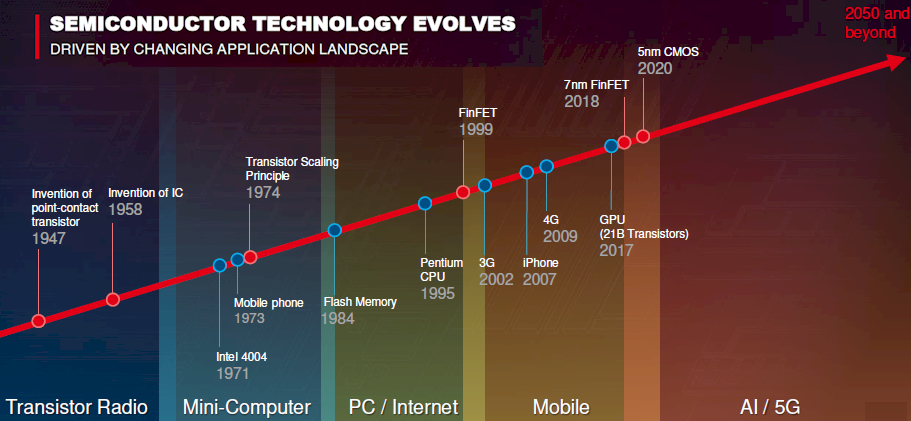

Toutes ces innovations sont survenues parce qu'il était nécessaire de développer de nouvelles plates-formes informatiques nécessitant un matériel plus rapide et plus économe en énergie. Cette évolution a donné naissance aux mini-ordinateurs dans les années 70, aux PC dans les années 80, à Internet dans les années 90 et aujourd'hui aux appareils mobiles. Chaque étape a nécessité une augmentation de la densité grâce à une fabrication de semi-conducteurs améliorée. Wong pense que les demandes suivantes proviendront de l'intelligence artificielle et de la 5G.

Évolution de la technologie des semi-conducteurs

Évolution de la technologie des semi-conducteursQuelles innovations seront nécessaires pour garantir que le Moore's Law Party ne s'arrête pas?

À court terme, la densité de calcul globale et la densité de mémoire augmenteront l'utilisation des chipsets utilisés pour créer des boîtiers multi-puces de structures 2.5D, même si les puces elles-mêmes ne deviennent pas plus denses. Wong a déclaré que ce processus fait déjà de la technologie de processus spécifique d'un chiplet individuel un paramètre moins important que la capacité d'intégrer ces composants dans un seul paquet.

TSMC a sa propre version du châssis 2.5D avec la technologie Chip-on-Wafer-on-Substrate (CoWoS) (Embedded Multi-die Interconnect Bridge, ou EMIB, d'Intel fait concurrence à cette technologie). CoWoS vous permet de créer des boîtiers multi-puces, de fixer des chipsets et une mémoire appropriée sur l'interposeur, et de les connecter à l'aide des contacts verticaux TSV. L'implémentation la plus intéressante de CoWoS est l'accélérateur GPU Nvidia Tesla V100, dans lequel le GPU GV100 est doté d'une mémoire à large bande passante (HBM). Plus de chipsets sont intégrés par Intel, AMD et Xilinx.

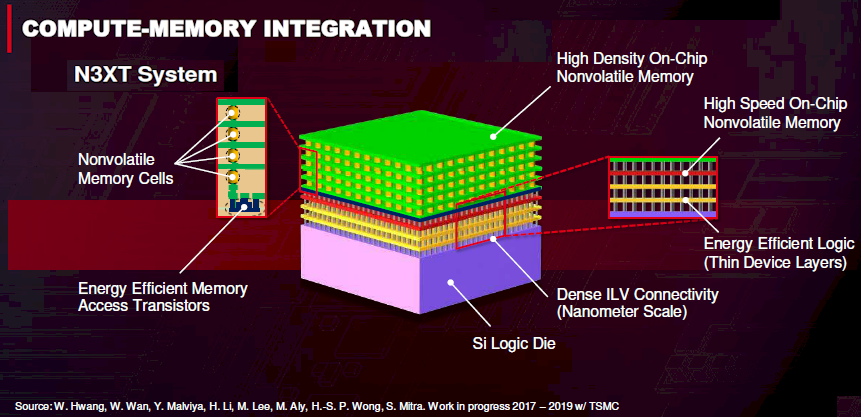

Mais les possibilités de 2.5D pour augmenter la densité ne sont pas illimitées. Une solution plus évolutive nécessitera des technologies de placement de transistors vraiment tridimensionnelles. Pour cela, selon Wong, la technologie monolithique tridimensionnelle N3XT est la mieux adaptée sur la base de nouveaux matériaux et d'une intégration étroite de la mémoire avec la logique. N3XT, la «technologie de nano-ingénierie des systèmes informatiques», est discutée dans le monde universitaire depuis 2015, mais maintenant que des entreprises comme TSMC ont commencé à la prendre au sérieux, elle a de bonnes chances de commercialisation.

Wong a montré des diapositives avec des diagrammes de l'apparence d'un tel appareil. Il se compose de couches de logique écoénergétique (jaune), de mémoire haute vitesse (rouge) et de mémoire non volatile de grande capacité (verte), disposées alternativement l'une au-dessus de l'autre. Et tout cela repose sur un cristal logique au silicium ordinaire (violet).

Système N3XT

Système N3XTL'essentiel ici est de combiner les différentes couches via ILV, Inter-Layer-Via (accès vertical intercouche). Contrairement à une échelle micrométrique TSV, ILV peut être formé à l'échelle nanométrique. Bien que ce soit une partie extrêmement importante de la technologie N3XT, Wong ne pouvait pas en dire beaucoup à ce sujet. Il est cependant évident que TSMC y travaille en étroite collaboration et a déjà déposé plusieurs brevets y afférents.

Dans les puces tridimensionnelles, l'entrelacement de la mémoire et de la logique est très important, car il vous permet de réduire la distance entre eux, garantissant ainsi un débit élevé et une faible latence du transfert d'informations, ce qui sera nécessaire pour des applications telles que l'IA et la 5G. En CMOS, la mémoire et la logique ne peuvent pas être entrelacées, car la gravure des transistors logiques nécessite une température de l'ordre de 1000 degrés Celsius, ce qui détruirait les couches voisines en production. Il nécessite quelque chose qui peut être fabriqué à des températures de l'ordre de 400 degrés.

Il s'avère qu'au cours des dernières années, les chercheurs ont étudié de nouveaux matériaux qui semblent convenir à la production de transistors à grande vitesse à des températures relativement basses. Contrairement aux matériaux de silicium utilisés dans la production actuelle, les monocouches de métaux de transition dichalcogénure (TMD) y sont utilisées sur la base d'éléments tels que le molybdène, le tungstène et le sélénium.

Les matériaux TMD démontrent une grande mobilité des porteurs de charge - les électrons les traversent avec une grande facilité - avec des canaux étroits. Ce qui est pratique, de telles caractéristiques sont nécessaires pour créer des transistors d'une taille inférieure à 2-3 nm. Wong a déclaré que le laboratoire TSMC testait des substrats TMD expérimentaux à base de disulfure de tungstène.

Un autre candidat pour les nanomatériaux est les nanotubes de carbone. Wong a déclaré que leurs variations expérimentales ont été faites, montrant un bon comportement du matériau en tant que semi-conducteur. Des prototypes de logique et de SRAM basés sur des nanotubes de carbone ont déjà été assemblés, y compris la variante RISC-V des chercheurs du MIT.

En ce qui concerne la mémoire, selon Wong, les candidats les plus probables pour l'intégration tridimensionnelle seront: SST-MRAM (mémoire à accès aléatoire magnétorésistif à couple de transfert de spin, mémoire à accès aléatoire magnétorésistif qui utilise le transfert de momentum de spin électronique pour enregistrer);

Mémoire de changement de phase PCM;

mémoire résistive à accès aléatoire ReRAM; mémoire basée sur la métallisation programmable de la cellule CBRAM; Mémoire vive

ferroélectrique FERAM. Tout cela est une mémoire non volatile à accès aléatoire, qui ne nécessite pas l'opération d'effacement d'une cellule avant d'y écrire de nouvelles informations. Certaines options sont déjà sur le marché - Everspin MRAM, Samsung MRAM, Crossbar ReRAM et Intel 3D XPoint (qui, selon la plupart, est une variante de PCM).

De nouveaux types de mémoire

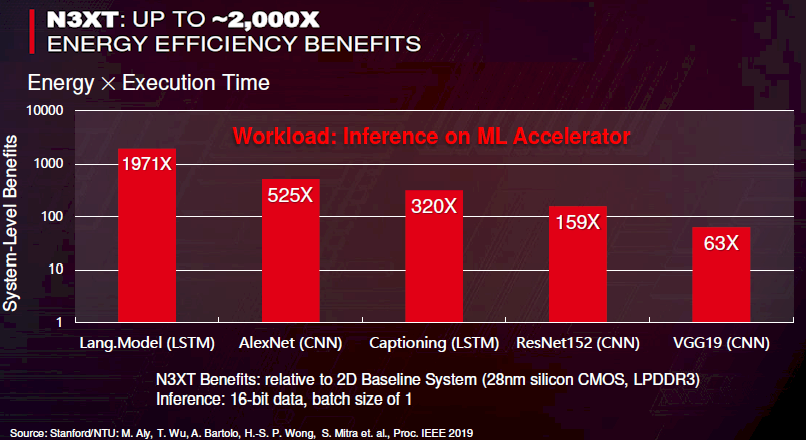

De nouveaux types de mémoireLes chercheurs ont simulé les performances des appareils N3XT et les ont comparés aux puces bidimensionnelles traditionnelles avec approximativement les mêmes capacités logiques et de mémoire. Selon leurs recherches, où diverses méthodes de mesure de la vitesse des algorithmes d'apprentissage automatique ont été utilisées, les appareils de la technologie N3XT se sont avérés 63 à 1971 fois plus efficaces que les appareils bidimensionnels.

L'avantage du N3XT par rapport aux systèmes bidimensionnels

L'avantage du N3XT par rapport aux systèmes bidimensionnelsCela semble prometteur. Mais Wong n’a pas expliqué comment exactement ces technologies au cours des 30 prochaines années pourront maintenir la vitesse d’amélioration technologique nécessaire à la loi de Moore. Par exemple, la transition vers de nouveaux nanomatériaux nous donnera une augmentation ponctuelle de la densité des transistors par rapport aux composants bidimensionnels. Mais là, à la fin, nous rencontrerons des restrictions atomiques.

Théoriquement, si vous pouvez doubler la hauteur des appareils tridimensionnels tous les 18 mois, vous pouvez obtenir une augmentation de la densité par surface carrée. Bien sûr, pour les appareils mobiles et embarqués, cette approche deviendra rapidement trop lourde, et les puces pour les ordinateurs des centres de données après sept à huit générations resteront dans un plafond de 4 mètres.

Pour que tout continue de fonctionner pendant plusieurs décennies et que la densité continue de s’insérer dans la courbe de la loi de Moore, d’autres innovations techniques non mentionnées par Wong devront être développées. Mais si vous produisez des puces comme TSMC, vous devez accepter que les chercheurs vous proposeront constamment de nouveaux candidats pour des technologies qui n'auront besoin que de demandes de nouvelles tâches plus exigeantes pour entrer sur le marché. Et si vous vous souvenez de l'histoire, de telles tâches apparaîtront certainement.