Placer des chipsets nus sur un réseau de silicium vous permettra de fabriquer des ordinateurs plus petits et plus de puissance de traitement

La nécessité de rendre de moins en moins certains appareils, tandis que d'autres de plus en plus, est depuis longtemps le principal moteur de l'innovation en électronique. La première option se manifeste des ordinateurs portables aux smartphones, puis aux montres intelligentes, aux écouteurs intelligents et à d'autres appareils électroniques «invisibles». La deuxième option détermine la configuration des centres de données modernes - des monstres mégawatts qui remplissent des installations de stockage spécialement construites pour eux dans le monde entier. Fait intéressant, dans les deux cas, les progrès sont limités par la même technologie - uniquement pour diverses raisons.

Nous soutenons que le PCB est le coupable. Notre solution est de s'en débarrasser complètement.

Notre étude montre que les cartes de circuits imprimés peuvent être remplacées par le même matériau que les puces qui y sont soudées - c'est-à-dire le silicium. Une telle approche permettrait de créer à la fois des systèmes de taille et de poids plus petits, adaptés à l'électronique portable et à d'autres appareils de taille limitée, et des ordinateurs à haute vitesse incroyablement puissants qui peuvent entasser la puissance de calcul d'une douzaine de serveurs dans un substrat de silicium de la taille d'une assiette.

Une technologie similaire entièrement en silicium, que nous appelons le réseau d'interconnexion en silicium, vous permet de connecter des puces nues directement à des fragments de silicium individuels. Contrairement aux pistes sur les circuits imprimés, le contact entre les puces sur notre substrat est de la même taille que les pistes à l'intérieur des puces. À cet égard, beaucoup plus de connexions peuvent être établies dans le substrat, et toutes sont capables de transmettre des données plus rapidement avec une consommation d'énergie moindre.

Le tissu d'interconnexion au silicium (Si-IF) offre un autre avantage supplémentaire. C'est un excellent moyen de briser les systèmes à puce unique de production relativement grands, complexes et inconfortables [système sur puce, SoC], sur lesquels tout repose aujourd'hui, des smartphones aux superordinateurs. Au lieu de SoC, les développeurs de systèmes pourraient utiliser des conglomérats plus petits, plus simples dans la conception et dans la production de copeaux, étroitement interconnectés sur Si-IF. Une telle révolution des chipsets est déjà en marche - AMD, Intel, Nvidia et d'autres sociétés proposent des jeux de chipsets assemblés dans des boîtiers avancés. Un réseau d'interconnexion en silicium étend cette idée en cassant le boîtier du système et en vous permettant d'y inclure l'intégralité de l'ordinateur.

Pour comprendre tous les avantages de l'élimination d'une carte de circuit imprimé, considérez ce qui se passe avec un SoC typique. En raison du développement de l'électronique selon la loi de Moore, sur un centimètre carré de silicium, vous pouvez emballer presque tout ce dont vous avez besoin pour qu'un smartphone fonctionne. Malheureusement, pour de nombreuses raisons liées aux caractéristiques de la carte de circuit imprimé, ce morceau de silicium est placé à l'intérieur d'un boîtier en plastique, parfois 20 fois la taille de la puce elle-même.

La différence de taille entre la puce et le boîtier crée au moins deux problèmes. Premièrement, le poids et le volume d'une puce emballée sont supérieurs à ceux d'un morceau de silicium lui-même. Évidemment, c'est un problème pour tous les appareils qui doivent être petits, fins et légers. Deuxièmement, si un produit fini nécessite plusieurs puces échangeant des données entre elles (et la plupart des systèmes en ont une), la distance que le signal doit couvrir augmente de plus de 10 fois. Il s'agit d'un goulot d'étranglement pour la vitesse et la consommation d'énergie, en particulier lors de l'échange de grandes quantités de données. C'est probablement le plus grand défi pour la mise en œuvre d'applications dépendant des données - graphiques, apprentissage automatique et recherche. Pire encore, les puces dans ces cas sont plus difficiles à refroidir. La dissipation thermique est un facteur limitant en électronique depuis plusieurs décennies.

Mais si ces cas sont si problématiques, pourquoi ne pas s'en débarrasser? À cause du circuit imprimé.

La tâche de la carte de circuit imprimé est de combiner des puces, des composants passifs et d'autres appareils dans un système fonctionnel. Mais cette technologie n'est pas parfaite. Les cartes de circuits imprimés sont difficiles à réaliser parfaitement, même - elles se plient souvent. Les boîtiers de copeaux sont généralement connectés à la carte à l'aide de gouttelettes de soudure, qui fondent et ressoudent pendant la production. Les limites de la technologie de soudage ainsi que la courbure de la surface font que les gouttelettes ne sont pas plus proches que 0,5 mm les unes des autres. En d'autres termes, il ne sera pas possible de placer plus de 400 contacts par centimètre carré. Pour de nombreuses applications, c'est trop peu pour la transmission de puissance et de signal vers et depuis la puce. Par exemple, sur une petite surface occupée par le cristal du processeur Intel Atom, il y a suffisamment d'espace pour des centaines de contacts d'une taille de 0,5 mm et il en faut 300. Les développeurs utilisent des cas pour les cristaux afin que les mathématiques convergent avec le nombre de contacts par unité de surface. Le boîtier prend de minuscules contacts d'une puce de silicium - de 1 à 50 microns de large - et les étend à l'échelle de la carte, 500 microns.

Récemment, l'industrie des semi-conducteurs a tenté de limiter les problèmes associés aux cartes de circuits imprimés en développant des boîtiers avancés avec la technologie d'interposeur au silicium. L'interposeur est une fine couche de silicium sur laquelle un petit nombre de puces de silicium nues sont fixées, connectées les unes aux autres par un grand nombre de contacts. Mais en même temps, l'interposeur avec ses puces doit toujours être caché dans le boîtier et placé sur la carte de circuit imprimé, de sorte que cette option ajoute de la complexité sans résoudre les problèmes restants. De plus, les interposeurs sont nécessairement minces, fragiles et de taille limitée - ce qui signifie qu'il est difficile de créer de gros systèmes dessus.

Nous pensons que la meilleure option serait de se débarrasser complètement des boîtiers et des cartes de circuits imprimés en fixant les puces à un substrat de silicium relativement épais (de 500 microns à 1 mm). Les processeurs, les cristaux de mémoire, les chipsets RF, les modules de contrôle de tension et même les composants passifs tels que les inductances et les condensateurs peuvent être connectés directement au silicium. Comparé au matériau habituel des cartes de circuits imprimés - composition en fibre de verre et époxy FR-4 - le substrat en silicium est solide et il peut être poli jusqu'à un plan presque parfait, de sorte que la courbure n'en a pas peur. De plus, étant donné que les puces et le substrat se dilatent et se contractent lorsque la température change de la même quantité, vous n'avez plus besoin d'une connexion large et flexible entre la puce et le substrat, telle que la soudure.

Les gouttes de soudure peuvent être remplacées par des broches en cuivre micrométriques intégrées dans le substrat. En utilisant la compression thermique - en fait, l'application précise du chauffage et de la pression - les contacts d'entrée / sortie en cuivre des puces peuvent être directement connectés aux broches. Une optimisation approfondie du joint de thermocompression peut nous donner des contacts beaucoup plus fiables que la soudure, et en même temps utiliser moins de matériaux différents.

En éliminant les cartes de circuits imprimés et leurs faiblesses, il sera possible de disposer les ports d'E / S à une distance de seulement 10 microns les uns des autres au lieu de 500 microns. En conséquence, il sera possible de placer 2500 fois plus de ports sur une puce de silicium sans avoir besoin d'utiliser un boîtier.

Encore mieux, le processus de fabrication de semi-conducteurs standard peut être reconfiguré pour fabriquer des schémas de câblage Si-IF à plusieurs niveaux. Leurs pistes peuvent être beaucoup plus fines que sur les cartes de circuits imprimés. Ils peuvent être séparés les uns des autres de seulement 2 microns, et non de 500 microns, comme sur les cartes de circuits imprimés. La technologie vous permet même de placer des puces à une distance de 100 microns les unes des autres, contrairement aux cartes de circuits imprimés, où elle devrait être supérieure à 1 mm. En conséquence, le système Si-IF économise de l'espace, de l'énergie et du temps de déplacement du signal.

De plus, contrairement aux cartes de circuits imprimés et aux matériaux pour les boîtiers de circuits intégrés, le silicium conduit la chaleur assez bien. Les radiateurs peuvent être montés des deux côtés du Si-IF pour éliminer encore plus de chaleur - selon nos estimations, 70% de plus. Et plus la chaleur est évacuée, plus les processeurs peuvent fonctionner rapidement.

Bien que le silicium ait une bonne résistance à la traction et une bonne ténacité, il est légèrement fragile. Heureusement, l'industrie des semi-conducteurs a développé des méthodes pour travailler avec de grands substrats en silicium afin d'éviter la fissuration sur plusieurs décennies. Et après toutes les procédures de production de Si-IF nécessaires, nous nous attendons à ce qu'ils passent la plupart des tests de fiabilité, y compris les tests d'impact, le chauffage cyclique et l'exposition environnementale.

Le silicium cristallin est plus cher que le FR-4. Bien que le coût dépende de nombreux facteurs, le prix au millimètre carré d'une carte de circuit imprimé à 8 couches peut être dix fois inférieur à celui d'une Si-IF à 4 couches. Cependant, notre analyse montre que si vous soustrayez le coût de placement des puces dans les boîtiers et la production complexe des cartes, et prenez en compte les économies d'espace grâce à la technologie Si-IF, la différence de coût sera insignifiante, et dans certains cas, le Si-IF pourrait même être plus rentable.

Réseau de silicium inter-composants par rapport à la carte de circuit imprimé et aux puces du châssis. Au bas du diagramme se trouve une échelle approximative pour comprendre la différence de taille.

Réseau de silicium inter-composants par rapport à la carte de circuit imprimé et aux puces du châssis. Au bas du diagramme se trouve une échelle approximative pour comprendre la différence de taille.Examinons quelques exemples des avantages de l'utilisation de Si-IF pour un système informatique. Dans une étude des conceptions de serveurs, nous avons constaté que l'utilisation de processeurs sans châssis utilisant Si-IF peut doubler les performances des processeurs conventionnels en raison d'une connectivité améliorée et d'une dissipation d'énergie accrue. De plus, la taille de la «carte» de silicium (en l'absence d'un meilleur terme) peut être réduite de 1000 cm

2 à 400 cm

2 . Une telle diminution grave affectera considérablement le volume des bâtiments du centre de données et la taille de l'infrastructure de refroidissement. Quant à l'autre extrémité de l'échelle, nous avons étudié un petit système pour «l'Internet des objets» basé sur le microcontrôleur Arm. Dans ce cas, l'utilisation de Si-IF réduit non seulement la taille de la planche de 70%, mais aussi son poids, de 20 à 8 grammes.

En plus de réduire les systèmes existants et d'augmenter la productivité, Si-IF permettra aux développeurs de créer des ordinateurs qui autrement seraient impossibles à construire - ou ce serait très peu pratique.

Dans un serveur puissant typique, la carte coûte 2 à 4 processeurs. Certains projets avec une charge de calcul élevée nécessitent plusieurs serveurs. Lors du déplacement de données entre différents processeurs et cartes, des retards et des goulots d'étranglement se produisent. Mais que faire si tous les processeurs étaient placés sur un seul substrat de silicium? Ils pourraient être intégrés si étroitement que l'ensemble du système fonctionnerait comme un seul grand processeur.

Ce concept a d'abord été proposé par Gene Amdahl dans sa société Trilogy Systems. Mais Trilogy n'a pas réussi, car leur processus de production n'a pas produit une qualité suffisante pour le système de travail. Lors de la fabrication d'une puce, il y a toujours la possibilité de défauts, et avec une augmentation de sa surface, la probabilité de mariage augmente de façon exponentielle. Lorsque la taille de la puce est comparable à une assiette, il est presque garanti qu'elle tue tout le système du mariage.

Mais si vous avez un réseau d'interconnexion en silicium, vous pouvez commencer avec les chipsets que nous pouvons déjà fabriquer sans défauts, puis les combiner en un seul système. Notre équipe de chercheurs de l'Université de Californie à Los Angeles et de l'Université de l'Illinois à Urbana-Campaign a développé un tel système avec un substrat contenant 40 GPU. Dans les simulations, il a accéléré les calculs de plus de 5 fois et consommé de l'énergie de 80% de moins que le système équivalent de 40 GPU créé à l'aide de boîtiers multi-puces avancés et de cartes de circuits imprimés.

Les résultats ont été convaincants, même si la tâche n'a pas été facile. Nous avons dû prendre en compte de nombreuses restrictions, notamment: la quantité maximale de chaleur évacuée du substrat; comment faire pour que le GPU échange des données le plus rapidement possible; comment fournir de l'énergie sur toute la surface du substrat.

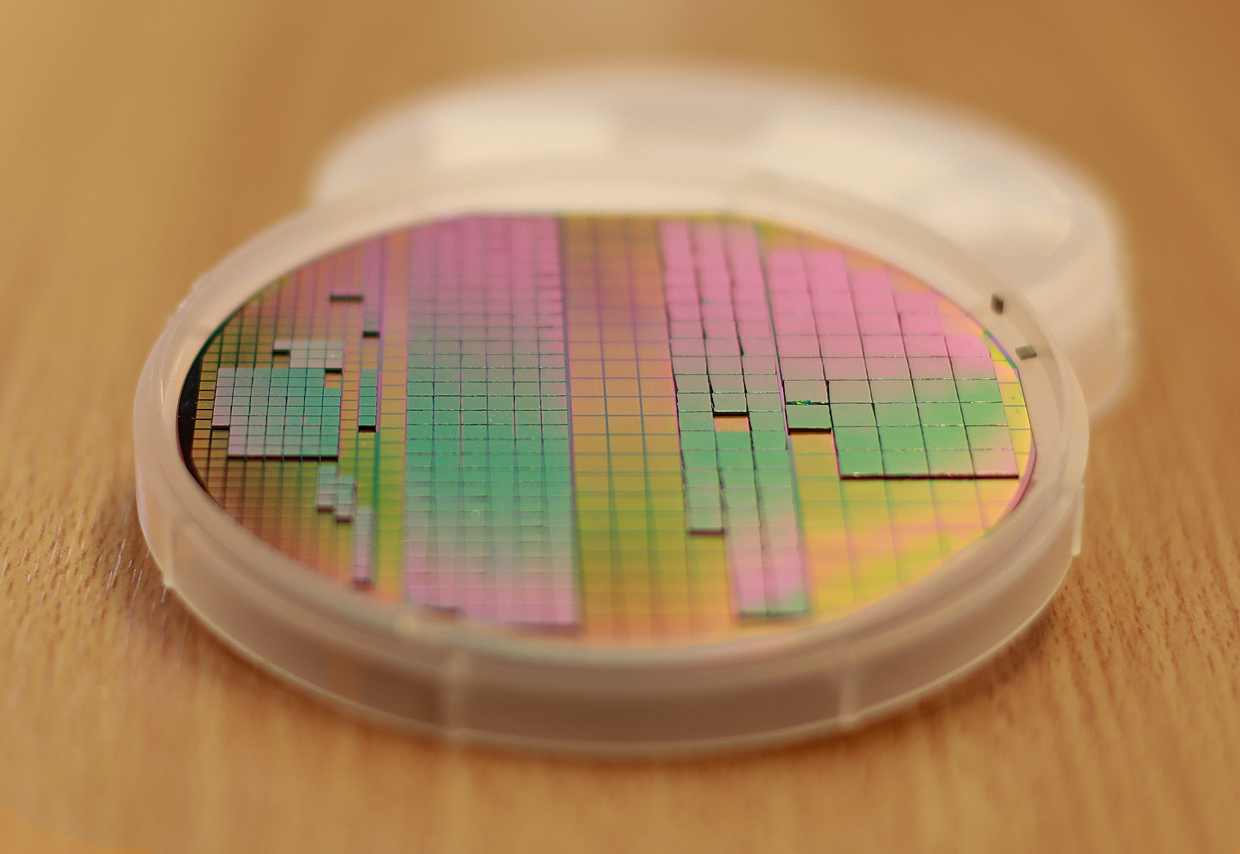

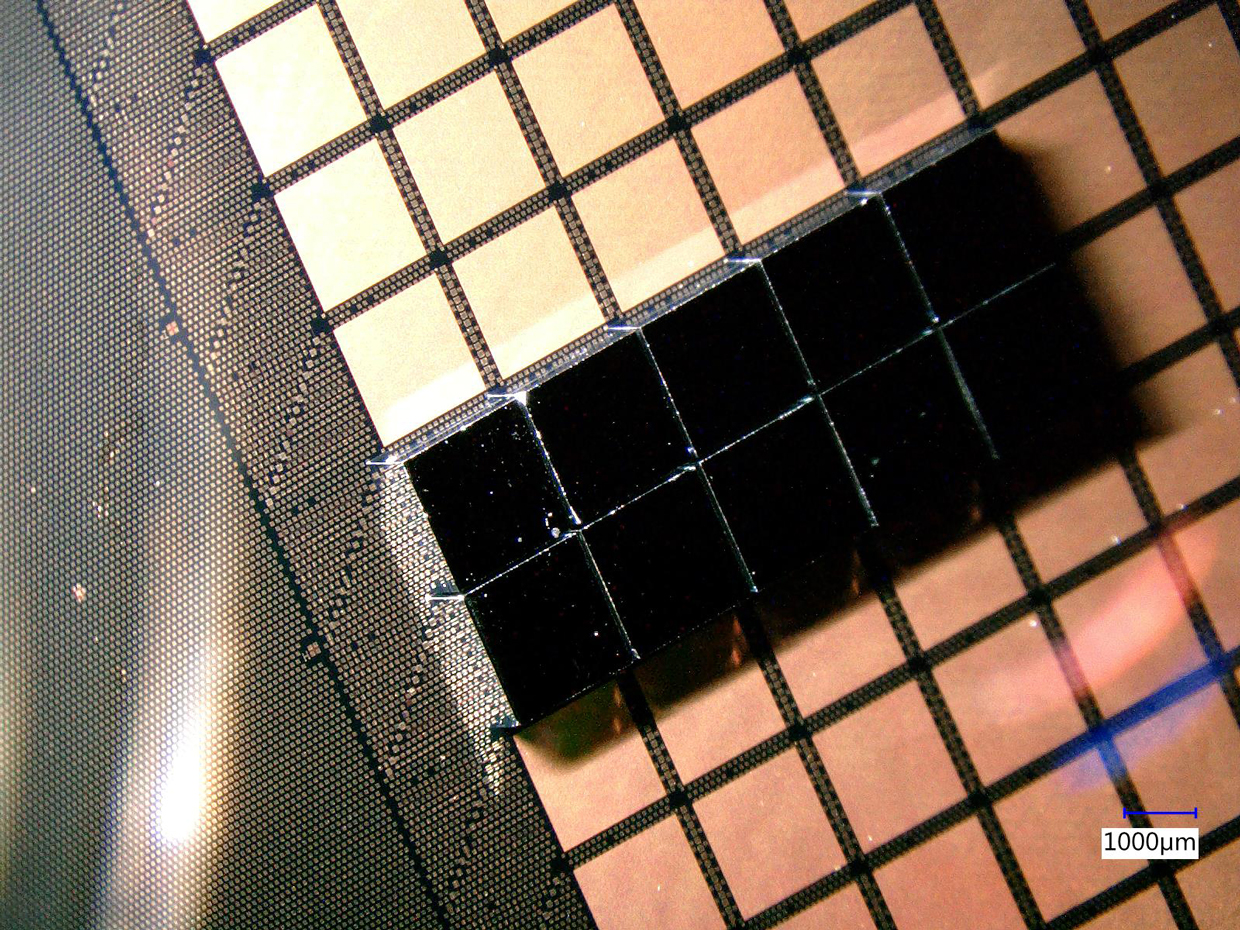

Dilets, ou chipsets, intégrés sur un réseau silicium interconnecté, substrat 100 mm. Les dilets, contrairement aux puces sur une carte de circuit imprimé, peuvent être placés à une distance de 100 microns les uns des autres

Dilets, ou chipsets, intégrés sur un réseau silicium interconnecté, substrat 100 mm. Les dilets, contrairement aux puces sur une carte de circuit imprimé, peuvent être placés à une distance de 100 microns les uns des autresLa principale limitation était la nutrition. Avec une tension de fonctionnement de puce standard de 1 V, les pistes minces du substrat devraient consommer 2 kW. Au lieu de cela, nous avons augmenté la tension à 12 V, réduisant ainsi le courant et la puissance. Pour ce faire, il était nécessaire de répartir les régulateurs de tension et les condensateurs à travers le substrat, et ils ont pris la place qui pourrait autrement être donnée à des GPU supplémentaires. Inspirés par les premiers résultats, nous assemblons maintenant un prototype de système informatique que nous espérons terminer d'ici la fin de 2020.

Un réseau de silicium d'interconnexion peut jouer un rôle dans une tendance importante de l'industrie informatique: la division du SoC en ensembles intégrés de daylets [diélectrique - de «die», crystal et «–let», prefix de réduction / approx. transl.], ou chiplets (nous préférons les appeler des daylets, car cela met l'accent sur leur essence en tant que cristaux de silicium nus, leur petite taille et, éventuellement, une fonctionnalité incomplète sans d'autres daylets Si-IF). Au cours des deux dernières décennies, le désir d'augmenter les performances et de réduire les coûts a convaincu les développeurs de remplacer les jeux de puces par des SoC intégrés encore plus grands. Et, malgré leurs avantages, les SoC présentent un nombre suffisant d'inconvénients.

Premièrement, le SoC est une grande puce et, comme déjà mentionné, il est assez difficile d'atteindre des indicateurs acceptables du pourcentage de rejets dans la production de grandes puces, en particulier dans les industries de semi-conducteurs avancées (rappelons que le pourcentage de rejets croît de façon exponentielle avec l'augmentation de la surface des puces). Un autre inconvénient du SoC est le coût élevé de la conception et du démarrage de la production; aux États-Unis, par exemple, un masque photolithographique peut coûter 2 millions de dollars, ce qui rend l'option SoC indisponible pour la plupart des systèmes. De plus, tout, même un petit changement dans le schéma ou la mise à jour du processus de production nécessitera un traitement important de l'ensemble du SoC. Enfin, l'approche SoC essaie d'intégrer tous les sous-systèmes dans un processus de production, même lorsque certains de ces sous-systèmes pourraient être améliorés dans un autre processus. En conséquence, rien dans SoC n'atteint la plus haute efficacité ou vitesse possible.

L'intégration sur Si-IF sans la participation de boîtiers évite tous ces problèmes, tout en conservant la petite taille et la vitesse du SoC, tout en offrant des avantages et des coûts de développement. Il décompose le SoC en ses composants et recrée un système sur un substrat, système - sur - Si-IF (SoIF).

Un tel système se compose de daylets produits indépendamment et connectés via Si-IF. La distance minimale des dilets de séparation (dizaines de micromètres) est comparable à la distance entre deux blocs fonctionnels SoC. Le câblage sur Si-IF est le même que celui utilisé au niveau supérieur du SoC, donc la densité des composés est comparable.

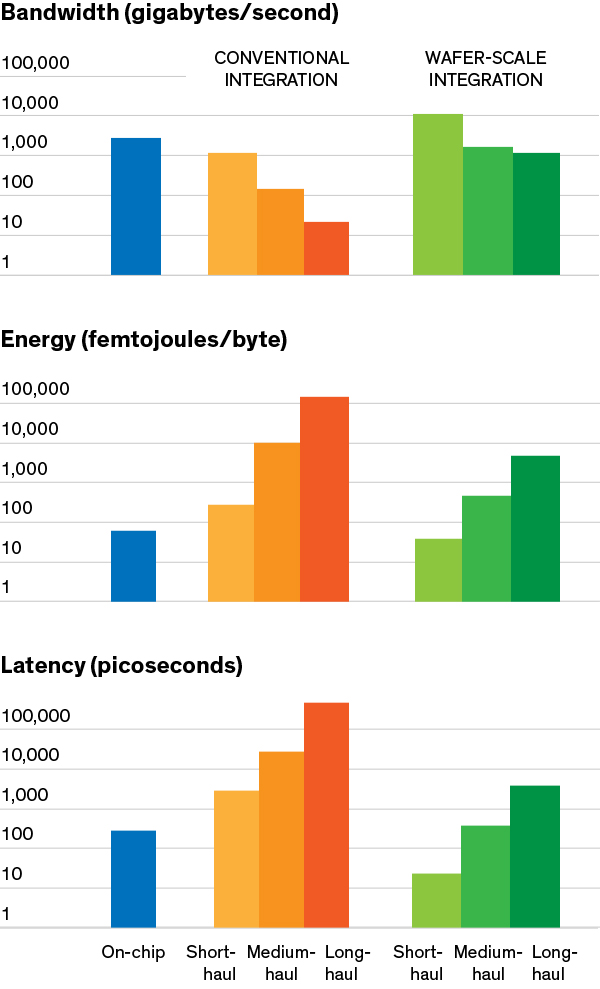

De haut en bas: bande passante (Go / s), consommation d'énergie (fJ / B), délai (ps).

De haut en bas: bande passante (Go / s), consommation d'énergie (fJ / B), délai (ps).

Bleu - système sur une puce, nuances de rouge - intégration normale, nuances de vert - système sur substratLes avantages de SoIF sur SoC sont dus à la taille du retard. Les petites suppressions sont moins chères à produire que les grands SoC car elles ont un taux de rejet inférieur en raison de leur petite taille. Dans SoIF, seul le substrat lui-même a une grande taille. Mais il est peu probable qu'elle ait un problème avec le mariage, car il est composé de plusieurs couches faciles à fabriquer. La plupart des pertes dues aux défauts sont dues à des défauts dans les couches de transistor ou dans les couches métalliques inférieures superdenses, et c'est le cas avec un réseau de silicium interconnecté.

De plus, SoIF aura tous les avantages dans la poursuite desquels l'industrie passe aux chipsets. Par exemple, la transition de SoIF vers le prochain processus de fabrication devrait être plus facile et moins coûteuse. Chaque dylet peut avoir sa propre technologie de production, et seuls les dylets qui en ont vraiment besoin peuvent être mis à jour. Et les suppressions qui ne bénéficient pas particulièrement de transistors réduits n'auront pas besoin d'être modifiées. Une telle intégration hétérogène vous permet de créer une toute nouvelle classe de systèmes mélangeant des mélangeurs de différentes générations et technologies qui ne sont généralement pas compatibles avec CMOS. Par exemple, notre groupe a récemment démontré la combinaison d'un cristal de phosphure d'indium avec SoIF comme exemple d'utilisation potentielle dans des circuits haute fréquence.

Étant donné que les dilettes seront produites et vérifiées avant la connexion à SoIF, elles peuvent être utilisées dans différents systèmes, ce qui leur permettra d'économiser considérablement. En conséquence, le coût total de développement et de fabrication de SoIF peut être 70% inférieur à celui de SoC. Cela sera particulièrement vrai pour les grands systèmes produits en petits lots - comme c'est le cas pour les industries de l'aérospatiale et de la défense, où il n'y a de demande que pour des lots de l'ordre de plusieurs centaines ou milliers d'unités. Les systèmes sur mesure seront également plus faciles à réaliser chez SoIF, car cela réduit à la fois les coûts et le temps de développement.

Nous pensons que de tels avantages en termes de coûts et de diversité peuvent conduire au début d'une nouvelle ère d'innovation dans laquelle de nouveaux matériels seront disponibles pour un plus grand nombre de concepteurs, de startups et d'universités.

Au cours des dernières années, nous avons fait des progrès importants dans la technologie d'intégration Si-IF, mais il reste beaucoup à faire. Tout d'abord, il est nécessaire de montrer un procédé de production de Si-IF faiblement défectueux commercialement viable.

La création de substrats à l'échelle Si-IF peut nécessiter des innovations en lithographie sans masque. La plupart des systèmes lithographiques qui existent aujourd'hui peuvent fabriquer des substrats de 33x24 mm. En conséquence, nous avons besoin d'un système capable de délivrer un substrat d'un diamètre de 300 mm.Nous avons également besoin de mécanismes pour vérifier les daylets nus et Si-IF. L'industrie s'oriente déjà vers le test des cristaux nus, alors que les fabricants de puces optent pour des cheatlets dans des packages avancés et une intégration en trois dimensions.Ensuite, nous avons besoin de nouveaux radiateurs ou d'autres stratégies de dissipation thermique qui utilisent une bonne conductivité thermique du silicium. Mes collègues de l'Université de Californie et moi développons une solution intégrée de refroidissement et de nutrition des substrats appelée PowerTherm.De plus, pour l'assemblage de systèmes complets, vous aurez besoin de cadres, d'attaches, de connecteurs et de câbles.Nous devrons également apporter quelques modifications à la méthodologie de développement afin que l'une des promesses SoIF devienne réalité. Si-IF est un substrat passif dans lequel il n'y a qu'un seul conducteur. Par conséquent, les connexions inter-vols doivent être courtes. Pour des pistes plus longues reliant des dilets éloignés, nous avons besoin de dilets intermédiaires qui transmettent les données plus loin dans la chaîne. Il faudra revoir les algorithmes de conception responsables de la disposition des éléments et de la finalité des contacts afin qu'ils profitent pleinement de ce type d'intégration. Et nous devrons également développer de nouvelles façons d'explorer diverses architectures de systèmes qui tirent parti de l'hétérogénéité et de la mise à jour de SoIF.Nous devrons également tenir compte de la fiabilité des systèmes. Si un dylet s'avère défectueux après l'avoir fixé ou échoue pendant le fonctionnement, il sera très difficile de le remplacer. Par conséquent, dans SoIF, en particulier dans les grands, il sera nécessaire de créer une tolérance aux pannes. Il peut être implémenté au niveau du réseau ou au niveau de la dayleet. Au niveau du réseau, il sera nécessaire d'assurer le passage du signal en contournant les daylets défaillants. Au niveau du daylet, diverses astuces avec redondance physique peuvent être envisagées, par exemple, l'utilisation de plusieurs broches en cuivre pour chacun des ports d'E / S.Bien entendu, les avantages d'un assemblage de daylets dépendent de la disponibilité de daylets utiles qui peuvent être intégrés dans le système. Jusqu'à présent, l'industrie trie le type de dilets à produire. Vous ne pouvez pas simplement créer une daylet pour chaque sous-système dans SoC, car certaines des daylets seront trop petites. Une approche prometteuse est l'utilisation du traitement statistique des circuits SoC existants et des cartes de circuits imprimés afin de trouver des fonctions qui "ont tendance" à être physiquement plus proches les unes des autres. Si ces fonctions ont les mêmes technologies de production et les mêmes cycles de mise à jour, elles doivent être intégrées dans une seule daylet.Cette liste de problèmes peut sembler très longue, mais les chercheurs travaillent déjà sur certains d'entre eux dans le cadre du programme CHIPS (Common Heterogeneous Integration and IP Reuse Strategies) de la Defense Advanced Research Projects Agency, ainsi qu'avec des consortiums industriels. Et si nous pouvons résoudre ces problèmes, cela nous aidera sérieusement à maintenir l'héritage de la loi de Moore d'une manière plus petite, plus rapide et moins coûteuse.