Boris Tsirlin et Alexander Kushnerov

30/10/2019

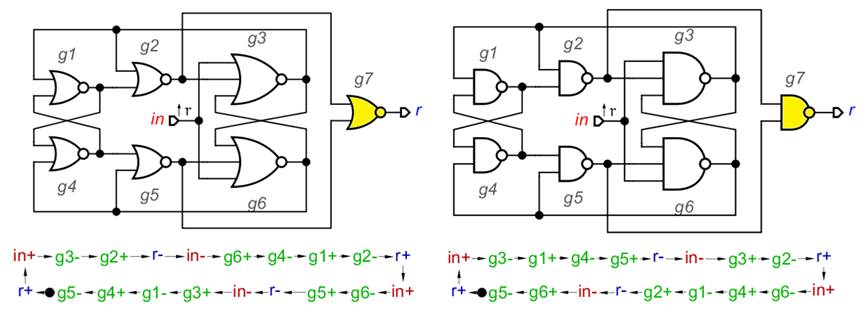

Il n'est pas difficile pour un concepteur de circuits expérimenté de découvrir un circuit familier, quelle que soit sa forme. Dans cet article, nous montrons que les deux circuits à transistors des brevets sont une variante du déclencheur de comptage asynchrone (AST). Par rapport au circuit standard, certains transistors sont absents des brevets. Cela peut être considéré comme un dysfonctionnement. Nous montrerons que si le même défaut se produit dans le circuit standard, il continue de fonctionner correctement. Un AST implémenté uniquement sur les éléments OR-NOT [1] ou uniquement sur les éléments AND-NOT est appelé déclencheur Harvard. Les deux variantes des schémas sont illustrées à la Fig. 1, où g7 est un indicateur d'achèvement transitoire. À l'avenir, nous ne l'envisagerons pas. Dans la Fig. La figure 1 montre également les graphiques de transition de signal (STG) [2] intégrés à Workcraft [3].

Fig. 1. Déclencheur de comptage asynchrone (AST) et son STG.

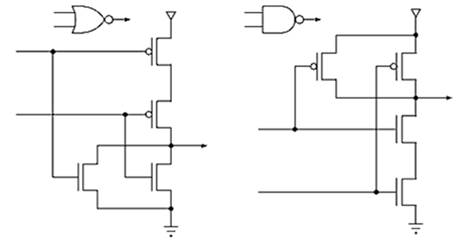

Notez que dans les deux versions de l'AST, il existe trois paires d'éléments (g1, g2), (g4, g5) et (g3, g6) qui ont une entrée commune. Circuits de transistor des éléments 2I-NOT et 2OR-NOT représentés sur la Fig. 2. Les éléments à trois entrées sont disposés de manière similaire et contiennent 6 transistors.

Fig. 2. Circuits à transistors des éléments 2I-NOT et 2OR-NOT.

Nous prenons deux éléments 2OR-NOT et sélectionnons à chaque entrée, où le transistor p-MOS est connecté à Upit. Connectez ces entrées ensemble et connectez-vous à la terre (log. 0). Les deux transistors s'ouvriront et la tension à leurs drains sera égale à Upit. Est-ce suffisant pour connecter en toute sécurité les drains et remplacer les deux transistors par un, comme indiqué sur la Fig. 3? Non. Vous devez vérifier ce qui se passe si vous vous connectez à l'entrée partagée. 1. Les sorties des deux éléments seront connectées à la terre, et nous aurons un circuit en pont de quatre transistors p-MOS. Pour les deux entrées restantes, nous avons quatre combinaisons 0 et 1. Il est facile de montrer que dans aucune d'entre elles il n'y a de court-circuit entre Upit et la masse.

Fig. 3. Deux éléments 2OR-NOT partageant une entrée commune.

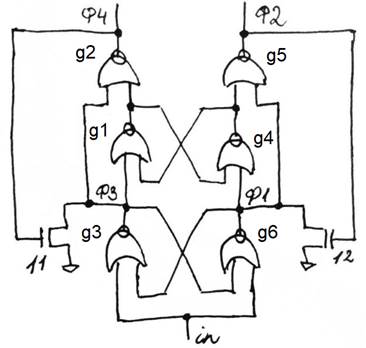

Nous considérons maintenant le circuit de distribution d'impulsions [4] de la Fig. 4. À l'aide de la Fig. 3, nous pouvons redessiner ce diagramme comme le montre la Fig. 5. Il est déjà possible de reconnaître AST sur la Fig. 1, cependant, les éléments g3 et g6 ont 3 entrées.

Fig. 4. Le schéma du distributeur d'impulsions de [4].

Fig. 5. Une variante du circuit de la Fig. 4.

Les grilles des transistors 11 et 12 peuvent être considérées comme des entrées d'éléments 3OR-NOT dans lesquels le troisième transistor p-MOS est court-circuité. Cela affecte-t-il le bon fonctionnement du circuit? Considérons l'ordre d'apparition des signaux dans, g2 et g6 à l'entrée de l'élément g3. Pour ce faire, supprimez tous les autres signaux dans le STG correspondant de la Fig. 1 comme le montre la Fig. 6.

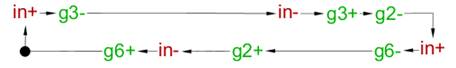

Fig. 6. STG pour OU NON. Signaux en, g2, g6 et g3.

Étant donné que le troisième transistor p-MOS est court-circuité, la commutation g3 + peut se produire après la commutation entre et g6- (dans n'importe quel ordre) sans autoriser la commutation g2-. Cependant, comme on peut le voir sur la Fig. 6, dans la section de g2 + à g2-, il n'y a que in et g6 +, par conséquent, la commutation interdite g3 + ne se produit pas. Avant de commuter g2 +, l'élément g3 est déjà à 0, et à son entrée g6 est toujours à 0, c'est-à-dire Le premier transistor p-mos est ouvert. La commutation de g2 + ouvre le transistor 11 et devrait couper le transistor p-MOS court-circuité. Cela ne se produit d'ailleurs pas, la commutation ouvre le deuxième transistor p-MOS. Ainsi, à travers deux transistors p-MOS ouverts et un transistor ouvert 11, le courant commence à circuler d'Upit vers la masse. Cela continue pendant une courte période jusqu'à ce que le prochain commutateur g6 + ferme le premier transistor p-MOS. Pendant ce temps, le transistor 11 fournit 0 à la sortie de g3. Comment exactement? Supposons que la résistance des transistors p-MOS et n-MOS ouverts soit identique et égale à R, puis après avoir commuté la tension sur les sauts g3 de 0 à (1/3) Upit, mais c'est l'idéal. Dans la pratique, il existe une certaine capacité parasite entre g3 et la masse, la tension à laquelle augmente en douceur et peut ne pas atteindre (1/3) Upit. D'une manière ou d'une autre, cette tension sera inférieure à (1/2) Upit et signifie un journal. 0. Pour le transistor 12, tout est similaire, il fournit un court instant 0 à la sortie de g6. Ainsi, les retards des éléments g6 et g3 déterminent deux périodes de temps où le déclencheur consomme un grand courant sensiblement égal à Upit / (3R).

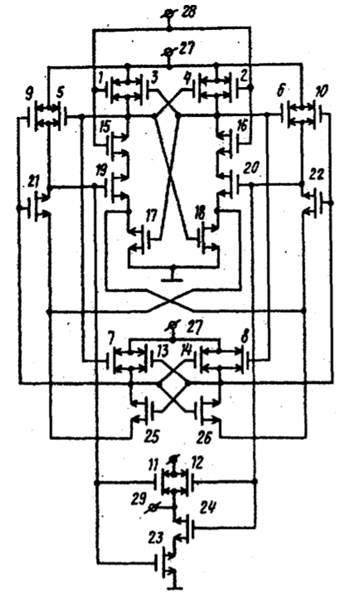

Considérons maintenant le circuit de déclenchement de comptage [5] de la Fig. 7. Ici, les transistors 11, 12, 24, 23 forment l'élément 2I-NOT, qui, apparemment, est un indicateur d'AST sur la Fig. 1. Un autre élément 2I-NOT est formé par les transistors 7, 13, 25 et 18. Prenons attention au fait que le transistor 18 est connecté à la masse et de manière similaire à l'exemple de la Fig. 3, est commun aux trois éléments ET NON. Le deuxième élément 2I-NOT, qui comprend le transistor 18, est formé par les transistors 5, 9, 21, et le troisième est 3I-NOT sur les transistors 2, 4, 16, 20. En parallèle avec les transistors 2 et 4, il devrait y avoir un troisième transistor p-MOS mais il est absent. Le circuit de la Fig. 7 est symétrique, pour une meilleure compréhension, nous le redessinons comme le montre la Fig. 8.

Fig. 7. Schéma du déclencheur dénombrable de [5].

Fig. 8. Une variante du circuit de la Fig. 7.

Y aura-t-il des sorties g3 et g6 sur la Fig. 8 commuter correctement si le troisième transistor p-mos en parallèle est manquant? Cela sera compris après analyse du STG sur la Fig. 9, qui, comme dans le cas précédent, est obtenue à partir du STG correspondant de la Fig. 1 en supprimant tous les signaux sauf en, g2, g6 et g3.

Fig. 9. STG pour NAND. Signaux en, g2, g6 et g3.

L'élément g3 est 3I-NOT, donc après avoir commuté en +, g6 + et g2 + (dans n'importe quel ordre), g3- changera. N'importe lequel des commutations inverses d'entrée, g6- ou g2- devrait provoquer le basculement g3 +. Cependant, g2- ne peut pas ouvrir le transistor p-MOS manquant, donc g3 restera à 0 et attendra que l'entrée ou g6- bascule. Comme on peut le voir sur la Fig. 9, sur la section de g3- à g3 +, il n'y a pas de commutation g2- et le transistor p-MOS n'est pas nécessaire ici. En revanche, ce transistor devrait fournir un journal. 1 à g3 en entrée et g6 commutent arbitrairement. Considérez dans la Fig. 9ème section de g3 + à g2 +. La commutation g2- ferme le transistor 19. Ensuite, la commutation in + ferme le transistor 1 et ouvre le transistor 15. L'élément g6 reste à 1, c'est-à-dire le transistor 17 est ouvert et le transistor 3 est fermé. Ainsi, in + déconnecte g3 de la terre et d'Upit. Cependant, le journal est conservé sur g3. 1, car en pratique il existe une capacité parasite entre g3 et la masse, qui est chargée jusqu'à Upit. La commutation g6- ouvre le transistor 3 et connecte cette capacité à Upit. Pour la seconde moitié du schéma, tout est similaire. Ainsi, les retards des éléments g6 et g3 déterminent le temps pendant lequel l'état est stocké sur le réservoir. En pratique, il est important que le courant de fuite des transistors 19 et 20 soit faible, sinon la capacité peut se décharger en dessous de (1/2) Upit dans le temps imparti.

Par rapport à l'AST standard de la Fig. 1, dans les schémas de la Fig. 5 et sur la Fig. 8, la fonction de mise à 1 élément 3 OU NON et la fonction de réinitialisation à 0 de l'élément 3 OU NON endommagé. Cela signifie que l'AST standard continuera de fonctionner correctement, même si un dysfonctionnement correspondant se produit dans les éléments g6 et g3. Pour un circuit standard (sans g7), 28 transistors sont nécessaires. Pour les circuits de la Fig. 4 et sur la Fig. 7 (sans transistors 11, 12, 24, 23), vous avez besoin de 23 et 22 transistors, respectivement. Si vous retournez les transistors p-MOS manquants, ces circuits fonctionneront de manière plus fiable. Le nombre minimum de transistors dans le circuit de la Fig. 7 ne signifie pas nécessairement qu'il est meilleur que le circuit de la Fig. 4 et meilleur circuit sur la Fig. 1. Outre le nombre de transistors et la consommation actuelle, il existe d'autres paramètres importants, par exemple,

- complexité d'un circuit supplémentaire pour établir les états initiaux

- capacité de charge (taux de rechargement de la capacité de charge)

- taux de sortie de l'état métastable

- nombre et valeurs des capacités parasites

- nombre et valeurs des courants de fuite

Une analyse comparative de ces paramètres, ainsi qu'une discussion des schémas AST mis en œuvre sur d'autres éléments, dépassent le cadre de cet article.

Littérature

[1] GT Osborne, "Etage de registre de compteur binaire asynchrone avec bascule et porte utilisant une pluralité de circuits NOR interconnectés." Brevet US3139540, 30 juin. 1964.

[2] L. Ya. Rosenblum et A. V. Yakovlev, «Sur une nouvelle forme graphique pour illustrer l'essence de l'invention», Issues of Invention, n ° 11, pp. 36-40, 1988.

[3] https://workcraft.org

[4] V. I. Goryachev, B. M. Mansurov, Ya. D. Martynenko et R. G. Talibov, «Distributeur d'impulsions à quatre phases». Certificat de droit d'auteur SU342299, 14/06/1972.

[5] V. I. Varshavsky, N. M. Kravchenko, V. B. Marakhovsky et B. S. Tsirlin, «Counting trigger on CMOS transistors». Certificat de droit d'auteur SU1398069, 23.05.1988.