Cette semaine, Intel a partagé ses plans à long terme pour l'introduction de nouveaux processus de fabrication. Vers 2029, Intel

prévoit d'introduire une technologie de processus aux normes 1,4 nm. Après 10 ans, l'équipe de direction de l'entreprise ne sera probablement plus la même qu'aujourd'hui. Donc, ces plans rappellent quelque peu subtilement la parabole de Khoja Nasreddin sur l'âne bien lu, le khan et le professeur de l'animal en la personne de Khoja lui-même. À midi, l'accusé n'est peut-être pas là. Mais ce n'est pas ça. Planifié, nous acceptons ensuite comme guide d'action.

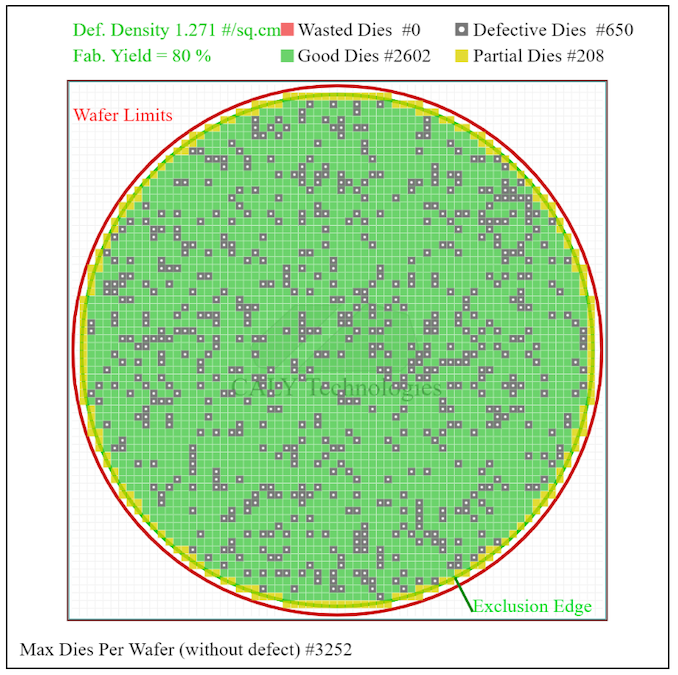

Dans les camps des principaux concurrents des semi-conducteurs, il y a un peu plus de clarté, ce qui est confirmé par la production risquée de puces TSMC avec des normes de 5 nm (

aujourd'hui le taux de défaut n'est que de 20% à la norme de 3-8% pour les cristaux d'une surface de 17,92 mm

2 , pour les puces) AMD Zen 2 aura un niveau de rejet plus élevé - jusqu'à 60%). Cependant, avant la sortie des processeurs AMD aux normes 5 nm, au moins un an et demi passera.

/ image du site AnandTech

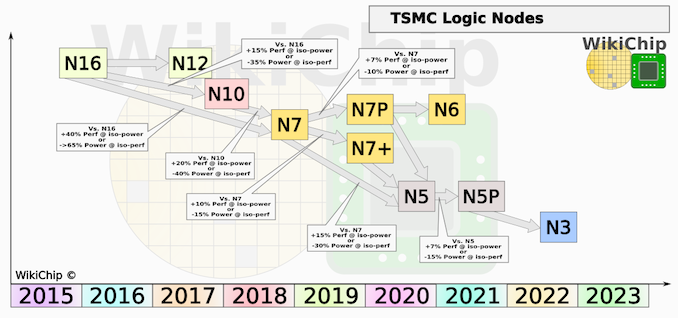

/ image du site AnandTechL'année prochaine, à partir du deuxième trimestre, la technologie de processus TSMC avec des normes de 5 nm sera utilisée pour la production en série de SoC sur des cœurs ARM. En 2022, TSMC commencera évidemment la production risquée de puces 3 nm (quoi que signifient ces nanomètres), et dans quelques années, la société promet de commencer la production de solutions 2 nm. Ce sera en 2024-2025, soit deux à trois ans plus tôt qu'Intel introduira la même technologie de processus.

Pour Samsung, les processus aux normes 5 nm et 4 nm seront l'

évolution de la technologie des processus 7 nm, qui se traduira par une petite réduction progressive des étapes de métallisation sous les éléments FinFET tels que les canaux et les portes. En général, la structure des transistors (le nombre de bords) restera la même que la structure de la cellule SRAM ne changera pas. Samsung commencera la production de puces en utilisant la technologie de traitement 4 nm dans le domaine de 2021. La même année, la société promet de démarrer une production risquée en utilisant une technologie de processus 3 nm. Et certaines sources sud-coréennes

affirment que cela pourrait arriver dès 2020, ce qui semble peu probable.

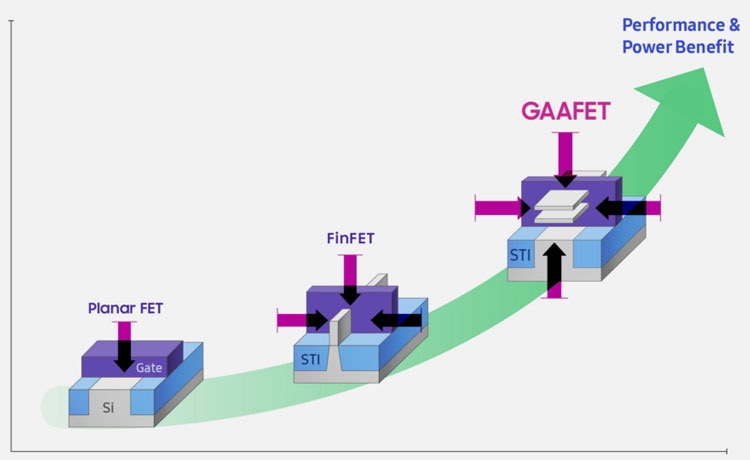

Dans cet article, nous nous intéressons au fait que, jusqu'à la technologie de traitement à 4 nm, Samsung et, évidemment, Intel et TSMC utiliseront des transistors FinFET - des ailettes de portes hautes, dans lesquelles des crêtes de canaux verticaux s'introduisent et se percent. Dans de tels transistors, le champ électromagnétique de grille pénètre dans les canaux de trois côtés, et deux ou trois canaux dans chaque transistor fournissent au total le courant nécessaire au fonctionnement de la valve.

/ Image Samsung

/ Image SamsungÀ partir de la technologie de processus 3 nm, Samsung mettra fin à cette pratique. Le concept FinFET cessera de fonctionner comme auparavant. Les grilles de transistor FinFET seront trop petites et ne pourront pas commuter les transistors. La nécessité de réduire encore la tension d'alimentation des transistors ne fera qu'aggraver cette situation. Par conséquent, pour la technologie de traitement à 3 nm, un transistor avec une porte en anneau GAA (Gate-All-Around) (entourant) sera

introduit .

/ Image Samsung

/ Image SamsungSamsung a donné au nouveau transistor le nom commercial MBCFET (Multi Bridge Channel FET). En pratique, c'est le développement de l'idée d'un transistor,

créé conjointement par des chercheurs d'IBM, de Samsung et de GlobalFoundries. Il a été supposé qu'un transistor de structure similaire serait impliqué dans la transition vers une technologie de processus avec des normes de 5 nm. Mais en réalité, cette structure de valve n'apparaîtra dans les puces qu'avec le début de la production de 3 nm de Samsung. Le transistor MBCFET sera composé de canaux disposés horizontalement les uns sur les autres sous la forme de nanopages, plutôt que de crêtes verticales, comme dans FinFET. Les caractéristiques des transistors MBCFET seront contrôlées de manière pratique à la fois en faisant varier le nombre de pages situées l'une au-dessus de l'autre et en modifiant la largeur de la page. Chaque page est un canal. La somme de ces variables déterminera quel transistor nous avons: puissant et rapide, ou faible, mais faible puissance. Il y aura plus de deux gradations - de cinq à sept.

/ Image Samsung

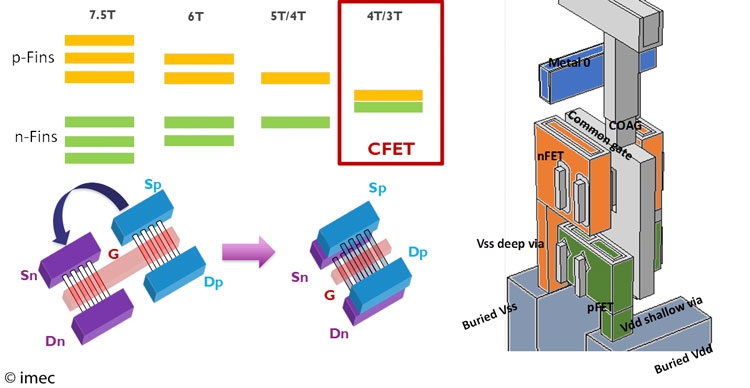

/ Image SamsungLa chose la plus intéressante, au nom de laquelle cette note a été conçue, est que le transistor MBCFET ne peut apparaître que dans le cadre de la technologie de processus 3 nm, et la technologie de processus avec des normes 2 nm nécessitera à nouveau des changements dans la structure du transistor. Un tel nouveau transistor sous le nom de Forksheet a été proposé par le centre de recherche belge Imec. Pour la première fois, les représentants de l'Imec ont

parlé en détail de la structure d'un transistor avec des pages (nano) séparées ce printemps lors d'un événement annuel. Mais vous ne pouvez pas nourrir le rossignol de fables. Nous le ressentirions. Vous ne le ressentez pas encore, mais les Belges ont effectué une simulation du transistor Forksheet sur TCAD, qui a été

signalée il y a trois jours.

Avant d'examiner les données, nous expliquons que le transistor Forksheet est une modification du transistor avec des nanopages - ce même MBCFET ou Gate-All-Around, si nous ignorons les termes Samsung. L'ailette d'obturation verticale du transistor Forksheet est légèrement plus large que celle du MBCFET, mais les nanopages des canaux du transistor sont divisées en deux et séparées par une couche diélectrique. En fait, un transistor MBCFET avec un coup de poignet se transforme en une paire de transistors complémentaires de transistors de type p et n.

La structure proposée détruit une barrière sérieuse dans le scellement des transistors sous forme de complexité pour rapprocher le plus possible les transistors p et n et en même temps éviter l'influence négative mutuelle des grilles.

Évidemment, l'approche proposée augmentera la densité des transistors sur la puce, mais la modélisation a montré que les performances et la consommation d'énergie s'améliorent également. Le passage à un transistor avec des pages séparées réduira la zone cristalline à 20%, et en réduisant les capacités parasites et les fuites, les performances des appareils électroniques augmenteront jusqu'à 10%. Si vous n'augmentez pas la fréquence, vous pouvez réduire la consommation d'énergie jusqu'à 24%.

En stock, Imec dispose d'une autre

technologie qui peut encore augmenter la densité des transistors. Il peut être appliqué à la fois au stade de la production de puces de 3 nm et avec des normes de production inférieures. L'idée est de faire une paire de transistors complémentaires les uns sur les autres. Cette opération apparemment simple promet de réduire de 50% la taille de la cellule logique standard et de la cellule SRAM. Les idées bien développées et partiellement testées sur les modèles se terminent ici.

Le passage à une technologie de traitement à 1 nm peut également nécessiter une nouvelle structure de transistor. Dans le même temps, il faut se rappeler que les ingénieurs trouvent souvent possible d'étirer leur plaisir - de proposer quelque chose comme ça pour faire un autre pas en avant sur les vieilles béquilles.