Alexander Kushnerov

18/12/2019

Même un ingénieur expérimenté peut parfois avoir du mal à acheminer le circuit afin que les pistes (ou fils) n'interfèrent pas avec son bon fonctionnement. Dans une première approximation, la disposition et le nombre de nœuds, quels fils sont connectés à chaque nœud et la longueur des fils après branchement, affectent la qualité du câblage. Si nous considérons la longueur du fil comme un retard, le bon fonctionnement des circuits numériques asynchrones peut ne pas dépendre des retards de certains fils. À l'avenir, nous appellerons ces fils sûrs, et la ramification de ces fils - complètement sûrs (FGP). Dans cet article, nous montrerons comment un circuit universel de douze transistors peut sécuriser certaines branches.

Considérons le schéma dit «papillon» [1], [2] montré sur la Fig. 1. Ce circuit génère des impulsions disjointes p et q, qui peuvent être utilisées pour contrôler les transistors de puissance. Tampons sur la Fig. 1 indique des fils sûrs. Le retard de tous les autres fils est supposé être nul. La pause entre les impulsions est définie par les retards des tampons wy et wz. À l'avenir, nous n'utiliserons pas le tampon pour indiquer le retard d'un élément. Les fils et les branches de tous les circuits de cet article ont été testés pour la sécurité (persistance de sortie) dans Workcraft [3]. Des graphiques de transition de signal (STG) ont été obtenus à partir de circuits en résolvant des conflits CSC. Les illustrations montrent des STG simplifiés où les signaux de tampon sont supprimés. Diagramme de temps (TD) sur la Fig. 1 est construit selon le STG correspondant.

Fig. 1. Le circuit «papillon», ses STG et TD sous l'hypothèse que les retards dans les fils sont nuls.

Fig. 1. Le circuit «papillon», ses STG et TD sous l'hypothèse que les retards dans les fils sont nuls.D'après la théorie [1], [2], il est connu que le circuit du déclencheur RS est sensible aux retards dans les fils dans le couplage croisé. C'est pourquoi les tampons dans les liaisons croisées de la Fig. 1 manquant. Ainsi, les deux éléments déclencheurs doivent être à une distance minimale l'un de l'autre. Si cela est difficile à faire, deux éléments peuvent être remplacés par un élément complexe avec rétroaction. Par exemple, les éléments x et xb du circuit papillon peuvent être remplacés comme indiqué sur la Fig. 2. De plus, nous obtenons FGP à la sortie d'un élément complexe.

Fig. 2. Une variante du circuit de la Fig. 1 et son STG en supposant que les retards dans les fils sont nuls.

Fig. 2. Une variante du circuit de la Fig. 1 et son STG en supposant que les retards dans les fils sont nuls.La mise en œuvre des schémas de la Fig. 1 et Fig. 2 nécessite respectivement 16 et 20 transistors. De plus, le diagramme de la Fig. 2 est plus lent, car les onduleurs wb1, wb2 et l'onduleur à l'intérieur de l'élément 2 OR-AND doivent commuter deux fois par cycle. La lenteur des performances est généralement le prix du FGP. Cependant, il existe des exceptions à cette règle. Par exemple, sur la Fig. 3 montre un schéma d'un déclencheur de comptage asynchrone (AST) [4] qui a deux FGP.

Fig. 3. AST et son STG en supposant que les retards dans les fils sont nuls.

Fig. 3. AST et son STG en supposant que les retards dans les fils sont nuls.Les inconvénients du circuit de la Fig. 3 sont un grand nombre de fils et le fait que la plupart d'entre eux se coupent. Cela peut compliquer la disposition, surtout si le nombre de couches avec des pistes est limité ou si elles sont occupées par d'autres composés. Ainsi, vous devez rechercher un compromis entre le nombre de fils, le nombre de transistors et le nombre de FGP. Un exemple d'un tel schéma de compromis avec un FGP est l'AST montré sur la Fig. 4. Il s'agit d'une petite modification du circuit de [5]. Notez qu'ici, comme dans le diagramme de la Fig. 2, une base mixte est utilisée. Pour mettre en œuvre cette AST sans indicateur (XOR sur wi2, wi4 et g5), 26 transistors sont nécessaires. Ce n'est que deux transistors de plus que l'AST sur la Fig. 3.

Fig. 4. Compromis AST et son STG, lorsque les retards dans les fils sont nuls.

Fig. 4. Compromis AST et son STG, lorsque les retards dans les fils sont nuls.Notez que tous les éléments avec rétroaction sur la Fig. 2 et Fig. 4 sont des cas particuliers d'un élément C généralisé (gC). Il est donné comme [6]:

où

et

Les fonctions d'installation et de réinitialisation satisfont-elles à la condition

. Des cas particuliers de l'élément gC sont également des éléments NCL, qui sont utilisés dans les schémas de traitement des données. Notez que le plus grand élément NCL a quatre entrées et est implémenté sur 28 transistors [7]. Cela peut s'expliquer par le fait qu'avec un plus grand nombre de transistors, les fils deviennent relativement longs et leur retard commence à affecter le fonctionnement de l'élément.

Considérez le circuit de transistor montré sur la Fig. 5. Il implémente la fonction de cinq variables [8], [9]

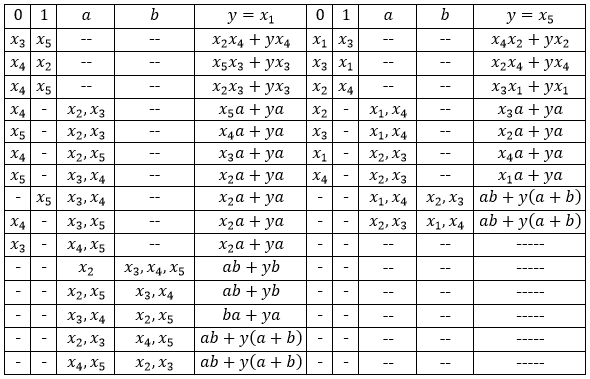

. Le tableau 1 montre les fonctions SDNF et SKNF

et sa double fonction

. D'après ce tableau, il est évident qu'en échangeant

et

dans

nous obtenons

et vice versa. Au cas où

, nous obtenons une fonction auto-double

.

Fig. 5. Un schéma qui implémente la fonction de cinq variables.

Fig. 5. Un schéma qui implémente la fonction de cinq variables.Tableau 1. Formes de fonctions logiques pour le circuit de la Fig. 5.

Notez que

signifie que les quatre transistors correspondants doivent être commutés en même temps. Même si les fils après branchement y ont le même retard, cela ne suffit pas, car le moment de commutation du transistor est déterminé par la tension à sa grille. De ce point de vue, l'analyse du circuit de la Fig. 5 a été faite en [10]. Cependant, cette analyse n'est pas complète, car seule la mise en œuvre d'un élément C à deux entrées a été envisagée. Pour effectuer une analyse complète, vous devez d'abord trouver toutes les options de combinaison des entrées ou, plus formellement, toutes les fonctions d'un plus petit nombre de variables qui peuvent être obtenues à partir de

. Une telle recherche a été effectuée sous une forme quelque peu simplifiée, et ses résultats sont présentés en annexe. La plupart des fonctionnalités se trouvent dans plusieurs variantes. Parmi eux, il est nécessaire de choisir ceux qui offrent des régimes sans concurrence [11]. Toutes les fonctions obtenues, le nombre de variantes de chacune d'entre elles et le numéro du tableau correspondant en annexe sont donnés dans le tableau 2. Les nombres avec un astérisque indiquent les fonctions duales.

Tableau 2. Les éléments gC mis en œuvre par le circuit de la Fig. 5.

Les fonctions 2 et 2 *, 5 et 5 *, 7 et 7 * sont auto-doubles, et la fonction 4 peut être obtenue à partir de la fonction 4 * en échangeant a et c. Notez qu'en plus de la fonction 6 *, toutes les autres fonctions sont à seuil. Cela peut s'expliquer par le fait que

est isotonique (unate positif) et le fait que pour quatre variables ou moins les fonctions isotoniques coïncident avec un pseudo-seuil [12]. La question des options pour les fonctions 1 *, 3 * et 6 * dans cet article reste ouverte.

Prenons l'exemple des fonctions 2 et 2 *. Conformément à l'une des options (tableau P3 en annexe)

et

. Laissez sortir

déconnecté de l'entrée

et laissez le signal être supprimé de l'entrée de l'onduleur. Cela vous permet de construire un distributeur de convoyeur de cellules [13] illustré à la Fig. 6. Les éléments de cette cellule sont différents, mais du fait que les entrées sont combinées, elles implémentent toutes deux la même fonction auto-double. Notez que les éléments réticulés dans les circuits de la Fig. 1, sur la Fig. 3 et sur la Fig. 6 sont des cas particuliers de la construction de base pour une mise en œuvre parfaite [2]. Ainsi, il doit y avoir des règles pour transformer les circuits de conception de base en circuits d'éléments gC et vice versa.

Fig. 6. Distributeur de convoyeur de cellules.

Fig. 6. Distributeur de convoyeur de cellules.D'un point de vue technologique, les transistors doivent être «enfilés» sur des bus en silicium polycristallin. Une telle mise en œuvre du circuit de la Fig. 5 est donné dans [14]. Pour définir les états initiaux, des transistors p-MOS et n-MOS peuvent être utilisés, ce qui crée un diviseur de tension avec des transistors dans l'onduleur. L'immunité au bruit des circuits peut être augmentée à l'aide de certaines transformations STG [15].

Remerciements

L'auteur est profondément reconnaissant à Svetlana Frolova (OmSU) d'avoir scanné l'article [1], ainsi qu'à Sergey Bystrov pour son inspiration.

App

Le MuPAD a été utilisé pour obtenir les résultats présentés dans cette section. Soit la sortie y connectée à une seule des entrées. Le tableau A1 montre que dans ce cas

. Pour obtenir des fonctions pour lesquelles

, vous pouvez soit combiner certaines variables, soit leur affecter des constantes. Les fonctions pour le cas de la combinaison de deux variables sont données dans le tableau A2. Les autres options ne donnent pas

. Puisque les quatre premières fonctions du tableau A1 coïncident jusqu'à une permutation des variables, nous ne considérerons que les première et cinquième. Étuis

et

pas intéressant, car dans le premier nous ne pouvons que réinitialiser l'élément gC, mais nous ne pouvons pas l'installer, et dans le second - vice versa. Les manipulations avec les variables ont permis d'obtenir à partir du tableau P1 les fonctions de quatre et trois variables, qui sont données respectivement dans les tableaux P3 et P4.

Tableau A1. Fonctions de cinq variables.

Tableau A2. Fonctions de quatre variables.

Tableau P3. Fonctions de quatre variables obtenues à partir du tableau A1.

Tableau A4. Les fonctions des trois variables obtenues à partir du tableau A1.

Littérature

[1] V. I. Varshavsky, M. A. Kishinev, A. R. Taubin et B. S. Zirlin, «Analyse des circuits logiques asynchrones. II. Accessibilité des états de fonctionnement et effet des retards dans les fils », Izv. Académie des sciences de l'URSS. Cybernétique technique, non. 4, pp. 84-97, 1982.

[2] Varshavsky, V. I. (éd.), Automatic control of asynchronous process in computers and discrete systems, Nauka, 1986.

[3]

workcraft.org .

[4] RC Todd, «Système logique». Brevet US3609569, 28 sept. 1971.

[5] EA Vittoz, «Structure logique de division de fréquence». Brevet US3829714, 13 août 1974.

[6] J. Cortadella, M. Kishinevsky, A. Kondratyev, L. Lavagno et A. Yakovlev, Synthèse logique pour les contrôleurs et interfaces asynchrones, Springer, 2002.

[7] A. Kondratyev, «Flux asynchrone multi-rails avec détection d'achèvement et système et procédé de conception de celui-ci.» Brevet US6526542, 25 février 2003.

[8] JJ Gibson, "Circuits logiques utilisant des transistors à effet de champ." Brevet US3439185, 15 avril 1969.

[9] R. Miller, Théorie des circuits de commutation. Volume I. Schémas de combinaison, Science, 1970.

[10] K. van Berkel, «Méfiez-vous de la fourchette isochronique», Integration, vol. 13, non. 2, pp. 103-128, 1992.

[11] P. Kudva, G. Gopalakrishnan, H. Jacobson et SM Nowick, «Synthèse de réseaux de portes complexes CMOS personnalisés sans danger sous des changements à entrées multiples», dans Design Automation Conf., 1996.

[12] GW Fagerlin, Énumération des fonctions pseudo-séparables de cinq variables. M.Sc. thèse, Université de l'Illinois, 1968.

[13] V. I. Varshavsky, A. Yu. Kondratiev, N. M. Kravchenko et B. S. Tsirlin, «Distributeur asynchrone». Brevet SU1598142, 07/10 1990.

[14] SW Cheng, «Circuit logique CMOS de l'arbre H», dans IEEE Conf. sur l'électronique, les circuits et les systèmes, 2008.

[15] A. Taubin, A. Kondratyev, J. Cortadella et L. Lavagno, «Transformations comportementales pour augmenter l'immunité au bruit dans les spécifications asynchrones», dans IEEE Symp. sur Async. Circuits et systèmes, 1999.