Salut, lecteurs de Habr. Nous voulons partager une très bonne nouvelle. Nous avons enfin attendu la véritable production en série d'une nouvelle génération de processeurs Elbrus 8C russes. Officiellement, la production en série devait commencer déjà en 2016, mais, en fait, c'était la production de masse qui n'a commencé qu'en 2019 et actuellement environ 4000 processeurs ont déjà été commercialisés.

Presque immédiatement après le début de la production de masse, ces processeurs sont également apparus dans notre Aerodisk, pour lesquels nous tenons à remercier la société NORSI-TRANS, qui nous a aimablement fourni sa plate-forme matérielle Yakhont UVM, prenant en charge les processeurs Elbrus 8C, pour le portage du logiciel de stockage. Il s'agit d'une plate-forme moderne et universelle répondant à toutes les exigences du MCST. À l'heure actuelle, la plate-forme est utilisée par des consommateurs spéciaux et des opérateurs de télécommunications pour assurer la mise en œuvre des actions établies lors des activités de recherche opérationnelle.

Pour le moment, le portage a été effectué avec succès et le stockage AERODISK est désormais disponible dans la version avec les processeurs Elbrus nationaux.

Dans cet article, nous parlerons des processeurs eux-mêmes, de leur histoire, de leur architecture et, bien sûr, de notre implémentation du stockage sur Elbrus.

L'histoire

L'histoire des processeurs Elbrus remonte à l'époque de l'Union soviétique. En 1973, à l'Institut de mécanique de précision et de génie informatique. S.A. Lebedev (du nom du même Sergey Lebedev, qui avait auparavant dirigé le développement du premier ordinateur soviétique MESM, puis de BESM) a commencé le développement de systèmes informatiques multiprocesseurs appelés "Elbrus". Vsevolod Sergeevich Burtsev a dirigé le développement, et Boris Artashesovich Babayan, qui était l'un des concepteurs en chef adjoints, a également pris une part active au développement.

Vsevolod Sergeevich Burtsev

Boris Artashesovich Babayan

Le principal client du projet était, bien sûr, les forces armées de l'URSS, et cette série d'ordinateurs a finalement été utilisée avec succès pour créer des centres informatiques de commandement et des systèmes de tir pour les systèmes de défense antimissile, ainsi que d'autres systèmes à usage spécial.

Le premier ordinateur Elbrus a été achevé en 1978. Il avait une architecture modulaire et pouvait comprendre de 1 à 10 processeurs basés sur des circuits d'intégration moyens. La vitesse de cette machine a atteint 15 millions d'opérations par seconde. La quantité de RAM, qui était courante pour les 10 processeurs, pouvait aller de 2 à 20 mots de machine, soit 64 Mo.

Plus tard, il s'est avéré que de nombreuses technologies utilisées dans le développement d'Elbrus en même temps ont été étudiées dans le monde, et l'International Business Machine (IBM) y a participé, mais le travail sur ces projets, contrairement au travail sur Elbrus, n'a jamais été ont été achevés et n'ont pas abouti à un produit fini.

Selon Vsevolod Burtsev, les ingénieurs soviétiques ont essayé d'appliquer l'expérience la plus avancée des développeurs nationaux et étrangers. L'architecture des ordinateurs Elbrus a également été influencée par les ordinateurs Burroughs, les développements Hewlett-Packard, ainsi que par l'expérience des développeurs BESM-6.

Mais en même temps, de nombreux développements étaient originaux. Le plus intéressant dans "Elbrus-1" était précisément son architecture.

Le supercalculateur créé a été le premier ordinateur de l'URSS à utiliser une architecture superscalaire. L'utilisation massive de processeurs superscalaires à l'étranger n'a commencé que dans les années 90 du siècle dernier avec l'avènement de processeurs Intel Pentium abordables sur le marché.

De plus, pour organiser le transfert des flux de données entre les périphériques et la RAM de l'ordinateur, des processeurs d'entrée / sortie spéciaux pourraient être utilisés. Il pouvait y avoir jusqu'à quatre de ces processeurs dans le système; ils fonctionnaient en parallèle avec le processeur central et avaient leur propre mémoire dédiée.

Elbrus-2

En 1985, Elbrus a obtenu sa suite logique, l'ordinateur Elbrus-2 a été créé et mis en production en série. En architecture, il n'était pas très différent de son prédécesseur, mais il utilisait une nouvelle base d'éléments, ce qui a permis d'augmenter la productivité globale de près de 10 fois - de 15 millions d'opérations par seconde à 125 millions. La RAM de l'ordinateur est passée à 16 millions de mots de 72 bits ou 144 Mo. Le débit maximal des canaux d'E / S Elbrus-2 était de 120 Mo / s.

"Elbrus-2" a été activement utilisé dans les centres de recherche nucléaire de Chelyabinsk-70 et Arzamas-16 dans le MCC, dans le système de défense antimissile A-135, ainsi que dans d'autres installations militaires.

Complexe SPRUT C1200 basé sur les processeurs Elbrus

La création d'Elbrus a été appréciée par les dirigeants de l'Union soviétique. De nombreux ingénieurs ont reçu des ordres et des médailles. Le concepteur général Vsevolod Burtsev et un certain nombre d'autres spécialistes ont reçu des prix d'État. Et Boris Babayan a reçu l'Ordre de la Révolution d'Octobre.

Ces récompenses sont plus que méritées, Boris Babayan a déclaré plus tard:

"En 1978, nous avons fabriqué la première machine superscalaire, Elbrus-1. Maintenant en Occident, ils ne fabriquent des superscalaires que de cette architecture. La première superscalaire est apparue dans la 92e année, la nôtre dans la 78e. De plus, cette version de la superscalaire que nous avons fabriquée , similaire au Pentium Pro, fabriqué par Intel au cours de la 95e année. "

Ces mots sur la primauté historique sont également confirmés aux États-Unis, Keith Diefendorff, le développeur de Motorola 88110, l'un des premiers processeurs superscalaires occidentaux, a écrit:

"En 1978, près de 15 ans plus tôt que les premiers processeurs superscalaires occidentaux sont apparus, un processeur a été utilisé dans Elbrus-1, avec l'émission de deux instructions par cycle, modifiant l'ordre d'exécution des instructions, renommant les registres et l'exécution par hypothèse."

Elbrus-3

C'était en 1986, et presque immédiatement après avoir terminé les travaux sur le deuxième Elbrus, ITM & VT a commencé à développer un nouveau système Elbrus-3 en utilisant une architecture de processeur fondamentalement nouvelle. Boris Babayan a qualifié cette approche de «post-superscalaire». C'est cette architecture, appelée plus tard VLIW / EPIC, que les processeurs Intel Itanium ont commencé à utiliser à l'avenir (au milieu des années 90) (et en URSS, ces développements ont commencé en 1986 et se sont terminés en 1991).

L'idée de gérer explicitement le parallélisme des opérations à l'aide d'un compilateur a d'abord été réalisée dans ce complexe informatique.

En 1991, le premier et, malheureusement, le seul ordinateur Elbrus-3 a été libéré, qu'ils n'ont pas pu installer complètement, et après l'effondrement de l'Union soviétique, personne n'en avait besoin, et les conceptions et les plans sont restés sur papier.

Contexte de la nouvelle architecture

L'équipe qui a travaillé à ITMiVT pour créer des superordinateurs soviétiques n'a pas éclaté, mais a continué à travailler en tant qu'entreprise distincte sous le nom de MCST (Moscow SPARK-Technology Center). Et au début des années 90, l'ICST a commencé une coopération active avec Sun Microsystems, où l'équipe ICST a participé au développement du microprocesseur UltraSPARC.

C'est durant cette période qu'est né le projet d'architecture E2K, initialement financé par Sun. Plus tard, le projet est devenu complètement indépendant et toute la propriété intellectuelle y est restée avec le personnel du STIC.

"Si nous avions continué à travailler avec Sun dans ce domaine, alors tout aurait appartenu à Sun. Bien que 90% du travail ait été fait avant l'apparition de Sun." (Boris Babayan)

Architecture E2K

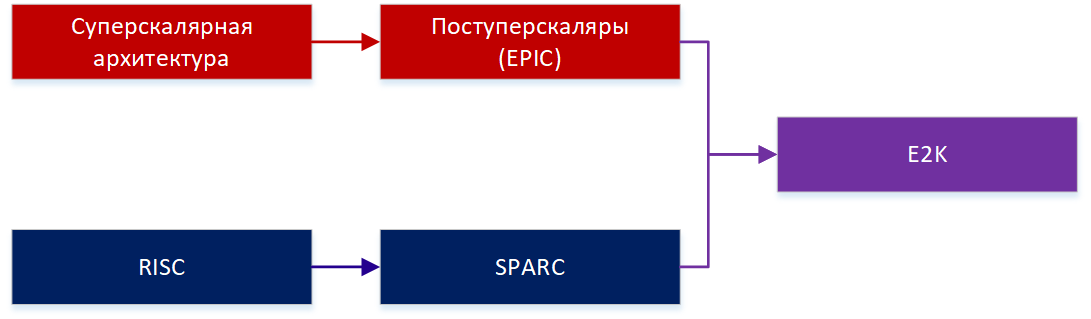

Lorsque nous discutons de l'architecture des processeurs Elbrus, très souvent de nos collègues de l'industrie informatique, nous entendons les déclarations suivantes:

«Elbrus est une architecture RISC»

«Elbrus est une architecture EPIC»

«Elbrus est une architecture SPARC»

En fait, aucune de ces affirmations n'est complètement vraie, et si c'est le cas, ce n'est que partiellement.

L'architecture E2K est une architecture de processeur originale distincte, les principales caractéristiques de E2K sont l'efficacité énergétique et une excellente évolutivité obtenues en définissant un parallélisme explicite des opérations. L'architecture E2K a été développée par l'équipe ICST et est basée sur l'architecture post-superscalaire (à la EPIC) avec une certaine influence de l'architecture SPARC (avec le passé RISC). Parallèlement, dans la création de trois des quatre architectures de base (Superscalars, postsuperscalars et SPARC), le MCST a été directement impliqué. Le monde est vraiment petit.

Afin d'éviter toute confusion supplémentaire, nous avons dessiné un schéma simple qui, bien que simpliste, mais montre très clairement les racines de l'architecture E2K.

Maintenant, un peu plus sur le nom de l'architecture, par rapport à laquelle il y a aussi un malentendu.

Dans différentes sources, vous pouvez trouver les noms suivants de cette architecture: "E2K", "Elbrus", "Elbrus 2000", ELBRUS ("ExpLicit Basic Resources Utilization Scheduling", c'est-à-dire une planification explicite pour l'utilisation des ressources de base). Tous ces noms disent la même chose - à propos de l'architecture, mais dans la documentation technique officielle, ainsi que dans les forums techniques, le nom E2K est utilisé pour désigner l'architecture, donc à l'avenir si nous parlons d'architecture de processeur, nous utilisons le terme "E2K", et si à propos d'un processeur spécifique, nous utilisons le nom "Elbrus".

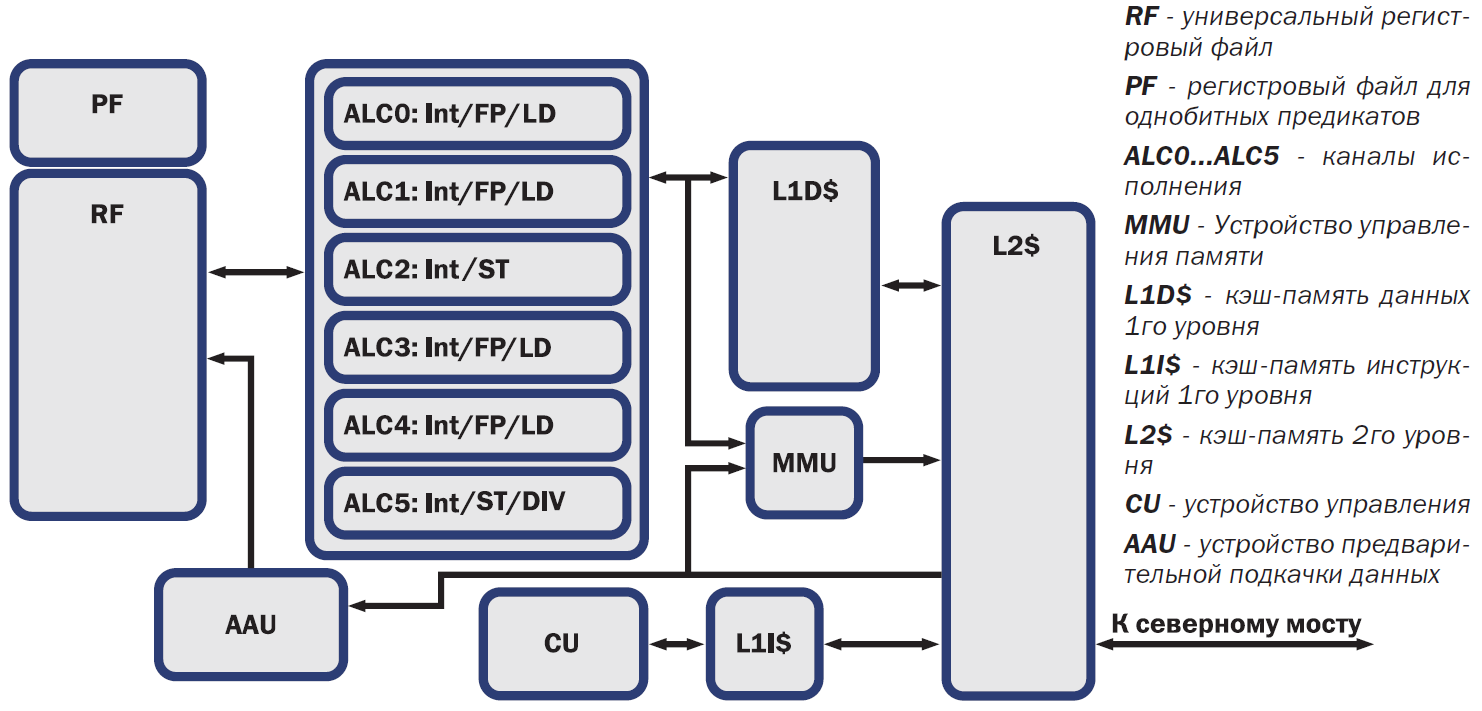

Caractéristiques techniques de l'architecture E2K

Dans les architectures traditionnelles telles que RISC ou CISC (x86, PowerPC, SPARC, MIPS, ARM), le processeur reçoit un flux d'instructions conçues pour une exécution séquentielle. Le processeur peut détecter des opérations indépendantes et les exécuter en parallèle (superscalarité) et même changer leur ordre (exécution extraordinaire). Cependant, l'analyse dynamique des dépendances et la prise en charge d'une exécution extraordinaire ont leurs limites en termes de nombre de lancement et d'analyse de commandes par cycle. De plus, les blocs correspondants à l'intérieur du processeur consomment une quantité importante d'énergie, et leur mise en œuvre la plus compliquée conduit parfois à des problèmes de stabilité ou de sécurité.

Dans l'architecture E2K, le compilateur prend la majeure partie du travail sur l'analyse des dépendances et l'optimisation de l'ordre des opérations. Le processeur reçoit la soi-disant entrée. des commandes larges, dans chacune desquelles sont codées les instructions pour tous les périphériques exécutifs du processeur qui doivent être exécutés sur cette horloge. Le processeur n'a pas besoin d'analyser les dépendances entre les opérandes ou de réorganiser les opérations entre les commandes larges: tout cela est fait par le compilateur basé sur l'analyse du code source et la planification des ressources du processeur. En conséquence, le composant matériel du processeur peut être plus simple et plus économique.

Le compilateur est capable d'analyser le code source beaucoup plus en profondeur que le matériel du processeur RISC / CISC et de trouver des opérations plus indépendantes. Par conséquent, il y a plus d'actionneurs simultanés dans l'architecture E2K que dans les architectures traditionnelles.

Caractéristiques actuelles de l'architecture E2K:

- 6 canaux de dispositifs arithmétiques logiques (ALU) fonctionnant en parallèle.

- Un fichier de registre de 256 registres de 84 bits.

- Support matériel pour les boucles, y compris le pipelining. Améliore l'utilisation du processeur.

- Dispositif de pré-recherche de données asynchrone programmable avec canaux de lecture séparés. Vous permet de masquer les retards d'accès à la mémoire et d'utiliser pleinement ALU.

- Prise en charge de l'informatique spéculative et des prédicats sur un seul bit. Il permet de réduire le nombre de transitions et d'exécuter simultanément plusieurs branches du programme.

- Une large équipe capable de mettre en place jusqu'à 23 opérations en un seul cycle avec un remplissage maximum (plus de 33 opérations lors du conditionnement d'opérandes en instructions vectorielles).

Émulation X86

Même au stade de la conception de l'architecture, les développeurs comprenaient l'importance de prendre en charge les logiciels écrits pour l'architecture Intel x86. Pour cela, un système de traduction dynamique (c'est-à-dire en cours d'exécution de programme, ou "à la volée") de codes binaires x86 en codes processeurs de l'architecture E2K a été implémenté. Ce système peut fonctionner à la fois en mode application (à la manière de WINE) et dans un mode similaire à l'hyperviseur (il est alors possible d'exécuter l'intégralité du système d'exploitation invité pour l'architecture x86).

Grâce à plusieurs niveaux d'optimisation, il est possible d'atteindre une vitesse élevée du code traduit. La qualité de l'émulation de l'architecture x86 est confirmée par le lancement réussi de plus de 20 systèmes d'exploitation (dont plusieurs versions de Windows) et des centaines d'applications sur les complexes informatiques Elbrus.

Mode d'exécution de programme protégé

L'une des idées les plus intéressantes héritées des architectures Elbrus-1 et Elbrus-2 est la soi-disant exécution sécurisée des programmes. Son essence est de garantir le fonctionnement du programme uniquement avec des données initialisées, de vérifier que tous les accès à la mémoire appartiennent à une plage d'adresses valide, de fournir une protection inter-modules (par exemple, protéger le programme appelant d'une erreur dans la bibliothèque). Toutes ces vérifications sont effectuées dans le matériel. Pour le mode protégé, il existe un compilateur complet et une bibliothèque de support d'exécution. Il faut comprendre que les restrictions imposées rendent impossible l'organisation de l'exécution, par exemple, de code écrit en C ++.

Même dans le mode de fonctionnement «non protégé» habituel des processeurs Elbrus, il existe des fonctionnalités qui augmentent la fiabilité du système. Ainsi, la pile d'informations de liaison (la chaîne d'adresses de retour pour les appels de procédure) est séparée de la pile de données utilisateur et n'est pas disponible pour les attaques utilisées dans les virus comme l'usurpation de l'adresse de retour.

Ces développements nous permettent non seulement de rattraper et de dépasser à l'avenir les architectures concurrentes en termes de performances et d'évolutivité, mais offrent également une protection contre les erreurs qui affectent x86 / amd64. Signets comme Meltdown (CVE-2017-5754), Spectre (CVE-2017-5753, CVE-2017-5715), RIDL (CVE-2018-12126, CVE-2018-12130), Fallout (CVE-2018-12127), ZombieLoad (CVE-2019-11091) et similaires.

La protection moderne contre les vulnérabilités de l'architecture x86 / amd64 est basée sur des correctifs au niveau du système d'exploitation. C'est pourquoi la baisse des performances sur les générations actuelles et précédentes de processeurs de ces architectures est si sensible et varie de 30% à 80%. En tant qu'utilisateurs actifs de processeurs x86, nous le savons, souffrons et continuons de «manger un cactus», mais la solution à ces problèmes est dans l'œuf pour nous (et, par conséquent, pour nos clients), un avantage incontestable, surtout si la solution est russe.

Spécifications techniques

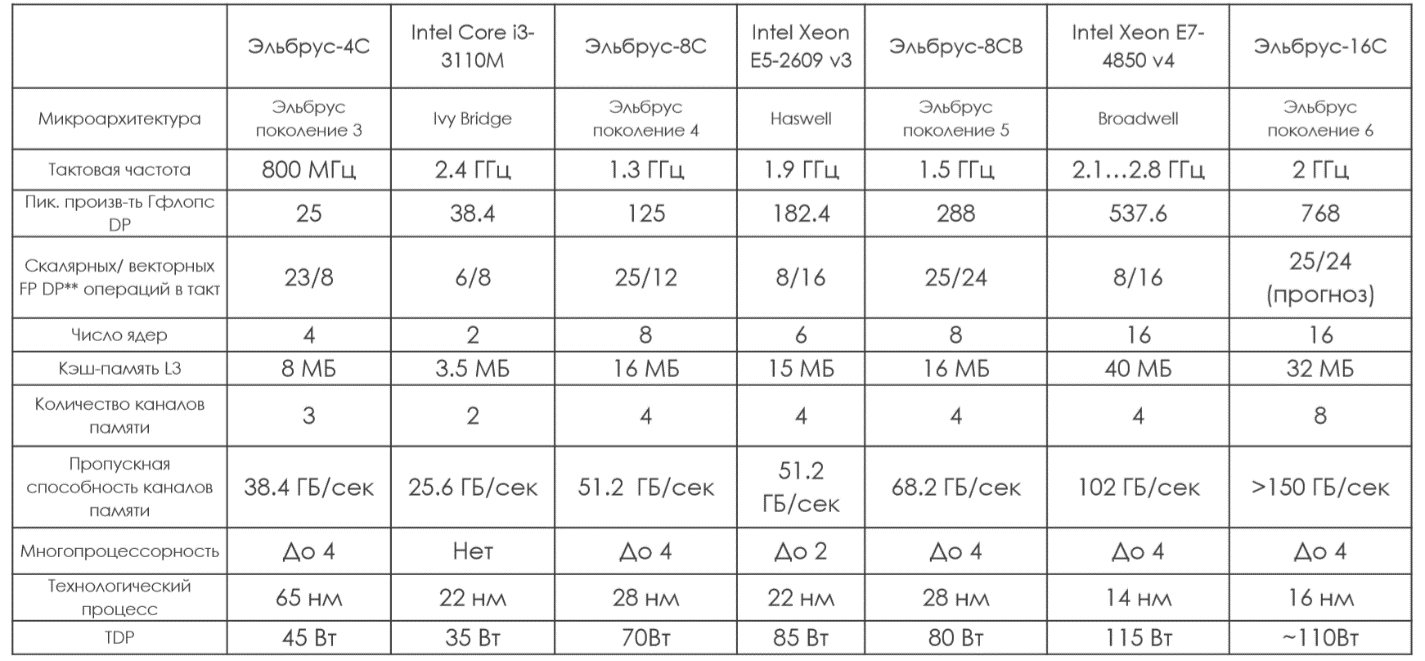

Vous trouverez ci-dessous les spécifications techniques officielles des processeurs Elbrus des générations passées (4C), actuelles (8C), nouvelles (8CB) et futures (16C) en comparaison avec des processeurs Intel x86 similaires.

Un simple coup d'œil sur ce tableau montre (et c'est très agréable) que l'arriéré technologique des transformateurs nationaux, qui semblait insurmontable il y a 10 ans, semble désormais très faible, et en 2021 avec le lancement d'Elbrus-16C (qui, entre autres, supportera la virtualisation) sera réduit à des distances minimales.

Stockage AERODISK sur les processeurs Elbrus 8C

On passe de la théorie à la pratique. Dans le cadre de l'alliance stratégique des sociétés MTsST, Aerodisk, Basalt SPO (anciennement Alt Linux) et NORSI-TRANS, un système de stockage de données a été développé et préparé pour fonctionner, ce qui pour le moment n'est pas le meilleur en termes de sécurité, fonctionnalité, coût et performance, puis , à notre avis, une solution indéniablement digne qui peut fournir avec vous le niveau d'indépendance technologique de notre pays.

Maintenant, les détails ...

Matériel informatique

Le matériel de stockage est implémenté sur la base de la plateforme universelle Yakhont UVM de NORSI-TRANS. La plate-forme Yakhont UVM a reçu le statut d'équipement de télécommunication d'origine russe et figure dans le registre unifié des produits radioélectroniques russes. Le système se compose de deux contrôleurs de stockage séparés (2U chacun), qui sont interconnectés par une interconnexion Ethernet 1G ou 10G, ainsi que des étagères de disques communes utilisant une connexion SAS.

Bien sûr, ce n'est pas aussi beau que le format «Cluster in a box» (lorsque les contrôleurs et les lecteurs avec un fond de panier commun sont installés dans le même châssis 2U), que nous utilisons habituellement, mais il sera également disponible dans un proche avenir. L'essentiel ici est de bien fonctionner, mais nous penserons plus tard aux «arcs».

Sous le capot, chaque contrôleur dispose d'une carte mère mono-processeur avec quatre emplacements RAM (DDR3 pour processeur 8C). Chaque contrôleur possède également 4 ports Ethernet 1G (dont deux sont utilisés par AERODISK ENGINE en tant que service) et trois connecteurs PCIe pour les adaptateurs dorsaux (SAS) et frontaux (Ethernet ou FibreChannel).

Comme disques de démarrage, nous utilisons des disques SSD SATA russes de GS Nanotech, que nous avons testés et utilisés à plusieurs reprises dans des projets.

Lorsque nous avons rencontré la plate-forme pour la première fois, nous l'avons soigneusement examinée. Nous n'avons eu aucune question concernant la qualité de l'assemblage et de la soudure, tout a été fait de manière soignée et fiable.

Système d'exploitation

Le système d'exploitation utilise la version du système d'exploitation Alt 8SP pour la certification. Dans un avenir proche, nous prévoyons de créer un plug-in et un référentiel constamment mis à jour pour Alt OS avec le logiciel de stockage Aerodisk.

Cette version de la distribution est construite sur la version stable actuelle du noyau Linux 4.9 pour E2K (une branche avec un support à long terme a été portée par les spécialistes du MCST), complétée par des correctifs pour la fonctionnalité et la sécurité. Tous les packages dans Alt OS ont été collectés directement sur Elbrus en utilisant le système d'assemblage transactionnel d'origine du projet ALT Linux Team, ce qui a permis de réduire les coûts de main-d'œuvre pour le port lui-même et d'accorder plus d'attention à la qualité des produits.

Toute version d'Alt OS pour Elbrus peut être considérablement étendue en termes de fonctionnalités, en utilisant le référentiel à sa disposition (d'environ 6 000 packages source pour la huitième version à environ 12 pour la neuvième).

Le choix a également été fait parce que la société Basalt SPO, le développeur d'Alt OS, travaille activement avec d'autres développeurs de logiciels et d'appareils sur diverses plates-formes, offrant une interaction transparente dans le cadre des systèmes matériels et logiciels.

Logiciels de stockage

Lors du portage, nous avons immédiatement abandonné l'idée d'utiliser l'émulation x86 prise en charge dans E2K, et avons commencé à travailler directement avec les processeurs (car Alt a déjà les outils nécessaires pour cela).

Entre autres choses, le mode d'exécution natif offre une meilleure sécurité (ces mêmes trois piles matérielles au lieu d'une) et des performances accrues (il n'est pas nécessaire d'allouer un ou deux noyaux sur huit pour que le traducteur binaire fonctionne, et le compilateur fait son travail mieux que JIT).

En fait, dans la mise en œuvre d'AERODISK ENGINE sur E2K, la plupart des fonctionnalités de stockage existantes, qui sont en x86, sont prises en charge. En tant que logiciel du système de stockage, la version actuelle d'AERODISK ENGINE est utilisée (A-CORE version 2.30)

Sans aucun problème, les fonctions suivantes ont été lancées sur E2K et testées pour une utilisation dans le produit:

- Tolérance aux pannes pour jusqu'à deux contrôleurs et E / S multivoies (mpio)

- Bloquer et accéder aux fichiers avec des volumes légers (RDG, pools DDP; protocoles FC, iSCSI, NFS, SMB, y compris l'intégration avec Active Directory)

- Différents niveaux RAID jusqu'à la triple parité (y compris la possibilité d'utiliser le constructeur RAID)

- Stockage hybride (combinant SSD et HDD dans le même pool, c'est-à-dire cache et déchirement)

- Options d'économie d'espace avec déduplication et compression

- Instantanés ROW, clones et différentes options de réplication

- Et d'autres fonctionnalités petites mais utiles comme QoS, hotspare global, VLAN, BOND, etc.

E2K , ( ) -, all-flash 20-30%.

, , , .

, , .

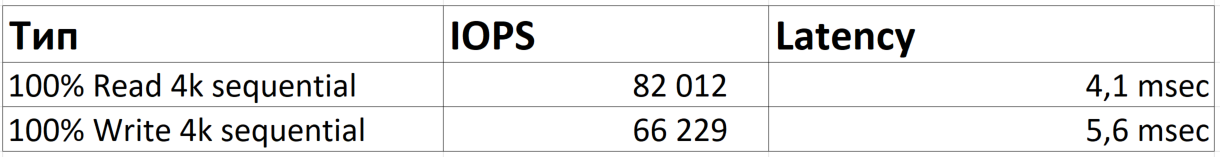

, (2xCPU E8C 1.3 Ghz, 32 GB RAM + 4 SAS SSD 800GB 3DWD), RAM-, DDP RAID-10 LUN 500G LUN- iSCSI (10G Ethernet) Linux-. FIO.

.

60%, .. , .

, highload - , , , 80% , .

.

, 8 – 2019 4000 . , 4 5000, .

, , , .

2020 8, . , 2020 -8 .

— .

, ( -16). , .

, , , , . , , .

, , , - , – , , . , , .

. , , , !

, , , , , . .

- , 100% – ))).

, :

https://www.ixbt.com/cpu/e2k-spec.html

«»:

https://topwar.ru/34409-istoriya-kompyuterov-elbrus.html

e2k:

https://ru.wikipedia.org/wiki/%D0%AD%D0%BB%D1%8C%D0%B1%D1%80%D1%83%D1%81_2000

4- (-8) 5- (-8, 2020 ):

https://ru.wikipedia.org/wiki/%D0%AD%D0%BB%D1%8C%D0%B1%D1%80%D1%83%D1%81-8%D0%A1

6- (-16, 2021 ):

https://ru.wikipedia.org/wiki/%D0%AD%D0%BB%D1%8C%D0%B1%D1%80%D1%83%D1%81-16%D0%A1

:

http://www.elbrus.ru/elbrus_arch

- «» :

http://www.mcst.ru/files/5a9eb2/a10cd8/501810/000003/kim_a._k._perekatov_v._i._feldman_v._m._na_puti_k_rossiyskoy_ekzasisteme_plany_razrabotchikov.pdf

«» , :

http://www.mcst.ru/files/5472ef/770cd8/50ea05/000001/rossiyskietehnologiielbrus-it-edu9-201410l.pdf

, :

http://www.mcst.ru/e2k_arch.shtml

:

https://www.osp.ru/os/1999/05-06/179819

, :

https://yadi.sk/i/HDj7d31jTDlDgA

:

https://altlinux.org/

https://sdelanounas.ru/blog/shigorin/