Le 10 juillet 1962, la fusée Tor avec le premier satellite de télécommunications commercial à bord a été lancée à partir du site de lancement de Cap Canaveral. Telstar-1 était l'aube d'une nouvelle ère de l'astronautique, qui a montré que l'espace peut apporter de réels avantages aux humains. Cet appareil attendait un grand avenir, mais un jour plus tôt dans le ciel au-dessus de l'atoll de Johnson, situé dans la partie désertique de l'océan Pacifique, la bombe atomique Starfish Prime a explosé. L'explosion a détruit trois cents lampadaires à Hawaï situés à un mille et demi de kilomètres, et a également créé une énorme quantité d'électrons libres, captés par le champ magnétique terrestre dans la ceinture de rayonnement artificielle. Chaque fois que Telsat-1 traversait cette ceinture, un remplissage avancé de transistor gagnait une dose de rayonnement et, en novembre 1962, il avait cessé de fonctionner. L'histoire de la protection de l'électronique spatiale contre les rayonnements a commencé par une étude des conséquences de cet incident.

Heureusement, ils ont commencé à se lancer dans des explosions nucléaires à haute altitude assez rapidement, mais même sans eux, il y a suffisamment de travail, et les exigences de fiabilité et de durabilité présentées aux satellites modernes deviennent plus ambitieuses. Il est impossible de parler de tout, mais je vais essayer de couvrir brièvement le passé et le présent des microprocesseurs spatiaux de différents pays. Pourquoi exactement des microprocesseurs? La plupart d'entre eux sont des informations les concernant et sont mieux compris par les non-spécialistes. L'article s'est avéré long, je l'ai donc divisé en deux parties: une histoire ancienne sur l'exemple des États-Unis et de l'Europe (sous la coupe) et moderne - sur l'exemple de la Russie (

ici ). C'est parti!

Règles du jeu

Commençons par les termes et définitions. Par "microprocesseur", j'entends un microcircuit ou un ensemble de microcircuits d'un haut degré d'intégration, conçu pour exécuter des programmes. Le premier microprocesseur monopuce populaire était l'Intel 4004 à quatre bits, sorti en 1971 - c'est après que les Américains ont atterri sur la lune, donc avec cette définition, les ordinateurs de bord de l'ère de l'exploration héroïque de l'espace disparaissent de l'image, ne nous laissant que des ennuyeux «chevaux de bataille». Cependant, beaucoup a été écrit sur les ordinateurs de bord de l'ère héroïque, y compris sur Habré.

Ici ,

ici et

là . En règle générale, ils étaient conçus pour une mission spécifique, avaient une sorte de système de commandement et une profondeur de bits de 13 bits, puis 17, puis 21 - en général, n'essayez pas de le répéter à la maison. L'unification a commencé avec des coupes budgétaires après la fin de la course lunaire et avec le déploiement simultané de diverses constellations de satellites. En conséquence, presque toutes les parties intéressées sont arrivées à un nombre limité de puces universelles utilisées où qu'elles se trouvent.

Le deuxième point important est la disponibilité des informations. L'industrie spatiale n'a jamais été particulièrement ouverte. Le premier satellite, l'accès de l'astronaute à la lune ou le nombre de satellites dans la constellation GLONASS est une publicité simple et compréhensible, mais il est difficile de se vanter des caractéristiques grand public de la conception de l'émetteur radio de Spoutnik-3. Ajoutez le secret traditionnel de la quasi-guerre d'en haut - et nous savons à propos du processeur RAD750 qu '«il y en a plus de 150» et seulement une douzaine de satellites sur lesquels il se trouve. Une citation typique de publications scientifiques spécialisées écrites dans les années 70 ressemble à ceci:

«Un registre à décalage PMOS / SOS 32 bits résistant aux rayonnements a également été construit et testé; cependant, les données de test sur ce circuit sont classées. » À propos des données ouvertes sur les satellites et microcircuits russes (et je n'utilise bien sûr que des données ouvertes), je ne veux même pas commencer; les miettes existantes vont généralement sur Internet par inadvertance. Les publications scientifiques nous épargnent un peu, surtout si vous savez ce que vous recherchez. La base de données en ligne IEEE est simplement un entrepôt pour l'historien de l'électronique; avec les archives des revues et conférences scientifiques soviétiques et russes, la situation est radicalement pire qu'avec les journaux étrangers, mais pas non plus sans espoir. L'inconvénient des publications est qu'à travers elles, il est difficile de tracer la connexion entre les microcircuits et leur application, mais des informations intéressantes sur la conception des microcircuits peuvent être trouvées. Total: l'article ne prétend pas être complet, il s'agit plutôt d'un recueil d'exemples par lesquels on peut suivre le développement et présenter l'état actuel des microprocesseurs et microcontrôleurs pour les applications spatiales.

La troisième chose sur laquelle je suis d'accord - je ne comparerai pas les performances du processeur du rover avec un iPhone. Il y a du plaisir à cela, mais la différence de performance ne vient pas d'une bonne vie, elle a des raisons objectives: un long cycle de développement, d'autres exigences de fiabilité, une longue certification et des tests de tout, de la technologie de fabrication de puces à l'assemblage de satellites. Bien sûr, les développeurs d'espace veulent toujours obtenir la puissance de calcul maximale - pour traiter les informations à bord, économiser la bande passante du canal radio - mais souvent d'autres priorités sont plus importantes. C'est pourquoi dix ans peuvent s'écouler entre l'achèvement du développement et le premier vol, et donc tout le monde aime les solutions qui ont déjà volé - il y a beaucoup moins de problèmes avec elles. En conséquence, la durée de vie spatiale des microcircuits spatiaux peut être de trente à quarante ans, le développement d'une nouvelle génération peut commencer avant même le premier vol de la précédente, et à l'heure actuelle, les processeurs développés dans les années 90 sont toujours en cours de démarrage. Je vais immédiatement remarquer que la conception des engins spatiaux devient de plus en plus compliquée, et maintenant il peut y avoir des dizaines d'ordinateurs à bord qui ont des exigences très différentes: vous devez traiter les réseaux d'images 24h / 24 et interroger quelques capteurs une fois par heure.

Quatrièmement, un rappel très bref des effets des rayonnements de l'espace. Un rappel de longueur moyenne

est ici , mais très long -

ici .

Les effets d'une dose complète de rayonnement sont associés à l'accumulation de charge électrique dans les diélectriques et à l'interface entre un diélectrique et un semi-conducteur; Nous nous intéressons principalement à l'oxyde de grille et à l'isolation latérale des transistors MOS. Ces effets se manifestent par un décalage de la tension de seuil des transistors (pour les canaux p, une augmentation de la valeur absolue, pour les canaux n diminuent généralement, mais plus tard vous verrez des nuances), une diminution de la mobilité des porteurs de charge (diminution de la vitesse du circuit) et des fuites dans les transistors à canal n ( à la fois entre le drain et la source d'un transistor, et entre différents transistors), conduisant à une augmentation de la consommation d'électricité statique.

Les effets uniques sont dus au fait que lorsqu'une seule particule chargée pénètre dans le transistor, une partie de l'énergie de cette particule est transférée au matériau du microcircuit, et des paires électron-trou libres s'y forment. Certaines de ces paires sont séparées dans le microcircuit par un champ électrique, et il «voit» une courte impulsion de courant, «amenée» par une particule externe. De plus, cette impulsion de courant peut changer la valeur enregistrée dans la cellule de mémoire, aller à l'entrée de l'élément logique ou faire quelque chose de catastrophique, par exemple, pour franchir la grille du transistor ou ouvrir la structure parasite du thyristor et créer un défaut à la terre local avec la puissance.

Les effets du déplacement sont dus au fait qu'une particule entrante peut non seulement créer des paires électron-trou, mais aussi interagir directement avec les atomes d'une substance, les faisant tomber des bonnes positions dans le réseau cristallin. Pour les transistors ordinaires, ces défauts locaux ne sont pas terribles, mais ils entraînent des dommages importants aux dispositifs optoélectroniques, aux semi-conducteurs bidimensionnels et aux transistors nanométriques.

Il y a toujours des

effets de débit de dose , mais ils ont surtout des applications non commerciales, donc je n'en parlerai pas.

La phase initiale - l'exemple des États-Unis

Le fait que je n'ai pas pu déterminer de manière fiable quel microprocesseur était le premier à bord du vaisseau spatial était tout à fait prévisible. Les données publiques ne sont disponibles que sur des missions scientifiques bien connues, et elles sont généralement placées sur les plus fiables et vérifiées, c'est-à-dire tranquillement élaborées à l'avance sur des satellites moins chers. On sait que les ordinateurs de bord Viking et Voyager étaient assemblés sur une logique discrète, mais c'est sur eux que la standardisation et la réutilisation des composants ont commencé. Voyager est intéressant en ce qu'il a été le premier appareil à utiliser une mémoire à semi-conducteur au lieu de noyaux magnétiques. De plus, il s'agissait d'une SRAM CMOS volatile, c'est-à-dire que les informations qu'elle contient sont effacées en cas de panne de courant. Comment les ingénieurs ont-ils réussi à convaincre la direction de prendre un tel risque? Tout d'abord, sans nouvelle mémoire, il ne serait pas logique d'appliquer une logique CMOS rapide. Dans l'espace, la technologie CMOS était plus qu'opportune: malgré le fait que les circuits CMOS étaient plus lents que les analogues bipolaires et beaucoup plus sensibles aux décharges électrostatiques, ils toléraient les températures extrêmes, avaient une faible sensibilité au bruit et consommaient radicalement moins d'énergie, qui est généralement à bord il y avait une pénurie. Deuxièmement, en tant que sauvegarde de l'alimentation, la tension de la sortie RTG a été directement portée à la mémoire, raisonnant raisonnablement que si quelque chose arrive au générateur, les problèmes de mémoire ne seront plus pertinents.

Figure 1. Carte avec une mémoire à semi-conducteur avec Voyager.

Le tout premier - RCA 1802

Le premier vaisseau spatial que j'ai trouvé dans lequel n'étaient pas des microcircuits de degré d'intégration moyen, mais à savoir un microprocesseur monolithique (8 bits RCA 1802) est le satellite Magsat lancé le 30 octobre 1979. Étant donné que les premiers RCA 1802 commerciaux ont été lancés en 1975, cela devrait signifier qu'ils ont frappé la NASA plus tôt que les étagères des magasins - ce qui, en général, était une pratique normale au début de la Silicon Valley.

Comme petit exemple de cette époque, je citerai un article d'EE King, «Effets de la dose totale sur le microprocesseur 1802», IEEE Transactions on Nuclear Science, 1977. L'article compare l'effet de la dose de rayonnement sur quatre variantes de 1802: deux commerciales, un échantillon expérimental produit sur un substrat de silicium sur saphir (SPS) et un échantillon produit par un procédé spécial conçu pour augmenter la résistance aux radiations.

Figure 2. Décalage de la tension de seuil des deux types de transistors sous l'influence de la dose de rayonnement. C1 et C2 sont des puces commerciales, S est une puce sur le SPS, X est un échantillon spécial.

On peut voir sur la figure que les échantillons commerciaux et la puce KNS à des doses de rayonnement plutôt faibles (8-15 crad (Si)), le seuil des transistors à canal n devient inférieur à zéro et les circuits logiques arrêtent simplement de commuter. Dans le même temps, un procédé technique spécial a permis d'atteindre une résistance de plus de 1 Mrad (Si), soit deux ordres de grandeur de plus. Encore une fois, je note que l'année n'est que de 1977, et des puces spéciales ont déjà été développées et produites. Cependant, le RCA 1802 décrit était probablement le premier signe, car dans les souvenirs des participants au développement du prochain grand appareil de la NASA - Galileo - j'ai trouvé une histoire qui, au moment de choisir l'architecture de l'électronique de commande en 1977, 1802 était le seul microprocesseur monolithique résistant aux rayonnements abordable.

Il est important de noter qu'ils ont déjà essayé d'utiliser les puces les plus courantes dans l'espace - et continuent de le faire avec succès maintenant. Pour de nombreuses applications, ni une fiabilité extrême, ni une résistance élevée aux radiations, ni l'absence complète de défaillances ne sont nécessaires - seule l'absence de défaillances dans un délai raisonnable est importante, et de nombreuses puces commerciales répondent à cette exigence, tout en étant de plusieurs ordres de grandeur moins chères que celles spécialement conçues frères. Pour une constellation de satellites de plusieurs centaines d'appareils en orbite basse, même la présence de pannes peu fréquentes n'est pas critique, contrairement au coût. Et ce n'est que lorsque la sécurité du pays dépend du fonctionnement des microcircuits, de la vie des astronautes, ou du moins du sort d'une mission scientifique de plusieurs millions d'années, est impossible sans puces résistantes aux radiations. Il existe, bien sûr, des approches mixtes, lorsque les systèmes les plus critiques sont exécutés sur des puces résistantes aux rayonnements, et le reste sont sur des puces conventionnelles, et également une bonne matrice connue, lorsque le fabricant prend les mêmes cristaux que ceux utilisés dans les produits radiants résistants coûteux, les met dans des boîtiers en plastique bon marché et ne procède pas à des tests de bout en bout, ce qui permet d'économiser plusieurs fois sur le prix. Il y a des entreprises qui sont spécifiquement engagées dans le test de puces commerciales pour trouver parmi elles celles qui se sont avérées accidentellement résistantes aux radiations. Mais revenons à Galileo et 1802.

Figure 3. Lancement de Galileo avec la navette spatiale. Les ordinateurs de bord de la navette, créés dans les années soixante-dix, fonctionnaient sur des microcircuits d'un faible degré d'intégration, et seulement lors d'une grande mise à niveau, effectuée déjà au deux millième, les 386-e, 1802-e et PowerPC 750 civils résistants ont été embarqués.

Galileo, en raison de divers problèmes, n'a volé qu'en 1989, mais a été conçu presque immédiatement après les Voyagers et en utilisant leurs meilleures pratiques. «1802, personne dans l'équipe de développement n'a vraiment aimé», car les solutions discrètes, bien que plus lourdes, étaient beaucoup plus rapides. En conséquence, ses avantages étaient toujours contrebalancés par les inconvénients, et le sous-système de commande et de données de l'appareil (sous-système de commande et de données) a été construit en 1802, et le sous-système moins chargé, mais plus exigeant lié à la vitesse, du contrôle de manœuvre (sous-système de contrôle d'attitude et d'articulation) était contrôlé par un ordinateur 16 bits. assemblé à partir de puces bipolaires à quatre bits Am2900 (homologue soviétique - série 1802).

Galileo est également important pour notre histoire en ce qu'il a été le premier appareil dans lequel le problème des défaillances uniques a été pris en compte dans la conception. Dans les microcircuits fabriqués selon des normes de conception approximatives, ils n'apparaissent presque pas et personne ne connaît leur existence jusqu'à ce que les sondes de recherche atteignent les ceintures de rayonnement de Jupiter. La magnétosphère de Jupiter est si grande qu'une partie de ses satellites (Europe, Io et Ganymède) sont à l'intérieur! Les champs magnétiques de Jupiter accélèrent les ions lourds à une énergie colossale, dont la source est volcaniquement active Io. Ces conditions monstrueuses se sont avérées suffisantes pour provoquer des dysfonctionnements même dans les anciens microcircuits Pioneer, mais plus les normes de conception sont petites, moins il faut d'énergie pour commuter le bit en mémoire!

Figure 4. Une image du rayonnement autour de Jupiter. Source: Hans Huybrighs, «La faisabilité des observations in situ des panaches de vapeur d'eau d'Europe», 2015

En 1977, lorsque la conception de Galileo a commencé, les Voyagers n'avaient pas encore atteint Jupiter, et toutes les données de rayonnement disponibles ne concernaient que les Pionniers. Certaines de leurs erreurs mystérieuses ont ensuite été classées comme des défaillances uniques, mais ce fut plus tard, et jusqu'à présent, ni les codes d'autocorrection, ni aucun autre moyen de trouver et de corriger les erreurs n'ont été incorporés dans l'équipement embarqué Galileo. Après la découverte de la cause probable des défaillances des Pionniers et Voyagers (1982), tous les composants électroniques de Galileo, sélectionnés pour être résistants à la dose de rayonnement, ont été envoyés d'urgence à l'accélérateur: découvrez comment ils vont faire face avec un nouveau problème. Les résultats ont été décevants: si 1806, réalisé à l'aide d'une technologie relativement ancienne, s'est comporté normalement, alors dans le jeu de microprocesseurs bipolaires progressifs 2901, de 20 à 50% des coups de particules chargées ont causé des dysfonctionnements, et il était impossible de le démarrer. Que faire Deux options ont été trouvées:

- Essayez le dernier ordinateur de bord résistant à la joie basé sur l'architecture 1750A et recompilez tous les logiciels, après avoir écrit le compilateur. Le coût de cette option était estimé à 20 millions de dollars (les dollars d'alors, ils étaient nettement plus chers que les actuels).

- Pour commander d'urgence le développement d'analogues tolérants aux pannes de puces à problème 2901. Dans ce cas, tous les logiciels testés à plusieurs reprises n'ont pas pu être refaits. Sandia Labs a estimé le développement de nouvelles puces à 5 millions et une décision a été prise.

NASA Tech Briefs, Volume 10, Issue 3 donne quelques détails sur les puces développées par Sandia Labs: elles n'étaient pas bipolaires comme l'original, mais CMOS, il y en avait neuf types (sur une quarantaine de puces de la série originale), et elles étaient utilisées pour atteindre la tolérance aux pannes transistors plus larges que nécessaire, ainsi que des résistances dans les circuits de rétroaction des éléments de stockage.

Retraite sur les échecs simplesFigure 5. Schéma d'une cellule de mémoire statique à six transistors (6T SRAM)

Lorsqu'un SLC pénètre dans le drain d'un transistor fermé, une impulsion de courant d'ionisation se produit et deux processus commencent dans la cellule: le déclenchement par rétroaction positive et la dissipation de charge induite.

Laissez le coup se produire dans un transistor fermé M2, au drain duquel une impulsion de courant est apparue en conséquence. Le transistor M1 à ce moment est complètement ouvert et a une petite résistance, c'est-à-dire que le courant TZCh induit à travers lui va à la terre. Cependant, la capacité du noeud nQ peut être suffisamment petite pour se charger à une haute tension, ce qui entraînera la commutation du deuxième onduleur (M3-M4), qui, à son tour, commutera le premier onduleur via le retour. Il s'agit d'une défaillance radio-induite (bouleversement à événement unique, SEU). L'installation de résistances dans le circuit de rétroaction vous permet de ralentir le processus de rétroaction et de donner à la charge suffisamment de temps pour se résoudre.

Conception SA3000 - Radiant Resistant 8085

Le processus de développement de microcircuits résistants aux radiations à cette époque semblait pouvoir suivre les publications scientifiques. À titre d'exemple, j'ai pris un article de W. Kim et. al., «Radiation-Hard Design Principles Use in CMOS 8085 Microprocessor Family», publié en 1983 par IEEE Transactions on Nuclear Science.

Dans ce document, les employés de Sandia Labs expliquent comment ils ont fabriqué le SA3000 - une version radiante de l'Intel 8085 (ainsi que les SA3001 et SA3002 en tant que variantes de la RAM Intel 8155 et de la ROM Intel 8355). Ils ont commencé par obtenir Intel toute la documentation de développement, y compris les schémas de câblage et la topologie. Je ne refuserais pas non plus une telle chose, je suppose. Avec RHBP, la situation dans ce cas est la même que dans le précédent - une technologie de processus CMOS spéciale avec un régime de température optimisé pour des oxydes sans défaut, une couche n + enfouie pour se protéger contre l'effet thyristor. Ce qui est intéressant pour nous, c'est une description détaillée des approches de RHBD contre une dose complète et des défaillances uniques.La puce d'origine a été réalisée sur la technologie NMOS utilisant une logique dynamique, qui est extrêmement vulnérable aux fuites, en particulier dans le cas de transistors à seuil fort. La résistance aux radiations d'échantillons commerciaux variait de 700 rad (Si) à 30 degrés (Si). En principe, les meilleurs d'entre eux pourraient même être utilisés en orbite basse, mais pour les projets sérieux, des niveaux de résistance à la dose étaient nécessaires d'au moins un ordre de grandeur de plus. Par conséquent, Sandia Labs n'a pas copié la topologie existante dans une technologie rayonnante (ce qui n'aiderait pas en soi), mais a agi différemment. Pour assurer la compatibilité avec la puce d'origine, le circuit complet est divisé en blocs relativement petits et les circuits de chacun des blocs sont transférés vers une logique CMOS statique, qui est plus résistante aux fuites et au décalage de la tension de seuil des transistors.Cette approche préserve l'agencement mutuel des blocs dans la topologie et les connexions principales, simplifiant et accélérant le développement.Un certain nombre de principes ont été formulés pour une refonte réussie.- Les blocs doivent maintenir leur opérabilité dans la plage de tension de seuil des transistors à canal n de 2 V à presque zéro (à une valeur nominale de 1 V) et à canal p de -0,5 V à -4 V (à une valeur nominale de -1 V). Ce sont des exigences strictes du fait que lorsque les seuils des transistors sont décalés dans différentes directions, le seuil de commutation des portes logiques change et, par conséquent, la synchronisation des changements de circuit, obligeant le développeur à prévoir des délais beaucoup plus longs et à réduire la fréquence de la puce.

- , -4 5 p- , , Sandia Labs , 10 . , , NMOS CMOS , .

- , p- , NAND ( p- ) NOR ( ).

- Le décalage de seuil des transistors sous la dose de rayonnement varie en fonction du mode électrique dans lequel se trouve le transistor. Ceci est important pour toutes sortes de paires appariées, par exemple pour les amplificateurs d'enregistrement et de lecture en mémoire. Par conséquent, les deux puces mémoire sont conçues pour que les lignes d'accès soient constamment rechargées, et pas seulement lorsque cela est nécessaire.

Aucune mesure spéciale n'a été prise pour se protéger contre les défaillances uniques (telles que le codage de Hamming ou les cellules de mémoire plus complexes), car la simulation a montré que l'augmentation de la tension d'alimentation à 10 V est suffisante pour rendre la charge de commutation critique plus élevée que les valeurs raisonnables que le TZ peut introduire . Des tests ont confirmé l'efficacité de cette approche, démontrant l'absence de coupure de courant à 10 V et leur présence avec une baisse de puissance à 5 V.Au total, l'approche «classique» pour augmenter la résistance aux normes de conception de trois microns ressemble à ceci: le principal problème est le décalage de dose de la tension de seuil des transistors, l'utilisation d'une technologie spécialement développée est nécessaire, la protection contre l'effet thyristor se fait technologiquement, à partir de la dose - ensemble au niveau de la technologie et des circuits de bas niveau, en cas de défaillance unique, tout va bien grâce à l'augmentation de la tension d'alimentation. Selon les résultats, la puce de Sandia Labs avec une compatibilité broche à broche complète et structurelle avec l'original avait 18 000 transistors contre 6 500, mais la résistance à la dose était de trois ordres de grandeur plus élevée. Un point important a également été noté dans l'article: le processus de fabrication a été complètement fixé avant le début du développement, car son optimisation ultérieure pourrait compromettre la conception de la puce. Par exemple, en utilisant un diélectrique à grille plus mince,considéré à l'époque comme le principal moyen d'augmenter la résistance aux rayonnements, en raison d'un changement de capacité de grille, il affecte sérieusement la vitesse de fonctionnement des éléments de puce.Arséniure de gallium

Un changement ou même une création spéciale de technologie pour la production de puces résistantes au rayonnement à cette époque était quelque chose non seulement pris pour acquis, mais aussi nécessaire. Par conséquent, il est logique qu'en parallèle à la recherche de moyens de rendre la technologie CMOS au silicium plus stable, il y ait eu une recherche d'options alternatives. Le principal était l'arséniure de gallium.La recherche active dans le domaine de l'arséniure de gallium a duré du début des années soixante-dix au milieu des années quatre-vingt-dix et sa haute résistance aux radiations, causée par l'absence de diélectrique de grille dans les transistors JFET, a été l'un des principaux moteurs de ces travaux. Le point culminant a été 1984, lorsque DARPA a signé trois contrats pour le développement de microprocesseurs GaAs MIPS - avec RCA, McDonnell Douglas et la collaboration CDC-TI. L'une des exigences importantes des spécifications techniques était une limitation de 30 000 transistors, avec la formulation «pour que les processeurs puissent être produits en série avec un rendement acceptable». En outre, il existait des versions GaAs de la famille Am2900, des microcontrôleurs 1802, ainsi que des cristaux matriciels de base pour plusieurs milliers de portes et des puces de mémoire statique pour plusieurs kilobits.Vous pouvez immédiatement remarquer qu'en 1984-1994, le thème GaAs a été développé en URSS, et la série K6500 avec un degré d'intégration similaire a été créée chez Micron. Certes, si les Américains essayaient de faire ressembler le CMOS à la technologie CMOS, le K6500 implémentait une logique liée à la source (ISL) beaucoup plus rapide, mais plus complexe et gourmande. Les développements soviétiques en GaAs ont été lancés en même temps que ceux américains - les avantages l'emportaient sur le coût élevé exorbitant dû au rendement, s'élevant à quelques pour cent. L'arséniure de gallium est resté le matériau de l'avenir.Architectures RISC

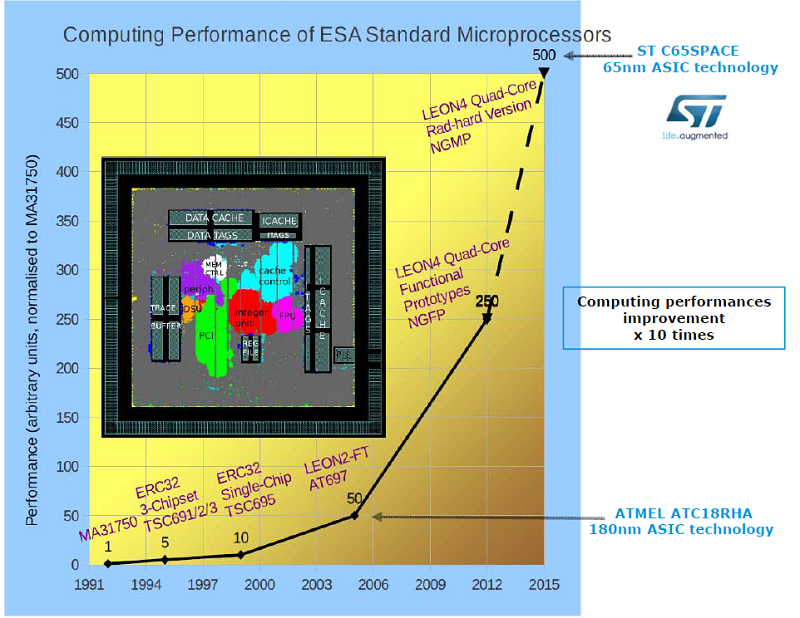

La souffrance du GaAs aux États-Unis a été considérablement étendue par le mode d'alors pour les processeurs RISC, qui promettait une réduction sérieuse du nombre de transistors sur une puce avec des performances similaires à celles du CISC. Bien sûr, les processeurs RISC ne vendaient pas seulement de l'arséniure de gallium, le silicium est également idéal pour cela. L'ensemble des Big Four - ARM, MIPS, SPARC, POWER - a été noté dans l'espace, mais d'une part, il est plus ou moins familier à tout le monde, et d'autre part, j'aurai des raisons d'en parler plus tard, alors voici maintenant un exemple moins connu, mais assez important pour l'architecture spatiale.En 1980, l'US Air Force a publié la norme Mil-Std-1750A, qui décrit le système d'instruction d'un microprocesseur 16 bits, pour réduire les coûts et unifier les logiciels d'aviation militaire. La norme ne réglemente en aucune façon les détails de mise en œuvre, ce qui a permis à divers fournisseurs de présenter leurs propres solutions compatibles avec tous les autres et avec les logiciels créés dans l'intérêt de l'USAF. À propos, le logiciel a été écrit dans le langage militaire spécial JOVIAL (Mil-Std-1589) ou dans le langage militaire non moins spécial Ada (Mil-Std-1815A). Soit dit en passant, beaucoup de systèmes de contrôle de la circulation aérienne fonctionnent toujours chez JOVIAL (ce qui, il n'y a pas si longtemps, a entraîné de nombreux problèmes en Angleterre, après quoi il s'est avéré que beaucoup d'efforts et d'argent ont été dépensés pour la formation du personnel dans la langue ancienne).La norme s'est avérée assez réussie et a gagné la distribution non seulement à l'USAF, mais aussi à la NASA, à l'ESA et même dans l'aviation militaire israélienne. Dans l'espace, 1750 processeurs de différents fournisseurs (à la fois sous forme de puces séparées et, par exemple, à partir de ces puces 2901 conçues pour Galileo) gèrent et contrôlent les missions américaines sur Mars, la mission sur Jupiter Cassini et bien d'autres. L'agence spatiale européenne Mil-Std-1750A et les puces anglaises MA31750 fabriquées par Dynex et Plessey, développées sur cette base, sont devenues la norme de facto. Devenue un jalon dans le développement de l'informatique à double usage, la norme 1750A a été déclarée inadaptée aux nouveaux projets de l'USAF en 1996, lorsqu'il est devenu clair que 16 bits étaient petits et qu'il était nécessaire de passer à des architectures 32 bits, qui étaient déjà installées et fermement en place. en électronique commerciale.Dans l'espace, le changement de génération est encore plus lent que dans l'aviation, et pendant de nombreuses années encore, les appareils exécutant le 1750A ont continué de fonctionner. Par exemple, la Rosetta européenne, envoyée sur la comète en 2004 et fonctionnant avec succès en orbite il y a seulement quelques années, ou la mission martienne indienne «Mangalyan», lancée en 2013.Je continuerai l'histoire détaillée de la prochaine génération de processeurs sur l'exemple des développements européens, donc je ne présenterai que les grandes lignes des puces américaines: la période «1802 + 8085» a été suivie de la période «1750 + 386», où 386 processeurs ont également été développés par Sandia Labs selon la documentation d'Intel; ces 386 volent vers l'ISS, ils ont également travaillé sur le Hubble après le remplacement des composants à l'aide de la navette spatiale. Puis, pendant un certain temps, une ligne de processeurs MIPS est apparue, dont le plus célèbre est le Mongoose-V dans New Horizons, et après que le marché américain a été de facto monopolisé par des processeurs RAD construits en utilisant l'architecture POWER. Ces processeurs contrôlaient les rovers Phoenix, Opportunity, Spirit and Curiosity, les télescopes Spitzer et Kepler - et généralement tout ce qui fonctionnait à la NASA depuis vingt ans.La dernière génération - RAD5500 - a été certifiée pour l'espace en 2016 et devrait effectuer son premier vol au jour le jour. Ce dernier est dû au fait que le nouveau programme HPSC (High Performance Spaceflight Computing) est en cours, dans lequel Boeing a remporté un appel d'offres pour le développement d'un processeur ARM multicœur, qui devrait devenir à l'avenir une plate-forme informatique unifiée pour les vaisseaux spatiaux de la NASA et de l'USAF. Il est à noter que le multi-core et le partage de ressources vous permettront de contrôler une partie de l'application en utilisant le système d'exploitation en temps réel (RTEMS dans ce cas), et le fait qu'il ne nécessite pas en temps réel d'utiliser Yocto Linux.dans lequel Boeing a remporté un appel d'offres pour le développement d'un processeur ARM multicœur, qui devrait devenir à l'avenir une plate-forme informatique unifiée pour les vaisseaux spatiaux de la NASA et de l'USAF. Il est à noter que le multi-core et le partage de ressources vous permettront de contrôler une partie de l'application en utilisant le système d'exploitation en temps réel (RTEMS dans ce cas), et le fait qu'il ne nécessite pas en temps réel d'utiliser Yocto Linux.dans lequel Boeing a remporté un appel d'offres pour le développement d'un processeur ARM multicœur, qui devrait devenir à l'avenir une plate-forme informatique unifiée pour les vaisseaux spatiaux de la NASA et de l'USAF. Il est à noter que le multi-core et le partage de ressources vous permettront de contrôler une partie de l'application en utilisant le système d'exploitation en temps réel (RTEMS dans ce cas), et le fait qu'il ne nécessite pas en temps réel d'utiliser Yocto Linux.Pour conclure la première partie, je note que jusqu'à récemment, les Américains s'en tenaient à l'approche éprouvée de la conversion des conceptions civiles dans l'espace en les transférant à des processus technologiques spécialement développés - HPSC semblera être le premier projet développé à partir de zéro. Le Mongoose-V susmentionné est un noyau MIPS commercial basé sur une matrice à matrice rayonnante, et l'ensemble de masques RAD6000 de première génération a été fabriqué à partir des mêmes fichiers de topologie que les PowerPC601 ordinaires. Dans le même temps, les progrès technologiques ont progressivement déplacé l'attention de certains types d'effets de rayonnement vers d'autres, car avec une diminution des normes de conception, l'épaisseur des diélectriques diminue, et avec elle le décalage de seuil des transistors; en parallèle, une diminution des normes de conception entraîne une diminution de la tension d'alimentation et une diminution de l'énergie de commutation des vannes. Ensemble, cela signifiequ'il était beaucoup plus facile d'obtenir une résistance à la dose de rayonnement acceptable, mais les échecs uniques de l'exotisme jupitérien au milieu des années 90 se sont transformés en un casse-tête majeur pour les développeurs, ce qui nécessitait des approches fondamentalement différentes pour la conception des microcircuits.

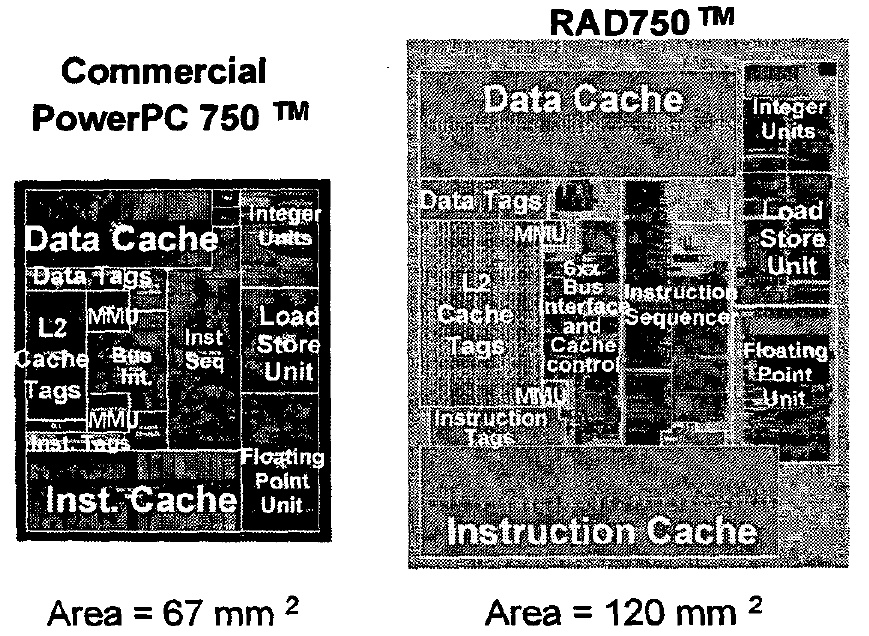

Figure 6. Comparaison des cristaux PowerPC750 et RAD750. Les puces sont fabriquées selon les mêmes normes de conception, leur surface en même temps double presque. Faites attention à la disposition des blocs presque identique - c'est ce qui se produit lorsque la compatibilité à bas niveau est assurée. D'énormes différences dans les tailles des blocs de mémoire suggèrent l'utilisation de cellules de mémoire résistantes aux radiations à transistors multiples (10T au lieu de 6T) avec redondance intégrée.

Un changement de paradigme - le cas de l'Agence spatiale européenne

L'histoire de l'ingénierie des processeurs spatiaux européens est inextricablement liée au nom de l'ingénieur suédois Jiri Gaisler. Il a rejoint l'ESA au milieu des années 80 et a commencé à développer les premiers microprocesseurs spatiaux européens propriétaires. Au début, il s'agissait d'un 1750A américain sous licence, puis de son propre développement basé sur le même système de commande (produit en Angleterre) - pour maintenir la compatibilité avec les logiciels déjà écrits. Et comme il s'agit d'un site informatique, voyons de quel type de logiciel il s'agit:

Des outils propriétairesCompilateur Ada de TLD (USA)

Open sourceLe système de compilation GNU pour le 1750 était initialement composé de deux parties principales.

un ensemble d'outils développés par CNS dans le cadre du contrat de l'Agence:

- Compilateur GNU C (gcc-2.7.2)

- Éditeur de liens, assembleur, archiveur, etc. (binutils-2.7)

- Bibliothèque c autonome

- Bibliothèque POSIX-Threads (IEEE 1003.1c-1995) (un cadre préemptif en temps réel)

- Débogueur GNU (gdb-4.16) pour le 1750

un ensemble d'outils développés en interne à l'Agence ou disponibles auprès de sources externes, à savoir:

- CRTX (le petit exécutif temps réel cyclique / synchrone SmartCom - externe)

- Simulateur autonome 1750 (O. Kellogg sim1750-2.3b - externe)

- wxIDE (un environnement de développement intégré portable basé sur J. Smart wxWindows 2.65 - interne)

Un point important qui distingue le travail de l'Agence Spatiale Européenne en termes de logiciel est le soutien et le paiement ciblés et systématiques pour la création de produits open source, ainsi que la création d'écosystèmes pour la réutilisation du développement et la réduction des coûts. Non seulement pour les logiciels: pour les microcircuits résistants aux rayonnements, l'Institut belge IMEC crée et soutient pour les intérêts de l'ESA les plateformes de développement DARE (Design Against Radiation Effects), qui incluent des itinéraires de conception, des PDK adaptés et de grands ensembles de blocs IP numériques et analogiques sur six processus de fabrication différents (350, 180 , 90 et 65 nm). Ces plateformes ne sont pas open source, mais sont concédées sous licence à tous les intervenants de contact de l'ESA si nécessaire.

ERC32 - le premier entièrement européen

Revenons maintenant à Jiri Geysler. La première génération de ses propres processeurs européens d'architecture 1750A (un kit à trois puces a été achevé en 1989, le MA31750 entièrement intégré en 1991) a été développée en tenant compte de la mission Rosetta, qui devait devenir l'un des fleurons d'un vaste programme scientifique américano-européen, qui comprenait également le télescope " Hubble »et des missions pour étudier le soleil et les planètes.

«Rosetta» est un appareil au destin long et complexe. Le projet a commencé en 1986, en collaboration avec les États-Unis et était censé réutiliser de nombreuses parties des appareils Mariner MkII (les jambes du 1750A se développent à partir d'ici), mais après un certain temps, le Congrès américain a annulé le financement de la partie américaine du programme (converti plus tard en un budget inférieur pour la sonde Cassini), et L'Europe est restée seule. En 1994, lorsqu'il est devenu clair que la mission d'origine, qui comprenait la livraison de matières cométaires à la Terre, ne pouvait pas être retirée à elle seule, les tâches de la mission ont été reformulées; dix ans plus tard, en 2004, Rosetta a commencé son voyage vers la comète Churyumov-Gerasimenko, et en 2014, lorsqu'elle l'a atteint, les nouvelles pouvaient être lues, y compris sur les circuits anciens avec les performances d'une calculatrice de poche. Et ce n'est pas encore assez de nouvelles dans les nouvelles sur les processeurs de pile du module d'atterrissage Philae qui implémentent le langage Forth.

Le sort de Rosetta a clairement montré à l'ESA que dépendre de partenaires américains n'est pas la meilleure idée, et l'agence a commencé à investir beaucoup d'argent dans des programmes pour atteindre l'indépendance technologique ou, à notre avis, dans la substitution des importations. Trente ans plus tard, ces programmes continuent d'exister, recevant un élan relativement nouveau lié au désir de l'Europe d'avoir accès au marché spatial russe et, plus important encore, au marché spatial chinois, quelles que soient les restrictions à l'exportation, les sanctions et les guerres commerciales des États-Unis avec la Chine.

Ayant acquis suffisamment d'expérience, l'équipe ESA a entrepris une tâche plus ambitieuse: un processeur 32 bits. À cette époque, il était toujours à la mode de proposer vos propres architectures RISC, mais l'ESA n'a pas alloué d'argent pour de tels divertissements, suggérant aux développeurs de choisir l'une des ISA existantes, en plus non propriétaires et de préférence avec un bon écosystème logiciel. Après quelques études et discussions ultérieures avec quelques dizaines d'entrepreneurs potentiels de l'ESA, le choix s'est porté sur SPARC, qui possède toutes les qualités nécessaires et est déjà distribué gratuitement au début des années 90 par un consortium réputé dirigé par Sun et Fujitsu. Un fait amusant: ARM a été envisagé, mais a été rejeté en raison de la petite quantité de logiciels. Parmi les autres exigences intéressantes pour le processeur, il y avait la prise en charge matérielle du langage Ada pour accélérer le travail du logiciel déjà écrit pour le 1750A, ainsi que la présence de modèles VHDL pour accélérer le développement de systèmes basés sur un processeur.

Un point fondamentalement nouveau dans les exigences de développement était que le microprocesseur lui-même n'était pas développé comme une puce, mais comme un modèle de processeur de haut niveau en VHDL. Cela a été fait afin de ne pas dépendre du fabricant de puces en particulier et d'assurer la disponibilité du processeur pendant de nombreuses années à venir, même si quelque chose arrive à l'usine sélectionnée. Selon la tradition américaine, la conception de base était basée sur le processeur commercial Cypress CY601, et l'usine française Temic Semiconductor (processus de fabrication volumétrique résistant aux rayonnements avec des normes de conception de 800 nm) était responsable de la résistance aux radiations. Au lieu des trois années prévues, le projet a duré cinq ans (1992-1997), la conception a été finalisée à la dixième (!) Itération des puces de test, Ada a dû être abandonné - mais le projet a donc été considéré comme réussi. La conception résultante s'appelait ERC32, un kit de microprocesseur à trois puces est entré sur le marché sous les noms TSC691-693, et même plus tard, le projet a été exécuté sur une seule puce comme TSC695 (20 MHz, 14 MIPS, 4 MFLOPS, 0,5 W).

En plus de l'implémentation habituelle de SPARC, ERC32 implémente la détection des défauts et la correction logicielle. 99% des déclencheurs dans les registres de l'unité entière, 100% des déclencheurs dans le FPU et les bus externes sont équipés de parité. Les erreurs détectées provoquent six types d'interruptions, dont la réponse est déterminée par programme. Dans le cas le plus simple, la gestion des interruptions consiste à répéter l'instruction échouée; dans le pire des cas, il peut s'agir d'un redémarrage de l'ordinateur de bord. De plus, l'instruction NOP est modifiée de telle sorte qu'au lieu de ne rien faire, elle vérifie la somme de contrôle reçue en tant qu'opcodes XOR de toutes les instructions précédentes. Si la somme ne correspond pas à la valeur attendue (obtenue lors de la compilation), une interruption est également appelée. Pour conclure la description de ERC32, je note qu'il n'y a pas de cache du tout, c'est-à-dire que les développeurs de processeurs ont poussé ce gros problème à d'autres personnes.

Les mesures proposées pour détecter les défaillances ont entraîné une augmentation de la superficie de 15%. Ou 130%, si l'on considère l'inclusion de deux ERC32 dans une configuration dupliquée, pour laquelle il y avait également un support matériel.

ERC-32 et le segment russe de l'ISS

Le premier appareil qui a utilisé ERC32 mérite sans aucun doute une histoire distincte, car il s'agissait du premier cas d'utilisation d'une unité étrangère dans un équipement russe essentiel à la mission, et aussi parce qu'il montre clairement à quel point les projets importants ne doivent pas être réalisés.

En 1992, en raison de nouvelles difficultés dans la construction de la station spatiale américaine à long terme Freedom, l'ESA a entamé des négociations sur la possibilité de sa participation au projet de la station orbitale russe Mir-2. La partie russe a accepté, mais elle n'avait pas de budget en 1992. Après deux ans d'intenses négociations (le vote au Congrès américain s'est terminé par le score de 216-215), les projets Mir-2 et Freedom se sont transformés en Station spatiale internationale (ISS), comme nous le savons aujourd'hui. Les accords russo-européens sont quant à eux restés en vigueur et l'ESA a lancé un projet de système informatique pour le module russe «Dawn» (DMS-R, Data Management System - Russian).

Les processeurs disponibles en 1995 - les radiants résistants 1750 et 386 - ne répondaient pas aux exigences de performances, et dans la charge du RAD6000, il était nécessaire d'acheter des cartes processeurs entières, ce qui ne donnait pas de flexibilité de développement. Une autre option était l'ERC32, mais à cette époque, il n'existait que sous forme de modèles, et aucune puce de test en silicium n'avait encore été fabriquée. Je ne sais pas ce qui a poussé ces gens, mais ce n’était clairement pas l’idée que quelque chose pouvait mal tourner avec un processeur avancé

inexistant . Et avec lui, bien sûr, il y avait un retard par rapport au calendrier (qui a été contourné pendant un certain temps en utilisant des analogues commerciaux) et une mer de bugs (qui était prévisible pour le premier grand projet d'une petite équipe de développement), et les bugs étaient mal documentés, même sous une constante directe contactez les développeurs DMS-R et les développeurs ERC32. L'un des bogues de FPU, que les développeurs de RSC Energia n'ont pu localiser en aucune façon, a finalement dû être contourné avec des correctifs dans le système d'exploitation.

Il y a eu des retards supplémentaires (en 1998, le financement de l'espace en Russie n'était plus très bon), mais en 2000, les ordinateurs de bord développés par l'ESA ont été mis en orbite avec succès et ont depuis fonctionné à l'intérieur du bloc russe Zarya.

Figure 7. L'ordinateur de bord du module ISS Zarya basé sur le processeur ERC32.

En 1996, avant même la fin du projet ERC32, le développement des exigences pour ses héritiers a commencé. L'appétit des programmeurs est passé à 100-500 MIPS au lieu de 10, et le succès retentissant du projet original signifiait que l'Europe continuerait à travailler avec l'architecture SPARC dans un avenir prévisible. La tâche principale était la création d'une version monopuce d'ERC32, la plus prometteuse étant le nouveau cœur de processeur.

LEON-FT

La principale caractéristique du projet LEON-FT était la tâche initiale de créer non pas un produit final sous la forme d'une puce, mais un noyau sous licence sous la forme d'un code vhdl, et d'assurer la tolérance aux pannes au lieu de la dureté de rayonnement. L'expérience d'ERC32 a montré qu'elle nécessite une duplication pour un fonctionnement fiable, et la prochaine étape logique était de développer un système qui n'en a pas besoin. La solution à ce problème nécessitait non seulement la détection, mais également la correction des défaillances au niveau matériel, sans utiliser de logiciel. Les idées de tolérance aux pannes et de durcissement aux radiations par conception n'ont bien sûr pas été inventées par les auteurs LEON-FT, mais avant eux, cette approche était principalement envisagée au niveau des transistors, et ils ont été les premiers à délier complètement la lutte contre les pannes uniques de la mise en œuvre physique de la puce et ont fait de l'objectif du projet de créer une puce stable. sur la technologie commerciale et sur toute technologie disponible à un moment donné - résolvant ainsi le problème de l'obsolescence des processus technologiques et des fermetures d'usines. Ainsi, un changement de paradigme a été enregistré: vingt ans avant de voir avec l'exemple des puces SA3000, le problème principal était la pleine dose de rayonnement, qui a été combattue avec des méthodes technologiques, et les défaillances uniques ont été considérées selon le principe résiduel. En 2000, l'orientation a changé, les défaillances uniques sont devenues le principal problème et l'attachement à une technologie spécifique a commencé à être considéré comme un inconvénient et non comme un mérite, même si l'usine était testée et fiable. Soit dit en passant, maintenant l'anglais (et pas un mot sur le Brexit) Dynex Semiconductor appartient aux Chinois, et le Temic français est devenu une partie de la micropuce américaine.

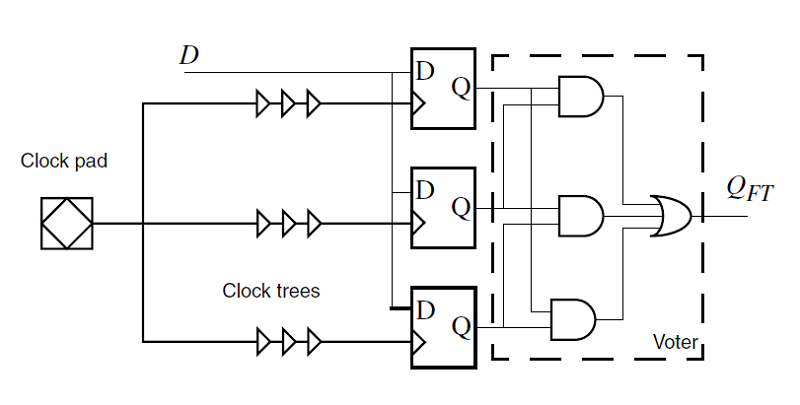

Le noyau LEON-FT a été écrit en VHDL et équipé d'un configurateur qui vous permet de choisir différentes options de protection contre les pannes uniques pour différentes parties de la puce: pour un fichier de registre et une mémoire cache (le cache est apparu!) Un / deux bits de parité ou un code de Hamming ainsi que le forçage cache miss, pour les déclencheurs dans le chemin de données la présence ou l'absence de triple redondance, pour un pipeline (un pipeline est apparu) - la possibilité de réinitialiser et de réessayer à partir d'une instruction ayant échoué. Ainsi, la seule dépendance à l'implémentation physique réside uniquement dans les fonctionnalités d'interface avec des blocs de mémoire personnalisés qui composent le fichier de registre. La croissance de la zone centrale avec une protection maximale hors caches est d'environ 100%, compte tenu - environ 40%; avec toutes les options désactivées, il s'est avéré être le noyau SPARC V8 publié en Open Source sous le nom de LEON (sans le préfixe -FT). Plus tard, cette pratique s'est poursuivie et les versions ultérieures de LEONx dans la version instable ont été présentées dans le domaine public, et les versions configurables à sécurité intégrée de LEONx-FT ont été autorisées pour de l'argent pour créer des micropuces ou comme IP douce pour le firmware des FPGA. En effet, comme LEONx-FT n'est en aucun cas attaché à la technologie, rien ne les empêche d'être utilisés dans les FPGA - bien sûr, si la condition (plutôt stricte) pour l'absence de défaillances dans la mémoire qui contrôle les connexions des éléments sur la puce est remplie. Cependant, si cette mémoire n'est pas SRAM, mais flash ou EEPROM, alors c'est une idée assez réaliste, même sans tenir compte de l'existence de FPGA tolérants aux pannes dans lesquels la mémoire de configuration est matériellement couverte de codes auto-corrigés.

Figure 8. Déclencheur troyed.

Note de conception de bibliothèque: pour la compatibilité avec toutes les bibliothèques, l'élément de vote ici est assemblé à partir de portes logiques ordinaires. Bien sûr, il n'est lui-même pas protégé contre les défaillances uniques, mais il est beaucoup moins qu'un déclencheur ordinaire, ce qui signifie que la probabilité d'y entrer est plus faible et que la défaillance est courte, mais pas verrouillée. Si cela ne suffit pas, il existe des implémentations spéciales de l'élément de vote au niveau du transistor, plus résistantes aux pannes que l'option illustrée sur la figure, et elles peuvent être ajoutées à la bibliothèque en tant que primitives. Aux normes de conception de 1000 à 100 nm, un grand nombre d'implémentations intéressantes d'éléments logiques avec une tolérance aux pannes accrue sont possibles, permettant de modifier au minimum la conception logique du microcircuit et de ne pas introduire de conceptions triples complexes. Les options les plus populaires sont la duplication interne des éléments et le filtrage intégré (par exemple, sous la forme de résistances dans les circuits de rétroaction en mémoire).

Figure 9. Cellule de mémoire DICE avec duplication intégrée; En raison des rétroactions croisées, une défaillance n'est possible que si elle frappe simultanément deux onduleurs, ce qui est relativement facile à éviter. À droite, les topologies d'une cellule de mémoire ordinaire et de DICE.

LEON-FT était un projet d'essai et n'était pas destiné à la commercialisation; Ce développement, ainsi que les produits commerciaux ultérieurs - les noyaux LEON2-FT - ont été réalisés par Geisler dans sa propre entreprise Gaisler Research, située à Göteborg. Atmel, qui a acquis Temic, une société ERC32, a obtenu les droits exclusifs de LEON2-FT; le produit résultant est la puce AT697, largement connue y compris en Russie, réalisée sur la technologie rayonnante spéciale Atmel et du fait qu'Atmel est une société américaine soumise à des restrictions à l'exportation et à des sanctions. En 2008, Gaisler Research a été vendu aux Américains par Aeroflex, puis l'anglais Cobham les a achetés, puis le Brexit a commencé, et maintenant Cobham achète un investisseur américain sous le hurlement de l'inadmissibilité de gaspiller le trésor national et la défense nationale. Telle est l'histoire de la substitution des importations et de l'indépendance technologique en Europe.

La version actuelle - LEON5 - dispose d'un pipeline à huit étages, d'un prédicteur de branche et d'autres caractéristiques des microprocesseurs modernes.À partir de la troisième version, Gaisler propose non seulement des cœurs de processeur, mais également une grande bibliothèque de blocs IP variés, permettant aux utilisateurs de créer des systèmes sur une puce qui conviennent à leurs besoins spécifiques. exigences, ainsi qu'une gamme assez large de logiciels propriétaires, tiers et open source (une description détaillée peut être trouvée

ici , les systèmes d'exploitation incluent VxWorks 6.9 et 7.0, RTEMS 4.10 et 5, ainsi que Linux basé sur le noyau 3.10 et 4.9).

Une petite digression sur l'économie et la planificationLEON sont considérés comme les puces spatiales à grande échelle les plus performantes. Dans le même temps, la circulation totale des deux variantes ERC32 était d'environ cinq mille unités, et la circulation des puces Atmel basées sur le noyau LEON2-FT était d'environ un mille et demi mille unités. American BAE Systems s'enorgueillit de brochures avec 200 ordinateurs de bord avec le RAD6000 et cent cinquante avec le RAD750. Il est absolument clair qu'avec de telles circulations, le développement et la certification de tels microcircuits ne peuvent être commercialement justifiés à aucun prix pour le microcircuit, et le développement doit être subventionné par l'État (ou, dans le cas de l'ESA, l'union des États). De plus, la nécessité de subventionner le développement dans la plupart des cas s'applique non seulement aux microprocesseurs, mais aussi à la plupart des autres microcircuits pour les applications spatiales, des exceptions se trouvent le plus facilement parmi les puces relativement simples qui peuvent être développées à moindre coût et ensuite vendues en grandes quantités selon les normes spatiales. À son tour, cela crée les conditions d'une planification stratégique à long terme pour le développement de la base de l'élément spatial, en mettant en évidence les domaines clés et en réutilisant la propriété intellectuelle développée avec de l'argent subventionné. À cet égard, les modèles opérant aux États-Unis, en Europe et en Russie ne diffèrent que par les détails de mise en œuvre et le niveau d'organisation du processus.

Division du travail

Comme je l'ai dit ci-dessus, les cœurs IP LEONx-FT ne résolvent que le problème des pannes uniques; la protection contre la pleine dose et l'effet thyristor appartient à l'utilisateur, qui doit choisir soit un FPGA stable, soit une combinaison de technologies et de bibliothèques.

Examinons de plus près l'exemple de la puce Gaisler GR712 utilisée dans la récente mission lunaire israélienne Bereshit.Il existe trois niveaux de mise en œuvre. Au plus haut niveau, le GR712 est un processeur double cœur LEON3-FT. Au niveau de la production, il n'y a pas de procédé technologique commercial modifié à 180 nm de l'usine israélienne TowerJazz. Entre eux - un ensemble de bibliothèques résistantes aux radiations RadSafe, développé par la société israélienne Ramon Chips (du nom de l'astronaute Ilan Ramon, décédé lors de la catastrophe de Columbia). Ce sont les bibliothèques RadSafe qui, en raison des circuits et de la topologie des éléments logiques de base, garantissent l'absence d'effet thyristor et la résistance à la dose totale de rayonnement absorbée. De même, le GR716 - le microcontrôleur LEON3-FT - a été créé en partenariat avec IMEC, qui a fourni des bibliothèques logiques et des IP analogiques pour la technologie de traitement à 180 nm de l'usine UMC taïwanaise. GR740 - processeur,implémente le quad-core LEON4-FT - fabriqué sur la technologie microélectronique ST 65 nm, qui a fourni des bibliothèques radiantes pour son processus. Comme vous pouvez le voir, il n'y a vraiment aucun lien avec la technologie, et vous pouvez choisir librement des partenaires pour la mise en œuvre physique, selon la tâche que vous devez résoudre avec une puce particulière.