Il s'agit de la deuxième partie de l'article sur l'histoire des microprocesseurs pour les applications spatiales. La première partie est

ici . Dans ce document, sur les exemples de microcircuits américains et européens, nous avons examiné l'histoire du développement de puces résistantes aux radiations depuis les premiers processeurs monocristallins jusqu'à la fin du deux millième, lorsque les normes de conception pour les développements spatiaux étaient proches de 100 nm.

La prochaine grande étape pour garantir la résistance aux rayonnements a commencé avec la transition vers des valeurs inférieures à 100 nm, où presque toutes les nouvelles générations de technologies posent de nouvelles questions: changement de matériaux, modification des exigences topologiques, augmentation de la puissance statique (fuites sans rayonnement, qui s'aggravent encore sous une dose) , l'importance des effets uniques, qui se transforment en effets multiples, continue de croître. Ces tâches ont nécessité le développement de nouvelles approches et, étonnamment, un retour partiel aux anciennes, car certaines des choses qui se sont avérées excellentes aux normes de 1-0,18 μm ne fonctionnent pas à des normes plus fines. Par exemple, dans de telles technologies, pour augmenter le rendement, il est interdit de faire des transistors en anneau appréciés des concepteurs de puces résistantes aux radiations. Je raconterai comment les concepteurs font face aux nouveaux défis avec l'exemple de la Russie - et en même temps je comparerai les réalisations de nos compatriotes aux succès de collègues étrangers et montrerai à quoi s'attendre dans un avenir prévisible.

Modernité - l'exemple de la Russie

J'ai choisi la Russie pour illustrer la phase actuelle, non pas parce que les développements russes se distinguent à l'échelle mondiale, mais parce que cela n'a aucun sens d'écrire sur quelque chose de plus ancien. Il y avait beaucoup de microcircuits sympas en URSS, mais toutes les informations sur les produits à double usage étaient gardées secrètes, et maintenant vous ne pouvez trouver que des vélos de la forme «après l'accident de Tchernobyl, Gorbatchev est venu personnellement chez les développeurs des robots pour faire face aux décombres et a ramené le microprocesseur radiant VM6» (en fait, les mots clés «maintient l'opérabilité dans un large éventail de facteurs mécaniques, climatiques et

autres » sont contenus dans la description non pas «xxxxxBM6», mais 1806BM2). Il y a des petites choses aléatoires: dans la série 1839, selon les interviews disponibles de développeurs créés pour les besoins industriels, il y a une puce N1839VZh2 - un élément de vote. Dans les ordinateurs conventionnels, l'élément majoritaire n'est nécessaire pour rien, mais si vous cherchez un peu sur Google, vous pouvez découvrir que la série 1839 est à bord des ordinateurs des satellites GLONASS-M. Il est dommage qu'une telle quantité de données ne permette rien d'écrire. En outre, au moment de l'avènement des microprocesseurs rayonnants, l'URSS s'était déjà fermement engagée sur la voie de la copie des développements occidentaux, de sorte qu'il ne fallait pas s'attendre à des innovations spéciales.

Les années 90 en microélectronique ont été marquées par la survie et la compression des derniers jus de l'héritage soviétique. Un revirement conditionnel s'est produit en 2003, qui s'est avéré mouvementé: chez NIISI RAS, sa propre usine aux normes de conception de 500 nm a été lancée, les premiers processeurs de la famille Multicor sont entrés dans la série Angstrem, la société Digital Solutions a été fondée, dans l'ancien avant cela, un distributeur de Milandre a ouvert un centre de design. Puis est venu le programme cible fédéral «Développement de la base de composants électroniques et de l'électronique radio» pour 2008-2015, qui n'a pas atteint les objectifs fixés (45 nm d'ici à 2015, ventes de 300 milliards de roubles, etc., etc.), mais tout de même réussi à aider sérieusement la microélectronique russe. À l'heure actuelle, en Russie, il existe environ 150 à 200 centres de conception impliqués dans le développement de circuits intégrés, de géants tels que le Micron à des équipes de cinq à six personnes impliquées dans des créneaux. La grande majorité de ces équipes travaillent d'une manière ou d'une autre avec les commandes du gouvernement et créent des produits à double usage. De plus, la décennie entre 2003 et 2014 s'est écoulée non seulement dans le développement de nouveaux microcircuits russes et dans les tentatives de combler le fossé déjà catastrophique avec les fabricants étrangers; une tâche plus difficile que la création de nouveaux microcircuits a été de convaincre les fabricants de systèmes de commencer leur application. Après avoir épuisé l'arriéré soviétique, la plupart des techniciens du système sont passés massivement à des composants importés qui étaient mieux fabriqués, mieux documentés, plus fiables, plus accessibles - en général, il n'y avait vraiment aucune raison de faire autrement. Ensuite - un cercle vicieux de rétrocompatibilité et de réutilisation de l'arriéré existant, grâce auquel les développements intérieurs resserrés sont restés à la mer. En toute honnêteté, il y avait et il y a des entreprises parmi les fabricants d'équipements radio embarqués en principe et en coopération constante avec les développeurs nationaux de composants électroniques, mais en général, la situation dans l'industrie ressemblait à ceci:

Une citation d'une interview avec Nikolay Testoedov, directeur du plus grand constructeur russe de vaisseaux spatiaux ISS nommé d'après Reshetnev:

- Le satellite de communication militaire Blagovest a-t-il une large part de composants étrangers?

- Là, le ratio n'était pas non plus très bon, car jusqu'en 2014, alors qu'il n'y avait pas de risques ou de restrictions , nous avions acheté un grand nombre de composants étrangers. Le moment de la création de satellites pour le ministère de la Défense était plus important.

Il semble que je ne comprenne pas quelque chose dans la définition du mot «risque». Mais une fois dans les véhicules militaires, vous pouvez utiliser des composants importés, nous pouvons supposer que les «signets» dans les microcircuits n'existent pas ou tombent au démarrage en raison de surcharges.

Un changement radical est intervenu en 2014, lorsque, en raison de sanctions, de bonnes puces importées à double usage sont devenues inopinément indisponibles. Ici, il semblerait que c'était un grand moment pour se réunir et passer aux développements nationaux, mais à la place, la microélectronique russe est à nouveau tombée sur les rails glissants de la copie ou, comme on dit maintenant, de la substitution des importations. Cependant, j'étais trop emporté par les paroles, alors ajoutons-le avant même de regarder les normes de conception inférieures à 100 nm, examinons brièvement la situation des microprocesseurs et microcontrôleurs spatiaux russes sur la base des résultats de dix ans de développement et de cinq ans de substitution des importations.

Le zoo

Alors qu'aux États-Unis, il existe un monopole de facto sur le pouvoir, et en Europe - SPARC, en Russie, toutes les fleurs ont fleuri sur toutes les architectures.

- ARM : trois modèles de microcontrôleurs résistants aux rayonnements basés sur les cœurs Cortex-M0 et Cortex-M4F sont fabriqués par Milander, un autre Cortex-M0 est l'alliance Angstrem et Digital Solutions et trois autres Cortex-M4F sont NIIIS.

- MIPS : les cœurs RISCore32 «compatibles MIPS» contrôlent quatre processeurs multi-cartes hétérogènes résistants aux rayonnements développés par Elvis SPC; Les noyaux KOMDIV "de type MIPS" sont dans le développement de "Progress" NIIISI, NIIIS et NIIMA.

- SPARC : maître d'oeuvre pour le développement du russe LEON4 (1906MB016) - Voronezh NIIET. Fait intéressant, le Centre de Moscou pour les technologies SPARC (ICST) n'a rien à voir avec cela. Apparemment, l'expérience de Voronezh dans la conception de puces résistantes aux radiations s'est avérée plus importante.

- AMCS-96 : en général, le MCS-96 est une architecture 16 bits, mais les sombres génies Voronezh de NIIET ont fait une extension 32 bits pour lui et assemblé un microcontrôleur rayonnant dessus.

- PowerPC (presque là): il y a une puce du «Module» STC, qui n'a pas de résistance déclarée, mais qui est conçue pour «l'équipement embarqué». Apparemment pour l'avionique.

De plus, il existe plusieurs microcontrôleurs 8 et 16 bits, un choix de DSP / VLIW (le leur et les «analogues» de quelqu'un d'autre), puis presque tout: mémoire, BMC, FPGA, FPAA, ADC, DAC, micro-ondes, dispositifs discrets. Il existe des microcircuits d'application spatiale pour presque tous les goûts - mais le fait est que nous n'en avons pas besoin, mais compétitifs, bien documentés et bien pris en charge, et avec les deuxième et troisième points, les fabricants russes avaient traditionnellement tout (et il y a, qui est déjà là) mauvais.

Figure 11. Autre remarque sur la question de la diversité des microprocesseurs nationaux: voici à quoi ressemble habituellement un module processeur "substitué à l'importation". Nous avons agité le drapeau «nous avons un processeur national», puis continuons en mode normal. La même photo, en principe, peut être utilisée comme illustration de l'échelle de tout ce qui doit être importé.

Digression numériqueLes normes de conception sont une excellente figure de marketing, qui n'a pas grand-chose à voir avec la taille réelle des transistors et est vraiment importante pour un nombre limité d'applications, qui incluent le traitement des données, le stockage à grande capacité et le FPGA, où beaucoup de métal et de transistors vont à la connexion des unités de calcul. Dans toutes les autres applications, les normes de conception ne sont pas aussi critiques: les microcontrôleurs commerciaux modernes sont fabriqués selon les normes de 180 à 90 nm, et les microcircuits de puissance - 180 à 600 nm, voire plus. Le choix de la technologie dépend de nombreux facteurs, principalement des tâches à accomplir. Cela s'applique également aux microcircuits spatiaux, et malgré tous les volumes croissants de traitement de l'information à bord, une partie importante des microcircuits à bord est occupée par des choses complètement différentes - contrôle des actionneurs, télémétrie, conversion d'énergie, communications radio - et ne nécessite donc pas les dernières normes de conception.

Si vous produisez des puces à l'étranger, alors pour les produits dont vous ne déclarez pas qu'il est à double usage, il n'y a pas de risques, pas de restrictions , et vous pouvez courir sur n'importe quoi. Pour la production en Russie, des technologies avec des normes de conception allant jusqu'à 90 nm sont désormais disponibles, mais les «chevaux de bataille» pour les puces résistantes aux rayonnements de la plupart des développeurs russes sont la technologie Mikron volumétrique 180 nm et leur propre processus SOI 240 nm. Les usines, cependant, sont également pleines de problèmes avec les sanctions dues aux fournitures et équipements importés, mais c'est une histoire longue et triste.

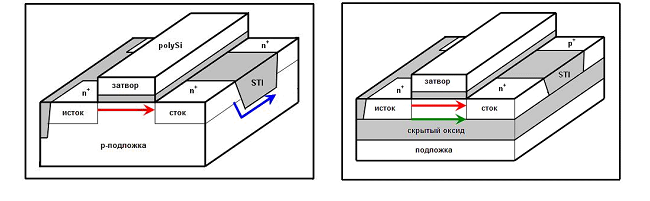

Figure 12. Comparaison de l'occurrence de courants de fuite dans les transistors volumétriques et SOI MOS. Les fuites sont la principale cause de pannes paramétriques causées par une dose complète de rayonnement. La figure montre clairement que le SOI ne résout pas tous les problèmes de résistance aux rayonnements, mais l'absence fondamentale d'un effet thyristor en raison de l'isolement complet de chaque transistor facilite la vie des développeurs, pour lesquels beaucoup d'entre eux sont très friands de SOI.

Puisqu'il est absolument impossible de mentionner tout le monde en Russie sans résistance aux radiations (et ils ne donnent pas d'informations sur les développements à chaque coin), je vais brièvement parler de trois entreprises qui traitent des microcircuits spatiaux non pas de temps en temps, mais de manière systémique et Bien sûr, ils sont engagés dans des microprocesseurs et des microcontrôleurs. Ces sociétés sont Elvis, Milander et NIISI. Je serais heureux de parler en détail du développement du NIIET, mais des méthodes de leur protection contre les radiations, il s'est avéré difficile de trouver quelque chose de plus spécifique que des mots généraux comme «des solutions structurelles et de circuits spéciales mises en œuvre dans le microcontrôleur qui garantissent son fonctionnement stable au niveau de la dose accumulée pas moins de 250 Crad et perte d'énergie linéaire (TZZ) jusqu'à 60 MeV ∙ cm2 / mg ”. L'exception est leur LEON, mais tout est le même que dans n'importe quel autre LEON-FT - déclencheurs triples et codage résistant au bruit en mémoire.

JSC SPC “Elvis”

La société Elvis développe la plate-forme Multicor depuis le début des années 2000, qui est une combinaison du noyau RISC de contrôle et du DSP sur une seule puce. Ils ont commencé un travail systémique en assurant la résistance aux radiations à peu près au même moment, en collaboration avec le Département d'électronique du MEPhI, en utilisant d'abord des technologies étrangères; après l'apparition de la propre technologie de 180 nm de Micron, Elvis est devenu l'un des premiers clients externes en développant une bibliothèque rayonnante de portes logiques et un ensemble de blocs IP pour créer des systèmes sur une puce. Dans les descriptions de la majorité des microcircuits de

la plate-

forme Multibort (la version résistante

aux radiations de Multicore), l'inscription «le microcircuit est conçu et fabriqué sur le territoire de la Fédération de Russie». Un jeu de puces est conçu pour construire des réseaux de données embarqués selon les normes SpaceWire et SpaceFibre et comprend des processeurs, DSP, mémoire, PLL et commutateurs.

Depuis le tout début, Elvis a été activement impliqué dans la création et le développement de la norme européenne pour le transfert de données à bord de vaisseaux spatiaux SpaceWire (les Américains utilisent leur propre norme - RapidIO), participant aux réunions du groupe de travail international et étant le principal moteur de la mise en œuvre de la norme SpaceFiber encore plus rapide.

Figure 13. Schéma fonctionnel du processeur 1892VM206. La fréquence de fonctionnement du cœur RISC est de 120 MHz, les cœurs DSP sont de 140 MHz, quatre ports SpaceWire de 300 Mbit / s chacun, deux ports SpaceFibre de 1,25 Gbit / s et puis il y a divers détails triviaux.

L'exécution sur notre propre bibliothèque résistante à la joie dans tous les circuits est déclarée comme le principal moyen d'obtenir une résistance aux radiations. Les détails sur certaines techniques architecturales dans les descriptions sur le site officiel sont peu nombreux, et une recherche de publications n'a pas rendu l'image plus claire car Elvis est peu publié et principalement sur d'autres sujets. Pour tous les processeurs, le codage de Hamming de toute la mémoire est déclaré, et dans l'une des puces il y a une triple réservation du fichier de registre et de l'arbre d'horloge. En se référant à l'exhaustivité de ces informations avec un scepticisme sain, supposons que la défense architecturale dans les Multiborts est un peu moins développée que dans LEON-FT.

JSC PKK «Milander»

Milander est un autre fabricant qui traite beaucoup de microcircuits résistants à la pluie. La plupart de leurs

puces résistantes à la joie sont en quelque sorte conçues pour les systèmes de télémétrie embarqués - ce sont des puces de traitement de signal provenant de capteurs, de commutateurs analogiques et numériques, d'ADC, de mémoire, et, bien sûr, notre sujet d'intérêt est trois microcontrôleurs. Plus précisément, pas trois, mais deux ans et demi, car les 1986BE8T et 1986BE81T ont tous deux des cœurs ARM Cortex-M4F à bord, des ensembles périphériques identiques et ne diffèrent que par le type de mémoire de programme - ROM dans le premier cas et SRAM dans le second. Supposons que la variante SRAM soit réellement nécessaire pour déboguer la variante ROM. 1923014 est équipé d'un noyau ARM Cortex-M0 plus modeste et fait partie du chipset pour l'organisation d'un système de capteurs multicanaux, et cette puce n'est pas un microcontrôleur au sens habituel, mais un contrôleur spécialisé, affûté pour une application spécifique.

Dans les spécifications pour 1986BE8T et 1986BE81T (elles en ont une en commun), vous pouvez trouver une description du «contrôleur pour le traitement des événements de défaillance, des échecs et des erreurs», y compris, entre autres, la fonctionnalité pour parer les échecs simples, similaire à celle décrite ci-dessus en utilisant également le processeur ERC32. une description détaillée du fonctionnement du codage correcteur d'erreurs (code Hamming SECDED) dans différents types de mémoire. Je n'ai pu trouver aucune information ouverte sur, par exemple, une triple réservation de déclencheurs ou un arbre d'horloge, supposons donc que du point de vue de la tolérance aux défaillances architecturales, 19868 se situe entre ERC32 et LEON-FT.

Figure 14. Section transversale SOI BCD avec transistor LDMOS haute tension dans une poche isoléeLa base technologique de la plupart des puces Milander résistantes aux rayonnements est constituée de bibliothèques et d'un ensemble IP propriétaire de technologie de processus BCD SOI à 180 nm de l'usine allemande XFAB. Cette technologie, contrairement au SOI conventionnel, possède une épaisse couche d'instruments en silicium (de l'ordre du micron) et se comporte dans la plupart des cas comme une technologie classique en vrac. La présence d'oxyde latent permet d'organiser l'isolement diélectrique des éléments les uns des autres et garantit ainsi l'absence d'un effet thyristor, et le fait qu'il soit à une grande profondeur vous permet de ne pas vous soucier des fuites à l'interface du silicium et d'un diélectrique caché, ce qui réduit la résistance à la dose de la technologie SOI conventionnelle.

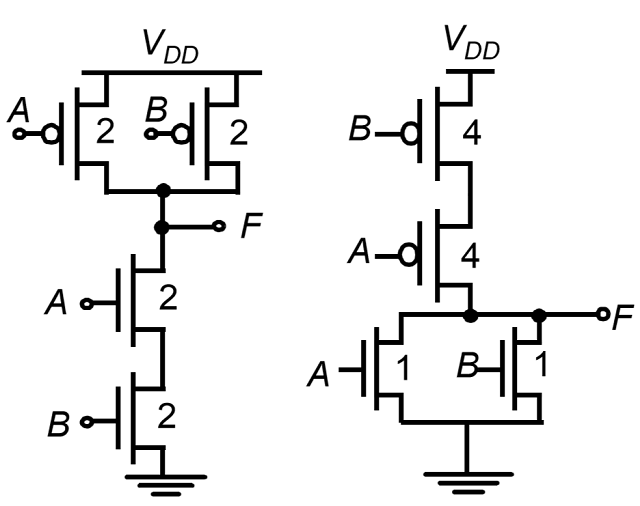

Figure 15. Comparaison de deux éléments OR.

La figure montre deux éléments logiques identiques (OR à deux entrées) des bibliothèques Milander réalisées en utilisant différentes méthodes pour augmenter la résistance aux radiations. Sur la gauche, vous pouvez voir des transistors en anneau à canal n qui neutralisent complètement la fuite du transistor. Cependant, une telle mesure radicale est souvent excessive, car les transistors linéaires conventionnels (parfois avec de légers changements) sont tout à fait suffisants pour des doses modérées de rayonnement, et en raison de leur application, une résistance suffisante peut être obtenue avec une surface et une consommation d'énergie plus petites - ce qui est clairement illustré sur la figure.

Une caractéristique importante de la technologie choisie par Milander est la présence de transistors et d'autres éléments conçus pour fonctionner avec des tensions élevées jusqu'à 200 V.L'intégration de la logique numérique et des dispositifs d'alimentation sur une seule puce vous permet de créer des convertisseurs DC / DC, des pilotes clés, des microcontrôleurs hautement efficaces avec des circuits intégrés pilotes et bien d'autres choses en demande. À l'heure actuelle, ces opportunités ne sont pas utilisées, mais lorsqu'elles commenceront, Milander obtiendra de sérieux avantages concurrentiels par rapport aux autres développeurs, car il n'y a pas d'analogues directs de cette technologie en Russie; ou 180 nm à une tension de 3,3 V, ou des tensions élevées aux normes de conception de 1 à 3 microns. Les travaux sur le sujet du LDMOS haute tension (et même leur joie) sont publiés par le NIIIS depuis quelques années, mais jusqu'à présent ce ne sont que des publications scientifiques, et il n'est pas question de production en série.

Au printemps, il y avait des nouvelles que les normes de conception de 500 nm "pour les microcircuits de sources d'alimentation secondaires" étaient maîtrisées chez Bryansk "Silicon-L", mais aucun détail n'a été donné.Figure 16. Feuille de route pour le développement de développements résistants aux radiations de Milander utilisant la technologie BCD SOI 180 nm. Et oui, vous voyez correctement le mot «FPGA» dans le coin inférieur droit, ils l'ont déjà et cela fonctionne.Institution d'État fédérale Centre de recherche scientifique pour la recherche sur les systèmes de l'Académie russe des sciences

NIISI explore systématiquement l'informatique, y compris les microprocesseurs radiants pour les applications spatiales. La recherche systématique, comme il sied à un institut universitaire, implique un KPI dans le nombre de publications, par conséquent, le suivi des progrès de l'institut est beaucoup plus facile que pour les entreprises commerciales. Nous nous intéressons à la partie «espace» de la ligne «COMDIV» (il y a aussi une partie «haute performance»).L'architecture de KOMDIV est une révision créative de MIPS32, sous licence NIIIS au début des années 90. Initialement, l'institut a travaillé avec des usines étrangères, et après l'apparition de sa propre production, il a commencé à travailler sur deux fronts, déplaçant la plupart de la ligne résistante à la joie. L'usine NIIIS est située à Moscou, à l'Institut Kurchatov; Il a été lancé en 2003 et est une production pilote à petite échelle située dans des grappes scellées sur une zone très modeste. En fait, les efforts des académiciens Betelin, Valiev et Velikhov ont réalisé le concept Minimal Fab qui est à la mode aujourd'hui, qui ne fonctionnait normalement que quinze ans plus tôt que les Japonais (et le premier a été inventé à Minsk par V.A.Labunov en 1983). Initialement, l'usine a travaillé avec des normes de conception de 500 nm, puis les normes de 350 et 250 nm ont été maîtrisées,ainsi que la technologie silicium sur isolant, qui est devenue la base de la ligne résistante aux radiations NIIIS.Deux principaux avantages du processeur 1890VM1T (technologie volumétrique 500 nm, 50 MHz) - il fonctionne et il est domestique. Mais les microcircuits russes sont si sévères que pour une orbite basse (notamment pour les ordinateurs de bord des nouveaux vaisseaux spatiaux «numériques» Soyouz-TMA et Progress-M), cela suffit, malgré l'absence totale de protection spéciale contre les radiations. Pour un fonctionnement normal, le 1890BM1T a besoin d'une puce compagnon chargée de travailler avec des interfaces externes (semblable à la façon dont ERC32 a été fabriqué sur trois puces). Pour des conditions plus graves, des analogues ont été développés (séries 5890, 1900 et 1907) utilisant la technologie SOI pour se débarrasser de l'effet thyristor. Dans le même temps, dans les puces de la série 1907, le contrôleur d'interface est déjà sur la même puce que le processeur lui-même.Comme je l'ai dit un peu plus haut, l'un des avantages de l'étude des produits NIISI est l'abondance de publications. À titre d'exemple, prenons deux articles publiés dans IEEE Transactions on Nuclear Science en 2011 et 2013. Le premier est MS Gorbunov et. Al., "Analyse de la sensibilité SEE du microprocesseur SOI CMOS: corrélation des résultats obtenus par différentes méthodes de test". Il décrit un processeur SOI à 500 nm avec une fréquence d'horloge de 33 MHz. Parmi les mesures architecturales déclarées pour augmenter la tolérance aux pannes, seule la parité du cache, où une erreur provoque la même interruption qu'un échec de cache. De plus, une topologie spéciale de transistors a été appliquée, qui supprime l'effet bipolaire parasite et augmente ainsi le seuil de dysfonctionnements (et en même temps, pour des raisons indépendantes, augmente la résistance à la dose de rayonnement complète). Relativement facilemais si l'objectif principal est la tolérance aux pannes, c'est exactement ce dont vous avez besoin. Et puis, lorsque le problème des pannes est résolu, vous pouvez commencer à penser à la tolérance aux pannes.Le deuxième article est PN Osipenko et.al., «Microprocesseur SOI tolérant aux pannes pour les applications spatiales». Ici, nous voyons déjà 350 nm au lieu de 500, et 50-66 MHz au lieu de 33 (performances 8,9 MFLOPS à 50 MHz). Ce n'est toujours pas 150 MHz, comme le RAD750 américain volant à peu près au même moment dans l'espace, mais des progrès sont évidents. Encore plus intéressante est la structure interne détaillée de la puce. Le noyau entier est triplé - pas les déclencheurs, comme dans LEON-FT, mais toute la logique combinatoire. Bien sûr, cela augmente la surface et la consommation de trois fois (1,8 W à 66 MHz), mais contribue aux pannes non seulement dans les éléments de stockage, mais aussi dans les éléments combinés. Ils sont beaucoup plus petits qu'en mémoire, car ils doivent coïncider dans le temps avec le front du signal d'horloge pour affecter quelque chose (et il y a aussi un effet de masquage lorsque la panne ne passe pas par la logique, mais c'est particulier),mais si vous avez déjà commencé à tout faire correctement, vous devez vous en débarrasser.

Et maintenant enfin moins de 100

Figure 19. Plusieurs pannes de mémoire en utilisant le cristal de test à 65 nm comme exemple.( ) , 65 . – , – . ! , – . , , , ( 2-2.5 ) – . , , . , , – , . – , . – , ( , ). – , . , ( ) – . , 65 DICE , . , .

Figure 20. Comparaison de la topologie d'une cellule mémoire 6T conventionnelle (en haut à droite) et d'une version étanche à la pluie de la bibliothèque DARE65 (IMEC, Belgique). Portes bleu vif, silicium brun - actif.Avec des déclencheurs triplés, c'est aussi amusant - pour que deux éléments de stockage ne s'écartent pas de la même particule, ils doivent être séparés par les mêmes 2-2,5 microns. À 180 ou 350 nm, ce n'est pas difficile, mais selon les normes à 65 nm, la zone du déclencheur triplé s'avère être douze fois plus grande que celle d'un déclencheur ordinaire (et la majeure partie de cette zone est vide). En conséquence, du point de vue de la consommation, de l'espace et de la simplicité de conception en CAO, un schéma fileté, exécuté sur des éléments complètement standard espacés suffisamment loin, est plus rentable que l'utilisation de déclencheurs tripliqués prêts à l'emploi et d'autres éléments de base avec redondance interne.Figure 21. Redondance modulaire triple et redondance modulaire double avec auto-vote. Tiré de l'article de J.Teufel, «Circuits de redondance double modulaire à vote

Single-Event-Transient Mitigation », IEEE Transactions on Nuclear Science, 2008 (Sandia Labs est toujours avec nous, ou plutôt toujours avec eux)

Le diagramme de la figure remonte à 2008 et montre que nos amis assermentés utilisent également beaucoup de choses intéressantes différentes dans des produits moins publics que RAD750 (et le principal domaine d'activité de Sandia Labs est le programme nucléaire militaire américain). En particulier, dans l'article mentionné ci-dessus et dans un certain nombre d'autres publications récentes, la question de savoir comment utiliser la redondance modulaire triple et double ensemble dans différentes parties de la puce est discutée en détail. Et au fait, si l'élément votant a un retard suffisamment important, alors dans le schéma de double redondance, il filtrera les défauts simples dans la logique, et le résultat sera aussi stable que la triple redondance.

Voyons maintenant à quoi ressemblent les éléments de bibliothèque sur la technologie 65 nm. Je cite à nouveau le travail de NIISI - Yu.B. Rogatkin et al., «Développement d'une bibliothèque d'éléments résistants aux rayonnements utilisant la technologie CMOS à 65 nm», Actes du NIISI RAS, 2018. Étant donné que le souci de la tolérance aux pannes est presque entièrement transféré à d'autres niveaux de développement - architecture et synthèse automatique de la topologie, compte tenu des restrictions sur l'emplacement des éléments - les principales tâches des développeurs de bibliothèques d'éléments sont à nouveau devenues la protection contre la dose totale absorbée et l'effet thyristor.

Figure 22. Cellules logiques réalisées à l'aide de la technologie 65 nm.

L'élément le plus à gauche de la figure est un onduleur de bibliothèque standard.

Le deuxième élément est sa version rayonnante, équipée d'anneaux de garde qui empêchent l'effet thyristor. Il est important que l'anneau n'ait des contacts avec le métal que d'un côté, et nous devons garder à l'esprit la résistance de la couche de silicium, qui peut être suffisamment grande pour affecter l'efficacité de cette solution.

Le troisième est le même onduleur, dans lequel les côtés de l'anneau de protection sont coupés pour économiser de l'espace.

Le quatrième est le même, mais avec des contacts avec la partie extérieure des anneaux de garde afin de bien contrôler leur résistance et de ne pas se soucier de la façon dont ils sont assemblés en blocs.

Cinquièmement - un bloc de deux onduleurs et un élément 2INE avec les parties de fermeture des anneaux de garde illustrés.

En ce qui concerne la pleine dose de rayonnement, ici, aux normes inférieures à 100 nm, tout est encore plus simple et plus compréhensible qu'avec les technologies plus anciennes. Les courants de fuite en eux sont déjà sans rayonnement, tout est posé sur eux, et donc, il ne reste plus qu'à introduire une correction supplémentaire pour le fait qu'ils vont continuer de croître. Les technologies typiques de ce niveau offrent généralement trois options pour les transistors - avec une tension de seuil basse (rapide, mais avec de grandes fuites), avec une tension de seuil moyenne et avec une tension de seuil élevée (lente, mais avec de petites fuites), et l'utilisateur peut les combiner si nécessaire. Les bibliothèques standard sont généralement également disponibles en trois versions, et lors de la conception d'une bibliothèque résistante aux radiations, un compromis doit être fait entre la vitesse et les fuites, étant donné que les transistors sont connectés en série ou en parallèle.

Figure 23. Schémas des éléments logiques 2I-NOT et 2OR-NOT.

Dans l'élément 2, OU NON, les transistors à canal n sont connectés en parallèle, ce qui double la fuite, ce qui signifie qu'il est judicieux d'utiliser des transistors avec une tension de seuil plus élevée à cet endroit. Et en 2I-NOT ils sont connectés en série, et là vous pouvez laisser le seuil habituel des transistors. Et un tel raisonnement (de préférence soutenu par des données de mesure) doit être appliqué à plusieurs centaines d'éléments dans la bibliothèque, puis réfléchir à ce qu'il faut faire avec les éléments de stockage afin qu'ils soient moins confus et fuit à travers les clés analogiques couramment utilisées dans les déclencheurs modernes, ils n'ont pas tout cassé, et ainsi de suite.

À ce jour, NIISI dispose d'une plate-forme à part entière pour le développement aux normes de conception à 65 nm, y compris les bibliothèques, les blocs IP, les compilateurs de mémoire, les interfaces à haute vitesse, etc. Il est également important que cette plate-forme soit concédée sous licence à d'autres sociétés russes, ce qui permet d'accélérer la réduction de l'écart avec les Américains et de rattraper pratiquement les Européens. Si l'usine n'était pas TSMC, mais la sienne, comme en Amérique et en Europe ... Mais c'est une autre histoire qui se déroule sous nos yeux. Après 2014, la technologie de traitement Micron de Mikron a gelé au statut de «qualification de passage et maîtrise en production» après 2014, et il n'y a pas eu de nouvelles à ce sujet depuis un certain temps; mais au cours des derniers mois, il y a eu suffisamment de nouvelles sur les plans à long terme pour créer une production en Russie aux normes 28 nm. Quand ces plans seront mis en œuvre et s'ils le seront est une grande question.

En résumant cette partie, nous notons comment, avec une diminution des normes de conception, les tâches auxquelles sont confrontés les développeurs ont à nouveau changé. Les technologies profondément submicroniques sont résistantes à une dose complète de rayonnement, suffisante pour la plupart des applications, et vous permettent d'organiser la protection contre l'effet thyristor et les défaillances simples / multiples au stade du développement de la puce, sans modifier la technologie de processus d'origine. Cela permet de réduire les coûts de production et d'accélérer le développement de nouvelles technologies. Les principaux obstacles au progrès sont économiques: le développement et l'étude approfondie des puces de test et de «combat» deviennent de plus en plus chers à chaque nouvelle génération de technologie, et les maigres circulations de puces spatiales ne nous permettent pas de compenser correctement ces coûts. Par conséquent, les développeurs cherchent à maximiser les capacités de chaque technologie utilisée et à l'utiliser aussi longtemps que possible, en ne poursuivant que lorsque cela est absolument nécessaire et en créant des plates-formes de développement et en vous permettant de créer une large gamme de microcircuits. Les développeurs russes sont aujourd'hui un peu en retard sur leurs collègues occidentaux, et les raisons de ce retard ne sont pas scientifiques ou techniques, mais organisationnelles et économiques.

Forcément une brève analyse de tout le monde

Japon

L'agence spatiale japonaise JAXA est modérément impliquée dans l'activité internationale, et la plupart de ses recherches spatiales sont effectuées par les Japonais seuls. Les missions sont impressionnantes avec de l'ambition et des histoires époustouflantes sur le succès de surmonter les difficultés qui se posent en orbite. Si Matt Damon pouvait jouer une sonde spatiale, alors nous verrions déjà des films sur Hayabusa au box-office (les Japonais, d'ailleurs, les ont déjà tournés déjà trois pièces), et sur Akatsuki. Les microprocesseurs spatiaux, comme tout le reste, les Japonais ont leurs propres architectures, et même leurs normes de conception de production ne sont pas les mêmes que dans le reste du monde (300 et 200 nm par exemple). Je serais très heureux d'écrire à ce sujet en détail, mais il y a peu d'informations, et il n'y a presque aucune information dans une langue non japonaise, donc je vais devoir me limiter à un bref aperçu.

Figure 24. Une source typique d'informations sur les processeurs japonais résistants aux radiations.

Les principaux fournisseurs d'instruments JAXA sont Hitachi, NEC et MHI (Mitsubishi Heavy Industries). Dans les années 80, l'industrie japonaise était passionnée par le projet TRON, qui offrait une conception d'infrastructure de réseau de bout en bout. Les Japonais utilisent encore le système d'exploitation en temps réel TRON dans l'industrie et dans l'espace jusqu'à présent, mais l'architecture des microprocesseurs TRON a été assez rapidement abandonnée (bien que des puces résistantes aux radiations y aient été fabriquées et, très probablement, elles ont volé) au profit de MIPS64 (dans le cas de NEC) et d'une autre Architecture SuperH japonaise 32 bits (H est Hitachi; sa version SH2 peut être trouvée dans les voitures japonaises, et SH4 dans Sega Dreamcast et les produits automobiles Hitachi et Renesas).

Figure 25. Microprocesseurs spatiaux japonais. HR5000 - MIPS64, SOI-SOC - SH4.

Figure 26. Illustration des applications SOI-SOC2.

«SOI» dans SOI-SOC, bien sûr, signifie «silicium sur l'isolant». Le niveau technologique de SOI-SOC3 est de 200 nm, la prochaine génération en développement en aura moins. Également une petite mais importante citation de JAXA: «Il y a un gros problème d'erreurs douces dans les processeurs grand public / industriels en raison des neutrons atmosphériques au niveau du sol. La SOI-SOC MPU sera livrée en tant que pièces de haute fiabilité aux utilisateurs de ces processeurs. " Le problème des neutrons atmosphériques est principalement lié à l'aviation, mais c'est une autre histoire. C'est tout avec les Japonais, allez chez leurs voisins.

La Chine

Le programme spatial chinois est celui qui connaît la croissance la plus rapide et l'une des informations les plus fermées sur les processeurs japonais par rapport aux Chinois juste la mer. Il est difficile de dire quoi que ce soit de concret, sauf que les Chinois ont commencé avec une copie couche par couche de tout dans une rangée, et qu'en 2014, ils avaient beaucoup de positions pour la Russie qui faisaient l'objet de sanctions. Récemment, cependant, beaucoup d'argent a été investi à la fois dans l'astronautique chinoise et la microélectronique chinoise, et les derniers appareils volent sur des processeurs compatibles MIPS développés par l'Académie chinoise des sciences (cela ne ressemble à rien?) Loongson. Loongson Civilians construit des PC, des tablettes et même un supercalculateur; ce processus s'est considérablement accéléré après le déclenchement de la guerre commerciale entre les États-Unis et la Chine.

Israël

L'Agence spatiale israélienne a été fondée en 1981, son premier satellite a été lancé depuis Israël en 1988. Aujourd'hui, Israël développe et lance (indépendamment et depuis des ports spatiaux étrangers) plusieurs familles de véhicules civils scientifiques et militaires. Je n'ai pas pu trouver d'informations sur leur bourrage, mais j'ose suggérer qu'au moins les premiers véhicules de reconnaissance développés par l'un des principaux entrepreneurs de l'aviation israélienne ont volé sur des puces d'architecture 1750A. Dans le génie civil moderne, les entreprises israéliennes collaborent beaucoup avec leurs homologues européens, il est donc logique d’assumer l’utilisation des LEON. La confirmation de cela est que le satellite privé Bereshit a volé l'année dernière sur le GR712, une version de LEON développée et fabriquée en Israël.

Inde

En Inde, il n'y a pas de production de micropuces, seulement une usine expérimentale de l'académie locale des sciences (cela ne rappelle-t-il rien?) Avec des normes à 180 nm. Les Indiens effectuent des recherches sur la joie, mais rien d'important n'est entendu d'eux. Selon des informations fragmentaires provenant de diverses sources, ils ont utilisé / utilisent des options de processeur ERC32 et LEON pour leurs satellites, et la magnifique mission martienne "Mangalyan" a été entièrement contrôlée par les processeurs d'architecture Mil-Std-1750A (toujours européens).

Le Brésil

La microélectronique brésilienne est presque comme un programme spatial brésilien: vous n'en savez rien, mais elle existe. En particulier, les Brésiliens sont de grands spécialistes de la correction de défaillances uniques sur du matériel ordinaire à l'aide de méthodes logicielles (par exemple, l'exécution d'une partie des commandes plusieurs fois et la vérification des résultats) et de la tolérance aux pannes FPGA. Des groupes universitaires spécialisés participent activement à des conférences scientifiques internationales et réalisent des projets communs avec des collègues européens et américains.

Cela semble être tout. Les autres pays ne développent pas indépendamment des microprocesseurs spatiaux ou des systèmes basés sur eux, achetant des composants clés, des blocs ou des satellites assemblés sur le côté, comme le Pakistan, qui développe sa propre industrie des satellites en étroite coopération avec les Chinois. Eh bien, il est clair que le remplissage d'appareils iraniens et nord-coréens n'est connu que de leurs créateurs et, si chanceux, de certains services de renseignement. Nous ne sommes pas du renseignement, alors passons à la partie suivante.

Le futur proche - un exemple de tous ensemble

Le niveau technologique des derniers microprocesseurs spatiaux est de 45 nm pour les États-Unis (RAD5500), 65 nm pour l'Europe (GR740) et 65 nm pour la Russie (ils promettent de sortir quelque chose déjà cette année). De plus, dans les deux premiers cas, nous pouvons observer un changement de génération - aux États-Unis, la prochaine génération de processeurs spatiaux (HPSC) sera fabriquée non pas par le monopole actuel de BAE Systems sur l'architecture PowerPC, mais par Boeing sur ARM (selon les normes de conception de 32 nm sur la technologie SOI), mais en Europe Parallèlement à la sortie du prochain SPARC LEON, un processeur multicœur DAHLIA avec une architecture ARM aux normes de conception à 28 nm (également SOI) est en cours de développement. Parallèlement, l'Agence spatiale européenne, dans son désir habituel de ne pas dépendre des licences d'autrui, a commencé à développer la nouvelle architecture RISC-V, qui prend rapidement de l'ampleur dans le secteur commercial et se transforme en un écosystème logiciel. Les premiers prototypes de puces RISC-V modifiées TMR ont déjà été démontrés en 2018 par la collaboration Antmicro et Thales. Malgré la popularité de LEON (comme on dit, dans des cercles étroits), vers SPARC, il y a longtemps des questions sur le support logiciel, et les concurrents sont pressés d'en profiter. Les concurrents sont particulièrement pressés par ARM, car l'accès pratiquement gratuit à une énorme quantité de logiciels d'application industrielle et commerciale est un atout très important dans les conversations avec les développeurs de vaisseaux spatiaux, dont l'importance augmente rapidement par rapport au désir d'avoir une compatibilité descendante avec les anciens projets.

En plus des microprocesseurs et des DSP, où la vitesse est une priorité évidente, il y a une demande de microcontrôleurs. Il existe de telles puces sur la plupart des architectures voisées - européenne GR716 (SPARC / LEON), américaine RAD EMC (PowerPC), ARM de différents fabricants (Vorago, Microchip, Milander, Angstrom), versions étanches du MSP430 de Texas Instruments, MCS- 96 et MCS-51 de NIIET et ainsi de suite et ainsi de suite. Les microcontrôleurs protègent généralement plus simplement que leurs «gros» homologues, en mettant l'accent sur l'absence de défaillances (effet thyristor) et avec une correction minimale des cœurs achetés (ou sans correction et synthèse à l'aide de déclencheurs triples et de bibliothèques d'éléments spéciaux). Revenons aux processeurs, regardons quelles plates-formes de développement inférieures à 100 nm existent ou sont annoncées en ce moment.

Figure 27. Plate-forme de développement inférieure à 100 nm pour les circuits intégrés résistants aux rayonnements.

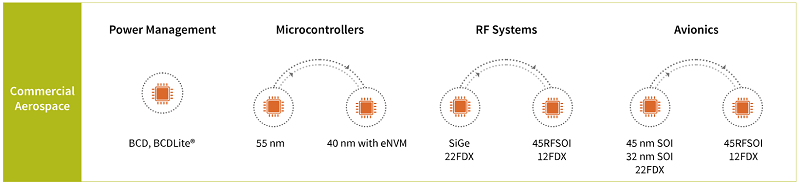

65 nm pour les développeurs d'Europe et de Russie, c'est déjà «aujourd'hui», et les Américains sont généralement passés de 150 immédiatement à 45 nm. Très probablement, au cours des dix prochaines années, ces technologies seront les principales et les normes les plus subtiles déjà illustrées dans ce diagramme passeront des stades précoces aux stades avancés du développement. Cependant, ce qui est montré dans la figure n'est que de grandes collaborations publiques; en fait, rien (sauf le temps et l'argent) n'interfère avec le développement de puces résistantes aux rayonnements sur d'autres processus technologiques sans bruit supplémentaire. Par exemple, GlobalFoundries propose de créer des puces aérospatiales toute une gamme de technologies pour différents goûts et budgets. C'est dans leurs installations que les derniers RAD5545 sont produits, et HPSC sera également produit chez eux; cela n'est pas surprenant, car les usines GloFo sont certifiées Trusted Foundry depuis leur appartenance à IBM. Et il est peu probable que tous les processus déclarés soient sans clients américains.

Figure 28. Offres GlobalFoundries pour l'industrie aérospatiale.

Chez GlobalFoundries, bien qu'ils ne soient pas américains, mais allemands (à Dresde), ils prévoient de produire leurs futures puces IMEC résistantes aux radiations (ce qui signifie toute l'Europe moins STM) et Milander.

Figure 29. Feuille de route de Milandra pour le développement de puces résistantes aux radiations basées sur la technologie 22 nm. Comme vous le voyez, il existe de nombreux plans, y compris de grands FPGA et des ADC rapides pour la radio définie par logiciel (SDR). La première puce de test a déjà été produite, nous attendons donc avec impatience de bonnes nouvelles.

Qu'est-ce que le FDSOI? FD est entièrement épuisé, complètement épuisé; la mince couche de silicium actif entre l'oxyde de grille et l'oxyde latent est complètement épuisée, et tout le canal du transistor l'occupe. Cela vous permet d'éliminer complètement la capacité parasite du drain et de la source, ainsi que de supprimer la ligne de fuite le long de la profondeur du silicium, ce qui est typique pour des technologies similaires en vrac, et de réduire la consommation d'électricité statique. De plus, au lieu d'utiliser plusieurs types de transistors, comme dans la technologie volumétrique, dans FDSOI, vous pouvez fournir localement une tension négative ou positive à un oxyde caché, modifiant ainsi le seuil du transistor (et avec lui la vitesse et la consommation d'énergie) - selon que la puce est en actif ou en mode veille. Ensemble, cela rend le FDSOI extrêmement attrayant, par exemple, pour l'Internet des objets. Ou pour les circuits spatiaux de faible puissance, l'avantage de la technologie SOI soulage automatiquement le développeur d'un mal de tête avec des pannes catastrophiques dues à l'effet thyristor.

Figure 30. Vues en coupe des transistors surround et FDSOI.

Le principal inconvénient du FDSOI en termes de résistance au rayonnement est le chemin de fuite supplémentaire le long de la frontière du canal et de l'oxyde latent. La charge s'accumulant dans l'oxyde caché joue le rôle d'une tension positive appliquée à l'oxyde caché, et au lieu de contrôler le comportement des transistors à travers la grille inférieure, l'effet du rayonnement doit être compensé. Et pour ce faire, une tension négative importante doit être appliquée - ce qui améliorera le processus d'accumulation de charge dans l'oxyde latent et aggravera la résistance à la dose. En général, un cercle vicieux est obtenu, dont l'issue peut s'avérer non triviale. Certes, il y a beaucoup de gens qui veulent le chercher, vous pouvez donc faire le plein de pop-corn. Le premier pop-corn sera très bientôt utile - le projet européen DAHLIA est presque terminé.

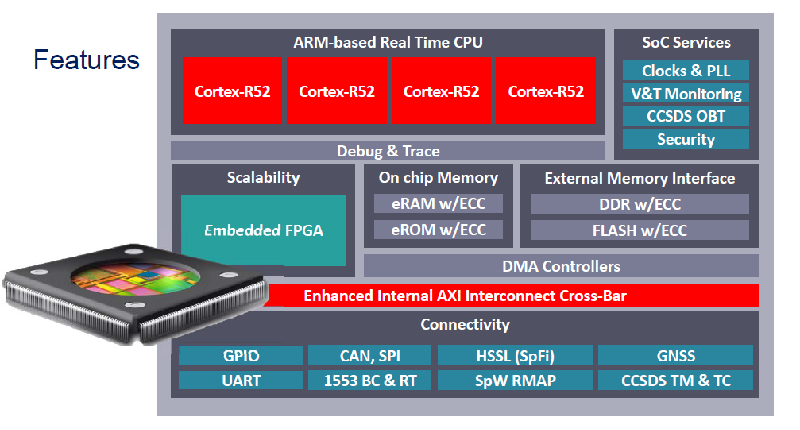

Figure 31. Schéma fonctionnel de DAHLIA. FDSOI 28 nm, quatre cœurs ARM-Cortex R52 (promesse 4000 DMIPS à 600 MHz), affinés pour les applications en temps réel avec séparation avancée des puissances, mémoire à bord, interfaces les plus populaires et même FPGA intégré pour 500 000 LUT, de sorte qu'une puce est précise couvrir les besoins de tous les utilisateurs pendant de nombreuses années à venir.

La technologie volumétrique, quant à elle, n'abandonnera pas.

Il peut offrir aux développeurs l'absence de chemin de fuite «supplémentaire» et, à long terme, des normes de conception plus faibles. De plus, dans les transistors FinFET, la grille commence à couvrir le canal de plus en plus densément, et l'oxyde isolant s'éloigne du fort champ électrique, ce qui devrait également affecter positivement la résistance à la pleine dose de rayonnement. IMEC commence déjà à développer des bibliothèques 16 nm résistantes aux rayonnements, et l'industrie commerciale continue d'adopter de nouvelles technologies.Figure 32. Différentes générations de transistors MOS.À long terme, le GAA (Gate All Around) de Samsung promet d'être résistant à une dose complète de rayonnement, soulageant complètement les développeurs des problèmes - il n'a tout simplement pas de voie latérale de la source au drain, devant le canal principal et l'obturateur principal, et un isolant de grille si subtile que le décalage de la tension de seuil sera négligeable même à très fortes doses. Mais, bien sûr, il y aura sûrement de nouvelles difficultés - non seulement avec des défaillances uniques, mais aussi, par exemple, avec des effets de polarisation qui sont déjà en plein essor avec les concepteurs de transistors HEMT à base de nitrure de gallium. Dans les dispositifs constitués de semi-conducteurs complexes, les effets quantiques et nanométriques ne sont pas nouveaux, et les développeurs de silicium auront très bientôt besoin de connaissances à leur sujet,donc pour les prochaines années, il faudra travailler pour assurer la résistance aux radiations des micropuces pour l'espace sera suffisante. Mais il y a aussi les collisionneurs de hadrons, l'énergie atomique et thermonucléaire; les progrès sont incessants et il ne va pas s'arrêter - mais je vais m'arrêter sur cette note positive. Merci d'avoir lu jusqu'au bout, j'espère que c'était intéressant.