Journal: Shock and Vibration 16 (2009) 45–59Auteurs: Robin Alastair Amy, Guglielmo S. Aglietti (E-mail: gsa@soton.ac.uk) et Guy RichardsonLieux d'auteurs: Astronautical Research Group, University of Southampton, School of Engineering Sciences, Southampton, UK

Surrey Satellite Technology Limited, Guildford, Surrey, Royaume-UniCopyright 2009 Hindawi Publishing Corporation. Il s'agit d'un article en libre accès distribué sous la licence Creative Commons Attribution, qui permet une utilisation, une distribution et une reproduction sans restriction sur n'importe quel support, à condition que l'œuvre originale soit correctement citée.

Annotation. À l'avenir, il est supposé que tous les équipements électroniques modernes auront une fonctionnalité toujours croissante, tout en conservant la capacité de résister aux chocs et aux vibrations. Le processus de prédiction de la fiabilité est entravé en raison des caractéristiques complexes des réponses et des défaillances des équipements électroniques, de sorte que les méthodes actuelles sont un compromis entre la précision des calculs et leur coût.

La prédiction fiable et rapide de la fiabilité d'un équipement électronique pendant son fonctionnement avec des charges dynamiques est très importante pour l'industrie. Cet article montre les problèmes de prédiction de la fiabilité des équipements électroniques, ralentissant la réception des résultats. Il convient également de noter que le modèle de calcul de la fiabilité est généralement construit en tenant compte d'une large gamme de configurations d'équipement pour un certain nombre de composants du même type. Quatre classes de méthodes pour prédire la fiabilité (méthodes de référence, données de test, données expérimentales et modélisation des causes physiques de la défaillance - physique de la défaillance) sont comparées dans cet article pour sélectionner la possibilité d'utiliser l'une ou l'autre méthode. Il est à noter que la plupart des défaillances des équipements électroniques sont causées par des charges thermiques, mais cette revue se concentre sur les défaillances causées par les chocs et les vibrations pendant le fonctionnement.

Note du traducteur.

Note du traducteur. L'article est une revue de la littérature sur ces sujets. Malgré son âge relativement important, il constitue une excellente introduction au problème de l'évaluation de la fiabilité par diverses méthodes.

1. Terminologie

Réseau de grilles à billes BGA.

Processeur DIP double en ligne, parfois appelé package double en ligne.

Élément fini FE.

PGA Pin Grid Array.

PCB Printed Circuit Board, parfois connu sous le nom de PWB (Printed Wiring Board).

Porte-puce en plastique PLCC.

Trou traversant plaqué PTH, parfois appelé trou traversant.

QFP Quad Flat Pack - également connu sous le nom d'aile de mouette.

Alliages à mémoire de forme SMA.

Technologie de montage en surface SMT.

Note des auteurs de l'original: Dans cet article, le terme «composant» fait référence à un appareil électronique spécifique qui peut être soudé à une carte de circuit imprimé, le terme «boîtier» fait référence à tout composant d'un circuit intégré (généralement tout composant SMT ou DIP). Le terme «composant attaché» fait référence à toute carte de circuit imprimé ou système de composants, tout en soulignant que les composants attachés ont leur propre masse et rigidité. (L'emballage en cristal et son effet sur la fiabilité ne sont pas pris en compte dans l'article, par conséquent, le terme «emballage» peut être compris davantage comme le «boîtier» d'un type ou d'un autre - environ la traduction).

2. Énoncé du problème

Les charges de choc et de vibration appliquées à la carte de circuit imprimé provoquent des contraintes sur le substrat de la carte de circuit imprimé, les boîtiers de composants, les conducteurs de composants et les joints soudés. Ces contraintes sont dues à une combinaison de moments de flexion dans la carte de circuit imprimé et à l'inertie de la masse du composant. Dans le pire des cas, ces contraintes peuvent provoquer l'un des modes de défaillance suivants: délaminage de la carte de circuit imprimé, destruction du joint de soudure, destruction du plomb ou destruction de l'emballage des composants. Si l'un de ces modes de destruction s'est produit, une panne complète de l'appareil suivra probablement. Le mode de défaillance rencontré pendant le fonctionnement dépend du type d'emballage, des propriétés de la carte de circuit imprimé, ainsi que de la fréquence et de l'amplitude des moments de flexion et des forces d'inertie. La lenteur des progrès dans l'analyse de la fiabilité des équipements électroniques est due aux nombreuses combinaisons de facteurs d'entrée et de types de pannes à prendre en compte.

Dans la suite de cette section, nous allons essayer d'expliquer la complexité de considérer simultanément différents facteurs d'entrée.

Le premier facteur de complication à considérer est la large gamme de types de paquets disponibles dans l'électronique moderne, car chaque paquet peut échouer pour diverses raisons. Les composants lourds sont plus sensibles aux charges inertielles, tandis que la réponse des composants SMT dépend davantage de la courbure du circuit imprimé. Par conséquent, en raison de ces différences fondamentales, ces types de composants ont des critères de défaillance considérablement différents, selon la masse ou la taille. Ce problème est encore exacerbé par l'émergence constante de nouveaux composants disponibles sur le marché. Par conséquent, toute méthode proposée pour prédire la fiabilité doit s'adapter à de nouveaux composants afin d'avoir une application pratique à l'avenir. La réponse de la carte de circuit imprimé aux vibrations est déterminée par la rigidité et la masse des composants qui affectent la réponse locale de la carte de circuit imprimé. Il est connu que les composants les plus lourds ou les plus gros modifient considérablement la réaction de la carte aux vibrations aux endroits de son installation. Les propriétés mécaniques de la carte de circuit imprimé (module d'Young et épaisseur) peuvent affecter la fiabilité d'une manière difficilement prévisible.

Une carte de circuit imprimé plus rigide peut réduire le temps de réponse global de la carte de circuit imprimé sous charge, mais en même temps, les moments de flexion appliqués aux composants peuvent en fait augmenter localement (en outre, en termes de défaillances induites thermiquement, il est en fait préférable de spécifier une carte de circuit imprimé plus compatible, car il réduit les contraintes thermiques imposées à l'emballage - env. La fréquence et l'amplitude des moments de flexion locaux et des charges inertielles superposées au paquet affectent également le mode de défaillance le plus probable. Les charges à haute fréquence de faible amplitude peuvent entraîner une rupture de fatigue de la structure, qui peut être la principale cause de défaillance (fatigue cyclique faible / élevée, LCF se réfère aux défaillances dans lesquelles la déformation plastique prédomine (N_f <10 ^ 6), tandis que HCF dénote une défaillance de la déformation élastique , généralement (N_f> 10 ^ 6) jusqu'à la panne [56] - note de l'auteur) La disposition finale des éléments sur la carte de circuit imprimé déterminera la cause de la panne qui peut se produire en raison de la tension dans un composant individuel causée par une charge inertielle ou moments de flexion locaux. Enfin, il est nécessaire de prendre en compte l'influence du facteur humain et des caractéristiques de production, ce qui augmente les risques de défaillance des équipements.

Lorsque l'on considère un nombre important de facteurs d'entrée et leur interaction complexe, il devient clair pourquoi une méthode efficace pour prédire la fiabilité des équipements électroniques n'a pas encore été créée. Une des revues de littérature recommandées par les auteurs à ce sujet est présentée dans IEEE [26]. Cependant, cette revue se concentre principalement sur des classifications assez larges des modèles de fiabilité, telles que la méthode de prédiction de la fiabilité dans la littérature de référence et réglementaire, les données expérimentales et la modélisation assistée par ordinateur des conditions de défaillance (Physics-of-Failure Reliability (PoF)), et n'aborde pas la défaillance de manière suffisamment détaillée. causée par des chocs et des vibrations. Foucher et al. [17] suivent un schéma similaire de l'examen de l'IEEE, étant donné qu'un accent important est mis sur les défaillances thermiques. La brièveté précédente de l'analyse des méthodes PoF, en particulier en ce qui concerne les défaillances dues aux chocs et aux vibrations, mérite leur examen plus approfondi. Un examen similaire à l'IEEE est en cours de compilation de l'AIAA, mais jusqu'à présent, la portée de cet examen est inconnue.

3. L'évolution des méthodes de prédiction de fiabilité

La première méthode de prédiction de fiabilité développée dans les années 1960 est actuellement décrite dans MIL-HDBK-217F [44] (Mil-Hdbk-217F est la dernière et dernière version de la méthode, publiée en 1995 - note de l'auteur). cette méthode utilisant une base de données de pannes d'équipements électroniques, permet d'obtenir la durée de vie moyenne de la carte de circuit imprimé, constituée de certains composants. Cette méthode est connue comme une méthode pour prédire la fiabilité selon la littérature de référence. Malgré le fait que le Mil-Hdbk-217F soit de plus en plus obsolète, la méthode de référence est toujours utilisée aujourd'hui. Les limites et les inexactitudes de cette méthode étaient bien documentées [42,50], ce qui a conduit au développement de trois classes de méthodes alternatives: simulation informatique des conditions de défaillance physique (PoF), données expérimentales et données de tests sur le terrain.

Les méthodes PoF prédisent la fiabilité analytiquement, sans recourir à l'utilisation de données précédemment collectées. Toutes les méthodes PoF ont deux caractéristiques communes à la méthode classique décrite dans Steinberg [62]: d'abord, la réponse vibratoire du PCB à un effet de vibration spécifique est recherchée, puis les critères de défaillance des composants individuels après exposition aux vibrations sont vérifiés. Une réalisation importante des méthodes PoF a été l'utilisation des propriétés distribuées (moyennes) de la carte pour créer rapidement un modèle mathématique de la carte de circuit imprimé [54], ce qui a considérablement réduit la complexité et le temps consacré au calcul exact de la vibration produite par la carte de circuit imprimé (voir section 8.1.3). Les développements récents dans le domaine des méthodes PoF ont amélioré la prédiction de défaillance des composants soudés SMT; cependant, à l'exception de la méthode Barkers [59], ces nouvelles méthodes ne sont applicables que dans des combinaisons très spécifiques de composants et de circuits imprimés. Il existe très peu de méthodes disponibles pour les gros composants, tels que les transformateurs ou les grands condensateurs.

Les méthodes de données expérimentales améliorent la qualité et les capacités du modèle utilisé dans les méthodes de prédiction de la fiabilité dans la littérature de référence. La première méthode basée sur des données expérimentales pour prédire la fiabilité des équipements électroniques a été décrite en 1999 par la méthode HIRAP (Honeywell In-service Reliability Assessment Program), qui a été créée par Honeywell, Inc [20]. La méthode des données expérimentales présente plusieurs avantages par rapport aux méthodes de prévision de la fiabilité dans la littérature de référence et réglementaire. Récemment, de nombreuses méthodes similaires sont apparues (REMM et TRACS [17], également FIDES [16]). La méthode des données expérimentales, ainsi que la méthode de prédiction de fiabilité selon la littérature de référence et réglementaire, ne permettent pas de prendre en compte de manière satisfaisante la disposition de la carte et l'environnement de travail de son fonctionnement dans l'évaluation de la fiabilité. Cet inconvénient peut être corrigé en raison de données sur les pannes de carte, de conception similaire, ou en raison de cartes qui étaient dans des conditions de fonctionnement similaires.

Les méthodes de données expérimentales dépendent de la disponibilité d'une base de données complète contenant des données sur les défaillances dans le temps. Chaque type de défaillance dans cette base de données doit être correctement identifié et sa véritable cause déterminée. Cette méthode d'évaluation de la fiabilité convient aux entreprises qui produisent le même équipement en lots suffisamment importants, de sorte qu'un nombre important de défaillances pourraient être traitées pour évaluer la fiabilité.

Des méthodes de test de fiabilité des composants électroniques sont utilisées depuis le milieu des années 1970, elles sont généralement divisées en tests accélérés et non accélérés. L'approche principale consiste à tester l'équipement, ce qui crée l'environnement d'exploitation attendu aussi réaliste que possible. Les tests sont effectués jusqu'à ce qu'une défaillance se produise, ce qui permet de prédire le MTBF (temps moyen entre les défaillances - MTBF). Si le MTBF est évalué comme très long, la durée du test peut être réduite par des tests accélérés, ce qui est obtenu en renforçant les facteurs environnementaux et en utilisant la formule bien connue pour relier le taux de défaillance d'un test accéléré au taux de défaillance attendu. De tels tests sont vitaux pour les composants à haut risque de défaillance, car ils fournissent au chercheur des données qui ont le plus haut niveau de confiance, cependant, il serait peu pratique de les utiliser pour optimiser la conception des cartes en raison du long temps d'une itération de l'étude.

Un examen rapide des travaux publiés dans les années 1990 suggère qu'il s'agissait d'une période où les méthodes utilisant des données expérimentales, des données de test et des méthodes PoF se faisaient concurrence pour remplacer les méthodes obsolètes pour prédire la fiabilité à partir de la littérature de référence et réglementaire. De plus, chaque méthode a ses avantages et ses inconvénients et, lorsqu'elle est utilisée correctement, donne des résultats précieux. En conséquence, l'IEEE a récemment publié une norme [26], qui répertorie toutes les méthodes utilisées pour prédire la fiabilité aujourd'hui. Le but de l'IEEE était de préparer un manuel qui fournirait à l'ingénieur des informations sur toutes les méthodes disponibles, ainsi que les avantages et les inconvénients inhérents à chaque méthode. Bien que l'approche IEEE soit encore au début d'un long chemin évolutif, elle semble avoir ses propres mérites, car l'AIAA (American Institute of Aeronautics and Astronautics) suit avec un guide appelé S-102, qui est similaire à IEEE, mais aussi prend en compte la qualité relative des données de chaque méthode [27]. Ces lignes directrices visent uniquement à rassembler les méthodes qui circulent à travers le monde dans la littérature publiée sur ces questions.

4. Défaillances dues aux vibrations

La plupart des études passées se sont principalement concentrées sur les vibrations aléatoires comme la charge du PCB, mais la prochaine étude traite spécifiquement des défaillances de choc. De telles méthodes ne seront pas complètement discutées ici, car elles relèvent de la classification des méthodes PoF et sont discutées dans les sections 8.1 et 8.2 de cet article. Hin et al. [24] ont créé une carte de test pour vérifier l'intégrité des joints BGA soudés sous impact. Lau et al. [36] ont décrit la fiabilité des composants PLCC, PQFP et QFP qui sont impactés le long du plan et hors du plan. Pitarresi et al. [53,55] ont examiné les défaillances des cartes mères d'ordinateurs à cause des charges de choc et ont donné une bonne revue de la littérature décrivant l'équipement électronique sous exposition aux «chocs». Steinberg [62] donne un chapitre entier consacré à la conception et à l'analyse des équipements électroniques impactés, considérant à la fois les méthodes de prédiction du milieu de choc et les méthodes permettant d'assurer l'opérabilité des composants électroniques. Sukhir [64.65] a décrit des erreurs dans les calculs linéaires de la réponse de la carte de circuit imprimé à la charge de choc appliquée aux supports de carte. Ainsi, les méthodes de référence et les méthodes de données expérimentales peuvent prendre en compte les défaillances des équipements liées à l'impact, mais les défaillances «de choc» sont implicitement décrites dans ces méthodes.

5. Méthodes de référence

De toutes les méthodes disponibles décrites dans les manuels, nous nous limitons à seulement deux qui prennent en compte la défaillance vibratoire: Mil-Hdbk-217 et CNET [9]. Le Mil-Hdbk-217 est accepté comme référence par la plupart des fabricants. Comme toutes les méthodes des manuels et manuels, elles sont basées sur des approches empiriques visant à prédire la fiabilité d'un composant à partir de données expérimentales ou de laboratoire. Les méthodes décrites dans la littérature de référence sont relativement simples à mettre en œuvre, car elles ne nécessitent pas de modélisation mathématique complexe, n'utilisent que les types de pièces, le nombre de pièces, les conditions de fonctionnement de la carte et d'autres paramètres facilement accessibles. L'entrée est ensuite entrée dans le modèle pour calculer MTBF - MTBF. Malgré ses avantages, le Mil-Hdbk-217 devient de moins en moins populaire [12, 17,42,50,51]. Considérez une liste incomplète de restrictions sur son applicabilité.

- Les données deviennent de plus en plus obsolètes depuis leur dernière mise à jour en 1995 et ne sont pas liées à de nouveaux composants, il n'y a aucune chance de réviser le modèle, puisque le conseil pour l'amélioration des normes de défense a décidé de permettre à la méthode de `` mourir par mort naturelle '' [26].

- Le procédé ne fournit pas d'informations sur le mode de défaillance, par conséquent, la disposition de la carte de circuit imprimé ne peut pas être améliorée ou optimisée.

- Les modèles supposent que la défaillance est indépendante de la conception, en ignorant l'emplacement des composants sur la carte de circuit imprimé, cependant, il est connu que la disposition des composants a un impact important sur la probabilité de défaillance. [50].

- Les données empiriques recueillies contiennent de nombreuses inexactitudes; des données provenant de composants de première génération avec un taux de défaillance anormalement élevé en raison d'enregistrements erronés de temps de fonctionnement, de réparation, etc. sont utilisées, ce qui réduit la fiabilité des résultats de prédiction de fiabilité [51].

Toutes ces lacunes indiquent que l'utilisation de méthodes de référence doit être évitée, cependant, dans les limites de l'admissibilité de ces méthodes, un certain nombre d'exigences des spécifications techniques doivent être mises en œuvre. Ainsi, les méthodes de référence ne devraient être utilisées que lorsque cela est approprié, c'est-à-dire aux premiers stades de la conception [46]. , , 1995 . , - .

6.

. , . (MTTF, ), [26]. .

, . , , . . , [70,71]. , , . , , . .

, , , , , , . Hart [23], Hin et al. [24], [37], . [36], . [57], Liguore Followell [40], . [15], Wang . [67], Jih Jung [30]. IEEE [26].

7.

, . , . : . , ; , . , , , , , . , , .

(HALT) , , [27]. [27], , MTBF , , . [11,17,20,26].

8. (PoF)

, , PoF, . , , . , . , .

, . [15,36,37,67], , [40], , [62] [59], , .

, [21,38], , , , . , ( , ) , .

SMT, , . , , .

PoF, PoF, FE ( ), . , , , , PoF . PoF [17,19,26,49].

8.1.

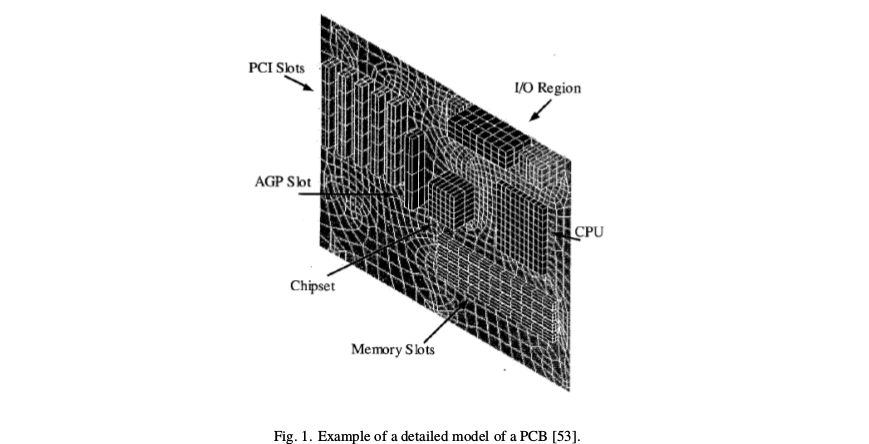

. , , . : , FE FE, . , , ( 8.1.4). FIG. 1. [53].

8.1.1.

[62] . , ; . , , . , .

, . [53] 2% , 3,5% ( 54 ), .

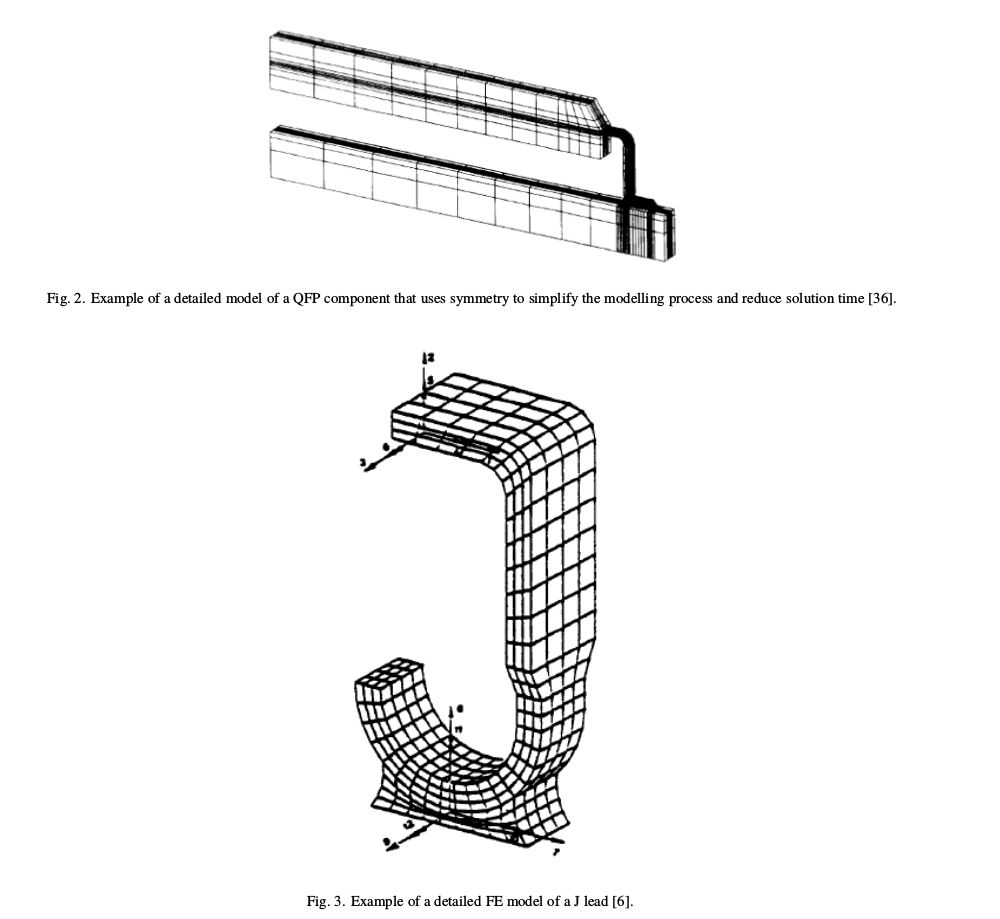

8.1.2. FE

FE [30,37,53, 57,58] ( . 1-3 ), ( ), , , . . , FE , JEDEC 4, [33-35], FE . , ( ), , . , FE , , , , .

8.1.3. FE

FE . , .

FIG. 2. QFP, [36]. FIG. 3. FE- J- [6].

[52]. Pitarresi . [52,54] , , .

FE- , . , , .

, . . . M ( ) . , , M , . , Cifuentes [10] .

- 90% .

- , , , .

- .

- , .

8.1.4.

[59], , . ( ) , , . [5] , , . , . , . , . Lim et al. [41] , FE PCB; , Barker Chen [5]. , - , . , , [21]; Aglietti [2]; Aglietti Schwingshackl [3], Lim . [41].

8.1.5.

Pitarresi . [53-55] FE- PCB , , 3D — . . (SRS) , .

8.2.

, (MTBF), , (. IEEE [26]; Jensen [28]; O'Connor [47] ). . . , - ( , ), , , . .

8.2.1.

Comme indiqué précédemment, la limitation de la plupart des modèles empiriques est qu'ils ne s'appliquent qu'à des configurations qui incluent la même épaisseur de la carte de circuit imprimé, des types de composants similaires et une charge d'entrée, ce qui est peu probable. Cependant, la littérature disponible est utile pour les raisons suivantes: elle fournit de bons exemples de tests de défaillance, met en évidence diverses options pour les mesures de défaillance et fournit des informations précieuses sur la mécanique de la défaillance. Lee [37] a créé un modèle empirique pour prédire la fiabilité d'un boîtier BGA à 272 broches et d'un boîtier QFP à 160 broches. La rupture en fatigue des conducteurs et du corps de boîtier est étudiée, les résultats expérimentaux sont en bon accord avec l'analyse des dommages basée sur les contraintes calculées à l'aide du modèle FE détaillé (voir aussi Li et Poglitsch [38, 39]). Le processus donne des dommages cumulatifs à un niveau donné d'accélération vibrationnelle du signal de vibration d'entrée.

Lau et al. [36] ont estimé la fiabilité de composants spécifiques soumis à des charges de choc et de vibration en utilisant les statistiques de Weibull. Liguore et Followell [40] ont examiné les défaillances des composants LLCC et J-lead en modifiant l'accélération locale des cycles de fonctionnement. L'accélération locale est utilisée contrairement à l'accélération d'entrée du châssis, en outre, l'effet de la température sur les résultats des tests a été étudié. L'article fait également référence à l'étude de l'effet de l'épaisseur des cartes de circuits imprimés sur la fiabilité des composants.

Guo et Zhao [21] comparent la fiabilité des composants lorsqu'ils utilisent la courbure de torsion locale comme charge, contrairement aux études précédentes qui utilisaient l'accélération. Les dommages par fatigue sont simulés, puis le modèle FE est comparé aux résultats expérimentaux. L'article discute également de l'optimisation de la disposition des composants pour augmenter la fiabilité.

Ham et Lee [22] ont présenté une méthode de données d'essai pour la détermination des contraintes de soudure au plomb sous une charge de torsion cyclique. Estes et al. [15] ont examiné le problème de la défaillance des composants de «l'aile de mouette» (GOST IEC 61188-5-5-2013) avec accélération d'entrée appliquée et charge thermique. Les composants étudiés sont les types de logements des microcircuits CQFP 352, 208, 196, 84 et 28, ainsi que les FP 42 et 10. L'article est consacré à la défaillance des composants électroniques due aux oscillations de l'orbite du satellite géostationnaire de la Terre, le MTBF est donné en termes d'années de vol géostationnaire ou orbites terrestres basses. Il est à noter que la défaillance des fils de «l'aile de mouette» est plus probable dans les endroits en contact avec le corps de l'emballage que dans une connexion soudée.

Jih et Jung [30] examinent les pannes d'équipement causées par des défauts de fabrication congénitaux dans un joint soudé. Cela se fait en créant un modèle FE très détaillé de la carte de circuit imprimé et en trouvant la densité spectrale de puissance (PSD) pour différentes longueurs de fissures de production. Ligyore, Followell [40] et Shetty, Reinikainen [58] ont suggéré que les méthodes empiriques fournissent les données de défaillance les plus précises et utiles pour des configurations spécifiques de composants connectés. De telles méthodes sont utilisées si certaines données d'entrée (épaisseur de carte, type de composant, plage de courbure) peuvent être supposées constantes pendant toute la durée de conception, ou si l'utilisateur peut se permettre d'effectuer de vrais tests de ce type.

8.2.2. Critère d'échec analytique

Modèles de joints d'angle SMTDivers chercheurs examinant les défaillances des terminaux d'angle SMT suggèrent qu'il s'agit de la cause la plus courante de défaillance. Les articles de Sidhart et Barker [59] complètent une série de travaux antérieurs, présentant un modèle pour déterminer la déformation des fils angulaires des composants de fils SMT et de contour. Le modèle proposé présente une erreur de moins de 7% par rapport au modèle FE détaillé pour les six scénarios les plus défavorables. Le modèle est basé sur une formule précédemment publiée par Barker et Sidhart [4], où la déflexion de la pièce attachée soumise au moment de flexion a été simulée. L'article de Suhira [63] analyse analytiquement les contraintes attendues dans les sorties de paquets dues aux moments de flexion appliqués localement. Barker et Sidhart [4] s'appuient sur les travaux de Suhir [63], Barker et al. [4], qui étudie l'influence de la rigidité de rotation dominante. Enfin, Barker et al. [7] ont utilisé des modèles EF détaillés pour étudier l'effet des variations dimensionnelles du plomb sur la durée de vie en fatigue du plomb.

Il convient de mentionner ici les travaux sur les constantes de ressort en plomb JEDEC, grâce auxquels la création de modèles de composants en plomb a été grandement simplifiée [33–35]. Les constantes de ressort peuvent être utilisées à la place d'un modèle détaillé de composés de plomb, tandis que le modèle réduira le temps de construction et de résolution du modèle FE. L'utilisation de telles constantes dans le modèle FE composant empêchera le calcul direct des contraintes locales de plomb. Au lieu de cela, une déformation générale du plomb sera donnée, qui devra ensuite être associée soit aux contraintes locales du plomb, soit à des critères de défaillance du plomb basés sur le cycle de vie du produit.

Données sur la fatigue des matériauxLa plupart des données sur la destruction des matériaux utilisés pour les soudures et les composants sont principalement liées aux fractures thermiques, et il existe relativement peu de données sur les fractures de fatigue. La référence principale dans ce domaine est fournie par Sandor [56], qui fournit des données sur la mécanique de la fatigue et de la rupture des soudures. Steinberg [62] considère la destruction des échantillons de soudure. Les données sur la fatigue des soudures et des fils standard sont disponibles dans un article de Yamada [69].

FIG. 4. L'état de défaillance habituel du manuel pour les composants QFP est proche du corps de l'emballage.

La modélisation des défaillances associées à la déconnexion de la soudure est un défi en raison des propriétés inhabituelles de ce matériau. La solution à cette question dépend du composant à tester. Il est connu que pour les packages QFP, cela n'est généralement pas pris en compte et la fiabilité est estimée à partir de la documentation de référence et de la réglementation. Mais si le soudage du BGA, le PGA des gros composants est calculé, les composés de plomb en raison de leurs propriétés inhabituelles peuvent affecter la défaillance du produit. Ainsi, pour les boîtiers QFP, les propriétés de fatigue du plomb sont les informations les plus utiles. Pour le BGA, les informations sur la durabilité des joints soudés soumis à une déformation plastique instantanée sont plus utiles [14]. Pour les composants plus gros, Steinberg [62] fournit des données sur la contrainte de traction des joints soudés.

Modèles de défaillance de composants lourdsLes seuls modèles de fracture qui existent pour les composants lourds sont présentés dans un article de Steinberg [62], qui examine la résistance à la traction des composants et donne un exemple de la façon de calculer la contrainte maximale admissible qui peut être appliquée à un composé de plomb

8.3. Conclusions sur l'applicabilité des modèles PoF

Les conclusions suivantes concernant les méthodes PoF ont été tirées dans la littérature.

La réponse locale est essentielle pour prévoir la défaillance d'un composant. Comme indiqué dans Li, Poglitsch [38], les composants sur les bords d'une carte de circuit imprimé sont moins sujets à l'échec que ceux situés au centre d'un PCB en raison de différences locales de flexion. Par conséquent, les composants à différents endroits de la carte de circuit imprimé auront des probabilités de défaillance différentes.

La courbure locale de la carte est considérée comme un critère de défaillance plus important que l'accélération pour les composants SMT. Des articles récents [38,57,62,67] indiquent que la courbure du panneau est le principal critère d'échec.

Différents types de packages, à la fois en nombre de sorties et en type utilisé, sont intrinsèquement plus fiables que les autres, quel que soit l'environnement local spécifique [15.36.38].

La température peut affecter la fiabilité des composants. Liguore et Followell [40] ont déclaré que la durée de vie en fatigue est la plus élevée dans la plage de températures de 0 ° C à 65 ° C, avec une diminution notable à des températures inférieures à -30 ° C et supérieures à 95 ° C. Pour les composants QFP, l'endroit où le fil se connecte au sac (voir Fig. 4) est considéré comme le principal lieu d'endommagement, et non comme un joint de soudure [15,22,38].

L'épaisseur du panneau a un certain effet sur la durée de vie en fatigue des composants SMT, car il a été démontré que la durée de vie en fatigue du BGA diminue d'environ 30 à 50 fois si l'épaisseur du panneau augmente de 0,85 mm à 1,6 mm (tout en maintenant une courbure totale constante) [13]. La flexibilité (flexibilité) des conducteurs des composants affecte de manière significative la fiabilité des composants des conducteurs périphériques [63], cependant, il s'agit d'une dépendance non linéaire, et les conclusions de la connexion intermédiaire des éléments sont les moins fiables.

8.4. Méthodes logicielles

Le Life Cycle Technology Center of Excellence (CALCE) de l'Université du Maryland fournit un logiciel pour calculer la réponse aux vibrations et aux chocs des cartes de circuits imprimés. Le logiciel (appelé CALCE PWA) possède une interface utilisateur qui simplifie le processus de démarrage du modèle FE et entre automatiquement le calcul de la réponse dans le modèle de vibration. Il n'y a pas d'hypothèses utilisées pour créer le modèle de réponse FE, et les critères de rejet utilisés sont tirés de Steinberg [61] (bien que la méthode Barkers [48] soit également censée être mise en œuvre). Pour fournir des recommandations générales sur l'amélioration de la fiabilité des équipements, le logiciel décrit donne de bons résultats, d'autant plus qu'il prend simultanément en compte les tensions induites thermiquement et nécessite un minimum de connaissances particulières, cependant, la précision des critères de défaillance dans les modèles n'a pas été confirmée expérimentalement.

9. Méthodes pour améliorer la fiabilité des équipements

Cette section discutera des modifications postérieures au projet qui augmentent la fiabilité de l'équipement électronique. Ils se répartissent en deux catégories: ceux qui modifient les conditions aux limites de la carte de circuit imprimé et ceux qui augmentent l'amortissement.

Le but principal des modifications des conditions aux limites est de réduire la déviation dynamique de la carte de circuit imprimé, ceci peut être réalisé en rigidifiant les nervures, des supports supplémentaires ou en réduisant les vibrations du support d'entrée. Les raidisseurs peuvent être utiles car ils augmentent les fréquences propres, réduisant ainsi la déflexion dynamique [62], il en va de même pour l'ajout de supports supplémentaires [3], bien que l'emplacement des supports puisse également être optimisé, comme le montrent JH Ong et Lim [40]. Malheureusement, les nervures et les supports nécessitent généralement une refonte du schéma de disposition, de sorte que ces méthodes sont mieux prises en compte au début du cycle de conception. En outre, il convient de veiller à ce que les modifications ne modifient pas les fréquences naturelles de sorte qu'elles coïncident avec les fréquences naturelles de la structure de support, car cela serait contre-productif.

L'ajout d'isolant peut améliorer la fiabilité du produit, réduire l'influence du milieu dynamique transmis à l'équipement, et peut être réalisé de manière passive ou active.

Les méthodes passives sont généralement simples et moins coûteuses à mettre en œuvre, par exemple en utilisant des isolateurs de câble [66] ou en utilisant les propriétés pseudo-élastiques des alliages à mémoire de forme (SMA) [32]. Cependant, il est connu que des isolateurs mal conçus peuvent en fait augmenter la réponse.

Les méthodes actives fournissent un meilleur amortissement sur une plage de fréquences plus large, généralement en raison de la simplicité et de la masse, c'est pourquoi elles sont généralement conçues pour augmenter la précision des instruments de précision très sensibles, et non pour éviter les dommages. L'isolation active des vibrations comprend les méthodes électromagnétiques [60] et piézoélectriques [18,43]. Contrairement aux méthodes de modification des conditions aux limites, la modification de l'amortissement vise à diminuer la réponse de résonance maximale des équipements électroniques, tandis que les fréquences naturelles réelles devraient varier légèrement.

Comme dans le cas de l'isolation vibratoire, l'amortissement peut être réalisé de manière passive et active, avec une simplification similaire de la structure dans le premier cas et une complexité et un amortissement plus élevés dans le second.

Les méthodes passives comprennent, par exemple, des méthodes très simples, comme le collage de matériaux, qui augmentent l'amortissement de la carte de circuit imprimé [62]. Des méthodes plus sophistiquées comprennent l'amortissement des particules [68] et l'utilisation d'absorbeurs dynamiques à large bande [25].

Le contrôle actif des vibrations est généralement obtenu grâce à l'utilisation d'éléments piézocéramiques liés à la surface de la carte de circuit imprimé [1.45]. L'utilisation de méthodes de durcissement est spécifique au cas et doit être soigneusement envisagée par rapport aux autres méthodes. L'application de ces méthodes à un équipement connu pour n'avoir aucun problème de fiabilité n'augmentera pas nécessairement le coût et le poids de la structure. Cependant, si un produit dont la conception est approuvée présente une défaillance lors des tests, il peut être beaucoup plus rapide et plus facile d'appliquer la technique de durcissement que de repenser l'équipement.

10. Opportunités pour le développement de méthodes

Cette section détaille les possibilités d'améliorer la prédiction de la fiabilité des équipements électroniques, bien que les progrès récents en optoélectronique, nanotechnologie et technologie d'emballage pourraient bientôt limiter l'applicabilité de ces propositions. Quatre méthodes de base pour prédire la fiabilité ne peuvent pas être utilisées au moment de la conception de l'appareil. Le seul facteur qui pourrait rendre ces méthodes plus attrayantes serait la création de technologies de fabrication et de test à faible coût entièrement automatisées, car cela permettrait de construire et de tester la conception proposée beaucoup plus rapidement qu'aujourd'hui, avec un minimum d'effort humain.

La méthode PoF offre de nombreuses possibilités d'amélioration. Le principal domaine dans lequel il peut être amélioré est l'intégration avec le processus de conception global. La conception d'équipements électroniques est un processus itératif qui rapproche le développeur du résultat final uniquement en collaboration avec des ingénieurs spécialisés en électronique, en fabrication et en génie thermique et en conception structurelle. Une méthode qui résout automatiquement certains de ces problèmes en même temps réduira le nombre d'itérations de conception et économisera beaucoup de temps, en particulier si l'on considère le volume de la coopération interinstitutions. D'autres domaines d'amélioration des techniques PoF seront divisés en types de prédiction de réponse et de critères d'échec.

La prédiction de réponse a deux voies de développement possibles: soit des modèles plus rapides et plus détaillés, soit des modèles simplifiés améliorés. Avec l'avènement de processeurs informatiques de plus en plus puissants, le temps nécessaire pour résoudre des modèles FE détaillés peut devenir assez petit, tandis que dans le même temps, les logiciels modernes réduisent le temps d'assemblage, ce qui minimise finalement le coût des ressources humaines. Les méthodes FE simplifiées peuvent également être améliorées grâce au processus de création automatique de modèles FE, similaires à ceux proposés pour les méthodes FE détaillées. Pour cela, un logiciel automatique (CALCE PWA) est actuellement disponible, mais la technologie n'est pas suffisamment testée en pratique, et les hypothèses avancées lors de la modélisation sont inconnues.

Le calcul de l'erreur inhérente à diverses méthodes de simplification serait très utile, ce qui nous permettrait de mettre en œuvre des critères utiles de tolérance aux pannes.

Enfin, une base de données ou une méthode serait utile pour conférer une rigidité accrue aux composants attachés, où ces améliorations de rigidité pourraient être utilisées pour améliorer la précision des modèles de réponse. La création de critères de défaillance des composants dépend d'une légère variation de composants similaires de différents fabricants, ainsi que du développement possible de nouveaux types d'emballage, car toute méthode ou base de données pour déterminer les critères de défaillance doit tenir compte de cette variabilité et de ces changements.

Une solution consisterait à créer une méthode / un logiciel pour construire automatiquement des modèles FE détaillés basés sur des paramètres d'entrée tels que les tailles de plomb et d'emballage. Une telle méthode peut être réalisable pour des composants de forme généralement uniforme, tels que des composants SMT ou DIP, mais pas pour des composants irréguliers complexes, tels que des transformateurs, des selfs ou des composants non standard.

Les modèles FE suivants peuvent être résolus pour les contraintes et combinés avec des données de rupture de matériau (données de courbe de ductilité S-N, mécanique de la rupture ou similaire) pour calculer la durée de vie des composants, bien que les données de rupture de matériau doivent être de haute qualité. Le processus FE doit être corrélé avec des données de test réelles, de préférence dans la gamme de configurations la plus large possible.

L'effort consacré à un tel processus est relativement faible par rapport à l'alternative aux tests directs en laboratoire, qui devraient effectuer un nombre statistiquement significatif de tests pour différentes épaisseurs de cartes de circuits imprimés, différentes intensités et directions de charge, des centaines de types de composants différents sont disponibles même pour plusieurs types de cartes. , , .

- , , , . FE , .

, , : FE, , , , . PoF , . , , , , ( ).

, , , , , (), .

11.

, ( - , , PoF), . - , , , , , , .

PF , , . « » , FE. , FE, . « » , SMT .

, , , . . , , , .

Littérature[1] GS Aglietti, RS Langley, E. Rogers and SB Gabriel, An efficient model of an equipment loaded panel for active control design studies, The Journal of the Acoustical Society of America 108 (2000), 1663–1673.

[2]GS Aglietti, A lighter enclosure for electronics for space applications, Proceeding of Institute of Mechanical Engineers 216 (2002), 131–142.

[3] GS Aglietti and C. Schwingshackl, Analysis of enclosures and anti vibration devices for electronic equipment for space applications, Proceedings of the 6th International Conference on Dynamics and Control of Spacecraft Structures in Space, Riomaggiore, Italy, (2004).

[4] DB Barker and Y. Chen, Modeling the vibration restraints of wedge lock card guides, ASME Journal of Electronic Packaging 115(2) (1993), 189–194.

[5] DB Barker, Y. Chen and A. Dasgupta, Estimating the vibration fatigue life of quad leaded surface mount components, ASME Journal of Electronic Packaging 115(2) (1993), 195–200.

[6] DB Barker, A. Dasgupta and M. Pecht, PWB solder joint life calculations under thermal and vibrational loading, Annual Reliability and Maintainability Symposium, 1991 Proceedings (Cat. No.91CH2966-0), 451–459.

[7] DB Barker, I. Sharif, A. Dasgupta and M. Pecht, Effect of SMC lead dimensional variabilities on lead compliance and solder joint fatigue life, ASME Journal of Electronic Packaging 114(2) (1992), 177–184.

[8] DB Barker and K. Sidharth, Local PWB and component bowing of an assembly subjected to a bending moment, American Society of Mechanical Engineers (Paper) (1993), 1–7.

[9] J. Bowles, A survey of reliability-prediction procedures for microelectronic devices, IEEE Transactions on Reliability 41(1) (1992), 2–12.

[10] AO Cifuentes, Estimating the dynamic behavior of printed circuit boards, IEEE Transactions on Components, Packaging, and Manufacturing Technology Part B: Advanced Packaging 17(1) (1994), 69–75.

[11] L. Condra, C. Bosco, R. Deppe, L. Gullo, J. Treacy and C. Wilkinson, Reliability assessment of aerospace electronic equipment, Quality and Reliability Engineering International 15(4) (1999), 253–260.

[12] MJ Cushing, DE Mortin, TJ Stadterman and A. Malhotra, Comparison of electronics-reliability assessment approaches, IEEE Transactions on Reliability 42(4) (1993), 542–546.

[13] R. Darveaux and A. Syed, Reliability of area array solder joints in bending, SMTA International Proceedings of the Technical Program (2000), 313–324.

[14] NF Enke, TJ Kilinski, SA Schroeder and JR Lesniak, Mechanical behaviors of 60/40 tin-lead solder lap joints, Proceedings – Electronic Components Conference 12 (1989), 264–272.

[15] T. Estes, W. Wong, W. McMullen, T. Berger and Y. Saito, Reliability of class 2 heel fillets on gull wing leaded components. Aerospace Conference, Proceedings 6 (2003), 6-2517–6 C2525

[16] FIDES, FIDES Guide 2004 issue A Reliability Methodology for Electronic Systems. FIDES Group, 2004.

[17] B. Foucher, D. Das, J. Boullie and B. Meslet, A review of reliability prediction methods for electronic devices, Microelectronics Reliability 42(8) (2002), 1155–1162.

[18] J. Garcia-Bonito, M. Brennan, S. Elliott, A. David and R. Pinnington, A novel high-displacement piezoelectric actuator for active vibration control, Smart Materials and Structures 7(1) (1998), 31–42.

[19] W. Gericke, G. Gregoris, I. Jenkins, J. Jones, D. Lavielle, P. Lecuyer, J. Lenic, C. Neugnot, M. Sarno, E. Torres and E. Vergnault, A methodology to assess and select a suitable reliability prediction method for eee components in space applications, European Space Agency, (Special Publication) ESA SP (507) (2002), 73–80.

[20] L. Gullo, In-service reliability assessment and top-down approach provides alternative reliability prediction method. Annual Reliability and Maintainability, Symposium Proceedings (Cat. No.99CH36283), 1999, 365–377.

[21] Q. Guo and M. Zhao, Fatigue of SMT solder joint including torsional curvature and chip location optimization, International Journal of Advanced Manufacturing Technology 26(7–8) (2005), 887–895.

[22] S.-J. Ham and S.-B. Lee, Experimental study for reliability of electronic packaging under vibration, Experimental Mechanics 36(4) (1996), 339–344.

[23] D. Hart, Fatigue testing of a component lead in a plated through hole, IEEE Proceedings of the National Aerospace and Electronics Conference (1988), 1154–1158.

[24] TY Hin, KS Beh and K. Seetharamu, Development of a dynamic test board for FCBGA solder joint reliability assessment in shock & vibration. Proceedings of the 5th Electronics Packaging Technology Conference (EPTC 2003), 2003, 256–262.58

[25] V. Ho, A. Veprik and V. Babitsky, Ruggedizing printed circuit boards using a wideband dynamic absorber, Shock and Vibration 10(3) (2003), 195–210.

[26] IEEE, IEEE guide for selecting and using reliability predictions based on ieee 1413, 2003, v+90 C.

[27] T. Jackson, S. Harbater, J. Sketoe and T. Kinney, Development of standard formats for space systems reliability models, Annual Reliability and Maintainability Symposium, 2003 Proceedings (Cat. No.03CH37415), 269–276.

[28] F. Jensen, Electronic Component Reliability, Wiley, 1995.

[29] JH Ong and G. Lim, A simple technique for maximising the fundamental frequency of structures, ASME Journal of Electronic Packaging 122 (2000), 341–349.

[30] E. Jih and W. Jung, Vibrational fatigue of surface mount solder joints. IThermfl98. Sixth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (Cat. No.98CH36208), 1998, 246–250.

[31] B. Johnson and L. Gullo, Improvements in reliability assessment and prediction methodology. Annual Reliability and Maintainability Symposium. 2000 Proceedings. International Symposium on Product Quality and Integrity (Cat. No. 00CH37055), 2000, -:181–187.

[32] M. Khan, D. Lagoudas, J. Mayes and B. Henderson, Pseudoelastic SMA spring elements for passive vibration isolation: part i modeling, Journal of Intelligent Material Systems and Structures 15(6) (2004), 415–441.

[33] R. Kotlowitz, Comparative compliance of representative lead designs for surface-mounted components, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 12(4) (1989), 431–448.

[34] R. Kotlowitz, Compliance metrics for surface mount component lead design. 1990 Proceedings. 40th Electronic Components and Technology Conference (Cat. No. 90CH2893-6), 1990, 1054–1063.

[35] R. Kotlowitz and L. Taylor, Compliance metrics for the inclined gull-wing, spider j-bend, and spider gull-wing lead designs for surface mount components. 1991 Proceedings. 41st Electronic Components and Technology Conference (Cat. No. 91CH2989-2), 1991, 299–312.

[36] J. Lau, L. Powers-Maloney, J. Baker, D. Rice and B. Shaw, Solder joint reliability of fine pitch surface mount technology assemblies, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 13(3) (1990), 534–544.

[37] R. Li, A methodology for fatigue prediction of electronic components under random vibration load, ASME Journal of Electronic Packaging 123(4) (2001), 394–400.

[38] R. Li and L. Poglitsch, Fatigue of plastic ball grid array and plastic quad flat packages under automotive vibration. SMTA International, Proceedings of the Technical Program (2001), 324–329.

[39] R. Li and L. Poglitsch, Vibration fatigue, failure mechanism and reliability of plastic ball grid array and plastic quad flat packages.

[40] Proceedings 2001 HD International Conference on High-Density Interconnect and Systems Packaging (SPIE Vol. 4428), 2001, 223–228.

[41] S. Liguore and D. Followell, Vibration fatigue of surface mount technology (smt) solder joints. Annual Reliability and Maintainability Symposium 1995 Proceedings (Cat. No. 95CH35743), 1995, -:18–26.

[42] G. Lim, J. Ong and J. Penny, Effect of edge and internal point support of a printed circuit board under vibration, ASME Journal of Electronic Packaging 121(2) (1999), 122–126.

[43] P. Luthra, Mil-hdbk-217: What is wrong with it? IEEE Transactions on Reliability 39(5) (1990), 518.

[44] J. Marouze and L. Cheng, A feasibility study of active vibration isolation using thunder actuators, Smart Materials and Structures 11(6) (2002), 854–862.

[45] MIL-HDBK-217F. Reliability Prediction of Electronic Equipment. US Department of Defense, F edition, 1995.

[46] SR Moheimani, A survey of recent innovations in vibration damping and control using shunted piezoelectric transducers, IEEE Transactions on Control Systems Technology 11(4) (2003), 482–494.

[47] S. Morris and J. Reilly, Mil-hdbk-217-a favorite target. Annual Reliability and Maintainability Symposium. 1993 Proceedings (Cat. No.93CH3257-3), (1993), 503–509.

P. O'Connor, Practical reliability engineering. Wiley, 1997.

[48] M. Osterman and T. Stadterman, Failure assessment software for circuit card assemblies. Annual Reliability and Maintainability. Symposium. 1999 Proceedings (Cat. No.99CH36283), 1999, 269–276.

[49] M. Pecht and A. Dasgupta, Physics-of-failure: an approach to reliable product development, IEEE 1995 International Integrated Reliability Workshop Final Report (Cat. No. 95TH8086), (1999), 1–4.

[50] M. Pecht and W.-C. Kang, A critique of mil-hdbk-217e reliability prediction methods, IEEE Transactions on Reliability 37(5) (1988), 453–457.

[51] MG Pecht and FR Nash, Predicting the reliability of electronic equipment, Proceedings of the IEEE 82(7) (1994), 992–1004.

[52] J. Pitarresi, D. Caletka, R. Caldwell and D. Smith, The smeared property technique for the FE vibration analysis of printed circuit cards, ASME Journal of Electronic Packaging 113 (1991), 250–257.

[53] J. Pitarresi, P. Geng, W. Beltman and Y. Ling, Dynamic modeling and measurement of personal computer motherboards. 52nd Electronic Components and Technology Conference 2002., (Cat. No. 02CH37345)(-), 2002, 597–603.

[54] J. Pitarresi and A. Primavera, Comparison of vibration modeling techniques for printed circuit cards, ASME Journal of Electronic Packaging 114 (1991), 378–383.

[55] J. Pitarresi, B. Roggeman, S. Chaparala and P. Geng, Mechanical shock testing and modeling of PC motherboards. 2004 Proceedings, 54th Electronic Components and Technology Conference (IEEE Cat. No. 04CH37546) 1 (2004), 1047–1054.

[56] BI Sandor, Solder Mechanics – A State of the Art Asssessment. The Minerals, Metals and Materials Society, 1991.

[57] S. Shetty, V. Lehtinen, A. Dasgupta, V., Halkola and T. Reinikainen, Fatigue of chip scale package interconnects due to cyclic bending, ASME Journal of Electronic Packaging 123(3) (2001), 302–308.

[58] S. Shetty and T. Reinikainen, Three- and four-point bend testing for electronic packages, ASME Journal of Electronic Packaging 125(4) (2003), 556–561.

[59] K. Sidharth and DB Barker, Vibration induced fatigue life estimation of corner leads of peripheral leaded components, ASME Journal of Electronic Packaging 118(4) (1996), 244–249.

[60] J. Spanos, Z. Rahman and G. Blackwood, Soft 6- axis active vibration isolator, Proceedings of the American Control Conference 1 (1995), 412–416.

[61] D. Steinberg, Vibration Analysis for Electronic Equipment, John Wiley & Sons, 1991.

[62] D. Steinberg, Vibration Analysis for Electronic Equipment, John Wiley & Sons, 2000.

[63] E. Suhir, Could compliant external leads reduce the strength of a surface-mounted device? 1988 Proceedings of the 38th Electronics Components Conference (88CH2600-5), 1988, 1–6.

[64] E. Suhir, Nonlinear dynamic response of a printed circuit board to shock loads applied to its support contour, ASME Journal of Electronic Packaging 114(4) (1992), 368–377.

[65] E. Suhir, Response of a flexible printed circuit board to periodic shock loads applied to its support contour, American Society of Mechanical Engineers (Paper) 59(2) (1992), 1–7.

[66] A. Veprik, Vibration protection of critical components of electronic equipment in harsh environmental conditions, Journal of Sound and Vibration 259(1) (2003), 161–175.

[67] H. Wang, M. Zhao and Q. Guo, Vibration fatigue experiments of SMT solder joint, Microelectronics Reliability 44(7) (2004), 1143–1156.

[68] ZW Xu, K. Chan and W. Liao, An empirical method for particle damping design, Shock and Vibration 11(5–6) (2004), 647–664.

[69] S. Yamada, A fracture mechanics approach to soldered joint cracking, IEEE Transactions on Components, Hybrids, and Manufacturing Technology 12(1) (1989), 99–104.

[70] W. Zhao and E. Elsayed, Modelling accelerated life testing based on mean residual life, International Journal of Systems Science 36(11) (1995), 689–696.

[71] W. Zhao, A. Mettas, X. Zhao, P. Vassiliou and EA Elsayed, Generalized step stress accelerated life model. Proceedings of 2004 International Conference on the Business of Electronic Product Reliability and Liability, 2004, 19–25.