Les listes de contrôle d'accès (Access Control List) sur les périphériques réseau peuvent être implémentées sous forme matérielle ou logicielle, ou plus généralement sous forme matérielle et logicielle. Et si tout doit être clair avec les ACL basées sur le logiciel, ce sont les règles qui sont stockées et traitées dans la RAM (c'est-à-dire sur le plan de contrôle), avec toutes les restrictions qui en découlent, alors nous comprendrons comment les ACL basées sur le matériel sont implémentées et fonctionnent. notre article. Par exemple, nous utiliserons les commutateurs de la gamme Extreme Networks ExtremeSwitching.

Étant donné que nous sommes intéressés par les listes de contrôle d'accès basées sur le matériel, l'implémentation interne de Data Plane, ou des chipsets réellement utilisés (ASIC), est d'une importance capitale pour nous. Les commutateurs de toutes les gammes de produits Extreme Networks sont construits sur les ASIC de Broadcom. Par conséquent, la plupart des informations ci-dessous s'appliqueront également aux autres commutateurs du marché et seront implémentées sur les mêmes ASIC.

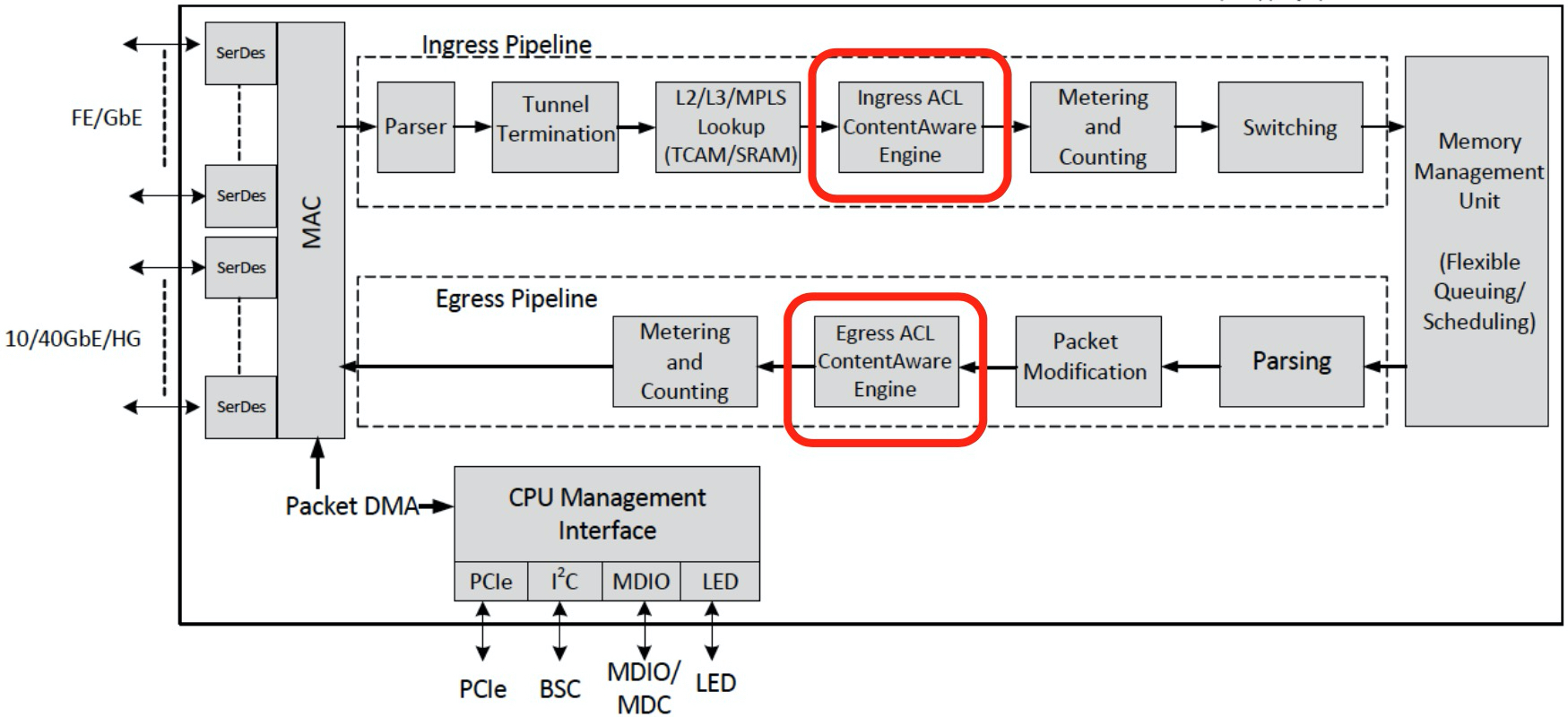

Comme on peut le voir sur la figure ci-dessus, le «ContentAware Engine», séparément pour «entrée» et «sortie», est responsable de l'opération ACL dans le chipset. Sur le plan architectural, ce sont les mêmes, seule la «sortie» est moins évolutive et moins fonctionnelle. Physiquement, les deux «ContentAware Engine» sont de la mémoire TCAM plus la logique associée, et chaque règle ACL d'utilisateur ou de système est un simple masque binaire écrit dans cette mémoire. C'est pourquoi le traitement par chipset du trafic est effectué sur une base unitaire et sans dégradation des performances.

Physiquement, le même TCAM Ingress / Egress, à son tour, est logiquement divisé en plusieurs segments (en fonction de la quantité de mémoire et de la plate-forme), les «tranches ACL». Par exemple, la même chose se produit avec physiquement le même disque dur sur votre ordinateur portable lorsque vous créez plusieurs lecteurs logiques dessus - C: \>, D: \>. Chaque tranche ACL, à son tour, se compose de cellules de mémoire, sous la forme de «chaînes» où des «règles» sont écrites (règles / masques de bits).

La répartition de TCAM en ACL-tranches a une certaine logique sous-jacente. Dans chacune des tranches ACL individuelles, seules des «règles» compatibles peuvent être écrites. Si l'une des «règles» n'est pas compatible avec la précédente, elle sera écrite dans la suivante dans l'ordre ACL-tranche, quel que soit le nombre de lignes libres sous les «règles» restant dans la précédente.

D'où vient cette compatibilité ou incompatibilité des règles ACL? Le fait est qu'une «ligne» de TCAM, où les «règles» sont écrites, a une longueur de 232 bits et est divisée en plusieurs champs - Fixe, Champ1, Champ2, Champ3. Une mémoire TCAM de 232 bits ou 29 octets suffit pour écrire un masque de bits d'une adresse MAC ou IP spécifique, mais beaucoup moins que l'en-tête de paquet Ethernet complet. Dans chaque tranche ACL individuelle, l'ASIC produit une recherche indépendante selon le masque de bits défini dans F1-F3. En général, cette recherche peut être effectuée sur le premier en-tête Ethernet de 128 octets. En fait, précisément parce que la recherche peut être effectuée sur 128 octets, et que seulement 29 octets peuvent être enregistrés, pour une recherche correcte, un décalage doit être défini par rapport au début du paquet. Le décalage pour chacune des tranches ACL est défini lorsque la première règle lui est écrite, et si la nécessité d'un autre décalage est trouvée lors de l'écriture de la règle suivante, cette règle est considérée comme incompatible avec la première et est écrite dans la tranche ACL suivante.

Le tableau ci-dessous montre l'ordre de compatibilité des conditions spécifiées dans l'ACL. Chaque ligne séparée contient des masques de bits qui sont compatibles entre eux et non compatibles avec d'autres lignes.

Chaque paquet individuel traité par ASIC exécute une recherche parallèle dans chaque tranche ACL. La validation est effectuée avant la première correspondance dans la tranche ACL, mais plusieurs correspondances sont autorisées pour le même paquet dans différentes tranches ACL. Chaque «règle» individuelle a une action correspondante qui doit être exécutée si la condition (masque de bits) correspond. Si une correspondance s'est produite dans plusieurs tranches ACL à la fois, puis dans le bloc «Action Conflict Resolution», en fonction de la priorité de la tranche ACL, une décision est prise sur celle à effectuer. Si à la fois l '«action» (autorisation / refus) et le «action-modifier» (count / QoS / log / ...) sont écrits dans l'ACL, alors en cas de correspondances multiples, seule «l'action» de priorité plus élevée sera exécutée, le «action-modifier» sera tout est fait. L'exemple ci-dessous montre que les deux compteurs seront augmentés et que le «refus» prioritaire sera exécuté.

avec des informations plus détaillées sur la façon dont les ACL sont accessibles au public sur

extremenetworks.com . Toutes les questions qui surviennent ou restent peuvent toujours être posées à notre personnel de bureau -

cis@extremenetworks.com .