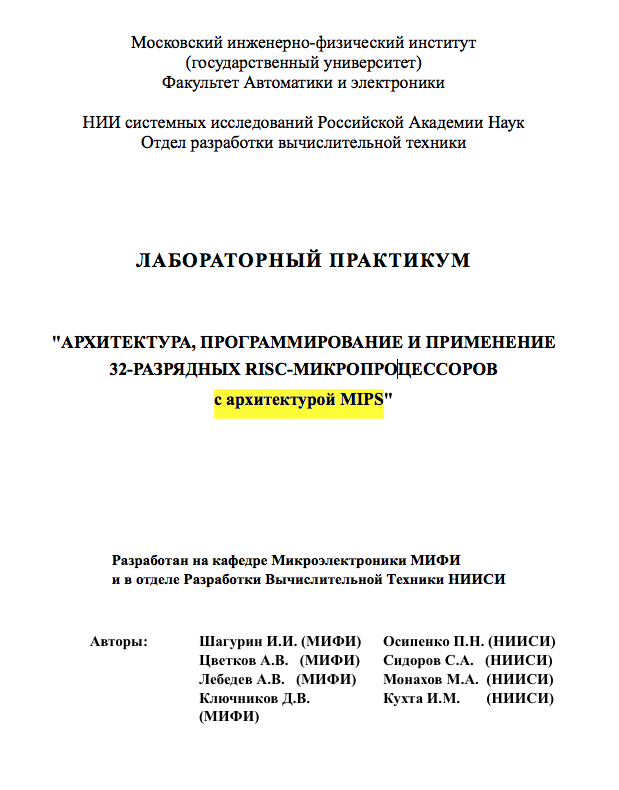

MIPSfpga — , Imagination Technologies, Microchip Technology -, Xilinx , MathWorks . — , , .

. «» , , , — , . (!)

( )

( ) — :

, .

- — Intel, Motorola PowerPC,

MIPS.

UPD: :

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

, - 1970- , . VLSI 1970- Muir Woods,

Sequoia sempervirens

—

/ SRISA, , MIPS — -32 -64.

-

RADECS :

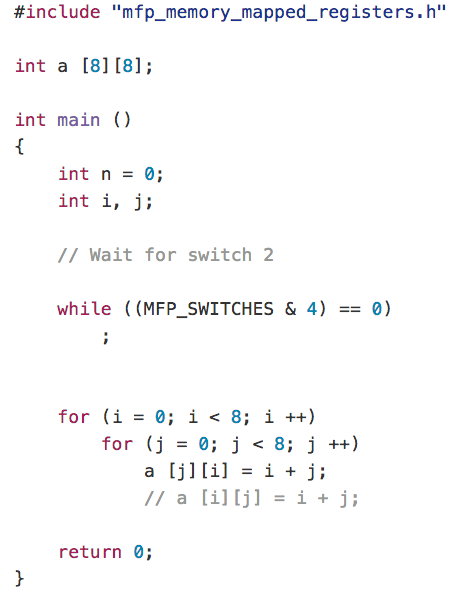

MIPSfpga , , race conditions , . , , ,

“ », , ( ), (D-) , , , :

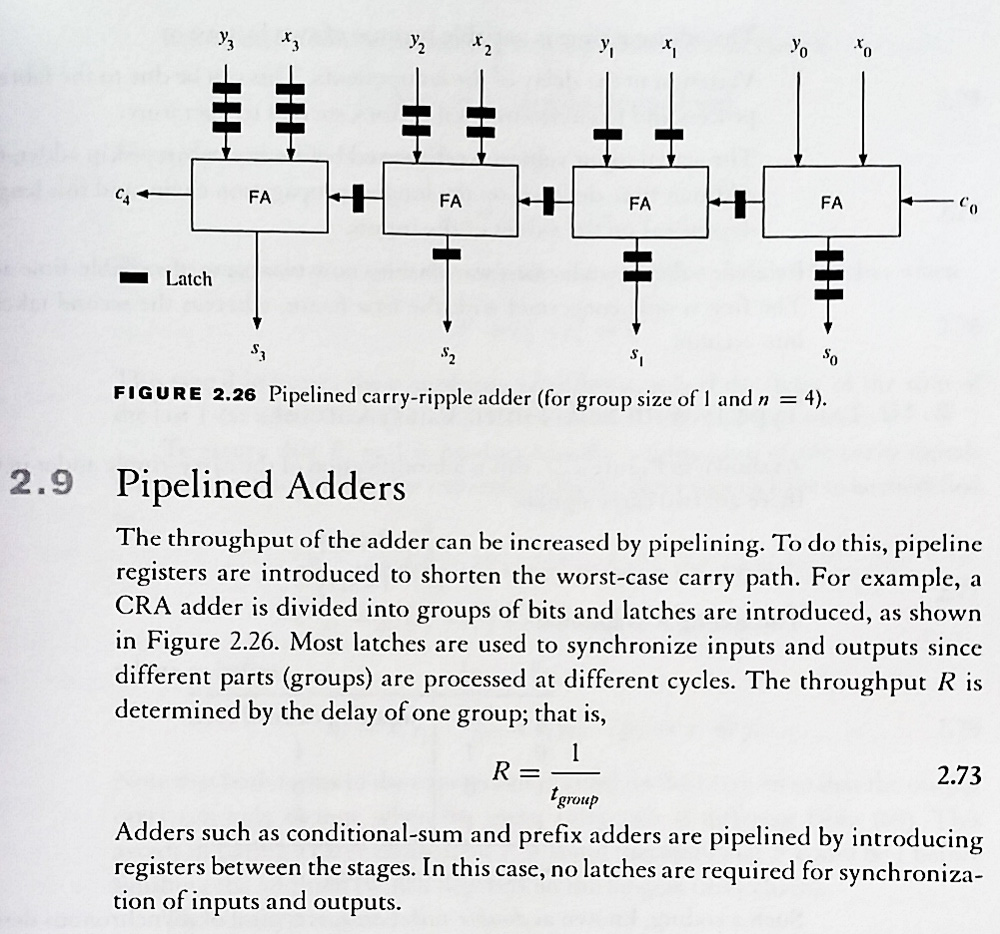

Digital Arithmetic 1st Edition by Milos D. Ercegovac and Tomás Lang self-times ,

self-times , .

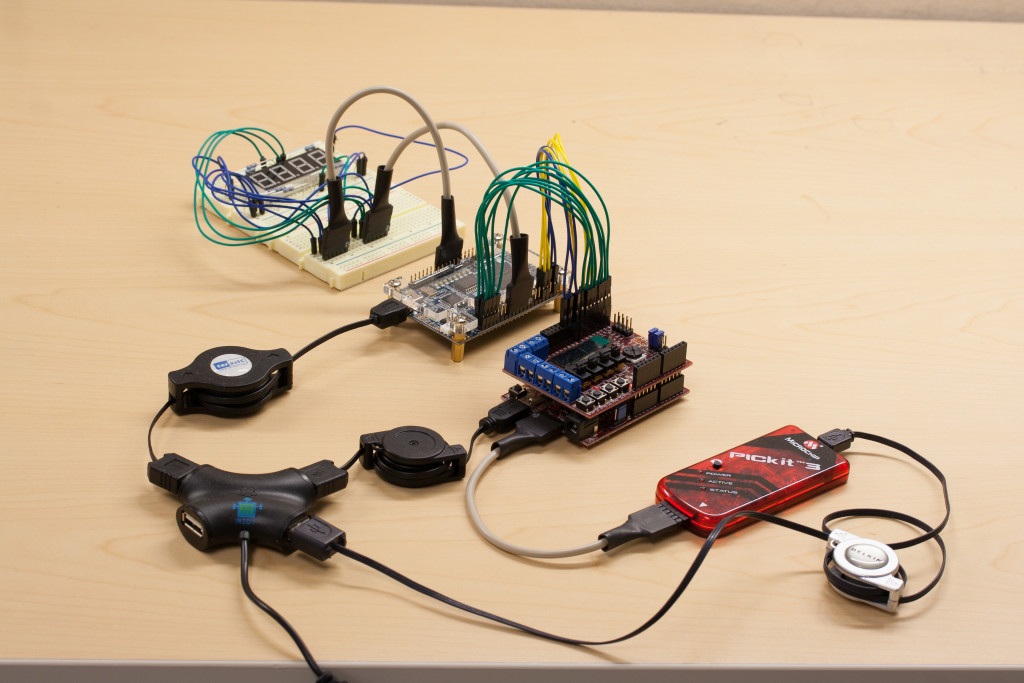

, , Microchip PIC32MX. ,

Imagination, Microchip Digilent

Microchip PIC32MZ, RTOS- . PIC32MZ MIPS microAptiv UP, , MIPSfpga. , ( ) - :

. MIPSfpga. :

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

, :

1.

Imagination Technologies MIPS business unit2.

Imagination Technologies3. RTL-to-GDSII flow , Verilog/VHDL :

IP- c ().4. MIPS —

, (MIPS microAptiv UP) MIPSfpga5. ,

MIPS microAptiv UP

, MathWorks:

MIPS Simulink

MIPS Simulink, MATLAB Central Pick of the Week:

, — Verilog VHDL, , Simulink.

, , , MIPSfpga, :

- , , -

- , . « ».

- , , .

SoC , / . , — Xilinx . Xilinx — , FPGA #1 FPGA.

:

- FPGA 7- MPSoC UltraScale – XILINX « »

- XILINX VIVADO « »

/ FPGA —

, — . :

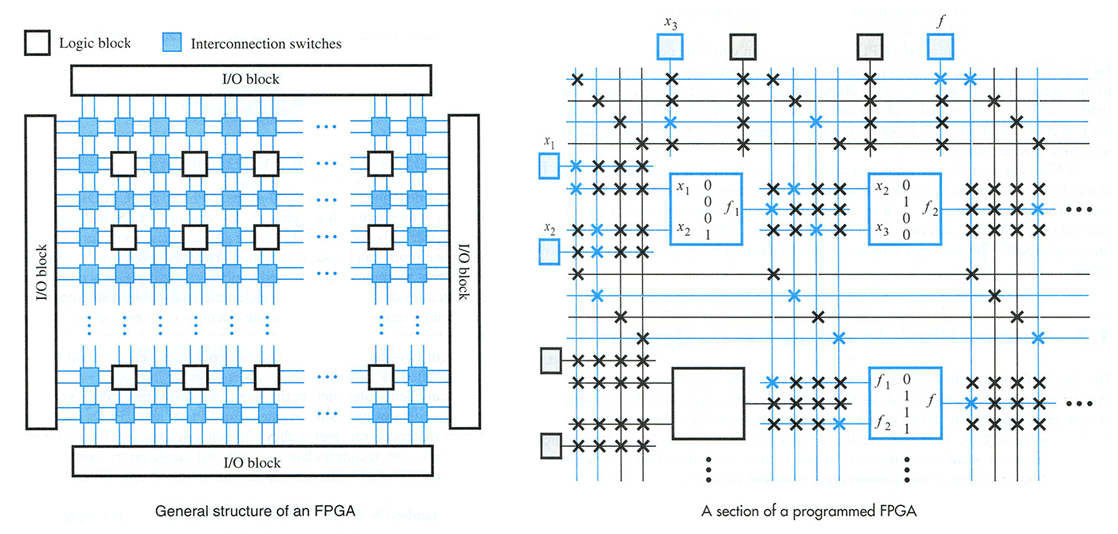

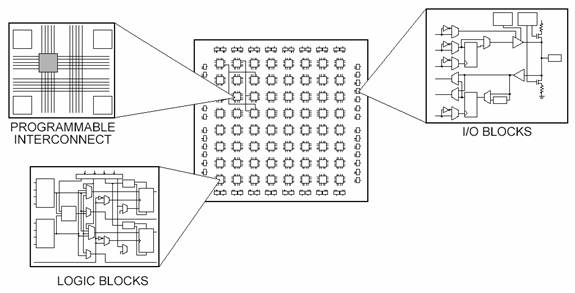

FPGA , , . AND , — .. — FPGA , , ..

- / FPGA — , «» ( -) (), ( ) ().

— FPGA, look-up table (LUT) flip-flop. , , .

, FPGA:

:

. , Imagination Technologies Xilinx -,

, . , :

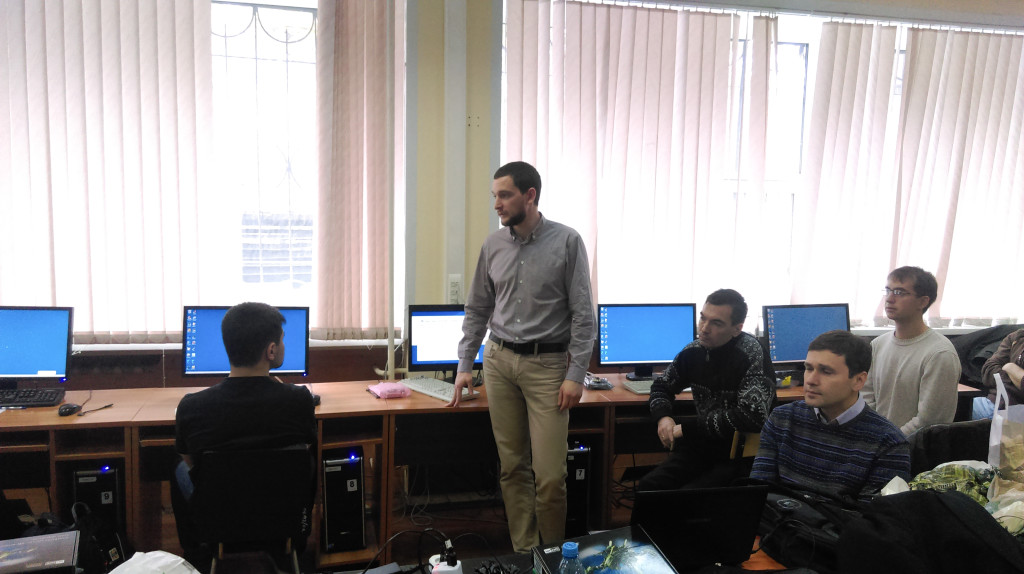

8 -.

https://github.com/MIPSfpga/mipsfpga-plus. :

1. Altera, -

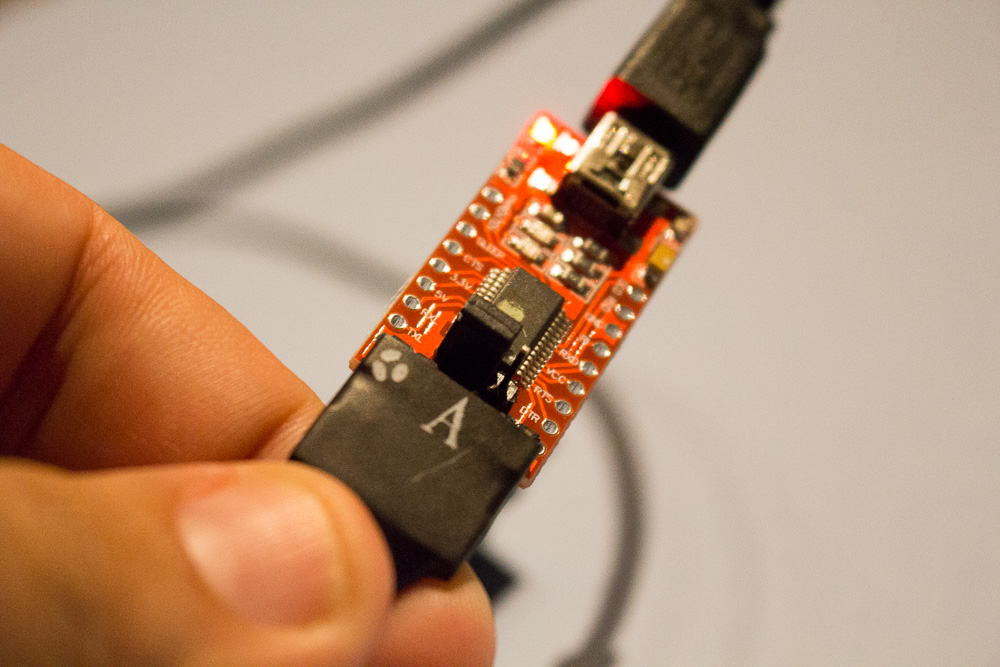

2. BusBlaster, UART

3. LCD

4. ,

5.

+ — / bootloader, ..

:

1. Altera

, Xilinx, Xilinx , 3-4 . place-and-route Xilinx Vivado, . Xilinx, Vivado; Vivado — 2013 ISE, - , .

, MIPSfpga , , Xilinx — Altera ( Intel-).

«». , Terasic DE0-CV Altera Cyclone V:

Terasic DE0-Nano — , , :

Terasic DE0-Nano — , , DE0-Nano :

2. UART

Bus Blaster OpenOCD. BusBlaster/OpenOCD — . - , EJTAG, JTAG. BusBlaster $43, , EJTAG-.

, BusBlaster/OpenOCD , , ( — ). ,

, BusBlaster/OpenOCD MIPS, .

, ( / ( )). - , EJTAG Altera USB Blaster, EJTAG, , — / UART. RS-232C, 1990- FTDI, USB , PC. $5 $2 :

, SoC . , , (bootloader), (reset) UART / serial port. , , geektimes

«MIPSfpga: ».

, , . PC UART

Motorola S-Record, ( ) , . . , PC — ELF- Motorola S-Record COM- windows-shell- «type».

3. LCD

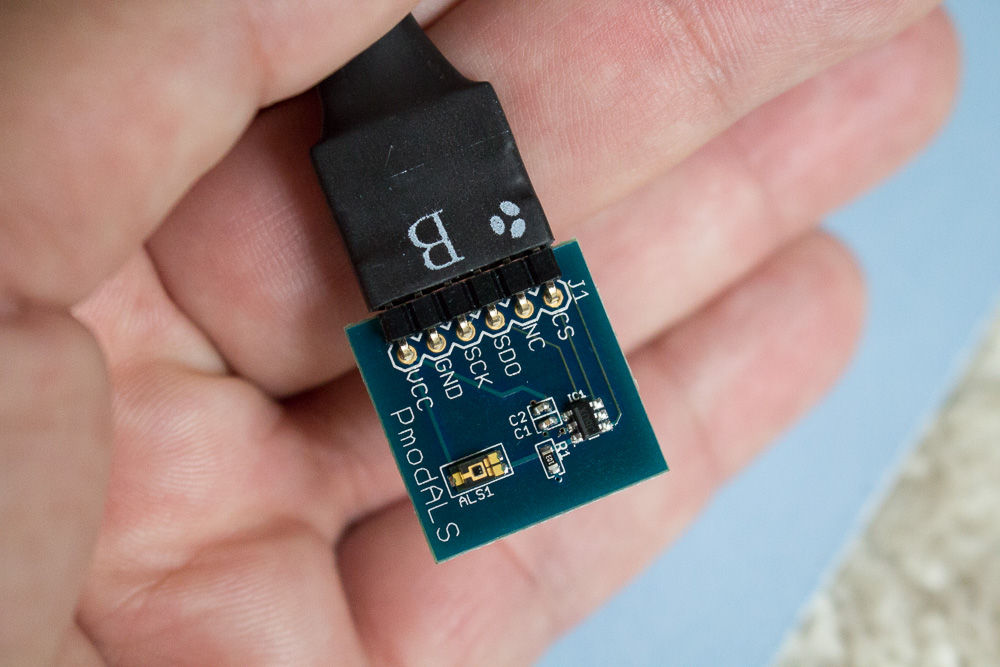

LCD- SPI. — , , . SPI , , , ? , 20 , SPI, :

— (: AHB-Lite, ):

4.

MIPSfpga , , , , , « », . , , , , ( , D-), , , .

, «», , . ? MIPS microAptiv UP ASIC 28 500 MHz, 65 300 MHz. - , — 50-60 MHz. — 50-100 MHz,

phase-locked loop (PLL) /

().

, PLL ~100 KHz, 1 Hz . Altera

ALTCLKCTRL, - . , ( ) , , , .

«global» ( Xilinx BUFG).

5.

— , , . , , :

, :

1. GPIO DE0-Nano GPIO DE0-CV Xilinx. , - GPIO inout- input, output. DE0-CV . GPIO ( Verilog) , DE0-Nano. DE0-CV Bus Blaster-.

2. , UART DE0-Nano , . 100% :

2.1. , Windows (7 ) USB-to-UART DE0-Nano. PL2303TA, . , PL2303HX Windows 8 (

.). , Windows 7, Windows 8, . , — .

2.2. . .

2.3. DE0-CV .

3. , . — - , pattern , .

, , , MIPSfpga

myMIPSfpga «MIPSfpga: ». , MIPSfpga

3, , - (: + : ), :

, - 1960-:

UPD: , ( , , appropriate geektimes):

, , - . , .. , , , 1) , -; 2) — , 1988 ( , , ); 3) .

.