प्रोसेसर के विकास का इतिहास: 80 के दशक का अंत - 2000 के दशक की शुरुआत

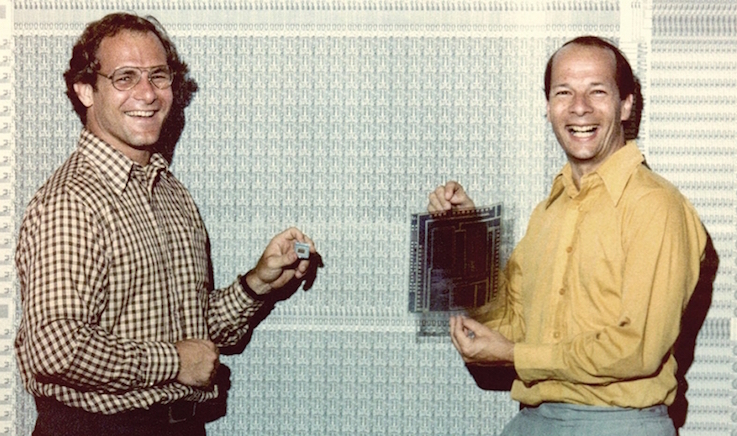

पहले लेख की थीम जारी रखना 20 वीं शताब्दी के अंत से 21 वीं सदी की शुरुआत तक प्रोसेसर के विकास का इतिहास है।80 के दशक के कई प्रोसेसरों ने CISC आर्किटेक्चर (कॉम्प्लेक्स इंस्ट्रक्शन सेट कंप्यूटिंग) का इस्तेमाल किया। चिप्स काफी जटिल और महंगे थे, साथ ही पर्याप्त रूप से उत्पादक नहीं थे। उत्पादन को आधुनिक बनाने और ट्रांजिस्टर की संख्या बढ़ाने की आवश्यकता थी।RISC आर्किटेक्चर1980 में, बर्कले RISC प्रोजेक्ट लॉन्च किया गया था, जिसका नेतृत्व अमेरिकी इंजीनियरों डेविड पैटरसन और कार्लो सेक्विन ने किया था। आरआईएससी (प्रतिबंधित निर्देश सेट कंप्यूटर) - सरलीकृत निर्देशों के कारण बढ़ी हुई गति के साथ प्रोसेसर वास्तुकला। बर्कले RISC प्रोजेक्ट मैनेजर - डेविड पैटरसन और कार्लो सेक्विनकई वर्षों के फलदायी कार्यों के बाद, प्रोसेसर के कई नमूने निर्देश के कम सेट के साथ बाजार में दिखाई दिए। आरआईएससी मंच का प्रत्येक निर्देश सरल था और एक ही चक्र में निष्पादित किया गया था। कई और सामान्य प्रयोजन रजिस्टर भी थे। इसके अलावा, सरलीकृत निर्देशों के साथ पाइपलाइनिंग का उपयोग किया गया था, जिसने घड़ी की आवृत्ति को प्रभावी ढंग से बढ़ाना संभव बना दिया।RISC I को 1982 में जारी किया गया था और इसमें 44,420 से अधिक ट्रांजिस्टर शामिल थे। उनके पास केवल 32 निर्देश थे और 4 मेगाहर्ट्ज की आवृत्ति पर काम किया। अगले RISC II में 40,760 ट्रांजिस्टर शामिल थे, 39 निर्देशों का उपयोग किया और तेजी से किया गया था।

बर्कले RISC प्रोजेक्ट मैनेजर - डेविड पैटरसन और कार्लो सेक्विनकई वर्षों के फलदायी कार्यों के बाद, प्रोसेसर के कई नमूने निर्देश के कम सेट के साथ बाजार में दिखाई दिए। आरआईएससी मंच का प्रत्येक निर्देश सरल था और एक ही चक्र में निष्पादित किया गया था। कई और सामान्य प्रयोजन रजिस्टर भी थे। इसके अलावा, सरलीकृत निर्देशों के साथ पाइपलाइनिंग का उपयोग किया गया था, जिसने घड़ी की आवृत्ति को प्रभावी ढंग से बढ़ाना संभव बना दिया।RISC I को 1982 में जारी किया गया था और इसमें 44,420 से अधिक ट्रांजिस्टर शामिल थे। उनके पास केवल 32 निर्देश थे और 4 मेगाहर्ट्ज की आवृत्ति पर काम किया। अगले RISC II में 40,760 ट्रांजिस्टर शामिल थे, 39 निर्देशों का उपयोग किया और तेजी से किया गया था। RISC IIप्रोसेसर MIPS प्रोसेसर: R2000, R3000, R4000 और R4400MIPS प्रोसेसर की वास्तुकला (इंटरलॉक की गई पाइपलाइन के बिना माइक्रोप्रोसेसर) क्रिस्टल में सहायक इकाइयों की उपस्थिति के लिए प्रदान की जाती है। MIPS ने एक विस्तारित कन्वेयर का उपयोग किया।1984 में, अमेरिकी वैज्ञानिक जॉन हेनेसी के नेतृत्व में शोधकर्ताओं के एक समूह ने माइक्रोइलेक्ट्रॉनिक उपकरणों को डिजाइन करने वाली एक कंपनी की स्थापना की। MIPS में स्मार्ट होम डिवाइस, नेटवर्क और मोबाइल एप्लिकेशन के लिए माइक्रोप्रोसेसर आर्किटेक्चर और IP कोर लाइसेंस हैं। 1985 में, कंपनी का पहला उत्पाद जारी किया गया था - 32-बिट R2000, जिसे 1988 में R3000 में अंतिम रूप दिया गया था। अपडेट किए गए मॉडल में मल्टीप्रोसेसिंग, इंस्ट्रक्शन कैश और डेटा कैश के लिए समर्थन था। प्रोसेसर को विभिन्न कंपनियों के एसजी-सीरीज़ वर्कस्टेशन में एप्लिकेशन मिला है। R3000 भी Sony PlayStation गेम कंसोल का आधार बन गया।

RISC IIप्रोसेसर MIPS प्रोसेसर: R2000, R3000, R4000 और R4400MIPS प्रोसेसर की वास्तुकला (इंटरलॉक की गई पाइपलाइन के बिना माइक्रोप्रोसेसर) क्रिस्टल में सहायक इकाइयों की उपस्थिति के लिए प्रदान की जाती है। MIPS ने एक विस्तारित कन्वेयर का उपयोग किया।1984 में, अमेरिकी वैज्ञानिक जॉन हेनेसी के नेतृत्व में शोधकर्ताओं के एक समूह ने माइक्रोइलेक्ट्रॉनिक उपकरणों को डिजाइन करने वाली एक कंपनी की स्थापना की। MIPS में स्मार्ट होम डिवाइस, नेटवर्क और मोबाइल एप्लिकेशन के लिए माइक्रोप्रोसेसर आर्किटेक्चर और IP कोर लाइसेंस हैं। 1985 में, कंपनी का पहला उत्पाद जारी किया गया था - 32-बिट R2000, जिसे 1988 में R3000 में अंतिम रूप दिया गया था। अपडेट किए गए मॉडल में मल्टीप्रोसेसिंग, इंस्ट्रक्शन कैश और डेटा कैश के लिए समर्थन था। प्रोसेसर को विभिन्न कंपनियों के एसजी-सीरीज़ वर्कस्टेशन में एप्लिकेशन मिला है। R3000 भी Sony PlayStation गेम कंसोल का आधार बन गया। R3000 प्रोसेसर1991 में, नई पीढ़ी R4000 लाइन जारी की गई। इस प्रोसेसर में 64-बिट आर्किटेक्चर, एक एकीकृत कोप्रोसेसर और 100 मेगाहर्ट्ज की घड़ी आवृत्ति पर काम किया गया था। आंतरिक कैश 16 KB (कैश निर्देशों के 8 KB और कैश डेटा का 8 KB) था।एक साल बाद, प्रोसेसर का एक संशोधित संस्करण - R4400 - जारी किया गया। इस मॉडल में, कैश बढ़कर 32 KB (16 KB कैश कमांड और 16 KB कैश डेटा) हो गया है। प्रोसेसर 100 मेगाहर्ट्ज - 250 मेगाहर्ट्ज की आवृत्ति पर काम कर सकता है।MIPS प्रोसेसर: R8000 और R100001994 में, MIPS आर्किटेक्चर, R8000 के सुपरस्क्लेर कार्यान्वयन के साथ पहला प्रोसेसर दिखाई दिया। डेटा कैश की क्षमता 16 KB थी। इस CPU में उच्च गति के संचालन के साथ संयोजन में एक उच्च डेटा एक्सेस बैंडविड्थ (1.2 Gb / s तक) था। आवृत्ति 75 मेगाहर्ट्ज - 90 मेगाहर्ट्ज तक पहुंच गई। छह सर्किट का उपयोग किया गया था: पूर्णांक निर्देशों के लिए एक उपकरण, फ़्लोटिंग पॉइंट निर्देशों के लिए, तीन माध्यमिक रैम कैश डिस्क्रिप्टर और एक एएसआईसी कैश कंट्रोलर।

R3000 प्रोसेसर1991 में, नई पीढ़ी R4000 लाइन जारी की गई। इस प्रोसेसर में 64-बिट आर्किटेक्चर, एक एकीकृत कोप्रोसेसर और 100 मेगाहर्ट्ज की घड़ी आवृत्ति पर काम किया गया था। आंतरिक कैश 16 KB (कैश निर्देशों के 8 KB और कैश डेटा का 8 KB) था।एक साल बाद, प्रोसेसर का एक संशोधित संस्करण - R4400 - जारी किया गया। इस मॉडल में, कैश बढ़कर 32 KB (16 KB कैश कमांड और 16 KB कैश डेटा) हो गया है। प्रोसेसर 100 मेगाहर्ट्ज - 250 मेगाहर्ट्ज की आवृत्ति पर काम कर सकता है।MIPS प्रोसेसर: R8000 और R100001994 में, MIPS आर्किटेक्चर, R8000 के सुपरस्क्लेर कार्यान्वयन के साथ पहला प्रोसेसर दिखाई दिया। डेटा कैश की क्षमता 16 KB थी। इस CPU में उच्च गति के संचालन के साथ संयोजन में एक उच्च डेटा एक्सेस बैंडविड्थ (1.2 Gb / s तक) था। आवृत्ति 75 मेगाहर्ट्ज - 90 मेगाहर्ट्ज तक पहुंच गई। छह सर्किट का उपयोग किया गया था: पूर्णांक निर्देशों के लिए एक उपकरण, फ़्लोटिंग पॉइंट निर्देशों के लिए, तीन माध्यमिक रैम कैश डिस्क्रिप्टर और एक एएसआईसी कैश कंट्रोलर। R8000 प्रोसेसर1996 में, एक संशोधित संस्करण जारी किया गया था - R10000। प्रोसेसर में डेटा और निर्देशों के प्राथमिक कैश के 32 KB शामिल थे। सीपीयू ने 150 मेगाहर्ट्ज - 250 मेगाहर्ट्ज की आवृत्ति पर काम किया।90 के दशक के अंत में, MIPS ने 32-बिट और 64-बिट MIPS32 और MIPS64 आर्किटेक्चर के लिए लाइसेंस बेचना शुरू किया।स्पार्क प्रोसेसर्ससन माइक्रोसिस्टम्स, जिसने स्केलेबल आर्किटेक्चर SPARC (स्केलेबल प्रोसेसर ARChitecture) विकसित किया है, प्रोसेसर के रैंक में शामिल हो गया। उसी नाम का पहला प्रोसेसर 80 के दशक के उत्तरार्ध में जारी किया गया था और इसे SPARC V7 कहा जाता था। इसकी आवृत्ति 14.28 मेगाहर्ट्ज - 40 मेगाहर्ट्ज तक पहुंच गई।1992 में, SPARC V8 नामक अगला 32-बिट संस्करण दिखाई दिया, जिसके आधार पर microSPARC प्रोसेसर बनाया गया था। घड़ी की आवृत्ति 40 मेगाहर्ट्ज - 50 मेगाहर्ट्ज थी।टेक्सास इंस्ट्रूमेंट्स, फुजित्सु, फिलिप्स और अन्य ने सन माइक्रोसिस्टम्स के साथ अगली पीढ़ी के SPARC V9 आर्किटेक्चर पर सहयोग किया। प्लेटफ़ॉर्म का विस्तार 64 बिट्स तक था और 9-स्टेज पाइपलाइन के साथ सुपरस्क्लेयर था। SPARC V9 को निर्देश और डेटा (प्रत्येक 16 KB की क्षमता के साथ), साथ ही 512 KB - 1024 KB की क्षमता के साथ विभाजित प्रथम स्तर कैश मेमोरी के उपयोग के लिए प्रदान किया गया है।

R8000 प्रोसेसर1996 में, एक संशोधित संस्करण जारी किया गया था - R10000। प्रोसेसर में डेटा और निर्देशों के प्राथमिक कैश के 32 KB शामिल थे। सीपीयू ने 150 मेगाहर्ट्ज - 250 मेगाहर्ट्ज की आवृत्ति पर काम किया।90 के दशक के अंत में, MIPS ने 32-बिट और 64-बिट MIPS32 और MIPS64 आर्किटेक्चर के लिए लाइसेंस बेचना शुरू किया।स्पार्क प्रोसेसर्ससन माइक्रोसिस्टम्स, जिसने स्केलेबल आर्किटेक्चर SPARC (स्केलेबल प्रोसेसर ARChitecture) विकसित किया है, प्रोसेसर के रैंक में शामिल हो गया। उसी नाम का पहला प्रोसेसर 80 के दशक के उत्तरार्ध में जारी किया गया था और इसे SPARC V7 कहा जाता था। इसकी आवृत्ति 14.28 मेगाहर्ट्ज - 40 मेगाहर्ट्ज तक पहुंच गई।1992 में, SPARC V8 नामक अगला 32-बिट संस्करण दिखाई दिया, जिसके आधार पर microSPARC प्रोसेसर बनाया गया था। घड़ी की आवृत्ति 40 मेगाहर्ट्ज - 50 मेगाहर्ट्ज थी।टेक्सास इंस्ट्रूमेंट्स, फुजित्सु, फिलिप्स और अन्य ने सन माइक्रोसिस्टम्स के साथ अगली पीढ़ी के SPARC V9 आर्किटेक्चर पर सहयोग किया। प्लेटफ़ॉर्म का विस्तार 64 बिट्स तक था और 9-स्टेज पाइपलाइन के साथ सुपरस्क्लेयर था। SPARC V9 को निर्देश और डेटा (प्रत्येक 16 KB की क्षमता के साथ), साथ ही 512 KB - 1024 KB की क्षमता के साथ विभाजित प्रथम स्तर कैश मेमोरी के उपयोग के लिए प्रदान किया गया है। UltraSPARC IIIप्रोसेसर स्ट्रॉन्गर्मा प्रोसेसर1995 में, एआरएम वी 4 इंस्ट्रक्शन सेट को लागू करने वाले स्ट्रांगर्मा माइक्रोप्रोसेसर परिवार को विकसित करने के लिए एक परियोजना शुरू की गई थी। ये सीपीयू 5-चरण की पाइपलाइन के साथ एक क्लासिक स्केलर आर्किटेक्चर थे, जिसमें मेमोरी कंट्रोल यूनिट और 16 केबी के निर्देशों और डेटा का समर्थन करते थे।

UltraSPARC IIIप्रोसेसर स्ट्रॉन्गर्मा प्रोसेसर1995 में, एआरएम वी 4 इंस्ट्रक्शन सेट को लागू करने वाले स्ट्रांगर्मा माइक्रोप्रोसेसर परिवार को विकसित करने के लिए एक परियोजना शुरू की गई थी। ये सीपीयू 5-चरण की पाइपलाइन के साथ एक क्लासिक स्केलर आर्किटेक्चर थे, जिसमें मेमोरी कंट्रोल यूनिट और 16 केबी के निर्देशों और डेटा का समर्थन करते थे। स्ट्रांगम एसए -११०और पहले से ही 1996 में, स्ट्रॉन्गर्म - SA-110 पर आधारित पहला प्रोसेसर जारी किया गया था। उन्होंने 100 मेगाहर्ट्ज, 160 मेगाहर्ट्ज या 200 मेगाहर्ट्ज की घड़ी की आवृत्तियों पर काम किया।SA-1100, SA-1110 और SA-1500 मॉडल भी बाजार में उतरे।

स्ट्रांगम एसए -११०और पहले से ही 1996 में, स्ट्रॉन्गर्म - SA-110 पर आधारित पहला प्रोसेसर जारी किया गया था। उन्होंने 100 मेगाहर्ट्ज, 160 मेगाहर्ट्ज या 200 मेगाहर्ट्ज की घड़ी की आवृत्तियों पर काम किया।SA-1100, SA-1110 और SA-1500 मॉडल भी बाजार में उतरे। Apple MessagePad 2000POWER, POWER2 और PowerPC प्रोसेसरमें SA-110 प्रोसेसर 1985 में, IBM ने अमेरिका प्रोजेक्ट के हिस्से के रूप में अगली पीढ़ी के RISC आर्किटेक्चर को विकसित करना शुरू किया। पॉवर प्रोसेसर का विकास (प्रदर्शन आरआईएससी के साथ प्रदर्शन अनुकूलन) और इसके लिए निर्देशों का सेट 5 साल तक चला। यह बहुत ही उत्पादक था, लेकिन इसमें 11 विभिन्न चिप्स शामिल थे। और इसलिए, 1992 में, एक और प्रोसेसर संस्करण जारी किया गया था जो एक चिप में फिट होता है।

Apple MessagePad 2000POWER, POWER2 और PowerPC प्रोसेसरमें SA-110 प्रोसेसर 1985 में, IBM ने अमेरिका प्रोजेक्ट के हिस्से के रूप में अगली पीढ़ी के RISC आर्किटेक्चर को विकसित करना शुरू किया। पॉवर प्रोसेसर का विकास (प्रदर्शन आरआईएससी के साथ प्रदर्शन अनुकूलन) और इसके लिए निर्देशों का सेट 5 साल तक चला। यह बहुत ही उत्पादक था, लेकिन इसमें 11 विभिन्न चिप्स शामिल थे। और इसलिए, 1992 में, एक और प्रोसेसर संस्करण जारी किया गया था जो एक चिप में फिट होता है। चिपसेट पावर1991 में, PowerPC वास्तुकला (PPC के रूप में संक्षिप्त) को IBM, Apple और Motorola Alliance द्वारा विकसित किया गया था। इसमें पॉवर प्लेटफ़ॉर्म के मूल सेट शामिल थे, और दो मोड में काम का समर्थन भी किया था और 64-बिट संस्करण के लिए 32-बिट ऑपरेशन मोड के साथ बैकवर्ड संगत था। मुख्य उद्देश्य व्यक्तिगत कंप्यूटर था।MacPCosh पर PowerPC 601 प्रोसेसर का उपयोग किया गया था।

चिपसेट पावर1991 में, PowerPC वास्तुकला (PPC के रूप में संक्षिप्त) को IBM, Apple और Motorola Alliance द्वारा विकसित किया गया था। इसमें पॉवर प्लेटफ़ॉर्म के मूल सेट शामिल थे, और दो मोड में काम का समर्थन भी किया था और 64-बिट संस्करण के लिए 32-बिट ऑपरेशन मोड के साथ बैकवर्ड संगत था। मुख्य उद्देश्य व्यक्तिगत कंप्यूटर था।MacPCosh पर PowerPC 601 प्रोसेसर का उपयोग किया गया था। PowerPC प्रोसेसर1993 में, POWER2 को निर्देशों के विस्तारित सेट के साथ पेश किया गया था। प्रोसेसर घड़ी की गति 55 मेगाहर्ट्ज से 71.5 मेगाहर्ट्ज तक थी, और डेटा और निर्देशों का कैश 128-256 Kb और 32 Kb था। प्रोसेसर माइक्रोकिरिस्क (वहां 8 थे) में 23 मिलियन ट्रांजिस्टर थे, और इसे 0.72-माइक्रोमीटर सीएमओएस तकनीक का उपयोग करके निर्मित किया गया था।1998 में, आईबीएम ने 64-बिट पॉवर 3 प्रोसेसर की तीसरी श्रृंखला जारी की जो कि पॉवरपीसी मानक के पूर्ण अनुपालन में है।2001 और 2010 के बीच, POWER4 मॉडल (आठ समानांतर चलने वाली कमांड्स), दोहरे कोर POWER5 और POWER6, और चार से आठ परमाणु POWER7 मॉडल जारी किए गए थे।अल्फा 21064 ए प्रोसेसर1992 में डिजिटल उपकरण निगम (डीईसी) ने अल्फा 21064 (ईवी 4) प्रोसेसर लॉन्च किया। यह एक 64-बिट सुपरस्क्लेयर क्रिस्टल था जिसमें एक पिपेलिंडेड आर्किटेक्चर और 100 मेगाहर्ट्ज की घड़ी आवृत्ति - 200 मेगाहर्ट्ज थी। एक बाहरी 128-बिट प्रोसेसर बस के साथ 0.75-माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित। इसमें 16 KB कैश (8 KB डेटा और 8 KB निर्देश) था।श्रृंखला में अगला मॉडल प्रोसेसर 21164 (EV5) था, जो 1995 में जारी किया गया था। उनके पास दो पूर्णांक ब्लॉक थे और पहले से ही कैश मेमोरी के तीन स्तर गिने गए (प्रोसेसर में दो, तीसरा - बाहरी)। पहले स्तर के कैश को एक डेटा कैश और प्रत्येक 8 केबी के एक निर्देश कैश में विभाजित किया गया था। दूसरे स्तर में कैश की मात्रा 96 Kb थी। प्रोसेसर घड़ी की गति 266 मेगाहर्ट्ज से 500 मेगाहर्ट्ज तक थी।

PowerPC प्रोसेसर1993 में, POWER2 को निर्देशों के विस्तारित सेट के साथ पेश किया गया था। प्रोसेसर घड़ी की गति 55 मेगाहर्ट्ज से 71.5 मेगाहर्ट्ज तक थी, और डेटा और निर्देशों का कैश 128-256 Kb और 32 Kb था। प्रोसेसर माइक्रोकिरिस्क (वहां 8 थे) में 23 मिलियन ट्रांजिस्टर थे, और इसे 0.72-माइक्रोमीटर सीएमओएस तकनीक का उपयोग करके निर्मित किया गया था।1998 में, आईबीएम ने 64-बिट पॉवर 3 प्रोसेसर की तीसरी श्रृंखला जारी की जो कि पॉवरपीसी मानक के पूर्ण अनुपालन में है।2001 और 2010 के बीच, POWER4 मॉडल (आठ समानांतर चलने वाली कमांड्स), दोहरे कोर POWER5 और POWER6, और चार से आठ परमाणु POWER7 मॉडल जारी किए गए थे।अल्फा 21064 ए प्रोसेसर1992 में डिजिटल उपकरण निगम (डीईसी) ने अल्फा 21064 (ईवी 4) प्रोसेसर लॉन्च किया। यह एक 64-बिट सुपरस्क्लेयर क्रिस्टल था जिसमें एक पिपेलिंडेड आर्किटेक्चर और 100 मेगाहर्ट्ज की घड़ी आवृत्ति - 200 मेगाहर्ट्ज थी। एक बाहरी 128-बिट प्रोसेसर बस के साथ 0.75-माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित। इसमें 16 KB कैश (8 KB डेटा और 8 KB निर्देश) था।श्रृंखला में अगला मॉडल प्रोसेसर 21164 (EV5) था, जो 1995 में जारी किया गया था। उनके पास दो पूर्णांक ब्लॉक थे और पहले से ही कैश मेमोरी के तीन स्तर गिने गए (प्रोसेसर में दो, तीसरा - बाहरी)। पहले स्तर के कैश को एक डेटा कैश और प्रत्येक 8 केबी के एक निर्देश कैश में विभाजित किया गया था। दूसरे स्तर में कैश की मात्रा 96 Kb थी। प्रोसेसर घड़ी की गति 266 मेगाहर्ट्ज से 500 मेगाहर्ट्ज तक थी। DEC अल्फा AXP 210641996 में, अल्फा 21264 (EV6) प्रोसेसर 15.2 मिलियन ट्रांजिस्टर के साथ आया था, जो 15.2-माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित किया गया था। उनकी घड़ी की आवृत्ति 450 मेगाहर्ट्ज से 600 मेगाहर्ट्ज तक थी। पूर्णांक ब्लॉक और लोड / सेव ब्लॉक को एक ईबॉक्स मॉड्यूल में जोड़ा गया था, और फ्लोटिंग-पॉइंट ब्लॉक को एक बॉक्स मॉड्यूल में जोड़ा गया था। पहले स्तर के कैश ने निर्देशों और डेटा के लिए मेमोरी आवंटन को बनाए रखा। प्रत्येक भाग का आयतन 64 Kb था। दूसरे स्तर में कैश की मात्रा 2 एमबी से 8 एमबी तक थी।1999 में, डीईसी को कॉम्पैक ने खरीदा था। परिणामस्वरूप, अल्फा का उपयोग करने वाले अधिकांश उत्पादन एपीआई नेटवर्क्स, इंक।इंटेल पी 5 और पी 54 सी प्रोसेसरविनोद धाम के लेआउट के अनुसार, पांचवीं पीढ़ी का प्रोसेसर, जिसका नाम P5 था, विकसित किया गया था। 1993 में, सीपीयू पेंटियम नाम के तहत उत्पादन में चला गया।P5 कोर प्रोसेसर द्विध्रुवी BiCMOS तकनीक का उपयोग कर 800-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग कर निर्मित किए गए थे। इनमें 3.1 मिलियन ट्रांजिस्टर शामिल थे। पेंटियम में 64-बिट डेटा बस, सुपरस्लेकर आर्किटेक्चर था। प्रोग्राम कोड और डेटा की अलग-अलग कैशिंग थी। 16 केबी के पहले स्तर के कैश का उपयोग किया गया था, जिसे 2 खंडों (डेटा के लिए 8 KB और निर्देशों के लिए 8 KB) में विभाजित किया गया था। पहले मॉडल 60 मेगाहर्ट्ज - 66 मेगाहर्ट्ज की आवृत्तियों के साथ थे।

DEC अल्फा AXP 210641996 में, अल्फा 21264 (EV6) प्रोसेसर 15.2 मिलियन ट्रांजिस्टर के साथ आया था, जो 15.2-माइक्रोन प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित किया गया था। उनकी घड़ी की आवृत्ति 450 मेगाहर्ट्ज से 600 मेगाहर्ट्ज तक थी। पूर्णांक ब्लॉक और लोड / सेव ब्लॉक को एक ईबॉक्स मॉड्यूल में जोड़ा गया था, और फ्लोटिंग-पॉइंट ब्लॉक को एक बॉक्स मॉड्यूल में जोड़ा गया था। पहले स्तर के कैश ने निर्देशों और डेटा के लिए मेमोरी आवंटन को बनाए रखा। प्रत्येक भाग का आयतन 64 Kb था। दूसरे स्तर में कैश की मात्रा 2 एमबी से 8 एमबी तक थी।1999 में, डीईसी को कॉम्पैक ने खरीदा था। परिणामस्वरूप, अल्फा का उपयोग करने वाले अधिकांश उत्पादन एपीआई नेटवर्क्स, इंक।इंटेल पी 5 और पी 54 सी प्रोसेसरविनोद धाम के लेआउट के अनुसार, पांचवीं पीढ़ी का प्रोसेसर, जिसका नाम P5 था, विकसित किया गया था। 1993 में, सीपीयू पेंटियम नाम के तहत उत्पादन में चला गया।P5 कोर प्रोसेसर द्विध्रुवी BiCMOS तकनीक का उपयोग कर 800-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग कर निर्मित किए गए थे। इनमें 3.1 मिलियन ट्रांजिस्टर शामिल थे। पेंटियम में 64-बिट डेटा बस, सुपरस्लेकर आर्किटेक्चर था। प्रोग्राम कोड और डेटा की अलग-अलग कैशिंग थी। 16 केबी के पहले स्तर के कैश का उपयोग किया गया था, जिसे 2 खंडों (डेटा के लिए 8 KB और निर्देशों के लिए 8 KB) में विभाजित किया गया था। पहले मॉडल 60 मेगाहर्ट्ज - 66 मेगाहर्ट्ज की आवृत्तियों के साथ थे। इंटेल पेंटियम प्रोसेसरउसी वर्ष, इंटेल ने P54C प्रोसेसर लॉन्च किया। नए प्रोसेसर के उत्पादन को 0.6-माइक्रोन प्रक्रिया प्रौद्योगिकी में स्थानांतरित किया गया था। प्रोसेसर की गति 75 मेगाहर्ट्ज थी, और 1994 से - 90 मेगाहर्ट्ज और 100 मेगाहर्ट्ज। एक साल बाद, P54C (P54CS) की वास्तुकला को 350 एनएम प्रक्रिया प्रौद्योगिकी में स्थानांतरित किया गया और घड़ी की आवृत्ति 200 मेगाहर्ट्ज तक बढ़ गई।1997 में, P5 को नवीनतम अपडेट मिला - P55C (पेंटियम एमएमएक्स)। MMX (MultiMedia eXtension) निर्देश सेट के लिए समर्थन दिखाई दिया है। प्रोसेसर में 4.5 मिलियन ट्रांजिस्टर शामिल हैं और इसे उन्नत 280-नैनोमीटर सीएमओएस तकनीक का उपयोग करके निर्मित किया गया है। पहले स्तर का कैश 32 Kb (डेटा के लिए 16 Kb और निर्देशों के लिए 16 Kb) तक बढ़ गया। प्रोसेसर की आवृत्ति 233 मेगाहर्ट्ज तक पहुंच गई।AMD K5 और K6 प्रोसेसर1995 में, एएमडी ने K5 प्रोसेसर जारी किया। आर्किटेक्चर एक RISC कोर था, लेकिन इसने CISC के जटिल निर्देशों के साथ काम किया। प्रोसेसर का निर्माण 350- या 500-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था, जिसमें 4.3 मिलियन ट्रांजिस्टर थे। सभी K5 में पांच पूर्णांक ब्लॉक और एक फ्लोटिंग पॉइंट ब्लॉक था। निर्देश कैश 16 KB था, और डेटा 8 KB था। प्रोसेसर घड़ी की गति 75 मेगाहर्ट्ज से 133 मेगाहर्ट्ज तक थी।

इंटेल पेंटियम प्रोसेसरउसी वर्ष, इंटेल ने P54C प्रोसेसर लॉन्च किया। नए प्रोसेसर के उत्पादन को 0.6-माइक्रोन प्रक्रिया प्रौद्योगिकी में स्थानांतरित किया गया था। प्रोसेसर की गति 75 मेगाहर्ट्ज थी, और 1994 से - 90 मेगाहर्ट्ज और 100 मेगाहर्ट्ज। एक साल बाद, P54C (P54CS) की वास्तुकला को 350 एनएम प्रक्रिया प्रौद्योगिकी में स्थानांतरित किया गया और घड़ी की आवृत्ति 200 मेगाहर्ट्ज तक बढ़ गई।1997 में, P5 को नवीनतम अपडेट मिला - P55C (पेंटियम एमएमएक्स)। MMX (MultiMedia eXtension) निर्देश सेट के लिए समर्थन दिखाई दिया है। प्रोसेसर में 4.5 मिलियन ट्रांजिस्टर शामिल हैं और इसे उन्नत 280-नैनोमीटर सीएमओएस तकनीक का उपयोग करके निर्मित किया गया है। पहले स्तर का कैश 32 Kb (डेटा के लिए 16 Kb और निर्देशों के लिए 16 Kb) तक बढ़ गया। प्रोसेसर की आवृत्ति 233 मेगाहर्ट्ज तक पहुंच गई।AMD K5 और K6 प्रोसेसर1995 में, एएमडी ने K5 प्रोसेसर जारी किया। आर्किटेक्चर एक RISC कोर था, लेकिन इसने CISC के जटिल निर्देशों के साथ काम किया। प्रोसेसर का निर्माण 350- या 500-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था, जिसमें 4.3 मिलियन ट्रांजिस्टर थे। सभी K5 में पांच पूर्णांक ब्लॉक और एक फ्लोटिंग पॉइंट ब्लॉक था। निर्देश कैश 16 KB था, और डेटा 8 KB था। प्रोसेसर घड़ी की गति 75 मेगाहर्ट्ज से 133 मेगाहर्ट्ज तक थी। AMD K5 प्रोसेसरब्रांड नाम K5 के तहत, SSA / 5 और 5k86 प्रोसेसर के दो संस्करणों का उत्पादन किया गया था। पहले 75 मेगाहर्ट्ज से 100 मेगाहर्ट्ज तक की आवृत्ति पर काम किया। 5k86 प्रोसेसर 90 मेगाहर्ट्ज से 133 मेगाहर्ट्ज तक आवृत्तियों पर काम करता है।1997 में, कंपनी ने K6 प्रोसेसर पेश किया, जिसका आर्किटेक्चर K5 से काफी अलग था। प्रोसेसर 350-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित किए गए थे, जिसमें 8.8 मिलियन ट्रांजिस्टर शामिल थे, जो निर्देशों के निष्पादन के क्रम में बदलाव, एमएमएक्स निर्देशों के एक सेट और फ्लोटिंग-पॉइंट ब्लॉक का समर्थन करते थे। क्रिस्टल क्षेत्र 162 मिमी crystal था। पहले स्तर का कैश कुल 64 Kb (डेटा का 32 Kb और निर्देशों का 32 Kb) था। प्रोसेसर ने 166 मेगाहर्ट्ज, 200 मेगाहर्ट्ज और 233 मेगाहर्ट्ज की आवृत्ति पर काम किया। सिस्टम बस की आवृत्ति 66 मेगाहर्ट्ज थी।1998 में, AMD ने K6-2 आर्किटेक्चर के साथ चिप्स जारी किए, जिसमें 9.3 मिलियन ट्रांजिस्टर 250-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित किए गए थे। अधिकतम चिप आवृत्ति 550 मेगाहर्ट्ज थी।

AMD K5 प्रोसेसरब्रांड नाम K5 के तहत, SSA / 5 और 5k86 प्रोसेसर के दो संस्करणों का उत्पादन किया गया था। पहले 75 मेगाहर्ट्ज से 100 मेगाहर्ट्ज तक की आवृत्ति पर काम किया। 5k86 प्रोसेसर 90 मेगाहर्ट्ज से 133 मेगाहर्ट्ज तक आवृत्तियों पर काम करता है।1997 में, कंपनी ने K6 प्रोसेसर पेश किया, जिसका आर्किटेक्चर K5 से काफी अलग था। प्रोसेसर 350-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित किए गए थे, जिसमें 8.8 मिलियन ट्रांजिस्टर शामिल थे, जो निर्देशों के निष्पादन के क्रम में बदलाव, एमएमएक्स निर्देशों के एक सेट और फ्लोटिंग-पॉइंट ब्लॉक का समर्थन करते थे। क्रिस्टल क्षेत्र 162 मिमी crystal था। पहले स्तर का कैश कुल 64 Kb (डेटा का 32 Kb और निर्देशों का 32 Kb) था। प्रोसेसर ने 166 मेगाहर्ट्ज, 200 मेगाहर्ट्ज और 233 मेगाहर्ट्ज की आवृत्ति पर काम किया। सिस्टम बस की आवृत्ति 66 मेगाहर्ट्ज थी।1998 में, AMD ने K6-2 आर्किटेक्चर के साथ चिप्स जारी किए, जिसमें 9.3 मिलियन ट्रांजिस्टर 250-नैनोमीटर प्रक्रिया प्रौद्योगिकी का उपयोग करके निर्मित किए गए थे। अधिकतम चिप आवृत्ति 550 मेगाहर्ट्ज थी। AMD K6 प्रोसेसर1999 में, तीसरी पीढ़ी को जारी किया गया था - K6-III वास्तुकला। क्रिस्टल ने K6-2 की सभी विशेषताओं को बरकरार रखा, लेकिन एक ही समय में 256 स्तर की क्षमता के साथ दूसरे स्तर का एक अंतर्निहित कैश दिखाई दिया। पहले स्तर के कैश की मात्रा 64 केबी थी।प्रोसेसर AMD K7उसी 1999 में, K6 को K7 प्रोसेसर से बदल दिया गया था। वे 22 मिलियन ट्रांजिस्टर के साथ 250nm तकनीक का उपयोग करके उत्पादित किए गए थे। सीपीयू की एक नई पूर्णांक इकाई (ALU) थी। EV6 सिस्टम बस ने घड़ी सिग्नल के दोनों किनारों पर डेटा ट्रांसमिशन प्रदान किया, जिससे 100 मेगाहर्ट्ज की भौतिक आवृत्ति पर 200 मेगाहर्ट्ज की प्रभावी आवृत्ति प्राप्त करना संभव हो गया। पहले स्तर का कैश 128 Kb (निर्देशों का 64 Kb और डेटा का 64 Kb) था। दूसरे स्तर का कैश 512 केबी पहुंच गया।

AMD K6 प्रोसेसर1999 में, तीसरी पीढ़ी को जारी किया गया था - K6-III वास्तुकला। क्रिस्टल ने K6-2 की सभी विशेषताओं को बरकरार रखा, लेकिन एक ही समय में 256 स्तर की क्षमता के साथ दूसरे स्तर का एक अंतर्निहित कैश दिखाई दिया। पहले स्तर के कैश की मात्रा 64 केबी थी।प्रोसेसर AMD K7उसी 1999 में, K6 को K7 प्रोसेसर से बदल दिया गया था। वे 22 मिलियन ट्रांजिस्टर के साथ 250nm तकनीक का उपयोग करके उत्पादित किए गए थे। सीपीयू की एक नई पूर्णांक इकाई (ALU) थी। EV6 सिस्टम बस ने घड़ी सिग्नल के दोनों किनारों पर डेटा ट्रांसमिशन प्रदान किया, जिससे 100 मेगाहर्ट्ज की भौतिक आवृत्ति पर 200 मेगाहर्ट्ज की प्रभावी आवृत्ति प्राप्त करना संभव हो गया। पहले स्तर का कैश 128 Kb (निर्देशों का 64 Kb और डेटा का 64 Kb) था। दूसरे स्तर का कैश 512 केबी पहुंच गया। AMD K7 प्रोसेसरथोड़ी देर बाद, ओरियन कोर पर आधारित क्रिस्टल दिखाई दिए। इनका उत्पादन 180 एनएम प्रक्रिया प्रौद्योगिकी के अनुसार किया गया था।थंडरबर्ड कर्नेल रिलीज़ ने प्रोसेसर में असामान्य परिवर्तन पेश किए। 2 के स्तर का कैश सीधे प्रोसेसर कोर में स्थानांतरित किया गया था और इसके साथ एक ही आवृत्ति पर काम किया था। कैश 384 केबी (पहले स्तर में 128 केबी कैश और दूसरे स्तर में 256 केबी कैश) की प्रभावी क्षमता के साथ था। सिस्टम बस की घड़ी की आवृत्ति में वृद्धि हुई है - अब यह 133 मेगाहर्ट्ज की आवृत्ति के साथ संचालित होता है।इंटेल पी 6 प्रोसेसर1995 में पी 6 आर्किटेक्चर ने पी 5 को बदल दिया। प्रोसेसर सुपरकार्कर था और संचालन के क्रम में परिवर्तन का समर्थन करता था। प्रोसेसर ने एक दोहरी स्वतंत्र बस का उपयोग किया, जिससे मेमोरी बैंडविड्थ में काफी वृद्धि हुई।उसी 1995 में, अगली पीढ़ी के पेंटियम प्रो प्रोसेसर पेश किए गए थे। क्रिस्टल ने 150 मेगाहर्ट्ज - 200 मेगाहर्ट्ज की आवृत्ति पर काम किया, पहले स्तर में 16 केबी कैश और दूसरे स्तर में 1 एमबी तक कैश था।

AMD K7 प्रोसेसरथोड़ी देर बाद, ओरियन कोर पर आधारित क्रिस्टल दिखाई दिए। इनका उत्पादन 180 एनएम प्रक्रिया प्रौद्योगिकी के अनुसार किया गया था।थंडरबर्ड कर्नेल रिलीज़ ने प्रोसेसर में असामान्य परिवर्तन पेश किए। 2 के स्तर का कैश सीधे प्रोसेसर कोर में स्थानांतरित किया गया था और इसके साथ एक ही आवृत्ति पर काम किया था। कैश 384 केबी (पहले स्तर में 128 केबी कैश और दूसरे स्तर में 256 केबी कैश) की प्रभावी क्षमता के साथ था। सिस्टम बस की घड़ी की आवृत्ति में वृद्धि हुई है - अब यह 133 मेगाहर्ट्ज की आवृत्ति के साथ संचालित होता है।इंटेल पी 6 प्रोसेसर1995 में पी 6 आर्किटेक्चर ने पी 5 को बदल दिया। प्रोसेसर सुपरकार्कर था और संचालन के क्रम में परिवर्तन का समर्थन करता था। प्रोसेसर ने एक दोहरी स्वतंत्र बस का उपयोग किया, जिससे मेमोरी बैंडविड्थ में काफी वृद्धि हुई।उसी 1995 में, अगली पीढ़ी के पेंटियम प्रो प्रोसेसर पेश किए गए थे। क्रिस्टल ने 150 मेगाहर्ट्ज - 200 मेगाहर्ट्ज की आवृत्ति पर काम किया, पहले स्तर में 16 केबी कैश और दूसरे स्तर में 1 एमबी तक कैश था। इंटेल पेंटियम प्रो प्रोसेसर1999 में, पहला पेंटियम III प्रोसेसर पेश किया गया था। वे पी 6 कोर की एक नई पीढ़ी पर आधारित थे जिन्हें कटमाई कहा जाता है, जो कि देशुचट्स के संशोधित संस्करण थे। SSE निर्देशों के लिए समर्थन कर्नेल में जोड़ा गया था, और मेमोरी के साथ काम करने के लिए तंत्र में सुधार हुआ था। कटमई प्रोसेसर की घड़ी की आवृत्ति 600 मेगाहर्ट्ज तक पहुंच गई।2000 में, विल्मेट कोर के साथ पहला पेंटियम 4 प्रोसेसर जारी किया गया था। सिस्टम बस की प्रभावी आवृत्ति 400 मेगाहर्ट्ज (भौतिक आवृत्ति - 100 मेगाहर्ट्ज) थी। पहले स्तर का कैश 8 KB की मात्रा तक पहुँच गया, और दूसरे स्तर का कैश 256 KB तक पहुँच गया।लाइन का अगला कोर नॉर्थवुड (2002) था। प्रोसेसर में 55 मिलियन ट्रांजिस्टर शामिल थे और तांबे के यौगिकों के साथ नई 130-एनएम CMOS तकनीक का उपयोग करके निर्मित किए गए थे। सिस्टम बस की आवृत्ति 400 मेगाहर्ट्ज, 533 मेगाहर्ट्ज या 800 मेगाहर्ट्ज थी।

इंटेल पेंटियम प्रो प्रोसेसर1999 में, पहला पेंटियम III प्रोसेसर पेश किया गया था। वे पी 6 कोर की एक नई पीढ़ी पर आधारित थे जिन्हें कटमाई कहा जाता है, जो कि देशुचट्स के संशोधित संस्करण थे। SSE निर्देशों के लिए समर्थन कर्नेल में जोड़ा गया था, और मेमोरी के साथ काम करने के लिए तंत्र में सुधार हुआ था। कटमई प्रोसेसर की घड़ी की आवृत्ति 600 मेगाहर्ट्ज तक पहुंच गई।2000 में, विल्मेट कोर के साथ पहला पेंटियम 4 प्रोसेसर जारी किया गया था। सिस्टम बस की प्रभावी आवृत्ति 400 मेगाहर्ट्ज (भौतिक आवृत्ति - 100 मेगाहर्ट्ज) थी। पहले स्तर का कैश 8 KB की मात्रा तक पहुँच गया, और दूसरे स्तर का कैश 256 KB तक पहुँच गया।लाइन का अगला कोर नॉर्थवुड (2002) था। प्रोसेसर में 55 मिलियन ट्रांजिस्टर शामिल थे और तांबे के यौगिकों के साथ नई 130-एनएम CMOS तकनीक का उपयोग करके निर्मित किए गए थे। सिस्टम बस की आवृत्ति 400 मेगाहर्ट्ज, 533 मेगाहर्ट्ज या 800 मेगाहर्ट्ज थी। इंटेल पेंटियम 42004 में, प्रोसेसर का उत्पादन फिर से अधिक सूक्ष्म तकनीकी मानकों पर स्थानांतरित किया गया - 90 एनएम। प्रेसकॉट कोर पर पेंटियम 4 जारी किया। पहले स्तर के डेटा का कैश बढ़कर 16 Kb हो गया और दूसरे स्तर का कैश 1 एमबी तक पहुंच गया। घड़ी की आवृत्ति 2.4 गीगाहर्ट्ज़ - 3.8 गीगाहर्ट्ज़, सिस्टम बस की आवृत्ति - 533 मेगाहर्ट्ज या 800 मेगाहर्ट्ज थी।पेंटियम 4 प्रोसेसर में प्रयुक्त अंतिम कोर सिंगल-कोर सेडर मिल था। एक नई प्रक्रिया प्रौद्योगिकी द्वारा उत्पादित - 65 एनएम। चार मॉडल थे: 631 (3 GHz), 641 (3.2 GHz), 651 (3.4 GHz), 661 (3.6 GHz)।Athlon 64 और Athlon 64 X2 प्रोसेसर2003 के अंत में, AMD ने एक नया 64-बिट K8 आर्किटेक्चर जारी किया, जिसे 130-नैनोमीटर प्रक्रिया प्रौद्योगिकी पर बनाया गया था। प्रोसेसर में एक एकीकृत मेमोरी कंट्रोलर और हाइपरट्रांसपोर्ट बस थी। उसने 200 मेगाहर्ट्ज की आवृत्ति पर काम किया। नए AMD उत्पादों को Athlon 64 कहा जाता है। प्रोसेसर ने कई निर्देश सेट का समर्थन किया, जैसे MMX, 3DNow!, SSE, SSE2 और SSE3।

इंटेल पेंटियम 42004 में, प्रोसेसर का उत्पादन फिर से अधिक सूक्ष्म तकनीकी मानकों पर स्थानांतरित किया गया - 90 एनएम। प्रेसकॉट कोर पर पेंटियम 4 जारी किया। पहले स्तर के डेटा का कैश बढ़कर 16 Kb हो गया और दूसरे स्तर का कैश 1 एमबी तक पहुंच गया। घड़ी की आवृत्ति 2.4 गीगाहर्ट्ज़ - 3.8 गीगाहर्ट्ज़, सिस्टम बस की आवृत्ति - 533 मेगाहर्ट्ज या 800 मेगाहर्ट्ज थी।पेंटियम 4 प्रोसेसर में प्रयुक्त अंतिम कोर सिंगल-कोर सेडर मिल था। एक नई प्रक्रिया प्रौद्योगिकी द्वारा उत्पादित - 65 एनएम। चार मॉडल थे: 631 (3 GHz), 641 (3.2 GHz), 651 (3.4 GHz), 661 (3.6 GHz)।Athlon 64 और Athlon 64 X2 प्रोसेसर2003 के अंत में, AMD ने एक नया 64-बिट K8 आर्किटेक्चर जारी किया, जिसे 130-नैनोमीटर प्रक्रिया प्रौद्योगिकी पर बनाया गया था। प्रोसेसर में एक एकीकृत मेमोरी कंट्रोलर और हाइपरट्रांसपोर्ट बस थी। उसने 200 मेगाहर्ट्ज की आवृत्ति पर काम किया। नए AMD उत्पादों को Athlon 64 कहा जाता है। प्रोसेसर ने कई निर्देश सेट का समर्थन किया, जैसे MMX, 3DNow!, SSE, SSE2 और SSE3। एथलॉन 64 प्रोसेसर2005 में, एथलोन 64 एक्स 2 नामक एएमडी प्रोसेसर ने बाजार में प्रवेश किया। ये पहले दोहरे कोर डेस्कटॉप प्रोसेसर थे। मॉडल एक ही क्रिस्टल पर बने दो कोर पर आधारित था। उनके पास एक सामान्य मेमोरी कंट्रोलर, एक हाइपरट्रांसपोर्ट बस और एक कमांड कतार थी।

एथलॉन 64 प्रोसेसर2005 में, एथलोन 64 एक्स 2 नामक एएमडी प्रोसेसर ने बाजार में प्रवेश किया। ये पहले दोहरे कोर डेस्कटॉप प्रोसेसर थे। मॉडल एक ही क्रिस्टल पर बने दो कोर पर आधारित था। उनके पास एक सामान्य मेमोरी कंट्रोलर, एक हाइपरट्रांसपोर्ट बस और एक कमांड कतार थी। Athlon 64 X2 प्रोसेसर2005 और 2006 के दौरान, एएमडी ने डुअल-कोर चिप्स की चार पीढ़ियों को जारी किया: तीन 90-एनएम मैनचेस्टर कोर, टोलेडो और विंडसर, साथ ही साथ 65-एनएम ब्रिस्बेन कोर। प्रोसेसर दूसरे स्तर और बिजली की खपत के कैश आकार में भिन्न होते हैं।इंटेल कोरप्रोसेसर पेंटियम एम प्रोसेसर नेटबर्स्ट माइक्रोआर्किटेक्चर पर आधारित डेस्कटॉप प्रोसेसर की तुलना में अधिक प्रदर्शन प्रदान करते हैं। और इसलिए, उनके वास्तु निर्णय कोर माइक्रोआर्किटेक्चर के लिए आधार बन गए, जो 2006 में जारी किया गया था। पहला डेस्कटॉप क्वाड-कोर प्रोसेसर इंटेल कोर 2 एक्सट्रीम QX6700 था जिसकी घड़ी की आवृत्ति 2.67 गीगाहर्ट्ज़ और दूसरे स्तर में 8 एमबी कैश थी।इंटेल के मोबाइल प्रोसेसर की पहली पीढ़ी का कोड नाम योना था। वे 65 एनएम प्रक्रिया प्रौद्योगिकी का उपयोग कर निर्मित किए गए थे, जो कि बनिआस / डोटन पेंटियम एम वास्तुकला पर आधारित है, जिसमें लाग्रांडे संरक्षण तकनीक शामिल है। प्रोसेसर प्रति घड़ी चक्र में चार निर्देशों तक की प्रक्रिया कर सकता है। कोर ने 128-बिट निर्देश SSE, SSE2 और SSE3 के प्रसंस्करण के लिए एल्गोरिथ्म को फिर से डिजाइन किया है। यदि पहले प्रत्येक आदेश को दो उपायों में संसाधित किया गया था, तो अब ऑपरेशन के लिए केवल एक उपाय की आवश्यकता थी।

Athlon 64 X2 प्रोसेसर2005 और 2006 के दौरान, एएमडी ने डुअल-कोर चिप्स की चार पीढ़ियों को जारी किया: तीन 90-एनएम मैनचेस्टर कोर, टोलेडो और विंडसर, साथ ही साथ 65-एनएम ब्रिस्बेन कोर। प्रोसेसर दूसरे स्तर और बिजली की खपत के कैश आकार में भिन्न होते हैं।इंटेल कोरप्रोसेसर पेंटियम एम प्रोसेसर नेटबर्स्ट माइक्रोआर्किटेक्चर पर आधारित डेस्कटॉप प्रोसेसर की तुलना में अधिक प्रदर्शन प्रदान करते हैं। और इसलिए, उनके वास्तु निर्णय कोर माइक्रोआर्किटेक्चर के लिए आधार बन गए, जो 2006 में जारी किया गया था। पहला डेस्कटॉप क्वाड-कोर प्रोसेसर इंटेल कोर 2 एक्सट्रीम QX6700 था जिसकी घड़ी की आवृत्ति 2.67 गीगाहर्ट्ज़ और दूसरे स्तर में 8 एमबी कैश थी।इंटेल के मोबाइल प्रोसेसर की पहली पीढ़ी का कोड नाम योना था। वे 65 एनएम प्रक्रिया प्रौद्योगिकी का उपयोग कर निर्मित किए गए थे, जो कि बनिआस / डोटन पेंटियम एम वास्तुकला पर आधारित है, जिसमें लाग्रांडे संरक्षण तकनीक शामिल है। प्रोसेसर प्रति घड़ी चक्र में चार निर्देशों तक की प्रक्रिया कर सकता है। कोर ने 128-बिट निर्देश SSE, SSE2 और SSE3 के प्रसंस्करण के लिए एल्गोरिथ्म को फिर से डिजाइन किया है। यदि पहले प्रत्येक आदेश को दो उपायों में संसाधित किया गया था, तो अब ऑपरेशन के लिए केवल एक उपाय की आवश्यकता थी। इंटेल कोर 2 एक्सट्रीम QX67002007 में, लेड-फ्री हाय-के मेटल गेट्स का उपयोग कर 45nm पेनरी माइक्रोआर्किटेक्चर सामने आया। इंटेल कोर 2 डुओ प्रोसेसर परिवार में प्रौद्योगिकी का उपयोग किया गया था। SSE4 निर्देशों के समर्थन को आर्किटेक्चर में जोड़ा गया था, और दोहरे स्तर के प्रोसेसर के दूसरे स्तर में कैश की अधिकतम मात्रा 4 एमबी से 6 एमबी तक बढ़ गई थी।

इंटेल कोर 2 एक्सट्रीम QX67002007 में, लेड-फ्री हाय-के मेटल गेट्स का उपयोग कर 45nm पेनरी माइक्रोआर्किटेक्चर सामने आया। इंटेल कोर 2 डुओ प्रोसेसर परिवार में प्रौद्योगिकी का उपयोग किया गया था। SSE4 निर्देशों के समर्थन को आर्किटेक्चर में जोड़ा गया था, और दोहरे स्तर के प्रोसेसर के दूसरे स्तर में कैश की अधिकतम मात्रा 4 एमबी से 6 एमबी तक बढ़ गई थी। प्रोसेसर AMD Phenom II X62008 में, अगली पीढ़ी की वास्तुकला, नेहेल्म, को रिलीज़ किया गया था। प्रोसेसर ने एक एकीकृत मेमोरी कंट्रोलर का अधिग्रहण किया जो DDR3 SDRAM के 2 या 3 चैनलों या FB-DIMM के 4 चैनलों का समर्थन करता है। एफएसबी बस के बजाय, एक नया क्यूपीआई बस आया। स्तर 2 कैश को घटाकर 256 केबी प्रति कोर कर दिया गया।

प्रोसेसर AMD Phenom II X62008 में, अगली पीढ़ी की वास्तुकला, नेहेल्म, को रिलीज़ किया गया था। प्रोसेसर ने एक एकीकृत मेमोरी कंट्रोलर का अधिग्रहण किया जो DDR3 SDRAM के 2 या 3 चैनलों या FB-DIMM के 4 चैनलों का समर्थन करता है। एफएसबी बस के बजाय, एक नया क्यूपीआई बस आया। स्तर 2 कैश को घटाकर 256 केबी प्रति कोर कर दिया गया। इंटेल कोर i7जल्द ही, इंटेल ने नेहम आर्किटेक्चर को एक नई 32nm प्रक्रिया प्रौद्योगिकी में स्थानांतरित कर दिया। प्रोसेसर की इस लाइन को वेस्टमेयर कहा जाता है।नए माइक्रोआर्किटेक्चर का पहला मॉडल क्लार्कडेल था, जिसमें दो कोर और एक एकीकृत ग्राफिक्स कोर है, जो 45-एनएम प्रक्रिया प्रौद्योगिकी द्वारा निर्मित है।प्रोसेसर AMD K10 AMDकंपनी ने इंटेल के साथ तालमेल रखने की कोशिश की। 2007 में, उसने x86 - K10 माइक्रोप्रोसेसर आर्किटेक्चर पीढ़ी जारी की। एक चिप पर चार प्रोसेसर कोर को जोड़ा गया था। 1 और 2 के स्तर के कैश के अलावा, K10 मॉडल को आखिरकार 2 एमबी का L3 मिला। 1 स्तर के डेटा और निर्देशों का कैश 64 Kb प्रत्येक था, और दूसरे स्तर का कैश 512 Kb था। DDR3 मेमोरी कंट्रोलर के लिए आशाजनक समर्थन भी है। K10 ने दो 64-बिट नियंत्रकों का उपयोग किया। प्रत्येक प्रोसेसर कोर में 128-बिट फ्लोटिंग-पॉइंट मॉड्यूल था। उसके शीर्ष पर, नए प्रोसेसर हाइपरट्रांसपोर्ट 3.0 इंटरफ़ेस के माध्यम से काम करते थे।2007 में, डेस्कटॉप पीसी के लिए एएमडी के फिनोम मल्टी-कोर सीपीयू को K10 आर्किटेक्चर के साथ जारी किया गया था। K10 पर आधारित समाधानों का उत्पादन 65- और 45-एनएम प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था। आर्किटेक्चर (K10.5) के नए संस्करण में, मेमोरी कंट्रोलर ने DDR2 और DDR3 मेमोरी के साथ काम किया।

इंटेल कोर i7जल्द ही, इंटेल ने नेहम आर्किटेक्चर को एक नई 32nm प्रक्रिया प्रौद्योगिकी में स्थानांतरित कर दिया। प्रोसेसर की इस लाइन को वेस्टमेयर कहा जाता है।नए माइक्रोआर्किटेक्चर का पहला मॉडल क्लार्कडेल था, जिसमें दो कोर और एक एकीकृत ग्राफिक्स कोर है, जो 45-एनएम प्रक्रिया प्रौद्योगिकी द्वारा निर्मित है।प्रोसेसर AMD K10 AMDकंपनी ने इंटेल के साथ तालमेल रखने की कोशिश की। 2007 में, उसने x86 - K10 माइक्रोप्रोसेसर आर्किटेक्चर पीढ़ी जारी की। एक चिप पर चार प्रोसेसर कोर को जोड़ा गया था। 1 और 2 के स्तर के कैश के अलावा, K10 मॉडल को आखिरकार 2 एमबी का L3 मिला। 1 स्तर के डेटा और निर्देशों का कैश 64 Kb प्रत्येक था, और दूसरे स्तर का कैश 512 Kb था। DDR3 मेमोरी कंट्रोलर के लिए आशाजनक समर्थन भी है। K10 ने दो 64-बिट नियंत्रकों का उपयोग किया। प्रत्येक प्रोसेसर कोर में 128-बिट फ्लोटिंग-पॉइंट मॉड्यूल था। उसके शीर्ष पर, नए प्रोसेसर हाइपरट्रांसपोर्ट 3.0 इंटरफ़ेस के माध्यम से काम करते थे।2007 में, डेस्कटॉप पीसी के लिए एएमडी के फिनोम मल्टी-कोर सीपीयू को K10 आर्किटेक्चर के साथ जारी किया गया था। K10 पर आधारित समाधानों का उत्पादन 65- और 45-एनएम प्रक्रिया प्रौद्योगिकी का उपयोग करके किया गया था। आर्किटेक्चर (K10.5) के नए संस्करण में, मेमोरी कंट्रोलर ने DDR2 और DDR3 मेमोरी के साथ काम किया। AMD Phenom प्रोसेसर2011 में, नया बुलडोजर आर्किटेक्चर जारी किया गया था। प्रत्येक मॉड्यूल में अपने स्वयं के पूर्णांक ब्लॉक और स्तर 1 कैश के साथ दो कोर होते थे। 8 एमबी एल 3 कैश, हाइपरट्रांसपोर्ट 3.1 बसें, दूसरी पीढ़ी के टर्बो कोर प्रौद्योगिकी, और एवीएक्स, एसएसई 4.1, एसएसई 4.2, एईएस निर्देश सेट का समर्थन किया गया। बुलडोजर प्रोसेसर भी 1866 मेगाहर्ट्ज की प्रभावी आवृत्ति के साथ एक दोहरे चैनल DDR3 मेमोरी कंट्रोलर के साथ संपन्न थे।

AMD Phenom प्रोसेसर2011 में, नया बुलडोजर आर्किटेक्चर जारी किया गया था। प्रत्येक मॉड्यूल में अपने स्वयं के पूर्णांक ब्लॉक और स्तर 1 कैश के साथ दो कोर होते थे। 8 एमबी एल 3 कैश, हाइपरट्रांसपोर्ट 3.1 बसें, दूसरी पीढ़ी के टर्बो कोर प्रौद्योगिकी, और एवीएक्स, एसएसई 4.1, एसएसई 4.2, एईएस निर्देश सेट का समर्थन किया गया। बुलडोजर प्रोसेसर भी 1866 मेगाहर्ट्ज की प्रभावी आवृत्ति के साथ एक दोहरे चैनल DDR3 मेमोरी कंट्रोलर के साथ संपन्न थे। एएमडी बुलडोजर प्रोसेसर2013 में, कंपनी ने प्रोसेसर की अगली पीढ़ी - Piledriver पेश की। यह मॉडल बुलडोजर की एक बेहतर वास्तुकला थी। शाखा भविष्यवाणी ब्लॉकों को परिष्कृत किया गया है, और फ्लोटिंग पॉइंट और पूर्णांक कंप्यूटिंग मॉड्यूल के प्रदर्शन में वृद्धि हुई है, साथ ही साथ घड़ी की गति भी।इतिहास को देखते हुए, आप प्रोसेसर के विकास के चरणों का पता लगा सकते हैं, उनकी वास्तुकला में बदलाव कर सकते हैं, विकास प्रौद्योगिकियों में सुधार कर सकते हैं और बहुत कुछ। आधुनिक सीपीयू उन लोगों से अलग हैं जो पहले सामने आए थे, लेकिन साथ ही साथ उनके पास सामान्य विशेषताएं हैं।

एएमडी बुलडोजर प्रोसेसर2013 में, कंपनी ने प्रोसेसर की अगली पीढ़ी - Piledriver पेश की। यह मॉडल बुलडोजर की एक बेहतर वास्तुकला थी। शाखा भविष्यवाणी ब्लॉकों को परिष्कृत किया गया है, और फ्लोटिंग पॉइंट और पूर्णांक कंप्यूटिंग मॉड्यूल के प्रदर्शन में वृद्धि हुई है, साथ ही साथ घड़ी की गति भी।इतिहास को देखते हुए, आप प्रोसेसर के विकास के चरणों का पता लगा सकते हैं, उनकी वास्तुकला में बदलाव कर सकते हैं, विकास प्रौद्योगिकियों में सुधार कर सकते हैं और बहुत कुछ। आधुनिक सीपीयू उन लोगों से अलग हैं जो पहले सामने आए थे, लेकिन साथ ही साथ उनके पास सामान्य विशेषताएं हैं। Source: https://habr.com/ru/post/hi392175/

All Articles