परिचय

एक बार, जब चारों ओर सब कुछ बड़ा था, और मैं छोटा था, मैंने Wojciechowski की पुस्तक रेडियो-इलेक्ट्रॉनिक खिलौने पढ़ी, जिसमें वर्णित उपकरणों को जीवन में लाने के लिए उत्सुक था। इसलिए, पहले से ही दूर के 2008 वर्ष में, कई दसियों में से विद्युत चुम्बकीय रिले, एक 4-बिट ALU ( RCVM1 - रिले डिजिटल कम्प्यूटिंग मशीन - संस्करण 1 ) को जोड़ने और घटाने में सक्षम इकट्ठा किया गया था। और फिर मैंने सोचा - और क्या होगा अगर मैं काफी बड़ी संख्या में रिले इकट्ठा करता हूं और एक पूर्ण रिले कंप्यूटर का निर्माण करता हूं? आवश्यक संख्या तक धीरे-धीरे रिले को यहां और वहां इकट्ठा करने में केवल 8 साल लग गए, और मैंने बनाना शुरू कर दिया।

मुझे एक डिजिटल रिले कंप्यूटर का दूसरा संस्करण बनाने के लिए अपनी परियोजना से परिचित करवाता हूं, जिसका नाम "ब्रेनफुकपीसी" है - वॉन न्यूमैन वास्तुकला के साथ 16-बिट कंप्यूटर और ब्रेनफक भाषा के लिए निर्देशों का एक सेट। डिजाइन का काम पूरा हो गया है, और मैं इस राक्षस को बनाने की प्रक्रिया में हूं।

1 विनिर्देशों

- पता बस की चौड़ाई: 16 बिट्स

- संबोधन: शब्द द्वारा शब्द, 16 बिट / शब्द

- मेमोरी क्षमता: 64 किलोसलोव (128KB)

- डेटा बस चौड़ाई: 16 बिट

- कोड और डेटा के लिए एकीकृत पता स्थान (वॉन न्यूमैन आर्किटेक्चर)

- घड़ी की आवृत्ति (डिजाइन): 100 हर्ट्ज, 1 निर्देश / चक्र

- निर्देश सेट: Brainfuck ++

- रिले (डिजाइन) की संख्या: 792

- प्रयुक्त रिले: रीड स्विच, RES55 (1p), RES64 (1z)

विवरण लुढ़का

काम का सामान्य सिद्धांत

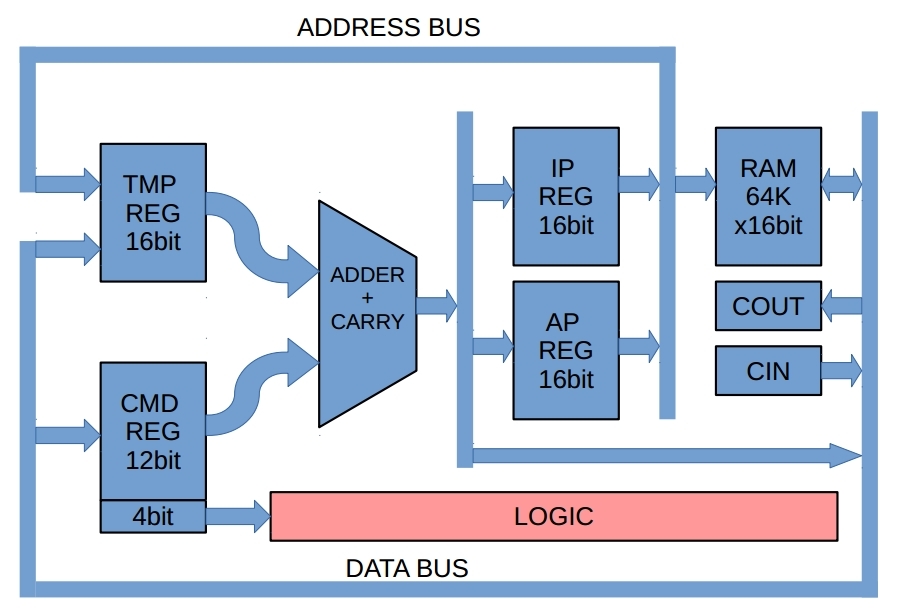

कंप्यूटर की सामान्यीकृत संरचना पर विचार करें:

चित्र 1: सामान्यीकृत कंप्यूटर संरचना

केंद्रीय तत्व योजक है, और सरल नहीं है, लेकिन समानांतर स्थानांतरण के साथ। इसकी आवश्यकता क्यों है - मैं थोड़ा नीचे बताऊंगा।

कार्यक्रम और डेटा एक मेमोरी ब्लॉक में संग्रहीत होते हैं। उन तक पहुंच आईपी अनुदेश रजिस्टर में दर्ज पते पर या एपी एड्रेस रजिस्टर में दर्ज की जाती है, जो अब हम पढ़ना चाहते हैं - एपी में निर्दिष्ट पते पर डेटा, या आईपी पते पर दर्ज अनुदेश।

इस ट्यूरिंग टेप को संचालित करने के लिए (और ब्रेनफक प्रोग्रामिंग भाषा इसकी सटीक पहचान करती है), हमें तीन में से एक कार्य करने में सक्षम होना चाहिए:

- वर्तमान डेटा सेल में मूल्य बदलें, अर्थात्, जोड़ें / उप संचालन करें। ब्रेनफक में, सेल में मूल्य केवल एक द्वारा बदला जा सकता है, अर्थात। +1 या -1। लेकिन एक पूर्ण योजक होने के नाते, यह एक पाप है कि लंबे समय तक नहीं गिरना +++++++++++++++++ (------------) एक ऑपरेशन में एपी + = एन ( एपी- = एन) काफी तेजी से प्रक्रिया को तेज करता है। गणना। ([[]] (या [+]) को * एपी = ०) में बदलना न भूलें;

- वर्तमान में चयनित डेटा सेल की संख्या बदलें। यही है, डेटा मेमोरी (एपी ++, एपी--) के माध्यम से चलना;

- वर्तमान अनुदेश की संख्या बदलें। सबसे पहले, प्रत्येक निर्देश के बाद, हमें आईपी रजिस्टर में एक से एक मूल्य बढ़ाना होगा। दूसरे, यदि कोड में शाखाएं हैं (छोरों को व्यवस्थित करने के लिए डिफ़ॉल्ट रूप से) तो यह मान बदल दें। केवल एक नियंत्रण ध्वज है - जेड। तदनुसार, जंपइफजेरो और जंपइफ्नोटजेरो कमांड हैं।

कुल मिलाकर, हमें योजक के एक इनपुट के लिए निम्नलिखित तीन ब्लॉकों में से किसी एक के मूल्य की आपूर्ति करने में सक्षम होने की आवश्यकता है - एपी-रजिस्टर, आईपी-रजिस्टर, डेटा बस। हम इसे अस्थायी रजिस्टर के माध्यम से करेंगे, जिसमें हम आवश्यक मानों में से एक को बचाएंगे, 16-बिट कुंजियों का उपयोग करके वांछित को जोड़ेंगे।

योजक के दूसरे इनपुट पर, हम एक संख्या सबमिट करेंगे जिसके द्वारा इनमें से किसी एक मान को प्लस या माइनस में बदलना चाहिए। निर्देश की सीमित चौड़ाई के कारण, आप इसे केवल + -12 बिट संख्या से बदल सकते हैं। हालांकि, ब्रेनफक के लिए यह पर्याप्त से अधिक है ("सभी के लिए पर्याप्त", हाँ)।

हम इन 12 बिट्स को कमांड के रजिस्टर से ले लेंगे, ऐसे कमांड्स की उपस्थिति में यह स्वाभाविक है, क्योंकि कमांड्स का कुछ हिस्सा एडिटर का उपयोग बिल्कुल नहीं करता है। यह मत भूलो कि अतिरिक्त के लिए दाखिल करने के साथ, संवर्धित कोड में नकारात्मक संख्याएं दी जाएंगी। यूनिट ट्रांसफर इनपुट (यानी A + invB + 1 होगा)

गणना परिणाम तुरंत उस स्थान पर लोड किया जाता है जहां हमें यह मिला है। अस्थायी रजिस्टर के कारण, हम यह दर्द रहित तरीके से कर सकते हैं।

वास्तुकला के बारे में अधिक विवरण (मैं भी उबाऊ कहूंगा) इस वीडियो में पाया जा सकता है:

निर्देश सेट

एक सामान्य योजनाबद्ध आरेख तैयार करने में सक्षम, जो 8 बुनियादी ब्रेनफक निर्देशों को लागू करने में सक्षम था, मुझे एहसास हुआ कि इसमें बहुत अधिक क्षमता है। इसलिए, मैंने निर्देशों का एक व्यापक सेट विकसित किया जो ब्रेनफक के साथ संगत है, लेकिन प्रत्येक स्रोत ब्रेनफक अनुदेश को 16-बिट कंप्यूटर अनुदेश में संकलित करने की आवश्यकता है।

निर्देशों का सामान्य विवरण

सभी निर्देश 16-बिट हैं। कई हिस्सों से बनाया गया है।

- 15, 14, 13 बिट्स - अनुदेश का वर्ग निर्धारित करते हैं

- बिट 12 - साइन निर्देशों के लिए साइन बिट

- बिट्स 11-0 - हस्ताक्षरित इंट-ए के निचले 12 बिट्स होते हैं। सबसे महत्वपूर्ण 4 बिट्स 12 बिट के मूल्य के अनुसार बनते हैं।

निर्देश तालिका

| निर्देश मैनुअल | opcode | आपरेशन | ब्रेनफॉक से बराबर | विवरण |

|---|

| m16 जोड़ें | 0X XX | एपी ← एपी + एम १६ | '+' (दोहराएँ m16 बार) | आधार को चयनित सेल के वर्तमान मूल्य में जोड़ता है |

| उप m16 | 1X XX | एपी ← एपी - एम १६ | '-' (m16 बार दोहराएं) | तदनुसार, यह आधार को घटाता है |

| एडीए एम १६ | 2X XX | एपी ← एपी + एम १६ | '>' (M16 बार दोहराएं) | पते का मूल्य बढ़ाता है |

| विज्ञापन m16 | 3X XX | एपी ← एपी - एम १६ | '<' (M16 बार दोहराएं) | पता मान घटाता है। |

| jz m16 | 4X XX | (* एपी == ०)? आईपी IP आईपी + एम १६: आईपी ← आईपी | '[' | यदि वर्तमान सेल का मान शून्य है तो IP + m16 पर जाएं |

| jz m16 | 5X XX | (* एपी == ०)? आईपी IP आईपी - एम १६: आईपी ← आईपी | नहीं | यदि वर्तमान सेल का मान शून्य है, तो IP - m16 पर जाएं |

| jnz m16 | 6X XX | (* एपी! = 0)? आईपी IP आईपी + एम १६: आईपी ← आईपी | नहीं | यदि वर्तमान सेल का मान शून्य नहीं है, तो IP + m16 पर जाएं |

| jnz m16 | 7X XX | (* एपी! = 0)? आईपी IP आईपी - एम १६: आईपी ← आईपी | ']' | यदि वर्तमान सेल का मान शून्य नहीं है, तो IP - m16 पर जाएं |

| और m16 | 8X XX | एपी ← एपी और एम 16 | नहीं | तार्किक और एक सकारात्मक संख्या के साथ |

| और m16 | 9 एक्स XX | एपी ← एपी और एम 16 | नहीं | तार्किक और एक नकारात्मक संख्या के साथ (किसी और को उच्च 4 बिट्स बनाना होगा) |

| या m16 | एएक्स एक्सएक्सएक्स | एपी ← एपी या एम १६ | नहीं | तार्किक या सकारात्मक निरंतर के साथ |

| या m16 | bX XX | एपी ← एपी या एम १६ | नहीं | तार्किक या नकारात्मक स्थिरांक के साथ |

| में | c0 00 | * एपी ← CIN | '' | कंसोल से एक m8 वर्ण पढ़ें। यदि इनपुट बफर खाली है, तो इसके लिए प्रतीक्षा करें। |

| बाहर | सी ०१ | COUT ← * AP | '।' | कंसोल के लिए M8 वर्ण मुद्रित करें |

| clr.ap | d0 01 | एपी ← 0 | नहीं | साफ एपी रजिस्टर। आदेश संयोजन की अनुमति देता है |

| clr.ip | घ ०२ | आईपी ← 0 | नहीं | IP रजिस्टर साफ़ करें। आदेश संयोजन की अनुमति देता है |

| clr.dp | दि ०४ | * एपी ← 0 | '[+]' या '[-]' | स्पष्ट मेमोरी सेल। आदेश संयोजन की अनुमति देता है |

| set.ap | d0 10 | एपी AP * एपी | नहीं | एपी रजिस्टर करने के लिए वर्तमान मूल्य लिखें |

| set.ip | d0 20 | आईपी AP * एपी | नहीं | आईपी रजिस्टर के लिए वर्तमान मूल्य लिखें |

| get.ap | d1 00 | * एपी ← एपी | नहीं | एपी रजिस्टर से वर्तमान मूल्य पढ़ें |

| get.ip | d2 00 | * एपी AP आईपी | नहीं | आईपी रजिस्टर से वर्तमान मूल्य पढ़ें |

| mode.b8 | ई १ ०० | | नहीं | 8-बिट सक्रियण (1) |

| mode.b16 | ई २ ०० | | नहीं | 16-बिट सक्रियण |

| पड़ाव | f0 00 | | नहीं | मशीन बंद करो |

- एपी - पता रजिस्टर

- आईपी - निर्देश रजिस्टर

- * एपी - वर्तमान स्मृति स्थान

- CIN - कंसोल इनपुट

- COUT - कंसोल आउटपुट

- जब 8-बिट मोड सक्रिय होता है, तो एडिटर 16-बिट मोड में काम करना जारी रखता है। हालांकि, सशर्त निर्देश (अर्थात्, शून्य के लिए समानता के लिए वर्तमान मेमोरी सेल के मूल्य का परीक्षण) 8-बिट बन जाता है। ( AP & 0x00FF == 0)? और ( AP & 0x00FF! = 0) कंसोल इनपुट और आउटपुट ने अब तक हमेशा 8-बिट को छोड़ने का फैसला किया है। अंत में प्रिंट करने के लिए यूनिकोड में नहीं?

इस वीडियो में, मैंने विस्तार से बात की (लेकिन थोड़ा समझ में आया) कि प्रत्येक निर्देश क्या करता है और यह किस ब्रेनफॉक निर्देश से मेल खाता है:

समानांतर योजक

रिले कंप्यूटर न केवल रिले, बल्कि तेजी से भी होना चाहिए। किसी भी अन्य कंप्यूटर की तरह, मेरा भी एक सिंक्रोनस मशीन होगा, जो घड़ी जनरेटर से सुसज्जित होगा। स्वाभाविक रूप से, मैं घड़ी चक्रों को बर्बाद नहीं करना चाहूंगा और प्रत्येक ऑपरेशन को एक चक्र में फिट करने की कोशिश करूंगा - अर्थात्, सिंक्रोनस जनरेटर के बढ़ते और गिरने वाले किनारों के लिए, मैं एक नई कमांड लोड कर सकता हूं और इसे निष्पादित कर सकता हूं। इसी समय, यह वांछनीय है कि सभी आदेशों को समान अवधि के लिए निष्पादित किया जाए।

प्रत्येक रिले के संचालन और रिलीज में एक निश्चित देरी होती है, जिसे हम समय की 1 पारंपरिक इकाई (क्यू) के लिए ले जाएंगे यदि हम रिले RES22, 1u.e का उपयोग करते हैं। 12-15ms (सूचनात्मक), RES64 - 1.3ms (सूचनात्मक) के बराबर होगा। मेरी कार में सबसे महंगा (और सबसे लगातार) ऑपरेशन योजक है।

अपने आप से, यह काफी सरल और तेज़ है, लेकिन "एक चेतावनी है" जो हस्तांतरण संकेत की गणना और संचार करने की विधि में निहित है।

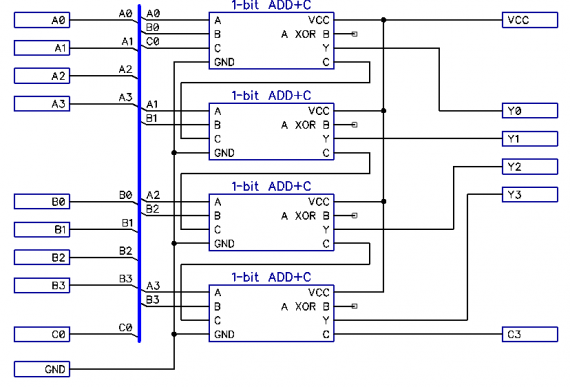

चित्रा 2: सीरियल ट्रांसफर योजक।

प्रारंभ में, मैंने एक अनुक्रमिक कैरी योजक का उपयोग करने की योजना बनाई। इस तरह के योजक में, प्रत्येक बाद का निर्वहन वर्तमान एक के निर्वहन हस्तांतरण संकेत की स्थिति पर निर्भर करता है। नतीजतन, गणना ऑपरेशन की अवधि 2 घन के बीच उतार-चढ़ाव होगी - एन * 2 क्यू, जहां एन अंकों की संख्या है। नतीजतन, 16-बिट अनुक्रमिक कैरी योजक में अधिकतम 32 घन की देरी होगी

समानांतर कैरी एडर्स अधिकतम प्रदर्शन प्रदान करते हैं। उनमें डिस्चार्ज से लेकर डिस्चार्ज तक ट्रांसफर के प्रसार की प्रक्रियाओं का अभाव है। प्रत्येक श्रेणी में, आउटपुट मान एक साथ उत्पन्न होते हैं:

चित्र 3: समानांतर कैरी योजक

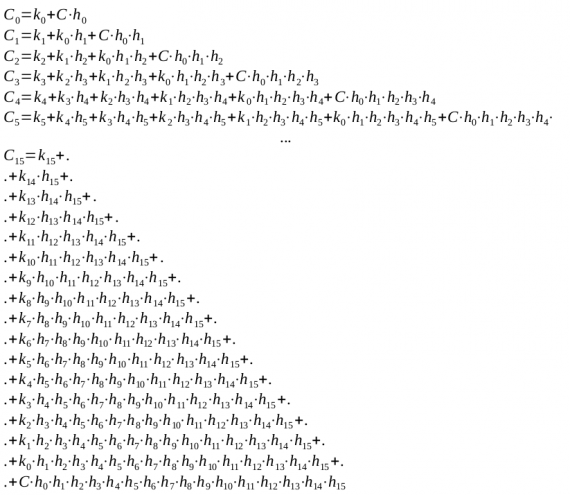

संकेतित गुणों के साथ एक योजक के निर्माण की क्षमता योग और हस्तांतरण कार्यों के प्रजनन पर आधारित है, जो केवल निर्वहन ग्रिड के स्थान की परवाह किए बिना, शर्तों के मूल्यों पर निर्भर करते हैं। पकड़ यह है कि समानांतर हस्तांतरण योजना स्वयं प्रत्येक बाद के निर्वहन के साथ अधिक जटिल हो जाती है। यहां देखें, क्या होता है:

चित्र 4: (जो लटेक्स फॉर्मूले के रूप में होना चाहिए था, लेकिन नहीं) बिट्स के लिए ट्रांसफर सिग्नल की गणना के लिए समीकरण। जहाँ - बिटवाइज़ एंड, - बिटवाइज़ OR

नतीजतन, समानांतर प्रवास को लागू करना बहुत महंगा है। हालांकि, यह ध्यान दिया जा सकता है कि अगले डिस्चार्ज में निकोलस केज के साथ पिछले एक की गणना के लिए समीकरण है (एक मेम "" ठीक है ?? "होना चाहिए), इसलिए, सिद्धांत रूप में, यह केवल वरिष्ठ डिस्चार्ज के लिए एक ट्रांसफर गणना योजना बनाने के लिए पर्याप्त होगा, और बाकी को प्रदान करना होगा।" मध्यवर्ती परिणामों का निष्कर्ष।

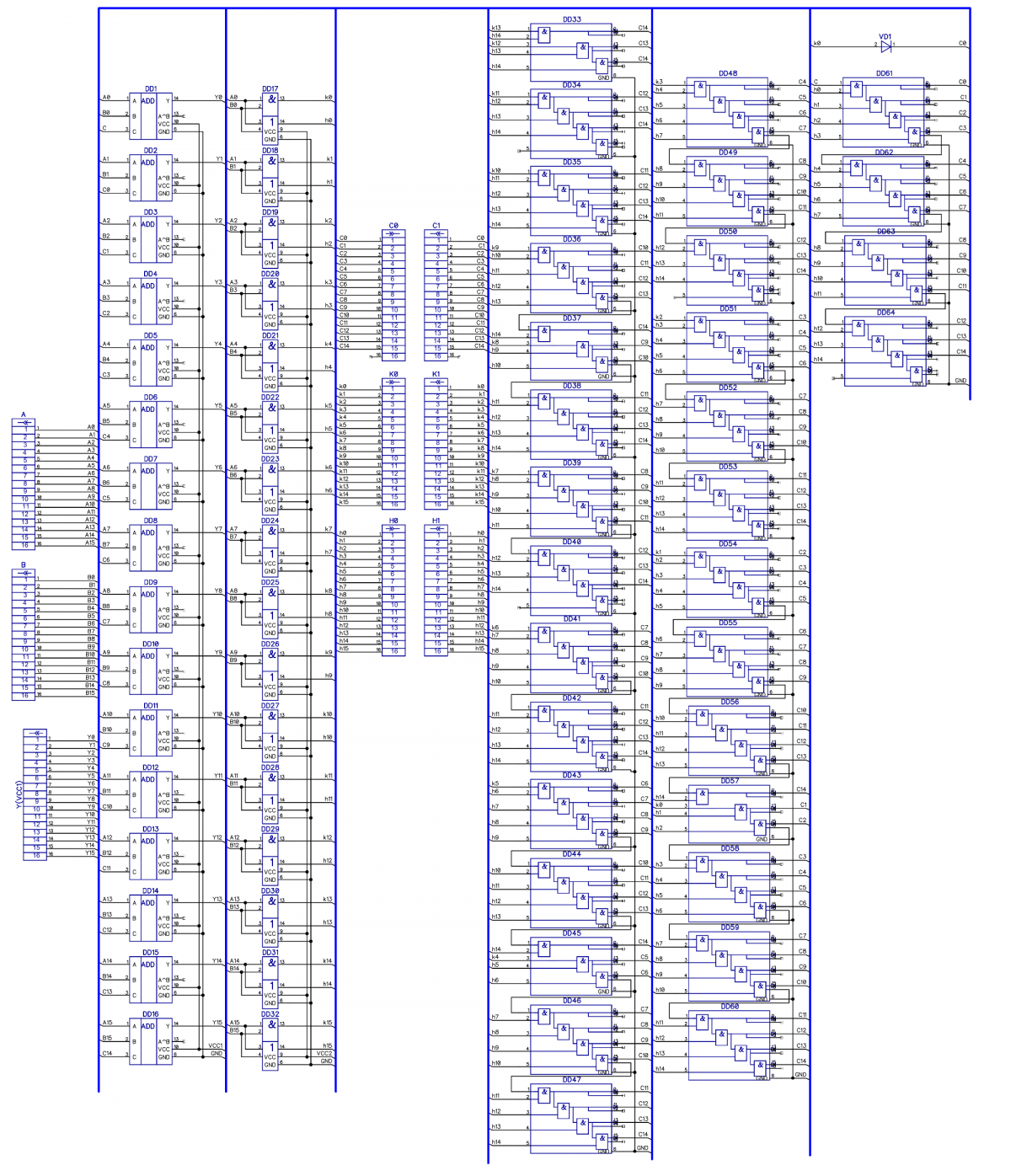

चित्र 5: 16-बिट समांतर योजक का पूर्ण आरेख

चित्रा 5 में, पहले दो कॉलम स्वयं जोड़ रहे हैं। इसके बाद 2AND और 2OR ब्लॉक आते हैं, जो h और k के मध्यवर्ती मान बनाते हैं, जो चित्र 4 में दिखाए गए हैं। उनकी उपस्थिति ने मुझे इसके अलावा और गुणन के तार्किक संचालन के साथ कमांड की सूची का विस्तार करने के लिए प्रेरित किया, जिसके लिए मुझे केवल कुछ जोड़े और इसी माइक्रोकोड को जोड़ने की आवश्यकता है।

बाकी सब कुछ 4 RES64 रिले के आधार पर 5AND ब्लॉक है, जिसे सोल्डर किया जा सकता है ताकि एक मॉड्यूल का उपयोग किया जा सके, उदाहरण के लिए, 2AND + 3AND। इन ब्लॉकों के लिए, प्रत्येक तार्किक और चरण एक डायोड के माध्यम से आउटपुट होता है, जो आपको मध्यवर्ती हस्तांतरण सिग्नल एकत्र करने की अनुमति देता है।

अनुमानित संकेत प्रसार समय: योजक 1 घन के लिए सामना करते हैं, इस समय संकेत 2AND / 2OR ब्लॉकों के आउटपुट पर उत्पन्न होते हैं, फिर 1 घन - 5AND ब्लॉक में गुणा करके, डायोड पर तार्किक जोड़, देरी का परिचय नहीं देता है। खैर, आखिरी वाला योजक को पुनर्गणना पर खर्च किया गया।

कुल 3 घन 32, बनाम या योजक के लिए 4.5 एमएस से अधिक नहीं।

रजिस्टरों

मशीन में चार 16-बिट विशेष पंजीकृत हैं। कोई रॉन नहीं। केवल तंग बंधन, केवल कट्टर! इसमें डी-फ्लिप-फ्लॉप होते हैं, प्रत्येक डी-फ्लिप-फ्लॉप निम्नलिखित सर्किट के साथ 4 RES55 रिले पर एक अलग मॉड्यूल है:

चित्रा 6: डी-फ्लिप-फ्लॉप मॉड्यूल के योजनाबद्ध आरेख। कहीं न कहीं अभी भी एक कनेक्टर है, लेकिन यहां यह महत्वपूर्ण नहीं है, क्योंकि सब कुछ हस्ताक्षरित है।

डेटा डेटा इनपुट के लिए आता है, जो रिले निर्धारित करता है कि सिंक्रनाइज़ेशन सिग्नल कहाँ जाएगा - ट्रिगर को रीसेट करने के लिए, या इसे स्थापित करने के लिए (जिसके लिए दो और रिले जिम्मेदार हैं, एक स्वयं-लॉकिंग के साथ)। चौथे रिले को स्विचिंग आउटपुट Q मिलता है। एक बहुत ही उपयोगी सुविधा।

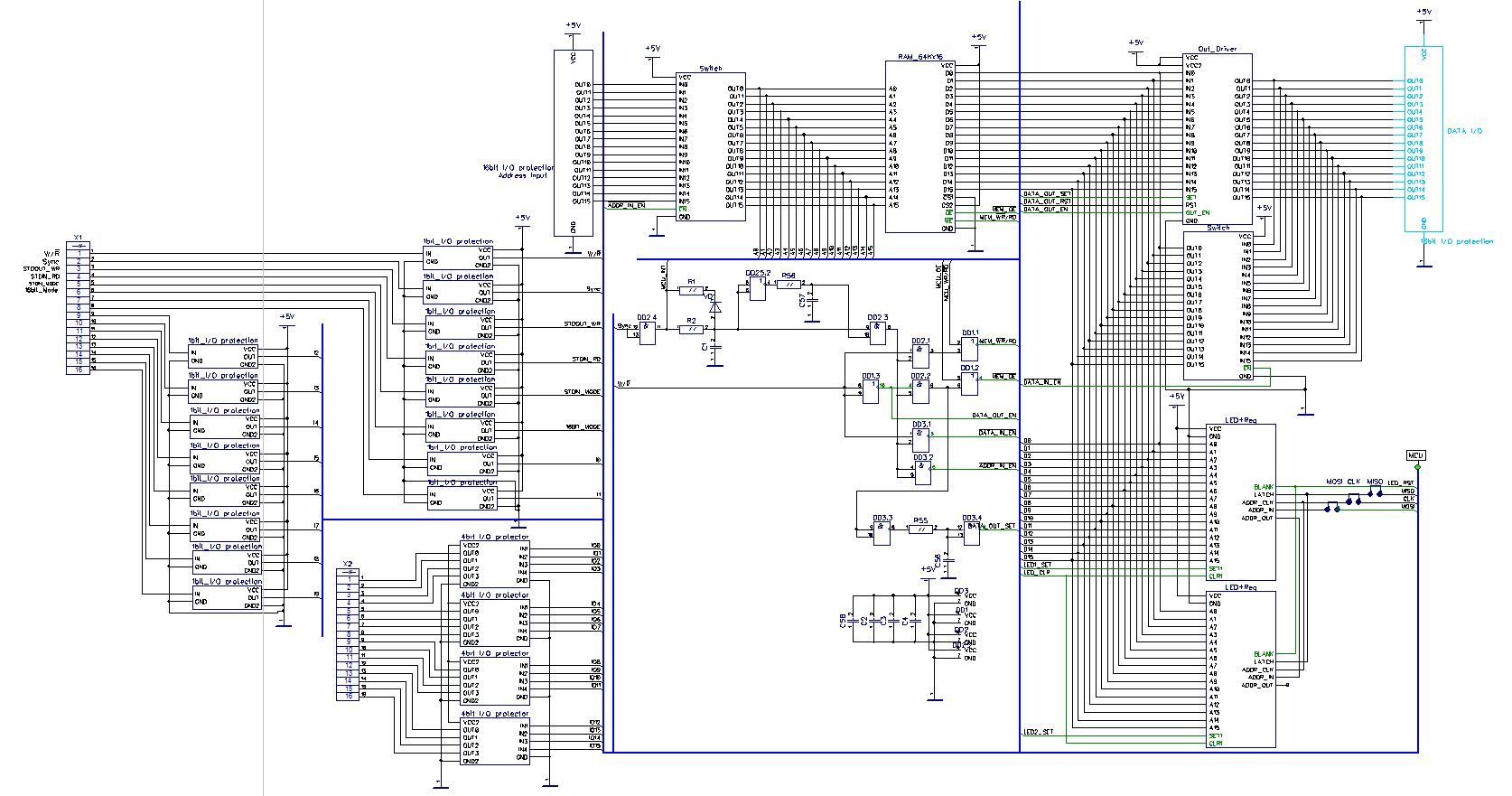

मेमोरी बोर्ड

चित्र 7: मेमोरी बोर्ड। बोर्ड का आयाम 315x200 मिमी

एक बहुत ही जटिल और महत्वपूर्ण तत्व, हालांकि मेमोरी सर्किट स्वयं ब्लॉक के कुल भरने का एक छोटा सा हिस्सा है। इस बोर्ड का कार्य, सबसे पहले, कार्यक्रमों और डेटा की कुल मेमोरी के 64 किलोसलोव को ले जाना है। इसे दो 64 केबीटी कैश चिप्स के आधार पर इकट्ठा किया गया है। प्रोटेक्शन सर्किट और स्विच के माध्यम से पता इनपुट कंप्यूटर एड्रेस बस से जुड़ा होता है, और डेटा बस की तरफ इनपुट बफर और आउटपुट ड्राइवर का एक जटिल सिस्टम भी स्विच के साथ होता है। मेमोरी में पढ़ने और लिखने के लिए, दो लाइनें डब्ल्यू / आर और सिंक जिम्मेदार हैं। पहला चुनता है कि हम क्या करेंगे, दूसरा - वास्तव में यह करेंगे।

और जबकि यह सिंक खुद नहीं है, मेमोरी कार्ड स्वाभाविक रूप से अपना जीवन जीता है। रेंडर करने पर, आप दो 16x16 एलईडी मैट्रिक्स देख सकते हैं। यह डिस्प्ले कुछ मेमोरी एरिया दिखाता है। एक तरह का VideoRAM, जो प्रोग्रामेटिक रूप से निर्धारित होता है। मेमोरी चिप से पूछताछ करता है और Atmega1280 माइक्रोकंट्रोलर के आउटपुट को नियंत्रित करता है।

सिम के लिए, माइक्रोकंट्रोलर के कार्य समाप्त नहीं होते हैं। कंसोल इनपुट और आउटपुट इस पर हैंग होते हैं। यह आउटपुट कहाँ होगा - मैंने अभी तक फैसला नहीं किया है, इसलिए नियमित कंसोल के लिए यूएसबी-सीरियल कनवर्टर और वाई-फाई के लिए ईएसपी 8266 बोर्ड पर तलाकशुदा हैं। उत्तरार्द्ध के अनुसार, कंप्यूटर में मेमोरी और कंसोल में प्रोग्राम डाउनलोड करने की क्षमता के साथ एक वेब पेज रखने की सबसे जरूरी योजनाओं में। हां, एमके के कार्यों में प्रोग्राम का प्रारंभिक लोडिंग रैम भी शामिल है, जिसके लिए रैम तक इसकी पूर्ण पहुंच है, साथ ही एक छोटे से 1 MEP EEPROM-in को प्रोग्रामों को संग्रहीत करने के लिए।

चित्र 8: मेमोरी कार्ड का योजनाबद्ध आरेख। माइक्रोकंट्रोलर और ब्लॉक आरेख नहीं दिखाए गए

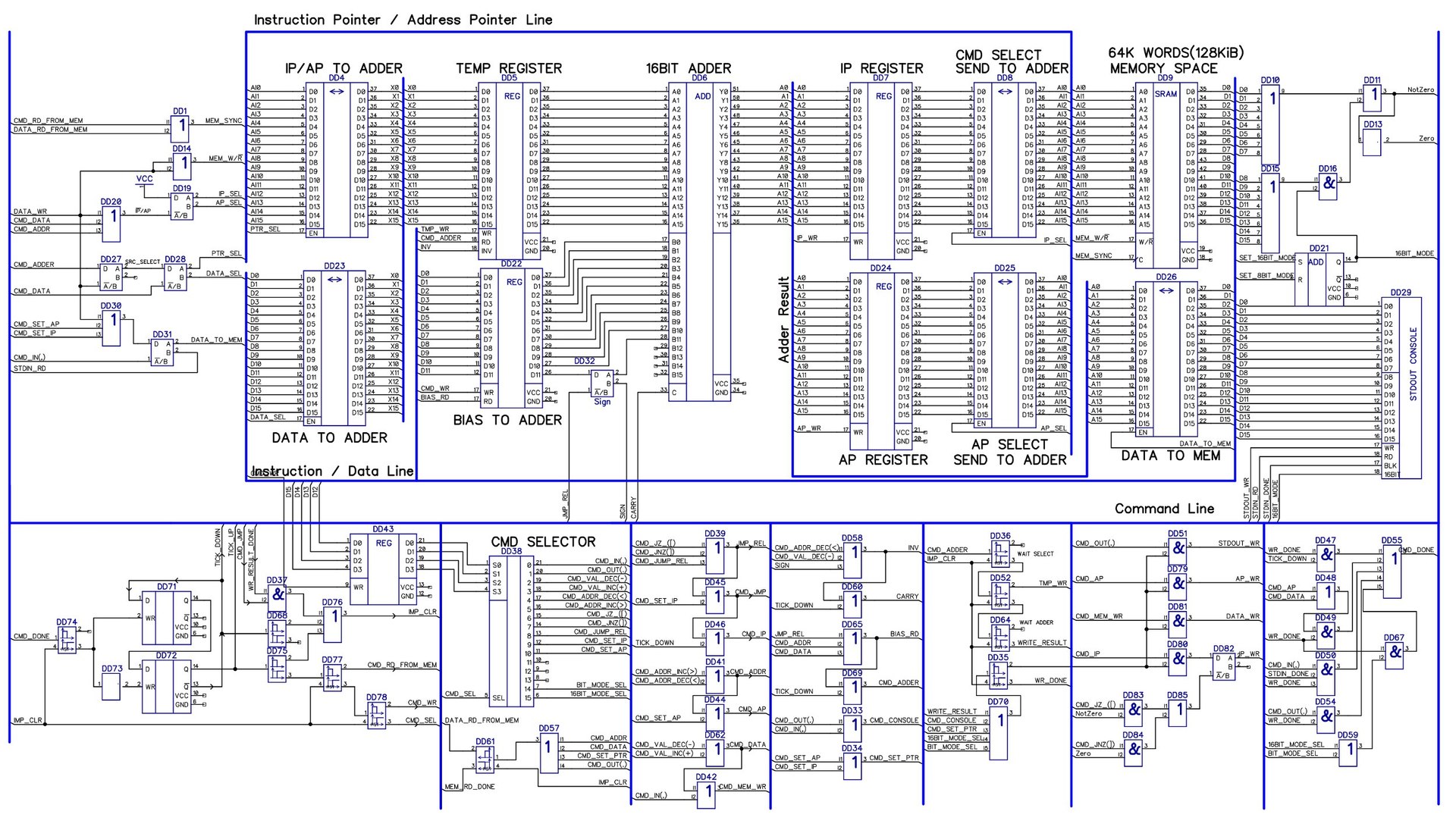

तर्क ब्लॉक

मुझे नहीं पता कि वह आखिर कैसे देखेगा। नवीनतम संस्करण सामान्य कंप्यूटर सर्किट पर मौजूद है, लेकिन मुझे यह पसंद नहीं है। सबसे अधिक संभावना है कि मैं 12-स्टेज सीक्वेंसर बनाऊंगा और चाबियों की मदद से मैं व्यक्तिगत ब्लॉक को सिग्नल भेजूंगा।

चित्र 9: 16-बिट ब्लॉक के आसपास सब कुछ एक लॉजिक ब्लॉक है

डिज़ाइन

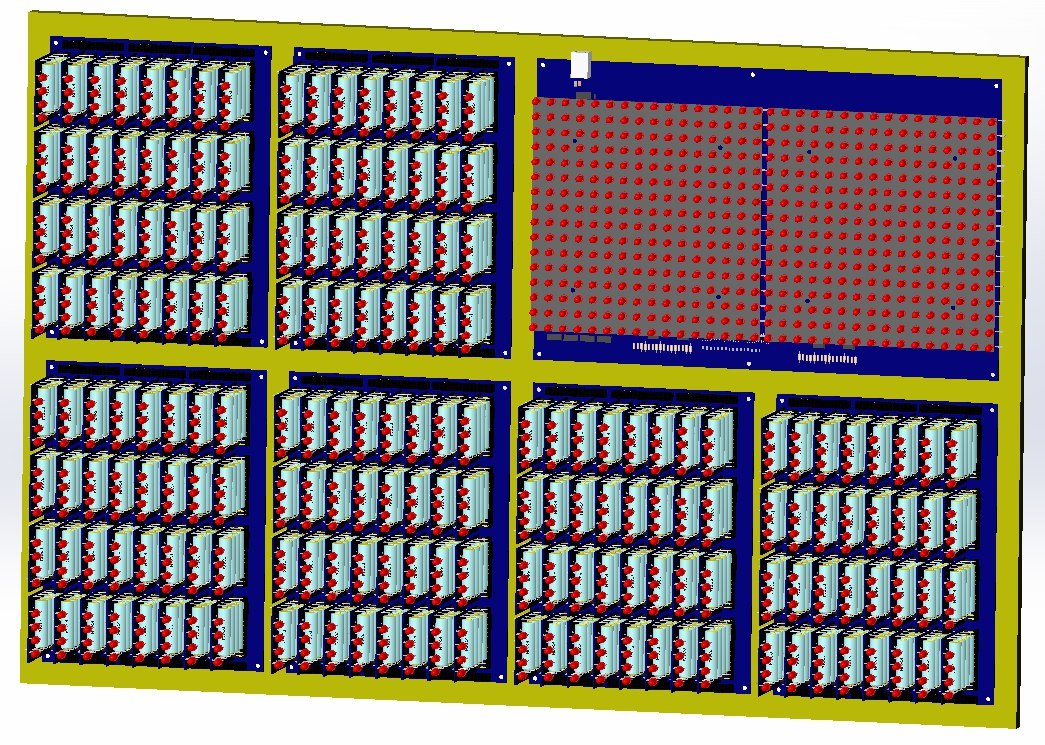

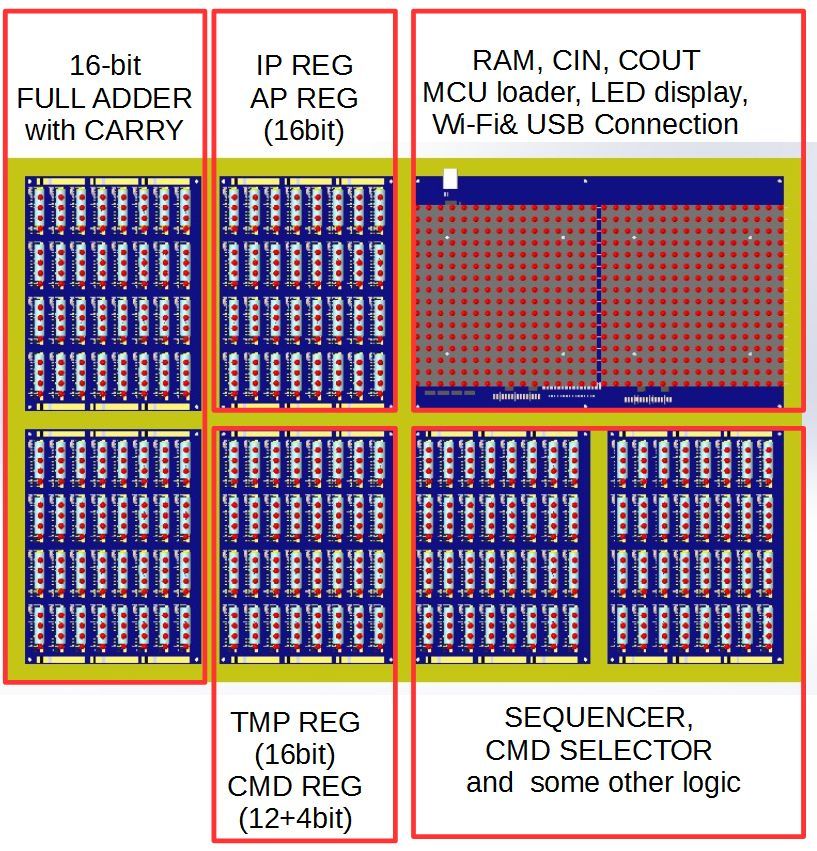

मशीन का डिज़ाइन मॉड्यूलर, ब्लॉक फ्रेम है। KDPV स्पष्ट रूप से दिखाता है कि मशीन का भरण कैसे स्थित होगा। लेकिन पहली चीजें पहले:

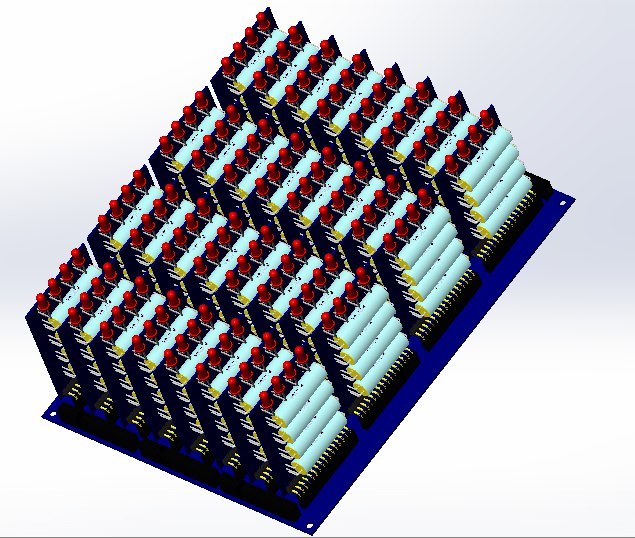

मॉड्यूल

कंप्यूटर का मूल तत्व एक 60x44 मिमी मॉड्यूल है, जिसमें 16-पिन कनेक्टर हैं, जिसमें 4 रिले, उनका हार्नेस और 4 एलइडी इंगित करने के लिए हैं:

चित्रा 10: मॉड्यूल का 3 डी मॉडल

विभिन्न प्रकार के मॉड्यूल:

- स्थानांतरण के साथ 1-बिट योजक - 16 पीसी;

- समानांतर स्थानांतरण सर्किट के लिए 5AND मॉड्यूल - 32 पीसी;

- डी-फ्लिप-फ्लॉप मॉड्यूल - प्रति रजिस्टर 64 पीसी, प्लस थोड़ा तर्क;

- मॉड्यूल 4x2AND_SW, कुंडी के आयोजन के लिए। केवल 4 समापन रिले हैं;

- 4x2AND मॉड्यूल, कुंडी के आयोजन के लिए। चेंजओवर संपर्क के साथ 4 में से 3 रिले हैं। 4 रिले पर पर्याप्त आउटपुट पिन नहीं था;

- मॉड्यूल एक डायोड है, 8 डायोड D226D। बहु-इनपुट OR व्यवस्थित करने के लिए

- यूनिवर्सल मॉड्यूल 2AND / 2OR, आपको 2AND-NOT, 2OR-NOT, 4AND, 4AND-NOT, 4OR, 4OR-NOT और कोई भी संयोजन बनाने की अनुमति देता है। स्विचिंग संपर्कों और सामान्य बिंदुओं के साथ 4 रिले के आधार पर;

चूंकि मैं, भले ही मैं नियंत्रण तर्क के ब्लॉक के साथ आया था, पहले से ही खारिज कर दिया गया है, मुझे प्रत्येक प्रकार के मॉड्यूल की सटीक संख्या नहीं पता है। मैं सड़क पर इसका पता लगाऊंगा। मॉड्यूल की अनुमानित संख्या 192 टुकड़े है।

खंड

हम एक 150x200 मिमी बोर्ड लेते हैं, इस पर 16 पिन के साथ 32 कनेक्टर्स, लेकिन साधारण नहीं, बल्कि रैप-अप के लिए और 8x4 मैट्रिक्स में उस पर हमारे मॉड्यूल स्थापित करने के लिए, इस तरह के ब्लॉक प्राप्त करना:

चित्र 11: ब्लॉक

मेरी कार में 6 ऐसे ब्लॉक होंगे - दो ब्लॉक प्रति एडिटर, दो ब्लॉक प्रति रजिस्टर और दो ब्लॉक प्रति लॉजिक। मुझे खरोंच है कुंडी के कुछ और ब्लॉकों के बारे में, लेकिन अगर वे हैं, तो वे फ्लैट और सोल्डर हैं

रैपराउंड स्थापना को चुना गया क्योंकि: सबसे पहले, प्रत्येक बेस बोर्ड की सर्किट्री, हालांकि यह पहले से जाना जाता है, बदल सकता है और त्रुटियों के अधीन है। दूसरे, सिद्धांत रूप में, पहली बार तर्क ब्लॉक को सही ढंग से अलग करना असंभव है, और यदि रजिस्टर ब्लॉक के लिए सब कुछ स्पष्ट है और आप एक सिंक्रनाइज़ेशन लाइन के साथ एक गलती, कह सकते हैं, तो आपको तर्क को एक हजार और एक बार फिर से करना होगा। यदि आप तर्क ब्लॉक के प्रत्येक घटक को धीरे-धीरे इकट्ठा करते हैं तो यह बहुत बेहतर होगा। तीसरा, एक विशुद्ध रूप से यांत्रिक कारक - इन ब्लॉकों को दो-परत बोर्ड पर अलग करना शारीरिक रूप से असंभव है :) 16-बिट टायर कई दिशाओं में विचलन करते हैं, जो बार-बार एक दूसरे को काटते हैं।

कुल में, प्रत्येक इकाई में 32 मॉड्यूल होते हैं, जिसमें कुल 128 टुकड़े होते हैं। प्रत्येक इकाई की शक्ति 5 वी 2 ए है।

कंप्यूटर

एक बड़े फ्रेम पर, 640x480 मिमी के आयाम (वास्तव में थोड़ा अधिक है, लेकिन संख्या सुंदर है) छह रिले ब्लॉक और एक मेमोरी बोर्ड हैं:

चित्रा 12: मशीन ब्लॉक का स्थान

पूरे कंप्यूटर को लकड़ी के फ्रेम में कीमती लकड़ी से बनाया गया है, जिसमें ग्लास फ्रंट और रियर है।

निर्माण

वर्तमान तिथि के बावजूद, परियोजना वास्तव में मौजूद है :-) और यह सबसे सक्रिय नहीं है, लेकिन अभी भी विनिर्माण चरण है।

रिले

मेरे पास है। बड़ी संख्या में, लेकिन समस्या यह है कि एक हजार से अधिक स्टॉक के तीन सौ हैं - 27 वोल्ट का रिले और 5-वोल्ट RES55 मेरे लिए पर्याप्त नहीं हो सकता है। मैं अंत में आपदा के पैमाने का अनुमान नहीं लगा सकता, लेकिन मुझे लगता है कि अगली बार जब मैं इस राक्षसी मशीन को इकट्ठा करूंगा तो समस्या बाहर से पुनःपूर्ति के कारण गायब हो जाएगी।

चित्र 13: रिले रिज़र्व। रिले के 800 टुकड़े - नए, सफलतापूर्वक एक पैसा के लिए Mitsa रेडियो बाजार पर कब्जा कर लिया

पुनःपूर्ति स्रोतों में से एक प्रयोगशाला बिजली आपूर्ति से डीएसी रिले बोर्ड है। ये हैं:

चित्र 14: रेडियो बाजार में खरीदी गई पीएसयू प्रकार की बिजली आपूर्ति से बोर्ड (नहीं, मैं नहीं

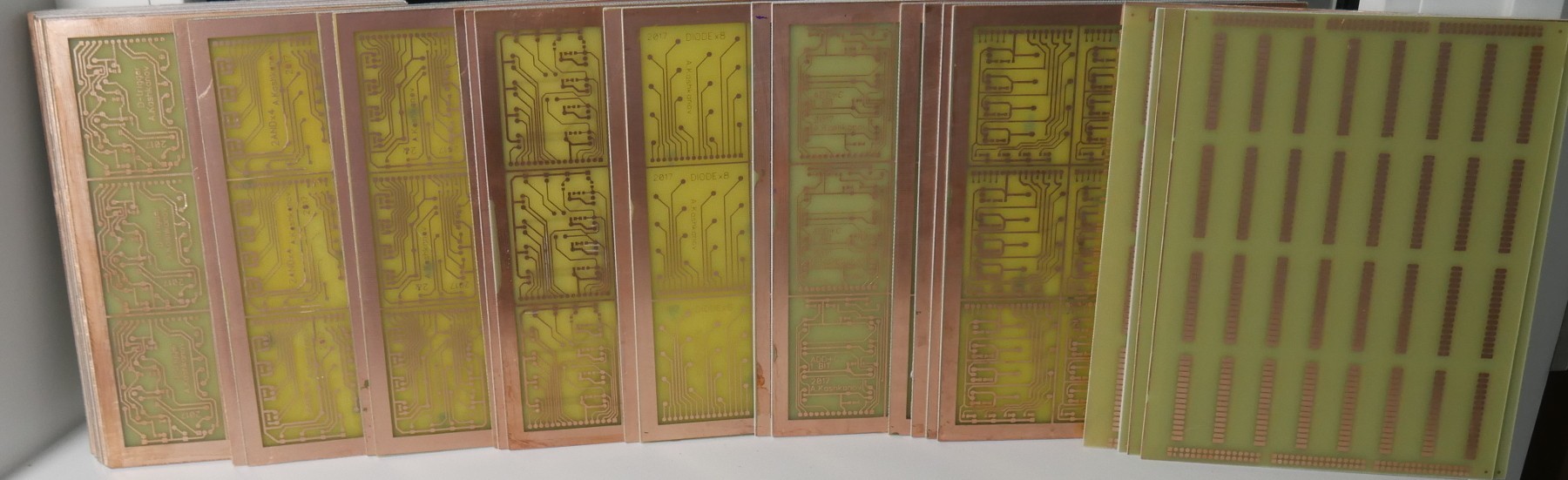

मुद्रित सर्किट बोर्ड

मैंने सभी मुद्रित सर्किट बोर्ड खुद करने का फैसला किया। मैंने चीनियों को 300 रुपये दिए और 4 महीने तक मैं फोटोजिस्ट, पारभासी, नक़्क़ाशी के साथ रिक्त स्थान को कवर करने, सोल्डर मास्क के साथ कवर करने, विकास, ड्रिलिंग और मिलिंग का काम कर रहा हूं।

चित्र 15: विभिन्न प्रकार के Etched पैनल

मैं प्लेटों में बोर्ड बनाता हूं, 200x150 मिमी प्लेट पर 9 मॉड्यूल। 30 प्लेटों को जोड़ा और मिलाप मास्क लगाने पर अटक गया। मैंने किसी भी तरह से शुरुआत नहीं की। मेरे FSR-8000 का सोल्डरिंग मास्क नीला, दो-घटक वाला है और मैंने इससे पहले ही निपटा लिया है।

200x150 मिमी की प्लेटों को संयोग से नहीं चुना गया था - हमने उन्हें रेडियो बाजार पर, एक गुप्त स्थान पर, वे कई वर्षों से बेच रहे हैं, और मेरा पूरा उपकरण इस प्रारूप के अनुरूप है।

एक शब्द में, मैंने लैमिनेटेटर का उपयोग करके फोटोरेसिस्ट (एमपीएफ-वीएससी डियाज़ोनियम से) लागू करना शुरू किया और ये केवल चमत्कार हैं। ग्लूइंग की गुणवत्ता में काफी वृद्धि हुई है।

फिर इन बोर्डों को काटने और ड्रिल करने के लिए आवश्यक होगा, जिसके लिए मेरे पास 3 डी मिलिंग कटर भी है।

चित्र 16: 3D DIY चीनी 2020CNC मिलिंग मशीन

मैंने इसे एक मामूली 175 डॉलर के लिए विशेष रूप से इलेक्ट्रॉनिक्स के लिए लिया। यह ड्रिल और मिल बोर्ड के लिए पर्याप्त है, और मैं पहले से ही 3D मशीनों के लिए बॉल्सक्रूज + रेल के सेट को देख रहा हूं। इस तरह के एक छोटे से महंगा खरीदने के लिए तैयार है, लेकिन जब यह आवश्यक होने लगता है, तो अपने आप को इकट्ठा करना - यही है।

:

, . ( ) Elf. , ( ). //TODO — , .

: . , . . Segmentation Fault!

, . — . leBrainfuck , .

, , Brainfuck . +-<>, [-] . , . , .

. 8 . :

— 10 . LLVM 0,9 . Intel Vtune Amplifier 120 10 .

. , 3 brainfuck-. 100 50 347 — .. , ! , , . .

, , ,

.

-6 , , . — , . — . - — 30-40 - 6 .

????777

संदर्भ

openSource. :

- https://github.com/radiolok/RelayComputer2 - योजनाबद्ध आरेख और पीसीबी लेआउट के साथ एक भंडार। मेमोरी बोर्ड फर्मवेयर रिपॉजिटरी का लिंक मैं बाद में जोड़ूंगा

- https://github.com/radiolok/RelayComputer2/blob/master/roadmap.md मैं इस पृष्ठ को प्रोजेक्ट रोडमैप के साथ अलग से नोट करूंगा जिस पर प्रमुख परिवर्तन दर्ज किए गए हैं।

- इस पृष्ठ पर https://hackaday.io/project/18599-brainfuck-relay-computer मैंने जो किया गया है उस पर विस्तृत रिपोर्ट प्रकाशित की। महत्वपूर्ण द्रव्यमान के सेट के अनुसार, वे जीटी पर एक लेख में बदल जाएंगे।

- https://github.com/radiolok/bfutils संकलक और एमुलेटर।