भाग Iभाग IIभाग IIIभाग ivभाग v

भाग Iभाग IIभाग IIIभाग ivभाग vहम वेरिलॉग में

लिटिल मैन कंप्यूटर डिजाइन करते हैं।

LMC के बारे में

लेख Habré पर था।

इस कंप्यूटर का ऑनलाइन सिम्युलेटर

यहाँ है ।

हम चार (N = 2) चार-बिट (M = 4) शब्दों से मिलकर एक RAM / RAM मॉड्यूल लिखते हैं। जब आप बटन पर क्लिक करते हैं तो डेटा

data_in से

adr पर

RAM में लोड हो जाता है:

module R0 #(parameter N = 2, M = 4) ( input RAM_button, // input [N-1:0] adr, // input [M-1:0] data_in, // output [M-1:0] RAM_out // ); reg [M-1:0] mem [2**N-1:0]; // mem always @(posedge RAM_button) // mem [adr] <= data_in; // data_in assign RAM_out = mem[adr]; // RAM_out endmodule

बाहरी जनरेटर के रूप में,

एक 555 सीएमओएस

टाइमर (3.3V से संचालन) कनेक्ट करें।

हम काउंटर से

555 टाइमर कनेक्ट करते हैं, काउंटर को

रैम के एड्रेस इनपुट से कनेक्ट करते हैं:

module R1 #(parameter N = 2, M = 4) ( input timer555, RAM_button, //input [N-1:0] adr, input [M-1:0] data_in, output [M-1:0] RAM_out ); reg [1:0]counter; // always @(posedge timer555) // counter <= counter + 1; // 1 wire [N-1:0] adr; assign adr = counter; // reg [M-1:0] mem [2**N-1:0]; always @(posedge RAM_button) mem [adr] <= data_in; assign RAM_out = mem[adr]; endmodule

यहां, काउंटर

काउंटर और

मेम मेमोरी का वर्णन करते समय, गैर-अवरुद्ध असाइनमेंट का उपयोग किया जाता है

<= असाइनमेंट ऑपरेटरों को

यहां marsohod.org वेबसाइट पर माना जाता

हैकाउंटर का विवरण

यहाँ marsohod.org पर

हैकाउंटर पर डाउनलोड फ़ंक्शन जोड़ें।

काउंटर_लोड कमांड के साथ

डाउनलोडिंग की

जाती है :

//input Counter_load; wire [3:0] branch_adr; // assign branch_adr = data_in; always @(posedge timer555) begin if(Counter_load) // "Counter_load" "branch_adr" counter <= branch_adr; else counter <= counter + 1; end

एक अलग मॉड्यूल में, एक 4bit रजिस्टर (बैटरी) बनाएँ:

module register4 ( input [3:0] reg_data, input reg_button, output reg [3:0] q ); always @(posedge reg_button) q <= reg_data; endmodule

Acc संचायक,

MUX2 मल्टीप्लेक्स और सामान्य सर्किट में

योग योजक जोड़ें।

योजक मेमोरी से बैटरी

Acc संख्या में संख्या में जोड़ता है।

मल्टीप्लेक्स के सिग्नल इनपुट को नंबर

data_in और

sum दिए जाते हैं।

इसके बाद,

MUX2 मल्टीप्लेक्स से संख्या को

Acc बैटरी में लोड किया जाता है:

module R2 #(parameter ADDR_WIDTH = 2, DATA_WIDTH = 4) ( input timer555, Counter_load, RAM_button, input MUX_switch, input Acc_button, input [3:0] data_in, output [3:0] Acc, output [DATA_WIDTH-1:0] RAM, output reg [1:0] counter ); wire [1:0] branch_adr; assign branch_adr = data_in[1:0]; //Counter always @(posedge timer555) begin if(Counter_load) counter <= branch_adr; else counter <= counter + 1; end wire [ADDR_WIDTH-1:0] adr; assign adr = counter; //RAM reg [DATA_WIDTH-1:0] mem [2**ADDR_WIDTH-1:0]; always @(posedge RAM_button) mem [adr] <= Acc; assign RAM = mem[adr]; //sum wire [3:0] sum; assign sum = Acc + RAM; //MUX reg [3:0] MUX2; always @* // Always @* — «» MUX2 = MUX_switch ? sum : data_in; //Accumulator register4 Acc_reg( .reg_data(MUX2), .reg_button(Acc_button), .q(Acc) ); endmodule

हमेशा @ * का अर्थ है "हमेशा।" कुछ सिंथेसाइज़र इस डिज़ाइन को नहीं समझते हैं। एक मल्टीप्लेक्सर हमेशा ऑवर @ * के बिना भी लिखा जा सकता है (यहां इसका उपयोग केवल उदाहरण के रूप में किया गया है)।

घटाव

घटाव प्रदर्शन करने के लिए,

एक अतिरिक्त कोड में एक

घटाया संख्या प्रदान करना आवश्यक है। आप पाठ्यपुस्तक "डिजिटल सर्किटरी और कंप्यूटर आर्किटेक्चर" में बाइनरी नंबर के जोड़ और घटाव के बारे में पढ़ सकते हैं (डेविड एम। हैरिस और सारा एल। हैरिस) अध्याय

1.4.6 में द्विआधारी संख्या का संकेतमुख्य मॉड्यूल में एक तत्व जोड़ें जो बैटरी में संख्या से मेमोरी में संग्रहीत संख्या को घटाता है:

wire [3:0] subtract; assign subract = Acc - RAM ;

2-इनपुट मल्टीप्लेक्स को 4-इनपुट से बदलें:

always @* MUX4 = MUX_switch[1] ? (MUX_switch[0] ? RAM : subtract) : (MUX_switch[0] ? sum : data_in);

हम आउटपुट डिवाइस को बैटरी (4bit'ny रजिस्टर) से जोड़ते हैं, हम बैटरी को 2 झंडे भी जोड़ते हैं:

1. झंडा "शून्य" एक लॉग है। तत्व 4 या नहीं। यदि

गधा की सामग्री शून्य है तो झंडा उठाया जाता है।

2. झंडा "शून्य या सकारात्मक संख्या" एक लॉग है। तत्व 4-बिट बैटरी के उच्च स्तर पर नहीं है। यदि

गधा की सामग्री शून्य से अधिक या उसके बराबर है तो झंडा उठाया जाता है।

// "" output Z_flag; assign Z_flag = ~(|Acc); // 4- - // " " output PZ_flag; assign PZ_flag = ~Acc[3];

4 या नहींयहां हमने एक बहु-इनपुट वाल्व का वर्णन किया है या ~ (! Acc) के रूप में नहीं है

वेरिलोग गेट प्रकार के एक सेट का भी समर्थन करता है।

निम्नलिखित कीवर्ड तर्क गेट्स के लिए परिभाषित किए गए हैं: और (और (), नंद (और नहीं), या (या), न ही (OR-NOT), xor (विशेष OR), xnor (विशेष OR-NOT), buf (बफर तत्व) , नहीं (निषेध, नहीं)।

वेरिलॉग में, वाल्व का उपयोग करते समय, आपको तत्व के इनपुट और आउटपुट को निर्दिष्ट करना होगा, साथ ही (वैकल्पिक रूप से) वाल्व का नाम। उदाहरण के लिए, और और वाल्वों में एक आउटपुट और दो या दो से अधिक इनपुट होने चाहिए। तो, न तो वाल्व के लिए, हमारे पास है

न तो नाम list_of_ तर्क

न तो मयूर (बाहर, in0, in1, in2, in3);

तीन टीमें जोड़ें

1.

डेटा_आउट आउटपुट

डिवाइस में बैटरी की सामग्री को लोड करना

2. पता काउंटर में लोड करना अगर झंडा “शून्य” बढ़ा हुआ है (

JMP अगर

Acc = 0)

3. पता काउंटर में लोड करना अगर झंडा "शून्य या एक सकारात्मक संख्या" उठाया जाता है (

जेएमपी अगर

Acc > = 0)

module R3 #(parameter ADDR_WIDTH = 2, DATA_WIDTH = 4) ( input timer555, RAM_button, input JMP, Z_JMP, PZ_JMP, input [1:0] MUX_switch, input Acc_button, input Output_button, input [3:0] data_in, output [3:0] Acc, output [3:0] data_out, output [DATA_WIDTH-1:0] RAM, output Z_flag, PZ_flag, output reg [1:0] counter ); wire [1:0] branch_adr; assign branch_adr = data_in[1:0]; wire Z,PZ; assign Z = Z_flag & Z_JMP; assign PZ = PZ_flag & PZ_JMP; //Counter always @(posedge timer555) begin if(JMP|Z|PZ) counter <= branch_adr; else counter <= counter + 1; end wire [ADDR_WIDTH-1:0] adr; assign adr = counter; //RAM reg [DATA_WIDTH-1:0] mem [2**ADDR_WIDTH-1:0]; always @(posedge RAM_button) mem [adr] <= Acc; assign RAM = mem[adr]; //sum wire [3:0] sum; assign sum = Acc + RAM; //subtract wire [3:0] subtract; assign subtract = Acc - RAM; //MUX reg [3:0] MUX4; always @* MUX4 = MUX_switch[1] ? (MUX_switch[0] ? RAM : subtract) : (MUX_switch[0] ? sum : data_in); register4 Acc_reg( .reg_data(MUX4), .reg_clk(Acc_button), .q(Acc) ); register4 Output_reg( .reg_data(Acc), .reg_clk(Output_button), .q(data_out) ); assign Z_flag = ~(|Acc); assign PZ_flag = ~Acc[3]; endmodule

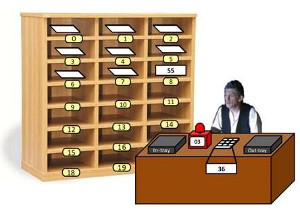

हम एक रैम / रैम और दूसरे में कमांड और एड्रेस डालते हैं।

योजना को

यहां से डाउनलोड किया जा सकता

है ।

पहले आठ अंकों में, कमांड संग्रहीत होते हैं, अंतिम चार अंकों में पता काउंटर में लोड होता है।

सामान्य तौर पर, घड़ी की क्षय के अनुसार,

MUX मल्टीप्लेक्स (

ADD ,

SUB ,

LDA कमांड्स के लिए) स्विच करने के बाद

Ass बैटरी में एक नंबर लोड किया जाना चाहिए।

इस प्रकार हमारे कंप्यूटर में निम्न कमांड सिस्टम

48x - एडीडी रैम से अस तक एक नंबर जोड़ते हैं

50x - एसयूबी एसई से रैम में संग्रहीत संख्या को घटाते हैं

80x - एसटीए पता एक्स पर बैटरी गधे से रैम तक संख्या को बचाता है

58x - LDA Ass में पता x से एक संख्या लोड करता है

04x - पता एक्स के साथ सेल में बीआर बिना शर्त संक्रमण

02x - पता x के साथ सेल में BRZ संक्रमण, अगर Ass = 0 (सशर्त संक्रमण)

01x - पता x के साथ सेल में बीआरपी संक्रमण, अगर गधा> = 0 (सशर्त संक्रमण)

40x - INP Ass में data_input से एक नंबर लोड करता है

20x - OUT संख्या को Ass से data_out पर लोड करता है

हमारे पास

एचएलटी टीम नहीं होगी।

उदाहरण के लिए साइट

http://peterhigginson.co.uk/LMC/ से अधिकतम दो नंबर खोजने के लिए एल्गोरिथ्म लें।

एल्गोरिथम इस तरह से काम करता है: हम डेटा मेमोरी में data_in से दो नंबर स्टोर करते हैं। दूसरे नंबर से पहली घटाएँ:

- यदि परिणाम नकारात्मक है, तो Ass में पहला नंबर लिखें, Ass से नंबर लिखें data_out में;

- यदि परिणाम सकारात्मक है, तो Ass में दूसरा नंबर लिखें, Ass से नंबर को data_out में लिखें।

00 INP

01 STA 11

02 INP

03 STA 12

04 SUB 11

05 BRP 08

06 LDA 11

07 BRA 09

08 LDA 12

09 OUT

हमारे कमांड सिस्टम में, यह एल्गोरिथम इस तरह दिखेगा

400

80b

400

80c

50b

018

58b

049

58c

200

काउंटर में डेटा लोड करने के लिए आवश्यक काउंटर के नियंत्रण इनपुट पर तत्व लॉजिम प्रोग्राम की ऐसी विशेषता

नहीं है , वास्तविक योजनाओं में, नियंत्रण इनपुट पर तत्व की आवश्यकता नहीं है (कम से कम मुझे ऐसे काउंटरों की जानकारी नहीं है)।

क्वार्टस II को आधिकारिक

वेबसाइट से डाउनलोड किया जा सकता है।

माई प्राइमरी जॉब फंक्शन के तहत पंजीकरण करते समय *, छात्र चुनें।

इसके बाद, आपको प्रोग्रामर के लिए ड्राइवर डाउनलोड करना होगा (usb-blaster के लिए ड्राइवर C: \ altera \ ... \ quartus \ ड्राइवर \ usb-blaster) से इंस्टॉल किया जा सकता है।

Logisim को

यहाँ डाउनलोड किया जा सकता

है ।