इस लेख में, हम SoC ARM + FPGA Xilinx Zynq 7000 पर आधारित इंटरफ़ेस यूनिट के इंटरफ़ेस कार्ड को विकसित करने में अपना अनुभव साझा करेंगे। बोर्डों को एनालॉग और डिजिटल PRI / BRI प्रारूप (ISDN, E1 / T1) में भाषण संकेतों को रिकॉर्ड करने के लिए डिज़ाइन किया गया था। अंतिम उपकरण का उपयोग नागरिक उड्डयन में बातचीत रिकॉर्ड करने के लिए किया जाएगा।

आयरन: डिवाइस हार्डवेयर प्लेटफ़ॉर्म चयन

हार्डवेयर प्लेटफ़ॉर्म का विकल्प PRI / BRI प्रोटोकॉल के समर्थन से निर्धारित किया गया था, जिसे केवल FPGA पक्ष पर लागू किया जा सकता है। माइक्रोकंट्रोलर (एमसीयू) और माइक्रोप्रोसेसर (एमपीयू) फिट नहीं थे।

कोई भी इस समस्या के दो समाधान चुन सकता है:

- माइक्रोब्लेज़ आईपी कोर संश्लेषण

- SoC Zynq-7000।

हम Zynq 7000 चिप (SoC) पर एक सिस्टम पर बसे, क्योंकि सॉफ़्टवेयर एप्लिकेशन लिखना आसान है और वर्तमान और भविष्य के कार्यों के लिए अधिक कार्यक्षमता प्रदान करता है।

कुल में, परियोजना के तहत लोहे की निम्नलिखित सूची एकत्र की गई थी:

1.Xilinx Zynq 7020 (

मार्स-जेडएक्स 3 और

मार्स ईबी 1 )

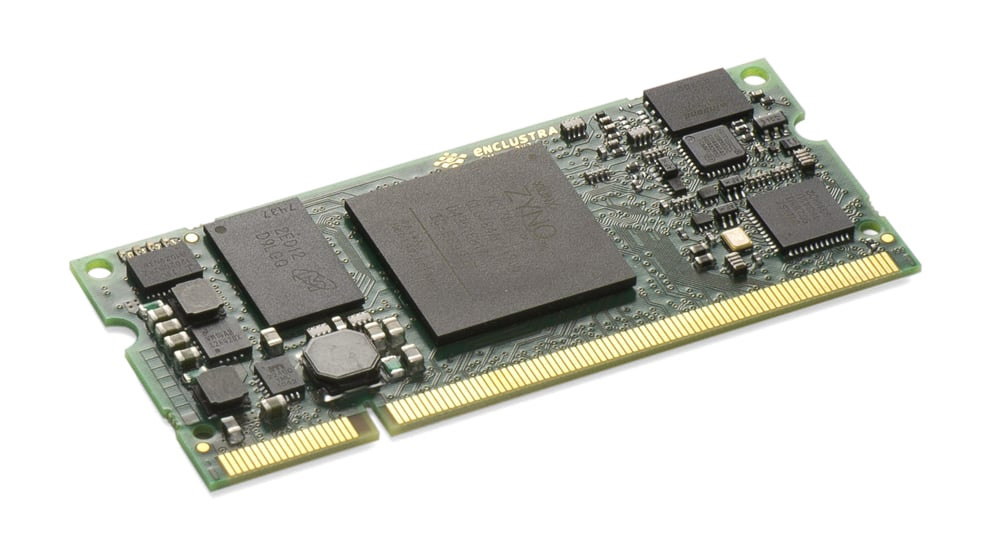

एंक्लस्ट्रा मार्स जेडएक्स 3 एसओएम

एंक्लस्ट्रा मार्स जेडएक्स 3 एसओएम एंक्लस्ट्रा मार्स EB1 बेसबोर्ड2. TI TLV320AIC34

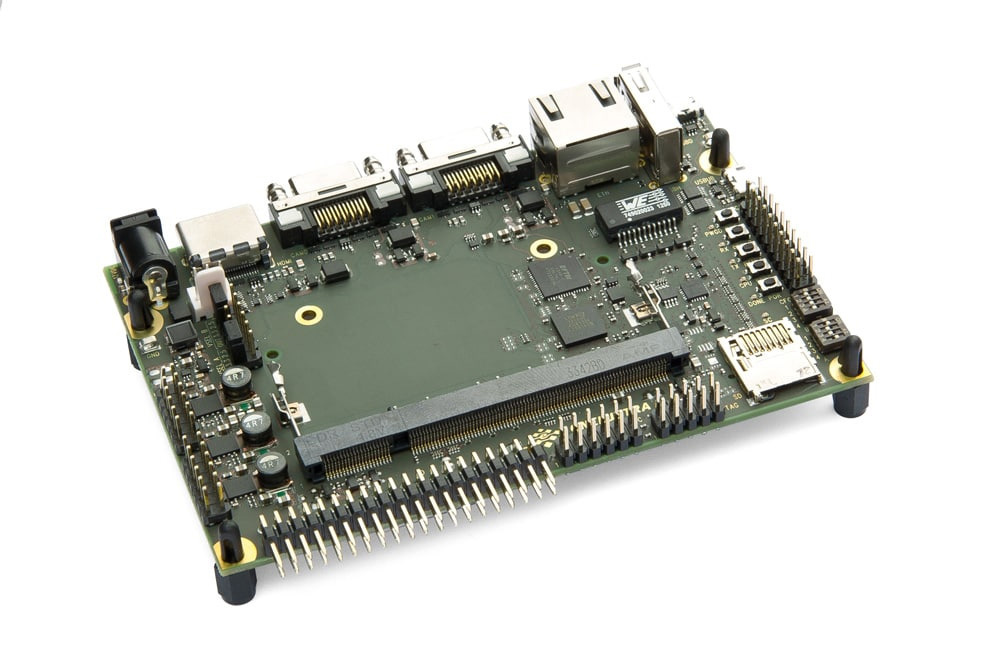

एंक्लस्ट्रा मार्स EB1 बेसबोर्ड2. TI TLV320AIC34 (

tlv320aic34evm-k और USB मदरबोर्ड)।

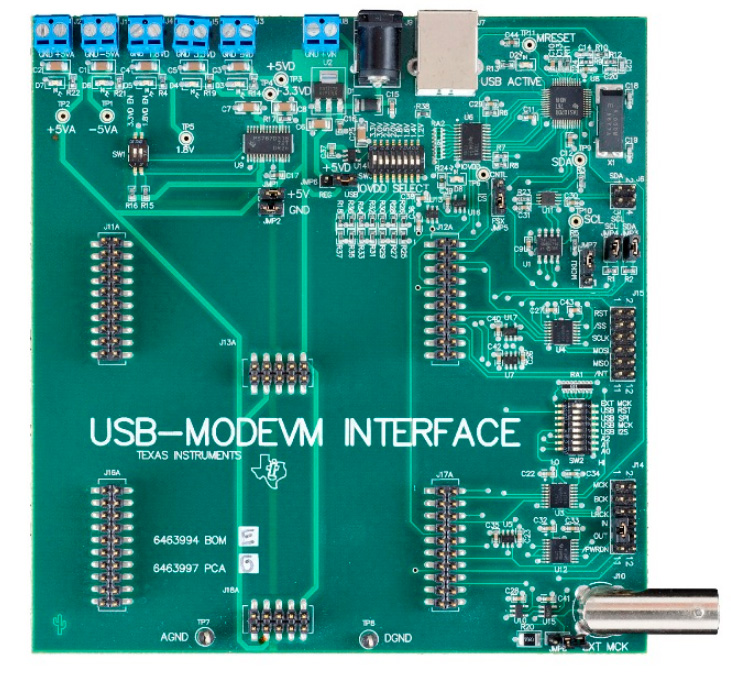

Tlv320aic34 के लिए डिबग बोर्ड (tlv320aic34evm-k)

Tlv320aic34 के लिए डिबग बोर्ड (tlv320aic34evm-k) Tlv320aic34evm-k के लिए USB-MODEVM विस्तार बोर्ड3. IDT82P2288 - PRI, XHFC-4SU - BRI microcircuits,

Tlv320aic34evm-k के लिए USB-MODEVM विस्तार बोर्ड3. IDT82P2288 - PRI, XHFC-4SU - BRI microcircuits, कोई डीबगिंग किट नहीं थे, इसलिए हमने केवल परीक्षण के लिए एक आईपी कोर के रूप में नींव रखी, और प्रोटोटाइप के बोर्ड बनाने के बाद आग की बपतिस्मा प्रक्रिया में सही हुआ।

Xilinx Zynq 7000 चिप पर सिस्टम के साथ काम करें

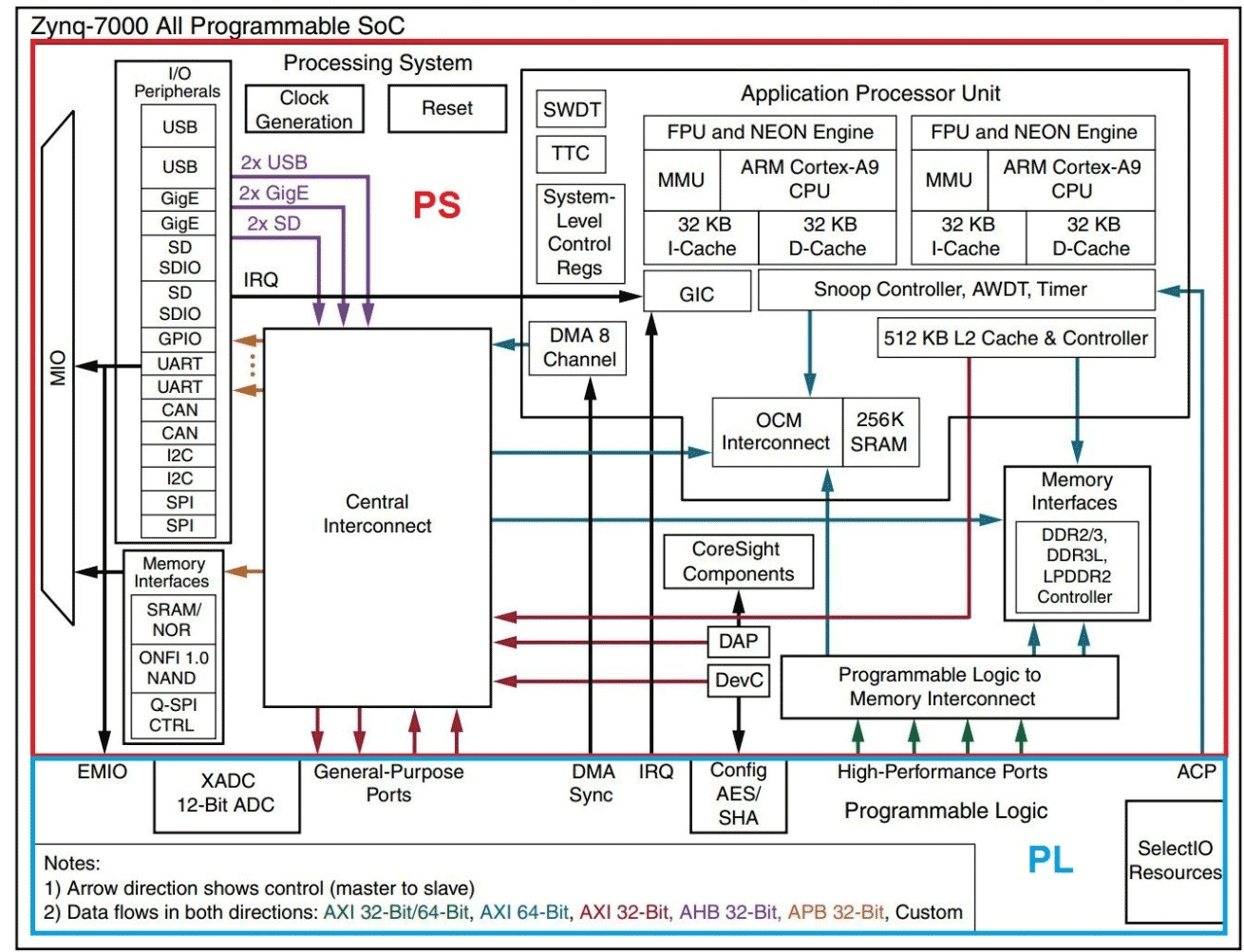

SoC Xilinx Zynq 7000 की आंतरिक संरचना

SoC Xilinx Zynq 7000 की आंतरिक संरचना Xilinx Zynq के लिए बूट फाइलें बनाने के लिए कदम

Xilinx Zynq के लिए बूट फाइलें बनाने के लिए कदमZynq के लिए फ्लैशिंग / डाउनलोडिंग निष्पादन एमपीयू के लिए सामान्य डाउनलोड से अलग है। कॉर्टेक्स-ए प्रोसेसर के साथ सामान्य कार्य यू-बूट, कर्नेल लाइनक्स, रूटफ़्स लोड कर रहा है। और Zynq पर, बिटस्ट्रीम दिखाई देता है, FPGAs के लिए फर्मवेयर फ़ाइल। बिटस्ट्रीम में FPGA पर हार्डवेयर ब्लॉक और प्रोसेसर के साथ आंतरिक संचार का विवरण होता है। यह फ़ाइल सिस्टम स्टार्टअप पर भरी हुई है। इसके अलावा लिनक्स की ओर एक तंत्र है जो आपको ऑपरेशन के दौरान पीएल भाग को तुरंत फ्लैश करने की अनुमति देता है, इस तरह के डिवाइस को 2018.1 के

बाद से xdevcfg (

ZYNQ FPGA प्रबंधक ) कहा जाता है।

PRI / BRI इंटरफेस

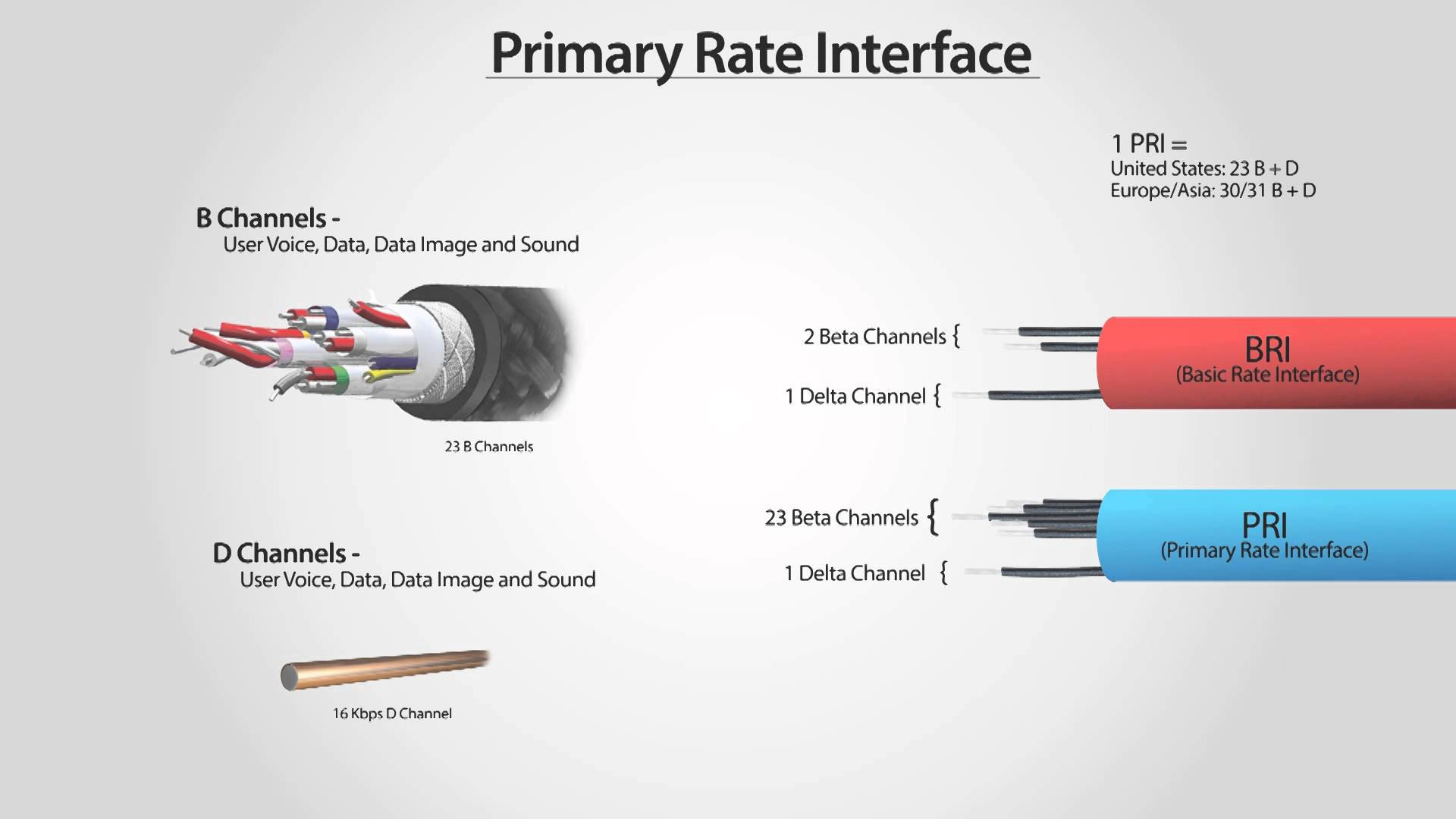

डिजिटल नेटवर्क PRI / BRI की विशेषताएं

डिजिटल नेटवर्क PRI / BRI की विशेषताएंप्राथमिक दर इंटरफ़ेस (PRI) एक मानक ISDN नेटवर्क इंटरफ़ेस है जो ISDN स्टेशनों को ब्रॉडबैंड ट्रंक से जोड़ने के अनुशासन को परिभाषित करता है जो स्थानीय और केंद्रीय एक्सचेंजों या नेटवर्क स्विच को जोड़ता है।

पीआरआई के लिए प्रेषित फ्रेम का प्रकार

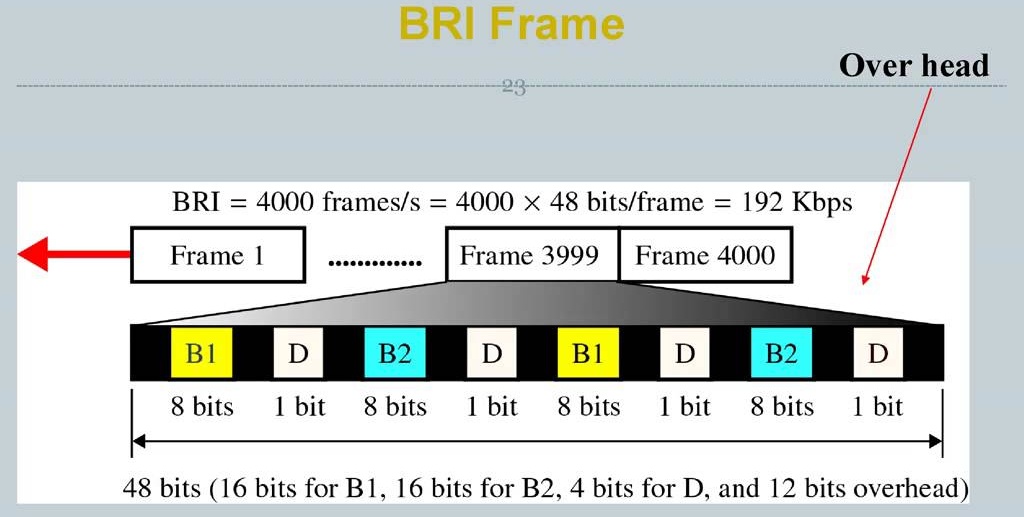

पीआरआई के लिए प्रेषित फ्रेम का प्रकार BRI के लिए संचरित फ्रेम का दृश्य

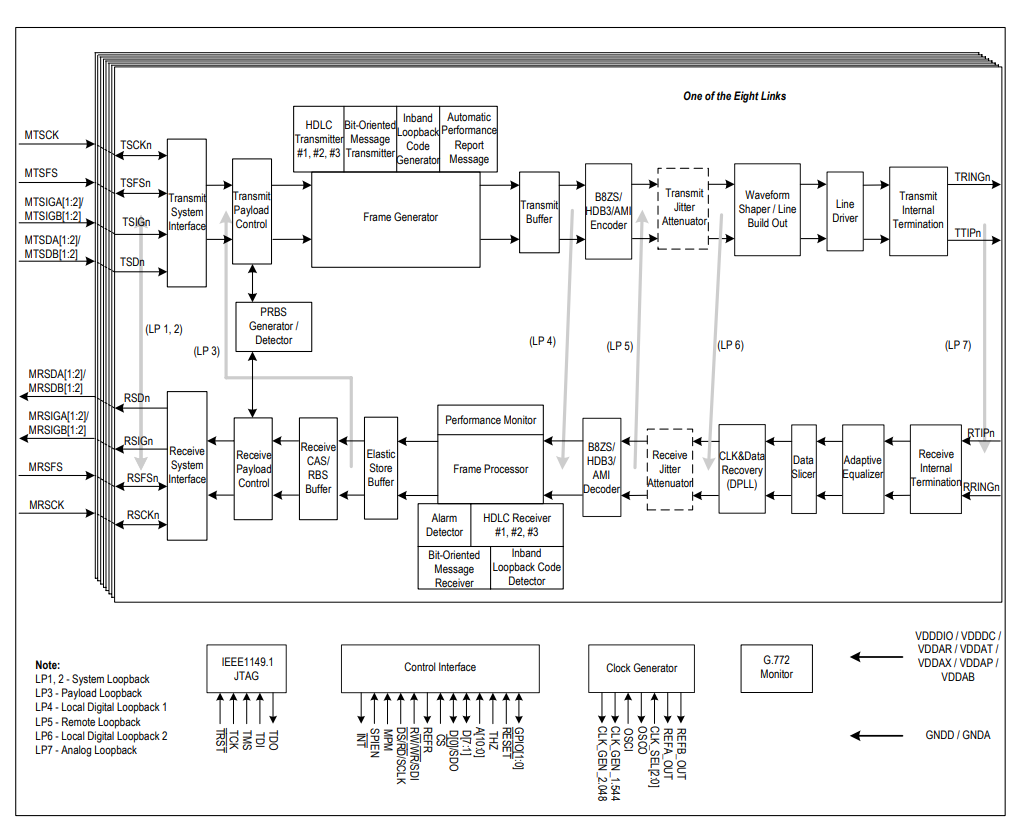

BRI के लिए संचरित फ्रेम का दृश्य PRI भौतिकी की आंतरिक संरचना - IDT82P2288

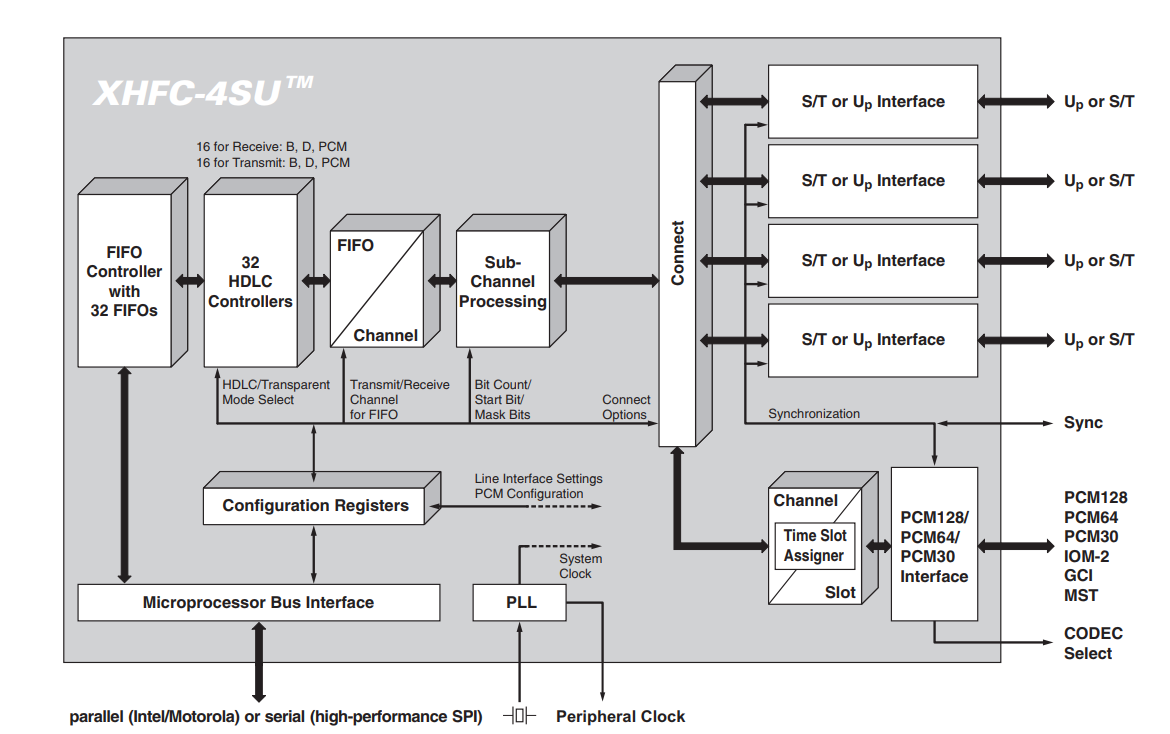

PRI भौतिकी की आंतरिक संरचना - IDT82P2288 BRI भौतिकी की आंतरिक संरचना - XHFC-4SU

BRI भौतिकी की आंतरिक संरचना - XHFC-4SUऑडियो कोडेक TLV320AIC34

पोर्टेबल ऑडियो और टेलीफोनी के लिए चार-चैनल लो-पावर

TLV320AIC34 ऑडियो कोडेक एनालॉग टेलीफोनी में उपयोग के लिए एक अच्छा समाधान है।

Tlv320aic34 A-part, ऑडियो कोडेक में दो ऐसे फंक्शन ब्लॉक होते हैं

Tlv320aic34 A-part, ऑडियो कोडेक में दो ऐसे फंक्शन ब्लॉक होते हैंडेटा को I2S इंटरफ़ेस, साथ ही डीएसपी, पीसीएम, टीडीएम के माध्यम से प्रेषित किया जा सकता है।

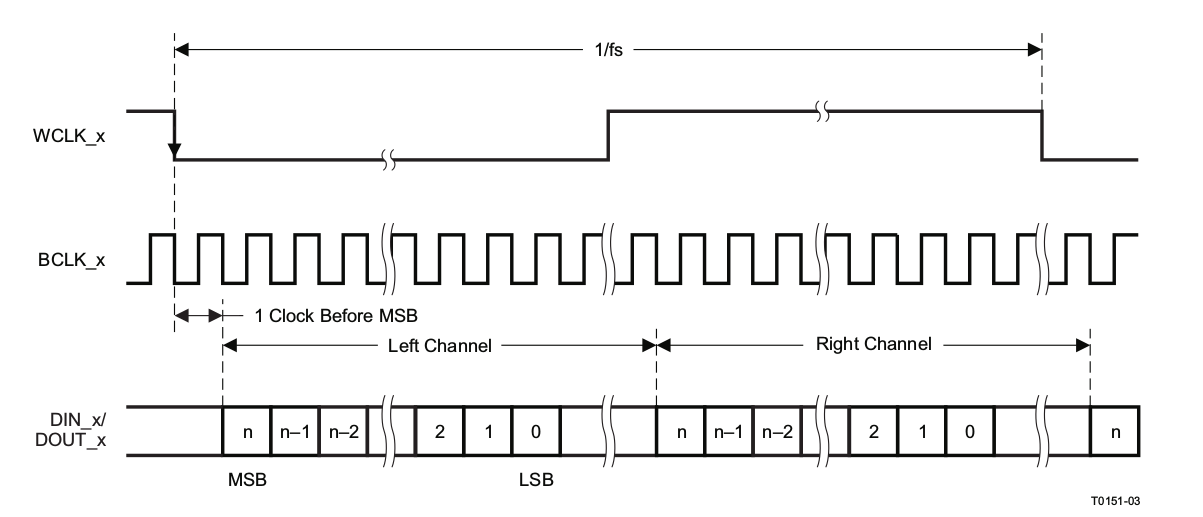

I2S एक सीरियल बस इंटरफ़ेस मानक है, इसका उपयोग डिजिटल ऑडियो उपकरणों को जोड़ने के लिए किया जाता है और विद्युत रूप से 3 कंडक्टरों का प्रतिनिधित्व करता है जो एक सक्रिय डिवाइस से निष्क्रिय एक तक जाते हैं, साथ ही 4 सिग्नल जो उनके अनुरूप हैं:

- बिट क्लॉक (BCLK)।

- घड़ी संकेत फ्रेम (शब्दों के अनुसार) तुल्यकालन (WCLK)।

- डेटा सिग्नल जो 2 टाइम-विभाजित चैनल (डीआईएन / डीओयूटी) प्रसारित या प्राप्त कर सकता है।

डेटा प्राप्त करने और प्रसारित करने के लिए चैनल विभाजित हैं, अर्थात डेटा प्राप्त करने के लिए एक अलग चैनल और ट्रांसमिशन के लिए एक चैनल है। नियंत्रक ऑडियो कोडेक द्वारा प्रेषित डेटा प्राप्त करता है, लेकिन रिवर्स भी संभव है।

I2S फ्रेम, I2S इंटरफ़ेस की विशेषताएं

I2S फ्रेम, I2S इंटरफ़ेस की विशेषताएंसभी हार्डवेयर घटकों का चयन करने के बाद, हमने ऑडियो कोडेक और Xilinx Zynq 7020 को जोड़ने की समस्या को हल किया।

I2S कोर के लिए खोजें

Xilinx Zynq 7020 में ऑडियो स्ट्रीम के साथ काम करते समय संभवतः सबसे कठिन क्षण यह था कि इस प्रणाली के प्रोसेसर भाग पर मूल रूप से चिप पर I2S बस नहीं है, इसलिए मुझे I2S कोर ढूंढना पड़ा। यह कार्य इस शर्त से जटिल था कि आईपी कोर मुक्त होना चाहिए।

हम कई आईपी कोर पर बस गए। नंगे धातु कोर I2S

Digilent के लिए मिला। हमें

opencores पर कई आईपी कोर मिले और, शायद, हमारे लिए सबसे अच्छा विकल्प

एनालॉग डिवाइसेस आईपी कोर है। वे अपने उपकरणों के लिए FPGA / FPGA इंटरैक्शन के लिए ip-cores का उत्पादन करते हैं।

हम

AXI-I2S-ADI नामक आईपी-कोर में रुचि रखते हैं

। एनालॉग डिवाइसेज खुद अपने हार्डवेयर प्लेटफॉर्म के लिए इन आईपी कोर को बढ़ावा दे रहे हैं।

उपयोग मामलों की कुल सूची:

- नंगे धातु - I2S के लिए आईपी कोर (डिजीलेंट ZYBO ऑडियो)

- opencores.org

- AXI-I2S-ADI नियंत्रक (एनालॉग डिवाइस)

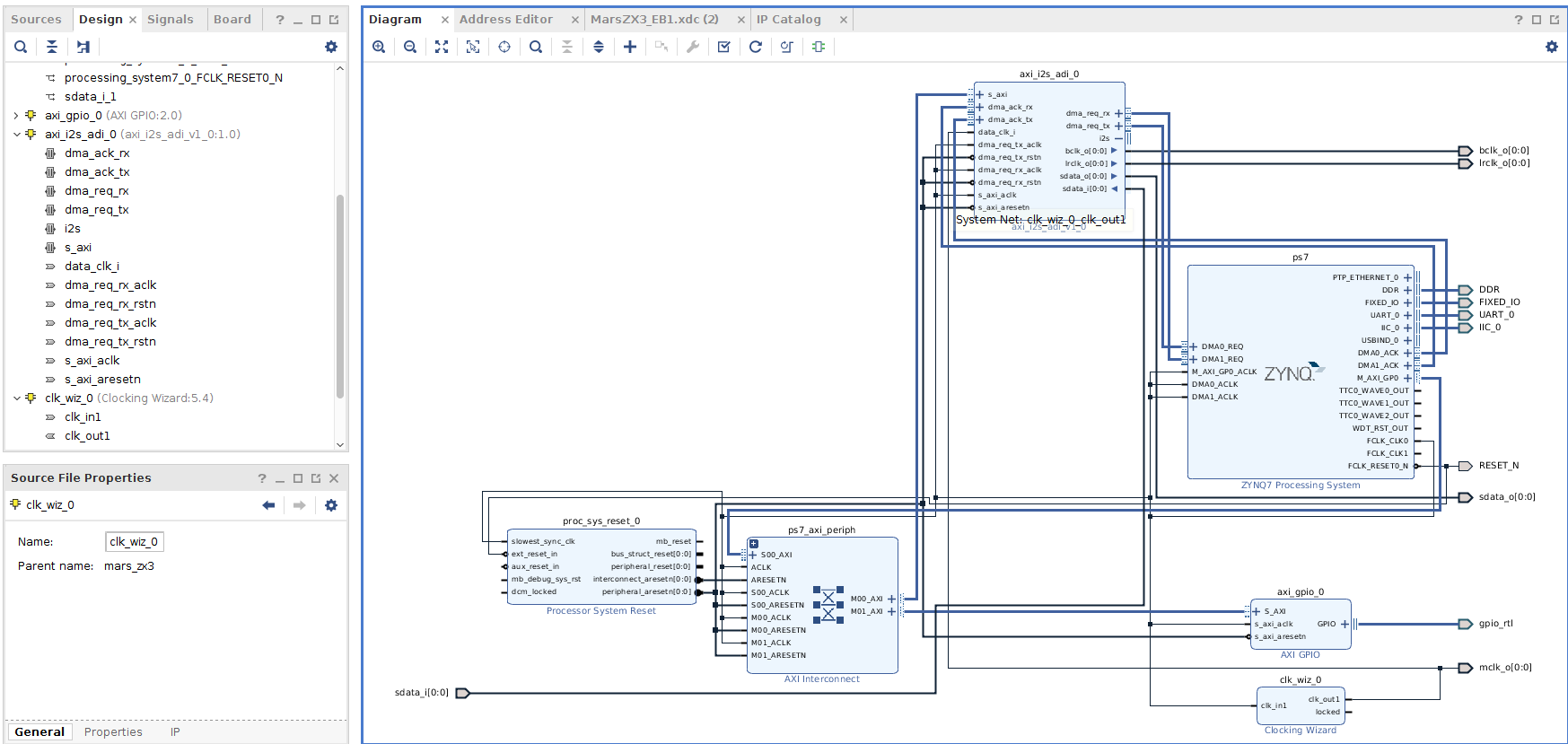

AXI-I2S-ADI IP कोर

आईपी कोर खुद इस तरह दिखता है: इसमें लाइनें हैं bclk, wclk, din, dout। यह DMA Xilinx Zynq 7000 से जुड़ता है, हमारे उदाहरण में, DMA PS भाग का उपयोग किया जाता है। सभी डेटा विनिमय डीएमए के माध्यम से होता है। DMA एक स्टैंडअलोन इकाई या PS SoC का अभिन्न अंग हो सकता है।

इस आईपी-कर्नेल को कॉन्फ़िगर करते समय, यह महत्वपूर्ण है कि mlk मास्टर आवृत्ति को tlv320aic34 में सबमिट करना न भूलें, tlv320aic34 के लिए डीबगिंग किट का उपयोग करते समय एक विकल्प के रूप में - एक बाहरी मास्टर आवृत्ति सबमिट करें।

कनेक्टेड ऐक्सी-आई 2 एस-एडी के साथ फंक्शन ब्लॉक

कनेक्टेड ऐक्सी-आई 2 एस-एडी के साथ फंक्शन ब्लॉककॉन्फ़िगरेशन प्रक्रिया के बाद, कार्य लिनक्स ओएस में कार्यक्षमता लॉन्च करना था।

Tlv320aic34 के लिए डिवाइस ट्री लॉन्च और कॉन्फ़िगर करें

I2c को कॉन्फ़िगर करना (tlv320aic34 इस इंटरफ़ेस पर कॉन्फ़िगर किया गया है):

i2c0: i2c@e0004000 { ... tlv320aic3x: tlv320aic3x@18 { #sound-dai-cells = <0>; compatible = "ti,tlv320aic3x"; reg = <0x18>; gpio-reset = <&axi_gpio_0 0 0>; ai3x-gpio-func = <&axi_gpio_0 1 0>, /* AIC3X_GPIO1_FUNC_DISABLED */ <&axi_gpio_0 2 0>; /* AIC3X_GPIO2_FUNC_DIGITAL_MIC_INPUT */ AVDD-supply = <&vmmc2>; DRVDD-supply = <&vmmc2>; IOVDD-supply = <&vmmc2>; DVDD-supply = <&vmmc2>; ai3x-micbias-vg = <1>; }; ... };

I2s को कॉन्फ़िगर करना (ऑडियो डेटा इस इंटरफ़ेस के माध्यम से प्रेषित होता है):

i2s_clk: i2s_clk { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <11289600>; clock-output-names = "i2s_clk"; }; axi_i2s_adi_0: axi_i2s_adi@43C00000 { compatible = "adi,axi-i2s-1.00.a"; reg = <0x43C00000 0x1000>; xlnx,bclk-pol = <0x0>; xlnx,dma-type = <0x1>; xlnx,has-rx = <0x1>; xlnx,has-tx = <0x1>; xlnx,lrclk-pol = <0x0>; xlnx,num-ch = <0x1>; xlnx,s-axi-min-size = <0x000001FF>; xlnx,slot-width = <0x18>; }; &axi_i2s_adi_0 { #sound-dai-cells = <0>; compatible = "adi,axi-i2s-1.00.a"; clocks = <&clkc 15>, <&i2s_clk>; clock-names = "axi", "ref"; dmas = <&dmac_s 0 &dmac_s 1>; dma-names = "tx", "rx"; };

डिवाइस ट्री (साउंड कार्ड) में साउंड कार्ड सेट करना:

sound { compatible = "simple-audio-card"; simple-audio-card,name = "TLV320AIC34"; simple-audio-card,format = "i2s"; simple-audio-card,bitclock-master = <&dailink0_master>; simple-audio-card,frame-master = <&dailink0_master>; simple-audio-card,widgets = ... simple-audio-card,routing = ... dailink0_master: simple-audio-card,cpu { clocks = <&i2s_clk>; sound-dai = <&axi_i2s_adi_0>; }; simple-audio-card,codec { clocks = <&i2s_clk>; sound-dai = <&tlv320aic3x>; }; }; };

लिनक्स में डिवाइस ट्री में कोडेक को कॉन्फ़िगर करने और कॉन्फ़िगर करने के लिए सभी जोड़तोड़ के बाद, प्रतिष्ठित ऑडियो कार्ड दिखाई दिया और हम संगीत सुनने में सक्षम थे (हमारा पहला संगीत ट्रैक हाईवे टू हेल, एसी / डीसी) था।

यहां हमें इसके लिए क्या करना है:

- आवश्यक आवृत्ति का उपयोग करके उत्पन्न clk_wiz (क्लॉकिंग विज़ार्ड)

- Tlv320aic34 के लिए सही रूप से कॉन्फ़िगर किया गया DTS

- Tlv320aic3x ड्राइवर के लिए जोड़ा गया समर्थन

- ऑडियो स्ट्रीम बनाने के लिए ऑडियो पैकेज को जोड़ा गया (ऑडियो, प्लेप्ले आदि)

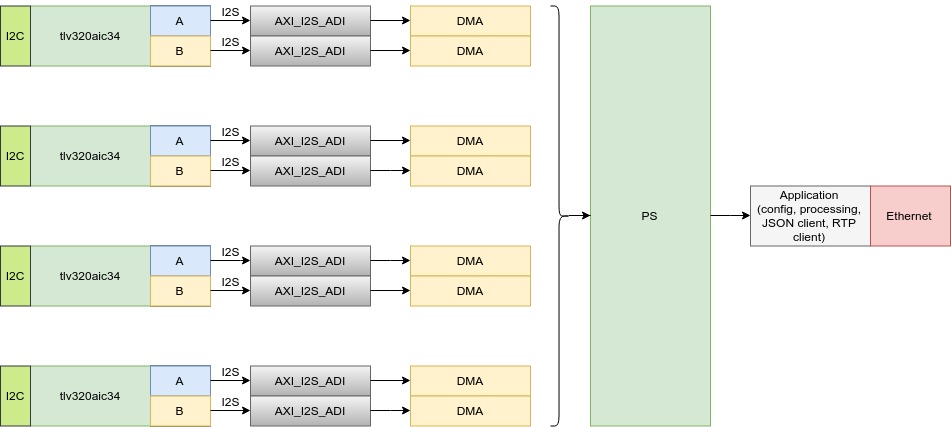

अंत डिवाइस को विकसित करने की प्रक्रिया में, हमें 4 tlv320aic34 microcircuits को जोड़ने के कार्य का सामना करना पड़ा। ऊपर वर्णित tlv320aic34 चिप में ऑडियो स्ट्रीम के साथ काम करने के लिए 2 ब्लॉक हैं, प्रत्येक ब्लॉक में ऑडियो मापदंडों को कॉन्फ़िगर करने और स्थापित करने के लिए अपनी i2c लाइन है। एक ब्लॉक में क्रमशः चार पते हो सकते हैं, चार tlv320aic34 microcircuits को एक i2c इंटरफ़ेस से जोड़ना असंभव है, आपको दो i2c इंटरफेस (8 स्वतंत्र ऑडियो ब्लॉक) का उपयोग करने की आवश्यकता है। प्रत्येक ब्लॉक के लिए, यदि आप व्यक्तिगत रूप से mclk, blck, wclk, din / dout शुरू करते हैं, तो आपको कुल मिलाकर 40 सिग्नल लाइनें जोड़ने की आवश्यकता होती है, जो हमने चुने गए सोम मॉड्यूल के लिए सर्किट के दृष्टिकोण से असंभव और तर्कहीन है, क्योंकि इन संकेतों के अलावा, आपको कई अन्य लाइनें और कनेक्ट करना था इंटरफेस।

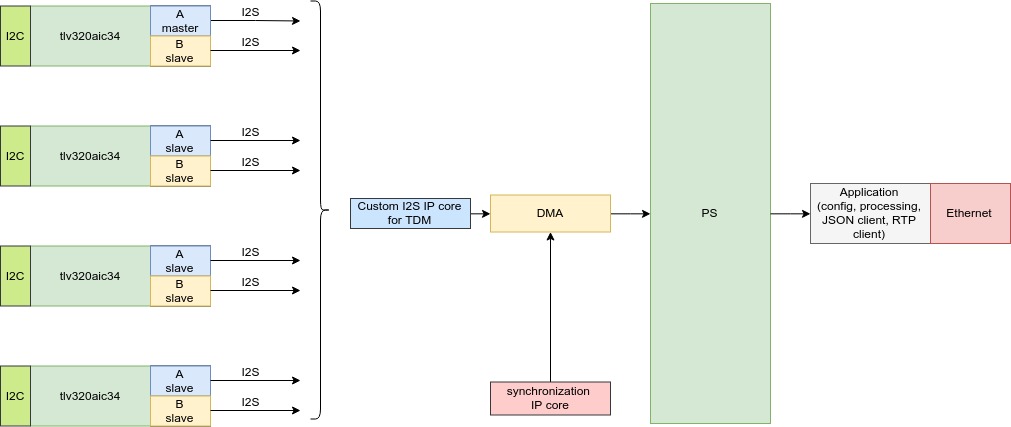

नतीजतन, हमने ऑडियो कार्ड को

टीडीएम मोड में बदलने का फैसला किया, जिसमें सभी mclk, bclk, din, dout लाइनें संयुक्त हैं, जो संचार लाइनों की कुल संख्या को कम करता है। इस निर्णय ने axi-i2s-adi के संचालन को प्रभावित किया, इस तथ्य के कारण कि आईपी कोर ने स्वयं मास्टर मोड में काम किया। इसके अलावा, इस बदलाव ने हमें टीडीएम-मोड में हमारे आईपी-कोर का उपयोग करने की अनुमति नहीं दी, और एक मजबूत-इच्छा वाले निर्णय को हमें चयनित आईपी-कोर के उपयोग को छोड़ना पड़ा। मुझे i2s ट्रैफ़िक को सुनने और इसे dma को भेजने के लिए एक आईपी कर्नेल लिखना था, इस समाधान ने हमें डेटा प्राप्त करने के लिए एक सामान्य इंटरफ़ेस बनाने की अनुमति दी जो रिकॉर्डिंग कॉल (एनालॉग और डिजिटल कार्ड) के लिए कार्ड के प्रकार पर निर्भर नहीं होगा।

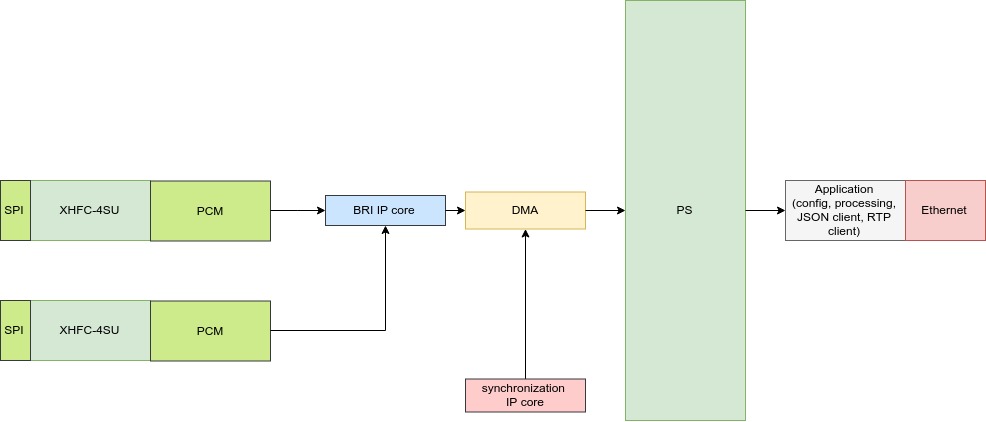

I2s इंटरफ़ेस के माध्यम से ऑडियो स्ट्रीम और इसके प्रसंस्करण को प्राप्त करने के लिए प्रारंभिक वास्तुकला:

I2s इंटरफ़ेस के माध्यम से ऑडियो स्ट्रीम और इसके प्रसंस्करण को प्राप्त करने के लिए अंतिम वास्तुकला:

PRI स्ट्रीम प्राप्त करने का आर्किटेक्चर और इसकी प्रोसेसिंग:

BRI स्ट्रीम रिसेप्शन और प्रोसेसिंग का आर्किटेक्चर:

आसी दमा

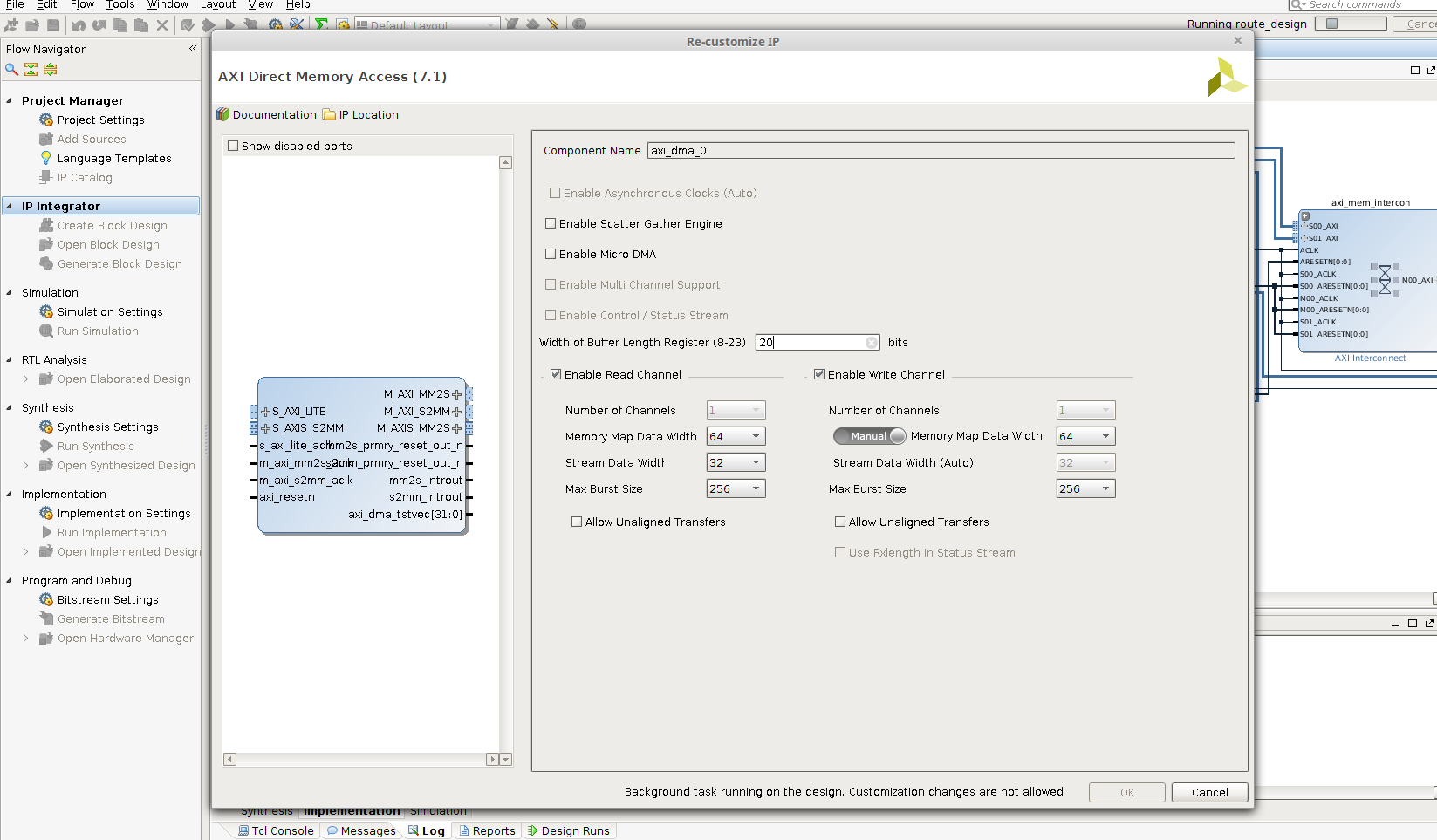

यह dma के लिए डेटा सिंक्रोनाइज़ेशन सिस्टम का एक महत्वपूर्ण तत्व है।

Xilinx Vivado में AXI DMA कॉन्फ़िगरेशन विंडो

Xilinx Vivado में AXI DMA कॉन्फ़िगरेशन विंडोप्रिंटस्क्रीन पर, AXI DMA ब्लॉक को ही प्रस्तुत किया जाता है। इसके कई मापदंड हैं। आप बस को कॉन्फ़िगर कर सकते हैं कि कितना डेटा स्थानांतरित करना है। डेटा को संरेखित या किसी भी प्रारूप में किया जा सकता है। अक्षीय डीएमए के साथ संचालन और बातचीत का विस्तृत विवरण

तकनीकी दस्तावेज में वर्णित

किया गया है (संस्करण से संस्करण तक विवरण में अशुद्धियों का एक जोड़ और सुधार है, साथ ही साथ आईपी-कर्नेल का शोधन)।

AXI DMA, AXI DMA परीक्षण विकल्पों के माध्यम से डेटा स्थानांतरण की जाँच करें

ड्राइवर को विकसित करते समय, हमने खुले स्रोत को खोजने और इसे अपने कार्य में अनुकूलित करने का निर्णय लिया। नतीजतन, हमने

गिटब-प्रोजेक्ट एज्डमा (

सजा , आसान

डमा के रूप में पढ़ा) के स्रोतों को चुना।

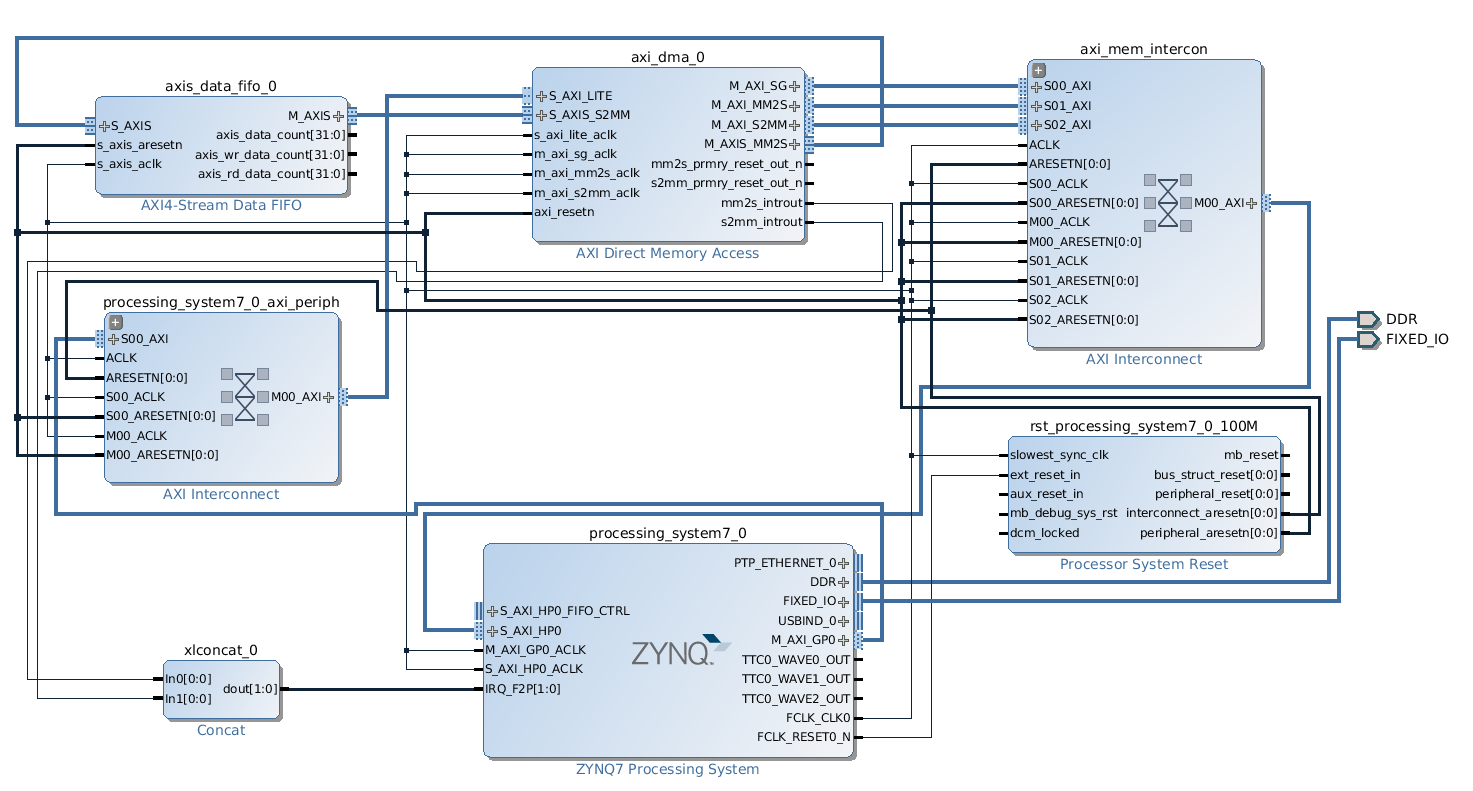

अगला कदम एक परीक्षण चालक का विकास है, यह उस क्षण की प्रत्याशा में एक प्रारंभिक चरण था जब एफपीजीए विकास विभाग से तैयार कार्यक्षमता के साथ एक आईपी कोर हमारे पास आया (वर्णित प्रोग्रामर द्वारा वर्णित विकास प्रक्रिया का गठन किया गया था)। इस क्षण से पहले हमने AXI DMA, AXI DATA FIFO को लेने का फैसला किया और भविष्य की त्रुटियों के खिलाफ सुनिश्चित करने के लिए एक लूपबैक बनाया। हमने डेटा भेजने और प्राप्त करने का काम टाल दिया, इसलिए हमने अपने काम के परिणाम और अपने ड्राइवर के प्रदर्शन की जाँच की। हमने कार्यक्षमता को थोड़ा अनुकूलित किया, इसे इंटरेक्शन इंटरफेस पर हमारी इच्छाओं के लिए लाया और एक बार फिर से चालक और चयनित इंटरैक्शन सिद्धांत की संचालन क्षमता की जांच की।

लुक-बैक ब्लॉक डिज़ाइन, AXI DMA का परीक्षण करने का पहला तरीका

लुक-बैक ब्लॉक डिज़ाइन, AXI DMA का परीक्षण करने का पहला तरीकाडिवाइस ट्री में डीएमए और एज़्डमा के विवरण का एक उदाहरण:

/ { amba_pl: amba_pl { #address-cells = <1>; #size-cells = <1>; compatible = "simple-bus"; ranges ; axi_dma_1: axi_dma { #dma-cells = <1>; compatible = "xlnx,axi-dma-1.00.a"; reg = <0x40400000 0x10000>; clock-names = "s_axi_lite_aclk", "m_axi_sg_aclk", "m_axi_mm2s_aclk", "m_axi_s2mm_aclk"; clocks = <&clkc 15>, <&clkc 15>, <&clkc 15>, <&clkc 15>; interrupt-parent = <&intc>; interrupts = <0 29 4 0 30 4>; xlnx,addrwidth = <0x20>; xlnx,include-sg; dma-channel@40400000 { compatible = "xlnx,axi-dma-mm2s-channel"; dma-channels = <0x1>; interrupts = <0 29 4>; xlnx,datawidth = <0x20>; xlnx,device-id = <0x0>; xlnx,include-dre ; }; dma-channel@40400030 { compatible = "xlnx,axi-dma-s2mm-channel"; dma-channels = <0x1>; interrupts = <0 30 4>; xlnx,datawidth = <0x20>; xlnx,device-id = <0x0>; xlnx,include-dre ; }; }; ezdma0 { compatible = "ezdma"; dmas = <&axi_dma_1 0 &axi_dma_1 1>; dma-names = "loop_tx", "loop_rx"; // used when obtaining reference to above DMA core using dma_request_slave_channel() ezdma,dirs = <2 1>; // direction of DMA channel: 1 = RX (dev->cpu), 2 = TX (cpu->dev) }; ... }; };

आप

डिवाइस ट्री जेनरेटर टूल का उपयोग करके आसानी से dts / dtsi फाइल तैयार कर सकते हैं।

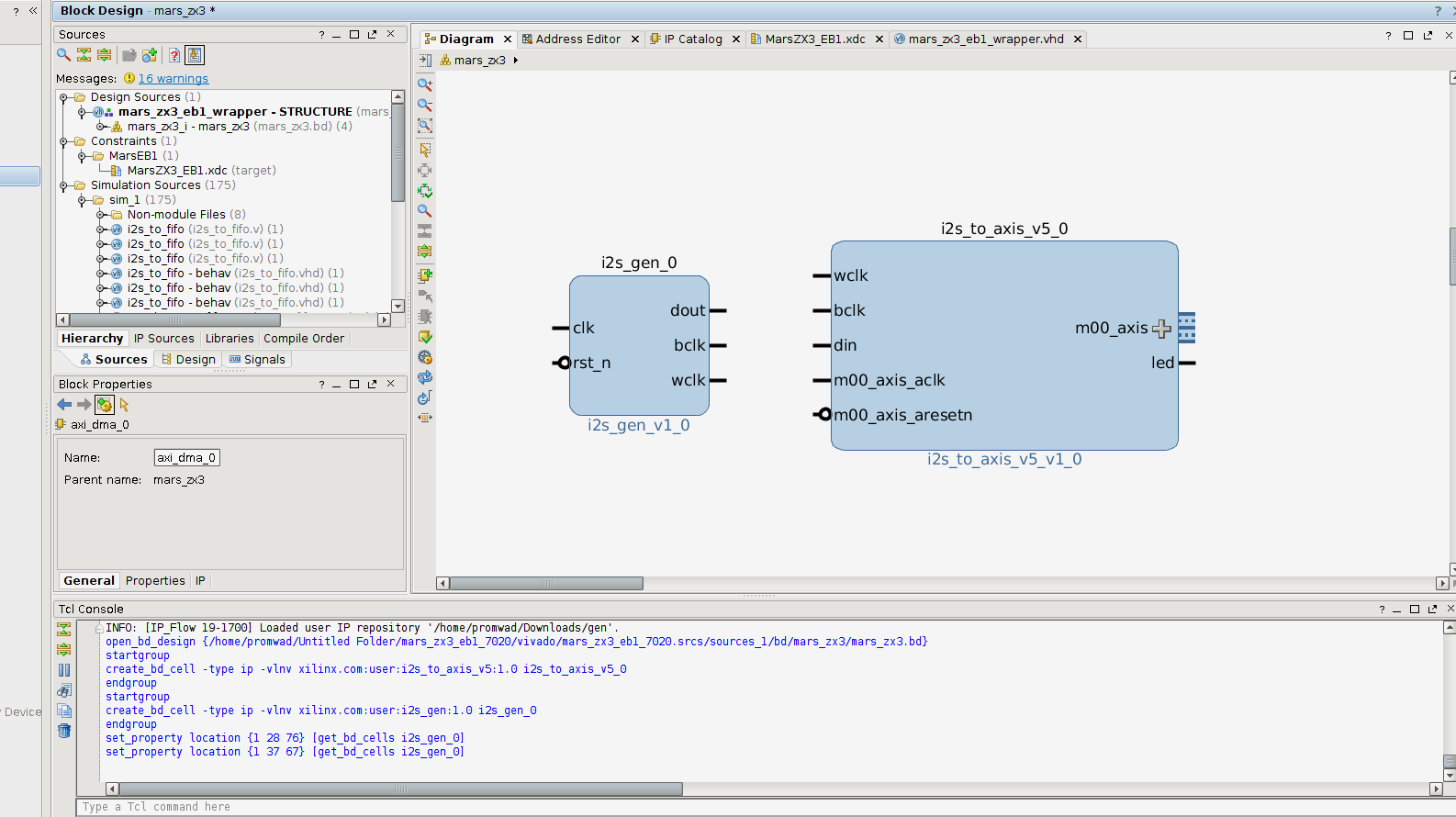

हमारी विकास प्रक्रिया का दूसरा चरण चालक के प्रदर्शन की जांच के लिए एक परीक्षण आईपी-कर्नेल का निर्माण है, केवल इस बार डेटा सार्थक होगा, AXIS_DMA के माध्यम से स्थानांतरण (जैसा कि यह आईपी-कर्नेल के अंतिम संस्करण में होगा)।

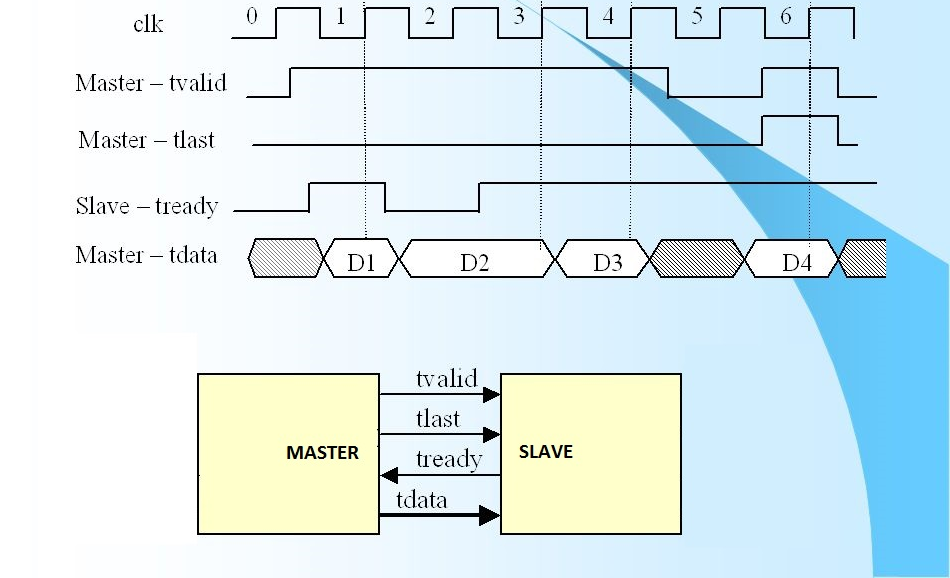

AXIS इंटरफ़ेस वर्कफ़्लो

AXIS इंटरफ़ेस वर्कफ़्लोहम डेटा उत्पादन के लिए आईपी-कर्नेल के दो वेरिएंट लागू करते हैं, पहला परीक्षण किया गया संस्करण वेरिलॉग के माध्यम से कार्यान्वित किया जाता है, दूसरा - एचएलएस पर (इस संदर्भ में, एचएलएस "स्टाइलिश-फैशन-यूथ" नारे के तहत दिखाई दिया)।

इस प्रकार के ip-cores को विकसित करते समय verilog डेटा जनरेटर (और आम तौर पर एचडीएल परिवार की भाषाओं में - verilog, vhdl, आदि) एक मानक समाधान है। यहाँ कुछ कोड स्निपेट मध्यवर्ती आईपी कर्नेल के लिए हैं:

module GenCnt ( …. assign HandsHake = m_axis_din_tready & m_axis_dout_tvalid; always @(posedge Clk) begin if (Rst) begin smCnt <= sIDLE; end else begin case (smCnt) sIDLE: begin smCnt <= sDATA; end sDATA: begin if (Cnt == cTopCnt - 1) begin smCnt <= sLAST; end end ... endmodule

अधिक विस्तृत विवरण की आवश्यकता नहीं है, क्योंकि यह एक FPGA डिजाइनर का एक विशिष्ट कार्य है।

एक और दिलचस्प "जानवर" यहां एचएलएस है।

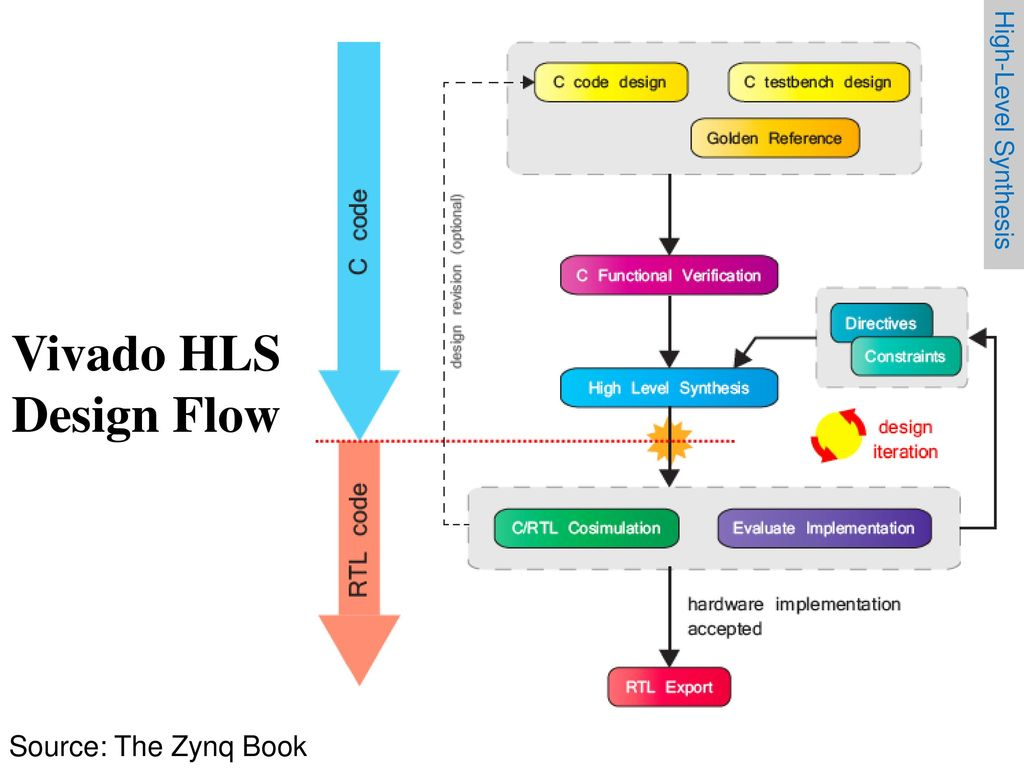

Vivado HLS (हाई लेवल सिंथेसिस) OpenCL, C या C ++ जैसी उच्च-स्तरीय भाषाओं का उपयोग करके डिजिटल डिवाइस बनाने के लिए नया Xilinx CAD सॉफ्टवेयर है।

सी / सी ++ एक एम्बेडेड सॉफ्टवेयर इंजीनियर के लिए मुख्य भाषाएं हैं, इसलिए भविष्य की परियोजनाओं के लिए कार्यान्वयन और तुलनात्मक विश्लेषण के मामले में इन भाषाओं का उपयोग करके एक समस्या को हल करना अधिक दिलचस्प है।

यहां एचएलएस के साथ काम करने के दो छोटे उदाहरण दिए गए हैं। पहला उदाहरण AXI_DMA के लिए डेटा जनरेटर है, दूसरा उदाहरण s_axilite इंटरफ़ेस के माध्यम से प्रोसेसर भाग और प्रोग्रामेबल लॉजिक के बीच डेटा का आदान-प्रदान है।

S_axilite इंटरफ़ेस (दूसरा उदाहरण) के माध्यम से डेटा विनिमय इसलिए लागू किया गया था ताकि किसी भी समय खरीद में यह संभव हो सके कि कौन सा बिटस्ट्रीम लोड किया गया था, और इसलिए कि यह SoC के PL भाग के लिए संस्करण द्वारा काम की शुद्धता को ट्रैक करना संभव था। यहां s_axilite के साथ एक बहुत ही दिलचस्प बिंदु दिखाई देता है: विवाडो HLS लिनक्स के लिए एक ड्राइवर बनाता है (ड्राइवर, बदले में, हमने लेखन की आनुवंशिकता को संरक्षित करने के लिए प्रूफ़ के माध्यम से काम करने के लिए अनुकूलित किया है)। लिनक्स के लिए उत्पन्न कोड का एक उदाहरण नीचे है (स्रोत समाधान 1 / प्रत्यारोपण / आईपी / ड्राइवर / name_xxx / src /) के लिए पथ।

एचएलएस संश्लेषण और आरटीएल कोड पीढ़ी के चरण

एचएलएस संश्लेषण और आरटीएल कोड पीढ़ी के चरणAXI_DMA के साथ ऑपरेशन की जाँच के लिए HLS डेटा जनरेटर:

#include <ap_axi_sdata.h> #include <hls_stream.h> #define SIZE_STREAM 1024 struct axis { int tdata; bool tlast; }; void data_generation(axis outStream[SIZE_STREAM]) { #pragma HLS INTERFACE axis port=outStream int i = 0; do{ outStream[i].tdata = i; outStream[i].tlast = (i == (SIZE_STREAM - 1)) ? 1 : 0; i++; }while( i < SIZE_STREAM); }

संस्करण और इंटरफ़ेस बोर्ड के प्रकार प्राप्त करने का एक उदाहरण:

#include <stdio.h> void info( int &aVersion, int &bSubVersion, int &cTypeBoard, int version, int subVersion, int typeBoard ){ #pragma HLS INTERFACE s_axilite port=aVersion #pragma HLS INTERFACE s_axilite port=bSubVersion #pragma HLS INTERFACE s_axilite port=cTypeBoard #pragma HLS INTERFACE ap_ctrl_none port=return aVersion = version; bSubVersion = subVersion; cTypeBoard = typeBoard; }

जैसा कि आपने देखा, hls पर विकास के लिए विभिन्न प्रागमाओं (HLS pragma) के कार्य और अनुप्रयोग को समझना बहुत महत्वपूर्ण है, क्योंकि संश्लेषण प्रक्रिया सीधे pragmas से जुड़ी होती है।

S_axilite के लिए निर्मित ड्राइवर:

एक महत्वपूर्ण फ़ाइल जो आपको पता स्थान में चर (रजिस्टर) का स्थान बताती है, फ़ाइल x # your_name # _hw.h है। आप हमेशा devmem टूल का उपयोग करके लिखित IP-कर्नेल की शुद्धता को सत्यापित कर सकते हैं।

इस फ़ाइल की सामग्री:

यह फ़ाइल रजिस्टर के पते का वर्णन करती है, रजिस्टर फ़ंक्शन में तर्कों के स्थान के अनुरूप है। परियोजना के संश्लेषण के बाद, आप देख सकते हैं कि बनाई गई परियोजना को चक्रों में कैसे निष्पादित किया जाएगा।

प्रोजेक्ट बीट उदाहरण

प्रोजेक्ट बीट उदाहरणहल्स के साथ काम करने से पता चला है कि यह उपकरण कार्यों को जल्दी से हल करने के लिए उपयुक्त है, विशेष रूप से यह कंप्यूटर दृष्टि की गणितीय समस्याओं को हल करने के लिए खुद को साबित कर चुका है, जिसे सी ++ या सी में आसानी से वर्णित किया जा सकता है, साथ ही साथ बातचीत और विनिमय के लिए छोटे आईपी-कर्नेल बनाने के लिए भी। मानक FPGA इंटरफेस के साथ जानकारी।

उसी समय, एचएलएस विशिष्ट हार्डवेयर इंटरफेस को लागू करने के लिए उपयुक्त नहीं है, उदाहरण के लिए, हमारे मामले में यह I2S था, और उत्पन्न आरटीएल कोड एफपीजीए पर मानक एचडीएल भाषाओं में लिखे गए से अधिक स्थान लेता है।

चालक परीक्षण में अंतिम चरण I2S ट्रैफिक जनरेटर का विकास है। यह आईपी-कोर पिछले आईपी-कर्नेल की कार्यक्षमता को दोहराता है, सिवाय इसके कि यह वृद्धिशील डेटा (ट्रैफ़िक) उत्पन्न करता है जो TDM मोड में वास्तविक I2S डेटा से मेल खाती है।

भविष्य के कस्टम I2S कोर परीक्षण और I2S यातायात जनरेटर के लिए ब्लॉक डिजाइन

भविष्य के कस्टम I2S कोर परीक्षण और I2S यातायात जनरेटर के लिए ब्लॉक डिजाइनपरिणामस्वरूप, हमें hls, axi dma और s_axilite के परिणाम मिले, हमारे सॉफ़्टवेयर और ड्राइवरों के प्रदर्शन की जाँच की।

निष्कर्ष

हमने आवश्यक प्रकार के इंटरफ़ेस कार्ड विकसित करने में कामयाबी हासिल की, साथ ही साथ tdm, pri, bri के लिए ip-kernels। हमने ऐसे उपकरणों के विकास के लिए वर्तमान दृष्टिकोण में काफी सुधार किया है और एक व्यापक समाधान बनाया है जो

एस्टरिक ,

पैट्टन और अन्य से समान इंटरफ़ेस बोर्डों के साथ प्रतिस्पर्धा कर सकता है। हमारे समाधान का लाभ यह है कि डेवलपर को डेटा ट्रांसफर के लिए पीसी और पीसीआई के बीच एक मध्यवर्ती लिंक की आवश्यकता नहीं है, वह सीधे ईथरनेट के माध्यम से प्राप्त जानकारी को प्रसारित करने में सक्षम होगा।