ऐसा नहीं है कि बहुत पहले हमने नई सेलेगल सेवा के बारे में बात की थी -

एफपीजीए त्वरक पर क्लाउड-उच्च प्रदर्शन कंप्यूटिंग । इस विषय पर एक नए लेख में, हम फ्रैगल छवियों को देखने के लिए एक प्रसिद्ध गणितीय एल्गोरिथ्म मेंडेलब्रोट सेट के निर्माण के लिए एफपीजीए प्रोग्रामिंग का एक उदाहरण मानते हैं। लेख ने

यूलर प्रोजेक्ट साइट से सामग्री का उपयोग किया।

इसके बजाय अग्रदूत

सबसे पहले, कुछ शब्द। एक FPGA त्वरक के साथ एक कंप्यूटर प्रणाली - एक नियम के रूप में, यह एक PCIe एडेप्टर है, जो F64A चिप के साथ x64 सर्वर के हिस्से के रूप में है। एक्सेलेरेटर एक अलग संसाधन-गहन कार्य करता है, जिसमें समानांतर कंप्यूटिंग शामिल हो सकती है और इसे x64 प्रोसेसर की तुलना में तेजी से परिमाण के कई आदेश निष्पादित करते हैं, इसे अनलोड करते हैं और पूरे कंप्यूटिंग सिस्टम के प्रदर्शन को बढ़ाते हैं। उदाहरण के लिए, एक क्लासिक x64 प्रोसेसर पर क्रमिक रूप से 100 हजार बार निष्पादित करने के बजाय, केवल एक पास में एक FPGA पर 100 हजार दोहराव के साथ एक गणना चक्र किया जा सकता है। तार्किक तत्व, हार्डवेयर संसाधन, संचार लिंक, FPGA चिप्स को उपयोगकर्ता द्वारा सीधे कार्य के लिए प्रोग्राम किया जाता है, जो आपको सिलिकॉन में एल्गोरिथ्म के कार्यान्वयन के रूप में कार्य को कार्यान्वित करने की अनुमति देता है - सिलिकॉन में एल्गोरिथ्म और जिससे उच्च प्रदर्शन प्राप्त होता है, और सबसे मामूली बिजली की खपत होती है।

आज, FPGA प्रौद्योगिकी में प्रवेश के लिए दहलीज भी स्टार्टअप्स के लिए काफी सुलभ है - FPGA त्वरक और सभी आवश्यक सॉफ़्टवेयर (SDK) वाला सर्वर उचित मूल्य (तथाकथित "क्लाउड BPGA") के लिए Selectel क्लाउड में किराए पर लिया जा सकता है, और FPGA में ओपन CL मानक के लिए समर्थन की ओर जाता है। एक प्रोग्रामर जो जानता है कि C के साथ कैसे काम करना है, FPGA पर एक प्रोग्राम तैयार और चला सकता है।

आगे देखें: काम पर FPGA का प्रयास करें

मैंडेलब्रोट सेट के निर्माण के लिए नीचे वर्णित प्रोग्रामिंग उदाहरण को पहले से ही चयन

सेल में एक परीक्षण सर्वर पर लागू किया गया है, जहां कोई भी अपने प्रदर्शन का मूल्यांकन कर सकता है (पंजीकरण की आवश्यकता होगी)।

परियोजना को कोड में प्रदान किया गया है और संकलन के लिए तैयार किया गया है। चयनकर्ता Intel Arria 10 FPGA त्वरक के साथ एक सर्वर तक दूरस्थ पहुँच प्रदान करता है। सर्वर साइड पर, OpenCL को विकसित करने, डिबग करने और संकलित करने के लिए एसडीके और बीएसपी टूल, होस्ट एप्लिकेशन तैयार करने के लिए विज़ुअल स्टूडियो कोड (सर्वर के केंद्रीय प्रोसेसर के लिए नियंत्रण अनुप्रयोग) तैनात हैं।

ध्यान दें कि उदाहरण में स्वयं कोई लागू मूल्य नहीं है, इसे समानता के सिद्धांतों का उपयोग करके त्वरण विधियों के प्रदर्शन के कारणों के लिए चुना गया था। इस उदाहरण के साथ, पाठक FPGA के साथ विषम कंप्यूटिंग प्रणाली में एक एप्लिकेशन को डिजाइन करने के मार्ग से परिचित हो जाता है - बाद में इस मार्ग का उपयोग समानांतर कंप्यूटिंग के साथ अपने स्वयं के अनुप्रयोगों को विकसित करने के लिए किया जा सकता है।

अद्यतन : 2018 के वसंत में, इंटेल ने उच्च-प्रदर्शन वाले हाइब्रिड प्रोसेसर Xeon Gold 6138P को एकीकृत Arria 10 FPGA चिप के साथ पेश किया। 2018 के अंत तक, इस प्रकार के सीरियल प्रोसेसर इंटेल भागीदारों के माध्यम से ग्राहकों के लिए उपलब्ध होने की उम्मीद है। सेलेल में हम इस चिप के लिए तत्पर हैं, और इस अद्वितीय नए उत्पाद का परीक्षण करने के अवसर के साथ अपने ग्राहकों को प्रदान करने के लिए रूस में पहले होने की उम्मीद करते हैं।

FPGA प्रोग्रामिंग के लिए OpenCL मानक के बारे में

OpenCL मानक को क्रोनोस ग्रुप द्वारा विकसित किया गया था, जो दुनिया की प्रमुख चिप और सॉफ्टवेयर निर्माता हैं जिनमें इंटेल, एएमडी, एप्पल, एआरएम, एनवीडिया, सोनी कंप्यूटर एंटरटेनमेंट और अन्य शामिल हैं। यह उन अनुप्रयोगों को लिखने के लिए डिज़ाइन किया गया है जो FPGA सहित विभिन्न प्रकार के प्रोसेसर पर समानांतर कंप्यूटिंग का उपयोग करते हैं। OpenCL मानक में C99 भाषा संस्करण पर आधारित C प्रोग्रामिंग भाषा शामिल है (C99 का नवीनतम संस्करण ISO / IEC 9899: 1999 / Cor 3: 2007 से 2007-11-15) और एक अनुप्रयोग प्रोग्रामिंग परिवेश है।

उच्च-प्रदर्शन कंप्यूटिंग के लिए ओपनसीएल का उपयोग करने की लोकप्रियता इस तथ्य पर आधारित है कि यह एक खुला मानक है, और इसके उपयोग के लिए लाइसेंस की आवश्यकता नहीं है। इसके अलावा, ओपनसीएल किसी विशेष ब्रांड के लिए समर्थित उपकरणों की सीमा को सीमित नहीं करता है, जिससे एक ही सॉफ्टवेयर प्लेटफॉर्म पर विभिन्न निर्माताओं से हार्डवेयर का उपयोग किया जा सकता है।

OpenCL के बारे में: Habr पर OpenCL का परिचय ।

थोड़ा सा इतिहास - FPGA डिजाइन मार्ग जो ओपनसीएल मानक से पहले अस्तित्व में था, बेहद विशिष्ट और समय लेने वाला था, जबकि जटिलता के संदर्भ में यह कस्टम-चिप डिजाइन (एएसआईसी, एप्लिकेशन-विशिष्ट एकीकृत सर्किट, "विशेष प्रयोजन एकीकृत सर्किट") से भी बेहतर था। FPGA हार्डवेयर संरचना की गहन समझ की आवश्यकता थी, जिसका विन्यास निम्न-स्तरीय हार्डवेयर विवरण भाषा (HDL) में किया जाना था। इस डिज़ाइन और सत्यापन मार्ग का कब्ज़ा एक ऐसी कला रही है, जो चरम जटिलता के कारण, डेवलपर्स के सीमित दायरे में उपलब्ध है।

FPGAs के लिए इंटेल के OpenCL समर्थन टूलकिट के आगमन ने आंशिक रूप से सॉफ्टवेयर डेवलपर्स के लिए FPGA प्रोग्रामिंग की पहुंच के मुद्दे को संबोधित किया है। प्रोग्रामर स्वतंत्र रूप से अपने एल्गोरिथ्म के उस हिस्से का चयन करता है जो समानांतर प्रसंस्करण के लिए उपयुक्त है और सी में इसका वर्णन करता है, तो FPGA के लिए इंटेल ओपनसीएल कंपाइलर बाइनरी कॉन्फ़िगरेशन फ़ाइल को त्वरक पर एल्गोरिदम के इस टुकड़े को चलाने के लिए बनाता है।

परिचित विज़ुअल स्टूडियो वातावरण या मानक gcc संकलक का उपयोग करके, एक होस्ट एप्लिकेशन तैयार किया जाता है (प्रकार का। Exe, मुख्य x64 प्रोसेसर पर निष्पादित), जबकि सभी आवश्यक समर्थन पुस्तकालयों को एसडीके में शामिल किया गया है। जब होस्ट एप्लिकेशन लॉन्च किया जाता है, तो FPGA फर्मवेयर लोड होता है, डेटा को चिप कोर में लोड किया जाएगा और कल्पना एल्गोरिथ्म के अनुसार प्रसंस्करण शुरू हो जाएगा।

FPGA (FPGA) एक उपयोगकर्ता-रिप्रोग्रामेबल बड़े पैमाने पर समानांतर हार्डवेयर संरचना है जिसमें लाखों तर्क तत्व, हजारों डीएसपी सिग्नल इकाइयां और ऑन-बोर्ड गणना के लिए दसियों मेगाबाइट्स कैश, सर्वर के मुख्य नेटवर्क मॉड्यूल तक पहुंच के बिना हैं। फास्ट I / O इंटरफेस (10GE, 40GE, 100GE, PCIe Gen 3, आदि) आपको प्रभावी रूप से सर्वर के मुख्य प्रोसेसर के साथ डेटा का आदान-प्रदान करने की अनुमति देते हैं।

OpenCL मानक विषम सॉफ्टवेयर निष्पादित करने के लिए एक वातावरण है। पर्यावरण में दो अलग-अलग भाग होते हैं:

- होस्ट सॉफ़्टवेयर - सर्वर के मुख्य केंद्रीय प्रोसेसर पर चलने वाला एप्लिकेशन, जो C / C ++ में लिखा गया है और कार्यों के OpenCL API सेट का उपयोग कर रहा है। होस्ट सर्वर कंप्यूटिंग की पूरी प्रक्रिया को व्यवस्थित करता है, स्रोत की आपूर्ति करता है और आउटपुट डेटा प्राप्त करता है, और FPG त्वरक के साथ सभी सर्वर सिस्टम के साथ सहभागिता करता है।

- त्वरक सॉफ्टवेयर - ओपनसीएल सी भाषा (प्रतिबंधों की एक संख्या के साथ सी भाषा) में लिखा गया एक कार्यक्रम, जिसे एफपीजीए चिप पर चलाने के लिए संकलित किया गया है।

समानांतर कंप्यूटिंग के लिए एक विशिष्ट सर्वर एक x64- आधारित कंप्यूटर (होस्ट अनुप्रयोगों को चलाने के लिए) है, जिसमें एक हार्डवेयर FPGA त्वरक शामिल है, जो अक्सर PCI-Express बस के माध्यम से जुड़ा होता है। वैसे, इस तरह की प्रणाली को Selectel Lab में प्रस्तुत किया गया है।

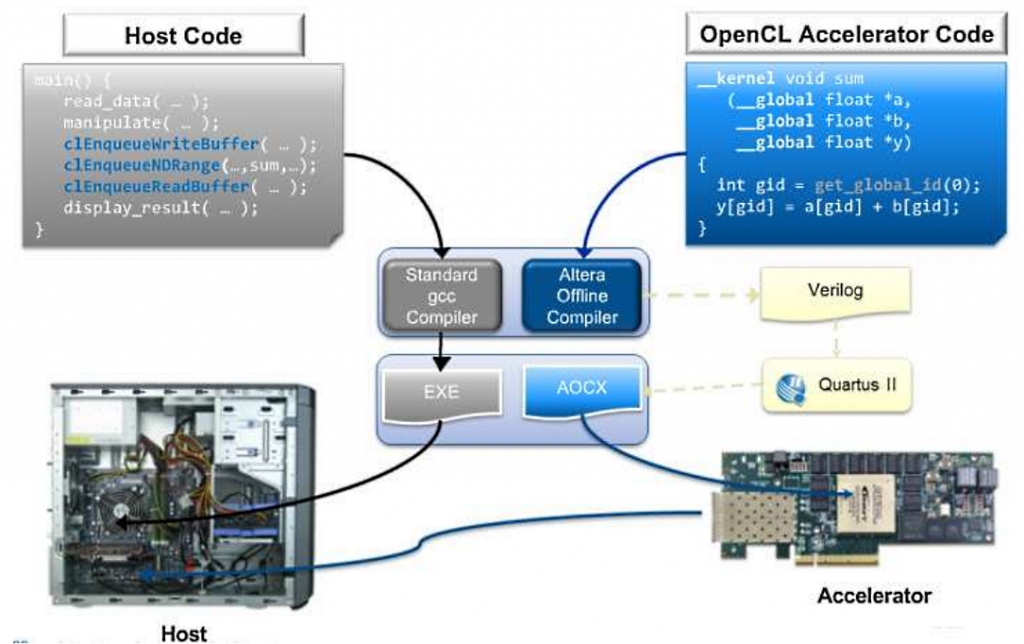

FPGA त्वरक के लिए प्रोग्रामिंग और संकलन अनुक्रम दो चरणों के होते हैं। सर्वर ऑपरेटिंग सिस्टम (उदाहरण के लिए, * .exe) में एक निष्पादन योग्य फ़ाइल प्राप्त करने के लिए होस्ट एप्लिकेशन कोड एक मानक संकलक (विज़ुअल सी ++, जीसीसी) द्वारा संकलित किया गया है। FPGA त्वरक (कर्नेल, कर्नेल) के स्रोत कोड को AOC संकलक द्वारा SDK के भाग के रूप में तैयार किया जाता है, जिसमें एक बाइनरी फ़ाइल (* .aocx) की प्राप्ति होती है। यह फाइल सिर्फ एक्सीलरेटर प्रोग्रामिंग के लिए है।

अंजीर। OpenCL सॉफ्टवेयर संकलन पर्यावरण वास्तुकला

दो तरीकों से एक बड़े वेक्टर की गणना के लिए कुछ उदाहरण कोड पर विचार करें

(

पीएस पियानोवादक को गोली मत चलाना - इसके बाद यूलर प्रोजेक्ट साइट से कोड का उपयोग किया जाता है ):

void inc (float *a, float c, int N) { for (int i = 0; i<N; i++) a[i] = a[i] + c; } void main() { ... inc(a,c,N); ... }

_kernel void inc (_global float *a, float c) { int i = get_global_id(0); a[i] = a[i] + c; } void main() { ... clEnqueueNDRangeKernel(...,&N,...) ... }

शुरुआत में कोड इस बात का एक उदाहरण है कि कैसे सी में एकल-थ्रेडेड कार्यान्वयन स्केलर तत्वों की अनुक्रमिक गणना की विधि का उपयोग कर सकता है।

कोड का दूसरा संस्करण एक FPGA त्वरक पर गणना की गई फ़ंक्शन के रूप में OpenCL पर एल्गोरिथ्म का एक संभावित कार्यान्वयन है। लूप नहीं है, और गणना लूप के एक पुनरावृत्ति में होती है। एक वेक्टर सरणी की गणना इस फ़ंक्शन की एन प्रतियों के निष्पादन के रूप में होती है। प्रत्येक कॉपी का अपना इंडेक्स होता है, जिसे लूप में इटरेटर में प्रतिस्थापित किया जाता है, और कोड निष्पादित होने पर होस्ट से रिट्रीट की संख्या निर्धारित की जाती है। Itter क्रिया get_global_id () फ़ंक्शन द्वारा प्रदान की जाती है, जो 0 ≤ इंडेक्स <N के भीतर एक इंडेक्स के साथ काम करती है।

इस बिंदु पर जाएं: एक भग्न का निर्माण

मैंडेलब्रॉट सेट जटिल विमान पर "सी" अंक का एक सरणी है, जिसके लिए Z0 = 0 के लिए पुनरावृत्ति संबंध Zn + 1 = Zn 1 + c एक अनुक्रम अनुक्रम को परिभाषित करता है।

हम Zn = Zn + IYn, और c = p + iq को परिभाषित करते हैं।

प्रत्येक बिंदु के लिए, निम्नलिखित अनुक्रम की गणना की जाती है:

Xn + 1 = Xn² + Yn + + p

Yn + 1 = 2XnYn + q

प्रत्येक पुनरावृत्ति पर सेट पर एक बिंदु से संबंधित की गणना समीकरण के रूप में की जाती है

Xn X + Yn² <4।

स्क्रीन पर सेट किए गए मैंडेलब्रोट को प्रदर्शित करने के लिए, हम एक नियम को परिभाषित करते हैं:

- यदि असमानता किसी भी पुनरावृत्ति पर रहती है, तो बिंदु सेट में प्रवेश करता है और काले रंग में दिखाया जाएगा।

- यदि असमानता पकड़ नहीं है, एक निश्चित पुनरावृत्ति मूल्य n = N से शुरू होता है, तो रंग पुनरावृत्तियों की संख्या एन द्वारा निर्धारित किया जाता है।

मेजबान पर गणना की प्रक्रिया इस प्रकार होगी:

- पिक्सेल विंडो के अंदर प्रत्येक बिंदु के पुनरावृत्तियों की संख्या को mandel_pixel () फ़ंक्शन को सौंपा गया है।

- छवि बिंदुओं के अनुक्रमिक गणना को सॉफ्टवेयरकैलिकेटफ्रेम () फ़ंक्शन द्वारा प्रदान किया जाएगा। पैरामीटर गणना किए गए बिंदुओं के वास्तविक अंतराल, एल्गोरिथ्म के वास्तविक चरण और छवि के आकार के रंग बफर के लिए एक सूचक (Width * theHight) निर्दिष्ट करते हैं।

- डॉट के रंग कोSoftColorTable द्वारा समायोजित किया जाता है।

कोड पर चलते हैं:

inline unsigned int mandel_pixel( double x0, double y0, unsigned int maxIterations ) { // variables for the calculation double x = 0.0; double y = 0.0; double xSqr = 0.0; double ySqr = 0.0; unsigned int iterations = 0; // perform up to the maximum number of iterations to solve // the current point in the image while ( xSqr + ySqr < 4.0 &&iterations < maxIterations ) { // perform the current iteration xSqr = x*x; ySqr = y*y; y = 2*x*y + y0; x = xSqr - ySqr + x0; // increment iteration count iterations++; } // return the iteration count return iterations; }

int softwareCalculateFrame( double aStartX, double aStartY, double aScale, unsigned int* aFrameBuffer ) { // temporary pointer and index variables unsigned int * fb_ptr = aFrameBuffer; unsigned int j, k, pixel; // window position variables double x = aStartX; double y = aStartY; double cur_x, cur_y; double cur_step_size = aScale; // for each pixel in the y dimension window for ( j = 0, cur_y = y; j < theHeight; j++, cur_y -= cur_step_size ) { // for each pixel in the x dimension of the window for ( cur_x = x, k = 0; k< theWidth; k++, cur_x += cur_step_size ) { // set the value of the pixel in the window pixel = mandel_pixel(cur_x, cur_y, theSoftColorTableSize); if ( pixel == theSoftColorTableSize ) *fb_ptr++ = 0x0; else *fb_ptr++ = theSoftColorTable[pixel]; } } return 0; }

प्रत्येक पिक्सेल को दूसरे से स्वतंत्र रूप से गणना की जाती है, और इसलिए इस प्रक्रिया को समानांतर किया जा सकता है। FPGA त्वरक के लिए एल्गोरिथ्म को लागू करते समय, प्रत्येक पुनरावृत्ति पिक्सेल के लिए संख्या की गणना करने के लिए एक SIMD निर्देश बनाया जाता है (पैलेट से रंग कोड का निर्धारण)। छवि बफ़र पर दो नेस्टेड छोरों के कार्यान्वयन को ओपनसीएल के माध्यम से ऑपरेशन (Width * theHight) चलाकर तैयार किया गया है।

नीचे दी गई लिस्टिंग में कर्नेल इंस्टेंसेस को वर्क-आइटम कहा जाता है, और सभी इंस्टेंस के सेट को इंडेक्स स्पेस कहा जाता है। हार्डवेयर फ़ंक्शन की विशेषताओं में निम्नलिखित शामिल हैं:

- फ़ंक्शन की घोषणा __kernel कीवर्ड से शुरू होती है।

- हार्डवेयर फ़ंक्शन का प्रकार - रिटर्न मान का प्रकार हमेशा शून्य होता है।

- रिटर्निंग मान पैरामीटर के रूप में पारित बफ़र्स के माध्यम से किया जाता है।

- पहले तीन पैरामीटर भौतिक ग्रिड को परिभाषित करते हैं, जिनमें से नोड्स आउटपुट छवि के पिक्सल के अनुरूप हैं।

- चौथा पैरामीटर मंडेब्रोट सेट से संबंधित बिंदुओं के लिए लूपिंग को रोकने, पुनरावृत्तियों की संख्या को सीमित करता है।

- पांचवां पैरामीटर आउटपुट रंग बफर के लिए एक संकेतक है।

- __Global कीवर्ड मेमोरी के प्रकार को दर्शाता है जिसके माध्यम से बफर प्रसारित किया जाएगा: यह त्वरक पर सामान्य DDR (QDR) मेमोरी है।

- प्रतिबंधित कीवर्ड ऑप्टिमाइज़र को अप्रत्यक्ष बफर संदर्भों का उपयोग करने पर प्रतिबंध देता है।

- 6 वें पैरामीटर में, पैलेट को एक पॉइंटर पारित किया गया है।

- __Constant कीवर्ड, केवल-पढ़ने के लिए विशेषता के साथ कैश उत्पन्न करके बफर एक्सेस का अनुकूलन करता है।

लिस्टिंग में फ़ंक्शन का विवरण x64 प्रोसेसर के लिए कार्यान्वयन के करीब है। यहां, वर्तमान कर्नेल उदाहरण की परिभाषा get_global_id फ़ंक्शन के माध्यम से की जाती है, जिसमें आयाम संख्या (0, 1) को एक पैरामीटर के रूप में पारित किया जाता है।

बेहतर अनुकूलन के लिए, चक्र की शुरुआत का एक स्पष्ट संकेत पेश किया गया है। संकलन के समय पुनरावृत्तियों की संख्या के बारे में जानकारी के अभाव में, लूप चरणों की संख्या स्पष्ट रूप से इंगित की जाती है, क्योंकि उनके लिए उनके स्वयं के हार्डवेयर ब्लॉक बनाए जाएंगे। इस तरह की कोडिंग के साथ, एक एक्सीलरेटर पर स्थापित एक विशिष्ट चिप की क्षमता पर "पीछे मुड़कर देखना" चाहिए, क्योंकि FPGA संसाधन खपत के कारण बड़ी संख्या में चक्र।

//////////////////////////////////////////////////////////////////// // mandelbrot_kernel.cl : Hardware implementation of the mandelbrot algorithm //////////////////////////////////////////////////////////////////// // Amount of loop unrolling. #ifndef UNROLL #define UNROLL 20 #endif // Define the color black as 0 #define BLACK 0x00000000 __kernel void hw_mandelbrot_frame ( const double x0, const double y0, const double stepSize, const unsigned int maxIterations, __global unsigned int *restrict framebuffer, __constant const unsigned int *restrict colorLUT, const unsigned int windowWidth) { // Work-item position const size_t windowPosX = get_global_id(0); const size_t windowPosY = get_global_id(1); const double stepPosX = x0 + (windowPosX * stepSize); const double stepPosY = y0 - (windowPosY * stepSize); // Variables for the calculation double x = 0.0; double y = 0.0; double xSqr = 0.0; double ySqr = 0.0;</code> <code>unsigned

OpenCL उपयोगिता पैकेज के लिए Intel FPGA SDK को एल्गोरिथम के हार्डवेयर कार्यान्वयन को संकलित करने से पहले मेजबान पर स्थापित करना होगा। पूर्व-स्थापित सॉफ़्टवेयर में, आपको विशिष्ट त्वरक बोर्ड के निर्माता से बीएसपी (बोर्ड सपोर्ट पैकेज) शामिल करना चाहिए। उदाहरण में, Intel Quartus Prime Pro 16.1 को OpenCL और BSP के Euler थ्रेड एक्सीलेरेटर (Intel Arria 10) के समर्थन से स्थापित किया गया है।

पथ और पर्यावरण चर का विन्यास निम्नलिखित है। चर ALTERAOCLSDKROOT में इंटेल FPGA SDK का पथ है, चर AOCL_BOARD_PACKAGE_ROOT में त्वरक BSP के लिए पथ समाहित है।

set ALTERAOCLSDKROOT=C:\intelFPGA_pro\16.1\hld set AOCL_BOARD_PACKAGE_ROOT=C:\intelFPGA_pro\16.1\hld\board\euler_thread set path=%path%;C:\intelFPGA_pro\16.1\hld\bin set path=%path%;C:\intelFPGA_pro\16.1\quartus\bin64 set path=%path%;C:\intelFPGA_pro\16.1\hld\board\a10_ref\windows64\bin set path=%path%;C:\intelFPGA_pro\16.1\hld\host\windows64\bin set path=%path%;C:\intelFPGA_pro\16.1\qsys\bin set path=%path%;C:\Program Files (x86)\GnuWin32\bin\

संकलन के लिए, एसडीके से एको कंपाइलर का उपयोग किया जाता है।

aoc mandelbrot_kernel.cl -o mandelbrot_kernel.aocx --board thread -v -v --report

हम डिक्रिप्ट करते हैं: mandelbrot_kernel.cl - स्रोत पाठ के साथ फाइल, mandelbrot_kernel.aocx - प्रोग्रामिंग FPGA, थ्रेड के लिए आउटपुट ऑब्जेक्ट फ़ाइल - BSP पैकेज से त्वरक का नाम। --Report स्विच एक FPGA संसाधन उपयोग रिपोर्ट प्रदर्शित करता है। -V स्विच संकलन के दौरान नैदानिक जानकारी प्रदर्शित करता है। कर्नेल के लिए संसाधन खपत रिपोर्ट इस प्रकार है:

+ ------------------------------------------------- ------------------- +

; अनुमानित संसाधन उपयोग सारांश;

+ ---------------------------------------- + -------- ------------------- +

; संसाधन + उपयोग;

+ ---------------------------------------- + -------- ------------------- +

; तर्क उपयोग; 49%;

; ALUTs; 26%;

; समर्पित तर्क रजिस्टर; 25%;

; मेमोरी ब्लॉक; 21%;

; डीएसपी ब्लॉक; 16%;

+ ---------------------------------------- + -------- -------------------;

होस्ट एप्लिकेशन को संकलित करने के लिए, उदाहरण में Microsoft SDK 7.1 स्थापित Microsoft Visual Studio 2010 एक्सप्रेस पैकेज का उपयोग किया गया था। प्रोजेक्ट सेटिंग्स में, x64 के लिए कॉन्फ़िगरेशन का चयन किया जाता है। अगला, बाहरी हेडर फ़ाइलों के लिए फ़ोल्डर कनेक्ट करें और लिंकर सेटिंग्स में अतिरिक्त इंटेल FPGA एसडीके पुस्तकालयों के लिए पथ निर्दिष्ट करें।

फ़ाइलों को शामिल करने के लिए अतिरिक्त निर्देशिका = $ (ALTERAOCLSDKROOT) \ host \ में शामिल हैं;

अतिरिक्त पुस्तकालय निर्देशिका = $ (AOCL_BOARD_PACKAGE_ROOT) \ windows64 \ lib;

$(ALTERAOCLSDKROOT)\host\windows64\lib;

त्वरक पर कर्नेल को लॉन्च करने की सामान्य योजना निम्नानुसार होगी:

- प्लेटफार्मों की एक सूची प्राप्त करें

- उपकरणों की एक सूची प्राप्त करें

- संदर्भ बनाएं;

- डिवाइस में कर्नेल लोड करें;

- डिवाइस को इनपुट बफ़र्स भेजें;

- निष्पादन के लिए कर्नेल चलाएं;

- डिवाइस से आउटपुट बफर पढ़ें;

- मुक्त संदर्भ।

कर्नेल शुरू करने से संबंधित कुछ बिंदुओं पर सीधे विचार करें। तो, एक कोर छवि के एक पिक्सेल को संसाधित करने के लिए डिज़ाइन किया गया है। इस प्रकार, आपको एन कर्नेल इंस्टेंसेस को चलाने की आवश्यकता है, जहां एन छवि में पिक्सल की कुल संख्या है।

नीचे, हम मामले को नोट करते हैं जब सर्वर में कई त्वरक बोर्ड होते हैं, तो उनके बीच कार्य वितरित किया जा सकता है। प्रत्येक एक्सेलेरेटर में, आपको कर्नेल लोड करने की आवश्यकता होती है (फ़ाइल mandelbrot_kernel.aocx)। मान लीजिए कि त्वरक की संख्या संख्यात्मक है, और छवि रेखाएं सभी त्वरक के बीच विभाजित हैं:

#define MAXDEV 10 static cl_context theContext; static cl_program theProgram; static cl_kernel theKernels[MAXDEV]; //.. // Create the program object theProgram = createProgramFromBinary( theContext, "mandelbrot_kernel.aocx", theDevices, numDevices); // Create the kernels for ( unsigned i = 0; i < numDevices; ++i ) theKernels[i] = clCreateKernel( theProgram, "hw_mandelbrot_frame", &theStatus ); // Create output pixel buffers for every kernel for( unsigned i = 0; i < numDevices; ++i ) thePixelData[i] = clCreateBuffer(theContext, CL_MEM_WRITE_ONLY, thePixelDataWidth*rowsPerDevice[i]*sizeof(unsigned int), NULL, &theStatus); // Preparing and writing palette buffer to every device theHardColorTable = clCreateBuffer(theContext, CL_MEM_READ_ONLY, aColorTableSize*sizeof(unsigned int), NULL, &theStatus); for( unsigned i = 0; i < numDevices; i++ ) theStatus = clEnqueueWriteBuffer(theQueues[i], theHardColorTable, CL_TRUE, 0, aColorTableSize*sizeof(unsigned int), aColorTable, 0, NULL, NULL); // Preparing kernels and run unsigned rowOffset = 0; for ( unsigned i = 0; i < numDevices; rowOffset += rowsPerDevice[i++] ) { // Create ND range size size_t globalSize[2] = { thePixelDataWidth, rowsPerDevice[i] }; // Set the arguments unsigned argi = 0; theStatus = clSetKernelArg (theKernels[i], argi++, sizeof(cl_double), (void*) &aStartX ); const double offsetedStartY = aStartY - rowOffset * aScale; theStatus = clSetKernelArg(theKernels[i], argi++, sizeof(cl_double), (void*)&offsetedStartY); theStatus = clSetKernelArg(theKernels[i], argi++, sizeof(cl_double), (void*)&aScale); theStatus = clSetKernelArg(theKernels[i], argi++, sizeof(cl_uint), (void*)&theHardColorTableSize); theStatus = clSetKernelArg(theKernels[i], argi++, sizeof(cl_mem), (void*)&thePixelData[i]); theStatus = clSetKernelArg(theKernels[i], argi++, sizeof(cl_mem), (void*)&theHardColorTable); theStatus = clSetKernelArg(theKernels[i], argi++, sizeof(cl_uint), (void*)&theWidth); // Launch kernel theStatus = clEnqueueNDRangeKernel(theQueues[i], theKernels[i], 2, NULL, globalSize, NULL, 0, NULL, NULL); } rowOffset = 0; for( unsigned i = 0; i < numDevices; rowOffset += rowsPerDevice[i++] ) { // Read the output theStatus = clEnqueueReadBuffer(theQueues[i], thePixelData[i], CL_TRUE, 0, thePixelDataWidth*rowsPerDevice[i]*sizeof(unsigned int), &aFrameBuffer[rowOffset * theWidth], 0, NULL, NULL); } / / . .

- CreateProgramFromBinary फ़ंक्शन ऑब्जेक्ट फ़ाइल से OpenCL प्रोग्राम ऑब्जेक्ट बनाता है।

- अगला, प्रत्येक डिवाइस के लिए, प्रोग्राम ऑब्जेक्ट के आधार पर एक कर्नेल बनाया जाता है।

- ThePixelData बफ़र प्रत्येक कोर से आउटपुट प्राप्त करने के लिए बनाए जाते हैं।

- एक पैलेट को रंग पैलेट को स्टोर करने के लिए बनाया गया है और प्रत्येक त्वरक में लोड किया गया है।

- अगला, प्रत्येक डिवाइस के लिए, स्थानीय अनुप्रयोग मापदंडों और कर्नेल मापदंडों का बंधन clSetK गिर्नेल फ़ंक्शन का उपयोग करके सेट किया गया है।

- पैरामीटर कर्नेल फ़ंक्शन घोषणा में सीरियल नंबर से निर्धारित होते हैं, शून्य से शुरू होते हैं।

अगला महत्वपूर्ण बिंदु वैश्विक आकार सरणी के अनुसार सूचकांक स्थान के आधार पर कार्य का आकार निर्धारित कर रहा है। यह सरणी एक-, दो- या त्रि-आयामी हो सकती है। प्रत्येक आयाम के लिए, एक आयाम पूर्णांक के रूप में दिया जाता है। अंतरिक्ष का आयाम कर्नेल में कार्य-वस्तु के सूचकांक क्रम को निर्धारित करेगा।

उदाहरण में, प्रत्येक कोर के लिए, एक दो-आयामी स्थान निर्दिष्ट किया जाता है, जहां एक कुल्हाड़ी पिक्सेल पंक्ति तत्व है, दूसरा इस डिवाइस पर संसाधित छवि लाइनों का सेट है। कर्नेल कोड में, लाइन में पिक्सेल नंबर get_global_id (0) को कॉल करके प्राप्त किया जाता है, लाइन नंबर get_global_id (1) है। GlobalSize चर को निष्पादित करने के लिए कर्नेल आवृत्तियों की आवश्यक संख्या शुरू करने के लिए clEnqueueNDRangeKernel फ़ंक्शन को पास किया जाता है।

कोर के निष्पादन के पूरा होने पर, पिक्सेल बफ़र्स को डिवाइस से स्थानीय सरणियों में पढ़ा जाता है। चलो प्रति सेकंड फ़्रेम की संख्या से प्रदर्शन का मूल्यांकन करते हैं - परिणाम सेलेटलटेकडे सम्मेलन ( लेख की शुरुआत देखें ) पर किए गए प्रदर्शन पर दिखाई देता है।

निष्कर्ष

उच्च स्तर की भाषा में FPGA त्वरक का प्रोग्रामिंग निस्संदेह परिमाण के क्रम से डेवलपर्स के लिए इस तकनीक तक पहुंच की सीमा को कम करता है। उदाहरण के लिए, जो लोग इस टूलकिट में महारत हासिल कर रहे हैं, उनके लिए प्रसिद्ध "हैलो वर्ल्ड" उदाहरण का FPGA कार्यान्वयन भी है।

लेकिन इतना सरल नहीं है। लेखन - और विशेष रूप से - एक वास्तविक लागू समस्या के स्पष्ट रूप से काम कर रहे एल्गोरिथ्म को डीबग करना अभी भी उच्च व्यावसायिकता की आवश्यकता है। एक और सीमा यह है कि प्रत्येक FPGA चिप आवेदन के भीतर केवल एक कम्प्यूटेशनल कार्य कर सकती है। किसी अन्य कार्य के लिए, इसे फिर से दोबारा लिखा जाना चाहिए।

वैसे, प्लेटफ़ॉर्म का उपयोग करने का मॉडल आपको होस्ट पर एक से अधिक FPGA त्वरक रखने की अनुमति देता है, हालांकि यह एक महंगा समाधान है।

होस्ट (होस्ट एप्लिकेशन) संदर्भ बनाने की प्रक्रिया (त्वरक के लिए डेटा संरचना) और कमांड कतार का प्रबंधन करता है। यानी एक एकल होस्ट एप्लिकेशन, जिसमें FPGA पर समानांतर कंप्यूटिंग के लिए विभिन्न उपकेंद्र हैं, उन्हें विभिन्न त्वरक पर लोड कर सकते हैं:

KERNEL1 => सहायक ए

KERNEL2 => सहायक बी

फिर भी, FPGA एक्सेलेरेटर को मास्टर करने के प्रयास इसके लायक हैं - कई अनुप्रयोग क्षेत्रों में यह तकनीक अपरिहार्य होती जा रही है: कम्प्यूटेशनल गणित और भौतिक क्षेत्र मॉडलिंग में दूरसंचार, जैव प्रौद्योगिकी, बिग डाटा प्रोसेसिंग, पैटर्न मान्यता, सिग्नल और इमेज प्रोसेसिंग।

लेख के लिए अतिरिक्त जानकारी:

www.altera.com इंटेल FPGA कोर संसाधन है।

www.eulerproject.com यूलर प्रोजेक्ट की आधिकारिक वेबसाइट है।

एल्टर + ओपनसीएल: हम वीएचडीएल / वेरिलोग के ज्ञान के बिना एफपीजीए के तहत कार्यक्रम करते हैं - हैबर पर एक लेख।