पिछले लेख के लेखन के बाद से,

“फ्लैश मेमोरी में 18 बाइट्स के लिए एसटीएम 8 बूट लोडर

को कैसे कम किया जाए” ,

एसटीएम 8 एलओएलएडर बूटलोडर के दो संस्करण

दिखाई दिए हैं । STM8uLoader बूटलोडर संस्करण

$ 36 ने सीखा कि एक होस्ट प्रोग्राम की भागीदारी के बिना रैम मेमोरी में किसी एप्लिकेशन प्रोग्राम का नियंत्रण कैसे स्थानांतरित किया जाए। फ्लैश मेमोरी में बूटलोडर के 18 बाइट्स का आकार नहीं बदला, विकल्प बाइट्स क्षेत्र में, आकार बढ़कर 53 बाइट्स तक पहुंच गया (इसमें सभी उपलब्ध स्थान लिया गया)।

$ 0D बूटलोडर की एक अलग शाखा आवंटित की गई थी। इस संस्करण के लिए मुख्य आवश्यकता कोड को यथासंभव संपीड़ित करना है। आज तक, FLASH मेमोरी में कोड का आकार 35 बाइट्स की EEPROM मेमोरी में 8 बाइट्स है।

मुझे STM8uLoader बूटलोडर की वास्तुकला की याद दिलाते हैं। बूटलोडर में boot_PC होस्ट प्रोग्राम और STM8 मेमोरी में boot_uC बूटलोडर कोड होते हैं। बाद को फ्लैश मेमोरी में स्थित boot_FLASH प्रारंभिक प्रतिलिपि कोड और EEPROM मेमोरी (या विकल्प बाइट्स क्षेत्र) में स्थित boot_EEPROM (या boot_OPTION) बूटलोडर कोड में विभाजित किया गया है।

RESET ईवेंट के बाद, boot_FLASH प्रारंभिक कोपियर लॉन्च किया गया है, RAM स्मृति में boot_EEPROM (या boot_OPTION) बूटलोडर कोड छवि को स्थानांतरित करता है और इसे नियंत्रित करता है। बूटलोडर UART को उसके संस्करण संख्या के साथ कार्यक्रम के लिए होस्ट बाइट को स्थानांतरित करता है और, यदि यह टाइमआउट के दौरान होस्ट प्रोग्राम से जानकारी प्राप्त नहीं करता है, तो फ़्लैश मेमोरी में एप्लिकेशन प्रोग्राम पर नियंत्रण स्थानांतरित करता है। या EEPROM मेमोरी (या ऑप्शन बाइट्स एरिया) से एप्लिकेशन कोड को रैम मेमोरी में ट्रांसफर करता है और इसे कंट्रोल ट्रांसफर करता है।

यदि, होस्ट प्रोग्राम के लिए संस्करण संख्या के साथ बाइट भेजने के बाद, बूटलोडर को UART के माध्यम से एक कोड के साथ एक डंप प्राप्त होता है, तो यह रैम मेमोरी में स्थानांतरित करता है और नियंत्रण स्थानांतरित करता है। कोड के साथ स्वीकृत डंप अपना वर्तमान कार्य करता है: STM8 कर्नेल रजिस्टरों के प्रारंभिक आरंभीकरण के साथ निर्दिष्ट पते पर नियंत्रण स्थानांतरित / STM8 कोशिकाओं को पढ़ना / कॉपी / मिटाना, बूट प्रोग्रामर को होस्ट प्रोग्राम द्वारा रैम मेमोरी में वर्तमान डंप को बदलने के लिए नियंत्रण स्थानांतरित करना।

प्रारंभिक कॉपियर बूट_फ्लैश रेव। $ 0D $ 8000 के पते पर स्थित है ... $ 8007 और पूरी तरह से RESET और TRAP (सॉफ्टवेयर इंटरप्ट) वैक्टर पर कब्जा कर लेता है। बाकी की जगह $ 8008 ... $ 9FFF की FLASH मेमोरी एप्लिकेशन प्रोग्राम के लिए पूरी तरह से सुलभ है। बाधित वेक्टर टेबल भी जगह में है।

प्रतिलिपि कोड पर विचार करें:

; boot_FLASH $0D($88) ; $4087($4187) ; $00 ; segment byte at 8000-8007 'bootF_rev0D' ; $8000 RESET Reset vector dc.b $AE, $40 ; [AE 40 88] ldw X,#$4088 ; dc.b $AE, $41 ; [AE 41 88] ldw X,#$4188 cycle: ; ; push A ldw X,#$4088($4188) push A ; [88] decw X ; [5A] ; $8004 TRAP Software interrupt ld A, (X) ; [F6] jrne cycle ; [26 FB] ret ; [81] ; $8008 TLI IRQ0 External top level interrupt

दो कमांड्स का कोड यहाँ प्रतिच्छेद करता है: ldw X, # $ 4088 (ldw X, # $ 4188) कमांड और पुश A। । इस समाधान ने एक बाइट को बचाया, लेकिन बूटलोडर कोड की छवि के साथ तालिका भंडारण क्षेत्र को संकीर्ण करने का कारण बना। तालिका के पते के $ 88 के निम्न बाइट इसे विकल्प बाइट्स क्षेत्र में रखने की अनुमति नहीं देता है। STM8S103F3 मॉडल के लिए, निर्दिष्ट तालिका को समायोजित करने के लिए EEPROM मेमोरी में केवल $ 4088 और $ 4188 पते उपलब्ध हैं। EEPROM मेमोरी 128 बाइट्स ($ 4000 ... $ 407F) के साथ STM8S003F3 के मालिकों के लिए और ये पते उपलब्ध नहीं हैं। उनके लिए अभी भी एक खामी है।

आपको केवल पुश A को स्वैप करना होगा और X कमांड को डिक्रिप्ट करना होगा:

; boot_FLASH $0D($5A) ; $405A($415A, $425A) ; $00 ; segment byte at 8000-8007 'bootF_rev0D' ; $8000 RESET Reset vector dc.b $AE, $40 ; [AE 40 5A] ldw X,#$405A STM8S003F3 ; dc.b $AE, $41 ; [AE 41 5A] ldw X,#$415A ; dc.b $AE, $41 ; [AE 42 5A] ldw X,#$425A cycle: ; ; decw X ldw X,#$405A($415A, $425A) decw X ; [5A] push A ; [88] ; $8004 TRAP Software interrupt ld A, (X) ; [F6] jrne cycle ; [26 FB] ret ; [81] ; $8008 TLI IRQ0 External top level interrupt

यहां, जब आप पहली बार लूप में प्रवेश करते हैं, तो ldw X, # $ 405A ($ 415A, $ 425A) कमांड को निष्पादित किया जाता है, और decw X कमांड को निष्पादित नहीं किया जाता है।

याद रखें कि RESET घटना के साथ, SP स्टैक का शीर्ष सूचक $ 03FF मूल्य के साथ हार्डवेयर-प्रारंभिक है। स्टॉक्स घटते पते की दिशा में बढ़ रहा है। पूंछ से स्टैक को भरने के लिए, हम टेबल से बूटलोडर कोड के साथ तालिका भी पढ़ेंगे, इसलिए डिकॉक एक्स कमांड। EEPROM मेमोरी में बूट लोडर कोड की छवि तदनुसार स्थित है।

पैसे बचाने के लिए, उन्होंने लूप काउंटर को छोड़ दिया। हम इस बात से सहमत थे कि बूटलोडर की कोड छवि में केवल टेबल की शुरुआत में एक शून्य बाइट होगा, और हम कंट्रोल ट्रांसफर एड्रेस को एप्लिकेशन प्रोग्राम (जिसमें जीरो बाइट हो सकता है) को टेबल के बाहर ले जाएंगे। प्रत्येक पुनरावृत्ति पर, हम टेबल से बाइट पढ़ते हैं और यदि यह शून्य नहीं है, तो इसे स्टैक पर धक्का दें। शून्य बाइट पढ़ें - लूप से बाहर निकलने की स्थिति।

यहाँ रिट कमांड का मतलब दो बाइट्स में निहित पते पर नियंत्रण पास करना है जो स्टैक पर अंतिम था। अब बूटलोडर कोड पर विचार करें:

; boot_EEPROM $0D($88) segment byte at 4067-4089 'bootE_rev0D_88' ; segment byte at 417B-4189 'bootE_rev0D_88' ; $4067 terminator RAM dc.b $00 ; [00] ; $4068 ($03E0) {RAM END - 31} ; {$0400 - (bootE_go_adr - bootE_start) } dc.w $03E2 ; [03 E2] $4067 - $3C85 = $03E2 ; UART 96001N8 ; BREAK $0D bootE_start: ; $406A ($03E2) {RAM END - 29} ld A, #%00001101 ; [A6 0D] ld UART1_BRR1, A ; [C7 52 32] ld UART1_CR2, A ; [C7 52 35] ld UART1_DR, A ; [C7 52 31] ; 243 ; n ; $4075 ($03ED) {RAM END - 18} bootE_rx_byte: incw X ; [5C] jreq bootE_exit ; [27 0C] btjf UART1_SR, #5, bootE_rx_byte ; [72 0B 52 30 F8] push UART1_DR ; [3B 52 31] ; clrw X ; [5F] inc A ; [4C] jrne bootE_rx_byte ; [26 F2] ; ; $02F1 ( $FE $02) ret ; [81] ; $4084 ($03FC) {RAM END - 3} bootE_exit: jp [bootE_go_adr] ; [72 CC 40 88] RAM END ; ; $4088 RAM bootE_go_adr: dc.w main_flash ; [80 08]

स्टैक की प्रतिलिपि बनाने के बाद कोड के पते कोष्ठक में दिखाए जाते हैं। पहला एक शून्य बाइट है; मेमोरी में रैम की नकल नहीं की जाती है। निम्नलिखित बूटलोडर को नियंत्रण के हस्तांतरण का पता है, वास्तव में, यह रैम मेमोरी में अगले सेल का पता है। यह जोड़ी स्टैक पर मिलती है, लेकिन फिर इसे होस्ट प्रोग्राम से अगले डंप के कोड द्वारा अनावश्यक के रूप में ओवरराइट किया जाता है। एप्लिकेशन के नियंत्रण हस्तांतरण पते के साथ एक जोड़ी को छोड़कर, बाद के सभी कोड को भी स्टैक पर कॉपी किया जाता है

इसके बाद UART का आरंभ है। यहां तीनों रजिस्टरों में एक ही नंबर $ 0D रखा गया है। पहले मामले में, यह UART की गति (16000000/8/9600/16 = 13) है। दूसरे मामले में, यह ट्रांसमिशन / रिसेप्शन की अनुमति है, यहां एक स्टीम लोकोमोटिव ने BREAK इवेंट की एक बार की पीढ़ी को पकड़ा। बाद के मामले में, यह लोडर के होस्ट संस्करण को प्रोग्राम में भेज रहा है। वास्तव में, होस्ट प्रोग्राम को दो बाइट्स $ 00 (ईवेंट BREAK) और $ 0D (बूटलोडर का संस्करण संख्या) प्राप्त होगा - यह एक संकेत है कि आप एक कोड के साथ एक डंप भेज सकते हैं।

$ 0D की सामग्री के साथ A रजिस्टर करें और फिर प्राप्त बाइट्स के एक काउंटर के कार्यों को करता है और यह उन्हें शून्य की वृद्धि के साथ गिनता है, जो 243 प्राप्त बाइट्स के बराबर है। यह इस आकार के साथ है कि होस्ट प्रोग्राम को कोड के साथ डंप भेजना चाहिए।

प्रारंभिक कॉपीिस्ट में इंडेक्स रजिस्टर X $ 4068 तक गिना जाता है। अब यह शून्य (49048 अभी भी शेष) में वृद्धि होगी, बूटलोडर को आवंटित समय की गिनती। इस समय के दौरान, बूटलोडर के पास डंप को आकार में 243 बाइट्स के कोड के साथ स्वीकार करने का समय होना चाहिए और इसे स्टैक पर आगे रखें और इसे नियंत्रण स्थानांतरित करें। अन्यथा, नियंत्रण आवेदन कार्यक्रम में स्थानांतरित कर दिया जाएगा और आपको फिर से रीसेट बटन दबाकर होस्ट प्रोग्राम को पुनरारंभ करना होगा।

प्राप्त डंप पर नियंत्रण स्थानांतरित करने के बाद, बूटलोडर कोड स्टैक पर रहता है और फिर से नियंत्रण लेता है जब होस्ट प्रोग्राम कोड के साथ डंप को बदलने का फैसला करता है। एक कोड के साथ किसी भी प्राप्त डंप को $ 02ED ... $ 03DF के पते पर स्टैक पर स्थित है और पता $ 02F0 पर नियंत्रण रखता है। बूटलोडर कोड $ 03E0 ... $ 03FF के पते पर स्टैक पर स्थित है, शुरू में यह पते पर $ 03E0 पर नियंत्रण रखता है, और यदि आवश्यक हो, तो कोड के साथ डंप को पते पर $ 03E8 कहा जाता है।

एप्लिकेशन को कंट्रोल ट्रांसफर कमांड $ 03FB पर स्टैक पर है।

वर्तमान डंप द्वारा पता $ 03FF के साथ एक सेल का उपयोग किया जा सकता है।

STM8 संस्करण में प्रारंभिक कोपियर और बूटलोडर का पूरा स्रोत कोड $ 4039 में EEPROM मेमोरी में एक टेबल के साथ $ 0D ... $ 405C ($ 4139 ... $ 415C, $ 4239 ... $ 2525C)।

फ़ाइल bootF_rev0D_5A.asm: stm8/ TITLE “bootF_rev0D_5A.asm” MOTOROLA WORDS .NOLIST ; #include "STM8S003F.inc" #include "STM8S103F.inc" .LIST ; boot_EEPROM $0D($5A) segment byte at 4039-405C 'bootE_rev0D_405A' ; STM8S003F ; segment byte at 4139-415C 'bootE_rev0D_415A' ; segment byte at 4239-425C 'bootE_rev0D_425A' ; $403A9 ($03DD) {RAM END - 34} terminator RAM ????? dc.b $00 ; [00] ; $403A ($03DE) {RAM END - 33} ; {$0400 - (bootE_go_adr - bootE_start - 1) } dc.w $03E0 ; [03 E0] ; UART 96001N8 ; BREAK $0D bootE_start: ; $403C ($03E0) {RAM END - 31} ld A, #%00001101 ; [A6 0D] ld UART1_BRR1, A ; [C7 52 32] ld UART1_CR2, A ; [C7 52 35] ; $4044 ($03E8) {RAM END - 23} ld UART1_DR, A ; [C7 52 31] ; 243 ; n ; $40487 ($03EB) {RAM END - 20} bootE_rx_byte: incw X ; [5C] jreq bootE_exit ; [27 0C] btjf UART1_SR, #5, bootE_rx_byte ; [72 0B 52 30 F8] push UART1_DR ; [3B 52 31] clrw X ; [5F] inc A ; [4C] jrne bootE_rx_byte ; [26 F2] ; ; $02EF ( $EF $02) ; $4056 ($03FA) {RAM END - 5} ret ; [81] ; $4057 ($03FB) {RAM END - 4} bootE_exit: jp [bootE_go_adr] ; [72 CC 40 5B] {RAM END - 1} ; ($03FF) RAM END ; ; $405B RAM bootE_go_adr: dc.w main_flash ; [80 08] ; boot_FLASH $0D($5A) ; $405A($415A,$425A) ; $00 ; segment byte at 8000-8007 'bootF_rev0D' ; $8000 RESET Reset vector dc.b $AE, $40 ; [AE 40 5A] ldw X,#$405A ; STM8S003F ; dc.b $AE, $41 ; [AE 41 5A] ldw X,#$415A ; dc.b $AE, $42 ; [AE 42 5A] ldw X,#$425A cycle: ; ; dec X ldw X,#$405A($415A,$425A) decw X ; [5A] push A ; [88] ; $8004 TRAP Software interrupt ld A, (X) ; [F6] jrne cycle ; [26 FB] ret ; [81] ; $8008 TLI IRQ0 External top level interrupt ; segment byte at 8008 'main_flash' main_flash: jra * ; [20 FE] ; end ; bootF_rev0D_5A.asm

प्रारंभिक कॉपीस्टार और बूटलोडर का पूरा स्रोत कोड STM8 संस्करण $ 0D में EEPROM मेमोरी में एक टेबल के साथ $ 4065 ... $ 4088 ($ 4165 ... $ 4188) है।

फ़ाइल bootF_rev0D_88.asm: stm8/ TITLE “bootF_rev0D_88.asm” MOTOROLA WORDS .NOLIST ; #include "STM8S003F.inc" #include "STM8S103F.inc" .LIST ; boot_EEPROM $0D($88) segment byte at 4065-4088 'bootE_rev0D_88' ; segment byte at 4165-4188 'bootE_rev0D_88' ; $4065 terminator RAM dc.b $00 ; [00] ; $4066 ($03DE) {RAM END - 33} ; {$0400 - (bootE_go_adr - bootE_start) } dc.w $03E0 ; [03 E0] ; UART 9600 1N8 ; BREAK $0D bootE_start: ; $4068 ($03E0) {RAM END - 31} ld A, #%00001101 ; [A6 0D] ld UART1_BRR1, A ; [C7 52 32] ld UART1_CR2, A ; [C7 52 35] ; $4070 ($03E8) {RAM END - 23} ld UART1_DR, A ; [C7 52 31] ; 243 ; n ; $4073 ($03EB) {RAM END - 20} bootE_rx_byte: incw X ; [5C] jreq bootE_exit ; [27 0C] btjf UART1_SR, #5, bootE_rx_byte ; [72 0B 52 30 F8] push UART1_DR ; [3B 52 31] clrw X ; [5F] inc A ; [4C] jrne bootE_rx_byte ; [26 F2] ; ; $02EF ( $EF $02) ; $4082 ($03FA) {RAM END - 5} ret ; [81] ; $4083 ($03FB) {RAM END - 4} bootE_exit: jp [bootE_go_adr] ; [72 CC 40 87] {RAM END - 1} ; ($03FF) RAM END ; ; $4087 ($4088 ) RAM bootE_go_adr: dc.w main_flash ; [80 08] ; boot_FLASH $0D($88) ; $4087($4187) ; $00 ; segment byte at 8000-8007 'bootF_rev0D' ; $8000 RESET Reset vector dc.b $AE, $40 ; [AE 40] ldw X,#$4088 ; dc.b $AE, $41 ; [AE 41] ldw X,#$4188 cycle: ; ; push A ldw X,#$4088($4188) push A ; [88] decw X ; [5A] ; $8004 TRAP Software interrupt ld A, (X) ; [F6] jrne cycle ; [26 FB] ret ; [81] ; $8008 TLI IRQ0 External top level interrupt ; segment byte at 8008 'main_flash' main_flash: jra * ; [20 FE] end ; bootF_rev0D_88.asm

हम STM8 की फ्लैश मेमोरी में निष्पादन के लिए सबसे सरल एप्लिकेशन प्रोग्राम की रूपरेखा तैयार करते हैं।

फ़ाइल main_rev0D.asm: stm8/ TITLE “main_rev0D.asm” MOTOROLA WORDS .NOLIST #include "STM8S103F.inc" .LIST ; segment byte at 8008-9FFF 'main_flash' main_flash: main_cycle: ; bset PB_DDR,#5 ; bset PB_CR1,#5 ; callr flash_delay ; bres PB_DDR,#5 ; bres PB_CR1,#5 ; callr flash_delay jra main_cycle flash_delay: ldw X, #35000 flash_delay_cycle: decw X jrne flash_delay_cycle ret end ; main_rev0D.asm

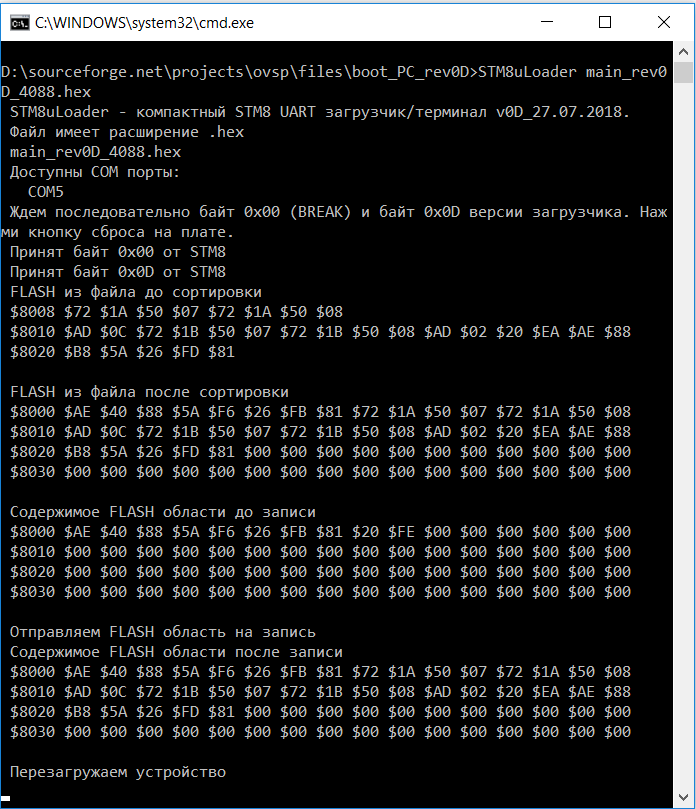

STM8 में सीवर प्रोग्रामर बूटलोडर। हम बोर्ड को USB-TTL एडाप्टर (UART) से जोड़ते हैं। बैच फ़ाइल

runSTM8uLoader.bat चलाएँ। बोर्ड पर रीसेट बटन दबाएं। हम परिणाम का निरीक्षण करते हैं:

एप्लिकेशन कोड को फ्लैश मेमोरी में लोडर द्वारा फ्लैश किया जाता है, डिवाइस रिबूट करता है। एलईडी झपकने लगती है।

डंप स्रोत कोड के उदाहरण जो होस्ट प्रोग्राम रैम मेमोरी में निष्पादन के लिए लोडर को भेजता है:

फ़ाइल Read_128000v0D.asm: stm8/ TITLE "Read_128000v0D.asm" MOTOROLA WORDS .NOLIST #include "STM8S103F3P.inc" .LIST ; 243 ; $02EE...$03DF ; ( $03DF:$03E0 ) ; $02F0 ; $03E1...$03FE ; $03E1 ( 9600, A<=$0D SP<=$03E0 X<=$0000) ; $03E9 ( , A<=$0D SP<=$03E8 X<=$0000) ; $03FB segment byte at 0000-00F2 'ram0' dc.w $02F0 start: ; UART1 / 9600, (8 , , 1 ) mov UART1_BRR2, #0 ; [35 00 52 33] Fmaster=16/8=2 128000 mov UART1_BRR1, #1 ; [35 0D 52 32] Fmaster=16/8=2 128000 mov UART1_CR2, #%00001100 ; [35 0C 52 35] UART1_CR2.TEN <- 1 UART1_CR2.REN <- 1 / main_cycle: wait_byte_adrH_cmnd: btjf UART1_SR, #5, wait_byte_adrH_cmnd ld A, UART1_DR cp A, #$EF JRUGT wait_byte_cmd_test ; Relative jump if Unsigned Greater Than ld XH, A ; XH ld UART1_DR, A ; tx_echo_adrH: btjf UART1_SR, #7, tx_echo_adrH ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty wait_byte_adrL: btjf UART1_SR, #5, wait_byte_adrL ld A, UART1_DR ld XL, A ; XL wait_byte_cntr: btjf UART1_SR, #5, wait_byte_cntr ld A, #$00 ld YH, A ; ld A, UART1_DR ld YL, A ; ; bset PB_DDR,#5 ; bset PB_CR1,#5 ; ; read_block_cycle: ld A, (X) ld UART1_DR, A wait_tx: btjf UART1_SR, #7, wait_tx ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty incw X decw Y jrne read_block_cycle ; bres PB_DDR,#5 ; bres PB_CR1,#5 ; jra main_cycle ; $F0 wait_byte_cmd_test: cp A, #$F5 ; jreq echo_F5cmd wait_tx_err: mov UART1_DR, #$F1 ; btjf UART1_SR, #7, wait_tx_err ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty jra main_cycle echo_F5cmd: ld UART1_DR, A ; wait_tx_echo_F5cmd: btjf UART1_SR, #7, wait_tx_echo_F5cmd ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty ; GoAdr wait_byte_adrH_toM; btjf UART1_SR, #5, wait_byte_adrH_toM mov $03E7, UART1_DR wait_byte_adrL_toM; btjf UART1_SR, #5, wait_byte_adrL_toM mov $03E8, UART1_DR ; SP wait_byte_adrH_toSP; btjf UART1_SR, #5, wait_byte_adrH_toSP ld A, UART1_DR ld XH, A wait_byte_adrL_toSP; btjf UART1_SR, #5, wait_byte_adrL_toSP ld A, UART1_DR ld XL, A ldw SP, X ; Y wait_byte_adrH_toY; ; btjf UART1_SR, #5, wait_byte_adrH_toY ; ld A, UART1_DR ; ld YH, A wait_byte_adrL_toY; ; btjf UART1_SR, #5, wait_byte_adrL_toY ; ld A, UART1_DR ; ld YL, A ; X wait_byte_adrH_toX; btjf UART1_SR, #5, wait_byte_adrH_toX ld A, UART1_DR ld XH, A wait_byte_adrL_toX; btjf UART1_SR, #5, wait_byte_adrL_toX ld A, UART1_DR ld XL, A ; A wait_byte_cntr_toA; btjf UART1_SR, #5, wait_byte_cntr_toA ld A, UART1_DR jp [$03E7.w] SKIP 59, $00 ; dc.b $00 dc.b $00 end ; Read_128000v0D.asm

फाइल लिखेंब्लॉक_फ्लैश_128000v0D.asm: stm8/ TITLE "WriteBlocks_FLASH_128000v0D.asm" MOTOROLA WORDS .NOLIST #include "STM8S103F3P.inc" .LIST ; 243 ; $02EE...$03DF ; ( $03DF:$03E0 ) ; $02F0 ; $03E1...$03FE ; $03E1 ( 9600, A<=$0D SP<=$03E0 X<=$0000) ; $03E9 ( , A<=$0D SP<=$03E8 X<=$0000) ; $03FB segment byte at 0000-00F2 'ram0' dc.w $02F0 start: ; UART1 / 9600, (8 , , 1 ) mov UART1_BRR2, #0 ; [35 00 52 33] Fmaster=16/8=2 128000 mov UART1_BRR1, #1 ; [35 0D 52 32] Fmaster=16/8=2 128000 mov UART1_CR2, #%00001100 ; [35 0C 52 35] UART1_CR2.TEN <- 1 UART1_CR2.REN <- 1 / main_cycle: wait_byte_adrH_cmnd: btjf UART1_SR, #5, wait_byte_adrH_cmnd ld A, UART1_DR cp A, #$F0 JRUGE wait_byte_cmd_test ; Relative jump if Unsigned Greater or Equal ld XH, A ; XH ld UART1_DR, A ; tx_echo_adrH: btjf UART1_SR, #7, tx_echo_adrH ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty wait_byte_adrL: btjf UART1_SR, #5, wait_byte_adrL ld A, UART1_DR ld XL, A ; XL wait_byte_cntr: btjf UART1_SR, #5, wait_byte_cntr ; mov $03FF, UART1_DR write_block_cycle: ldw Y, #64 ; ; unlock FLASH memory (writing the correct MASS keys) mov FLASH_PUKR, #$56 ; Write $56 then $AE in FLASH_PUKR($5062) mov FLASH_PUKR, #$AE ; If wrong keys have been entered, another key programming sequence can be issued without resetting the device. ; FLASH Block programming mode mov FLASH_CR2, #$01 mov FLASH_NCR2, #$FE ; ; FLASH Word programming mode ; mov FLASH_CR2, #$40 ; mov FLASH_NCR2, #$BF ; else FLASH byte programming ; bset PB_DDR,#5 ; bset PB_CR1,#5 ; ; ; wait_rx_byte: btjf UART1_SR, #5, wait_rx_byte ld A, UART1_DR ld (X), A incw X decw Y jrne wait_rx_byte mov UART1_DR, #$FA ; OK wait_tx_OK_FA: btjf UART1_SR, #7, wait_tx_OK_FA ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty ; bres PB_DDR,#5 ; bres PB_CR1,#5 ; dec $03FF jrne write_block_cycle jra main_cycle ; $F0 wait_byte_cmd_test: cp A, #$F5 ; boot_OPTION jreq echo_F5cmd wait_tx_err: mov UART1_DR, #$F1 ; wait_tx_err_F1: btjf UART1_SR, #7, wait_tx_err_F1 ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty jra main_cycle echo_F5cmd: ld UART1_DR, A ; boot_OPTION wait_tx_echo_F5cmd: btjf UART1_SR, #7, wait_tx_echo_F5cmd ; skip if UART1_SR.TXE = 0 TXE: Transmit data register empty ; GoAdr wait_byte_adrH_toM; btjf UART1_SR, #5, wait_byte_adrH_toM mov $03E7, UART1_DR wait_byte_adrL_toM; btjf UART1_SR, #5, wait_byte_adrL_toM mov $03E8, UART1_DR ; SP wait_byte_adrH_toSP; btjf UART1_SR, #5, wait_byte_adrH_toSP ld A, UART1_DR ld XH, A wait_byte_adrL_toSP; btjf UART1_SR, #5, wait_byte_adrL_toSP ld A, UART1_DR ld XL, A ldw SP, X ; Y wait_byte_adrH_toY; ; btjf UART1_SR, #5, wait_byte_adrH_toY ; ld A, UART1_DR ; ld YH, A wait_byte_adrL_toY; ; btjf UART1_SR, #5, wait_byte_adrL_toY ; ld A, UART1_DR ; ld YL, A ; X wait_byte_adrH_toX; btjf UART1_SR, #5, wait_byte_adrH_toX ld A, UART1_DR ld XH, A wait_byte_adrL_toX; btjf UART1_SR, #5, wait_byte_adrL_toX ld A, UART1_DR ld XL, A ; A wait_byte_cntr_toA; btjf UART1_SR, #5, wait_byte_cntr_toA ld A, UART1_DR jp [$03E7.w] SKIP 28, $00 ; dc.b $00 dc.b $00 end ; WriteBlocks_FLASH_128000v0D.asm

फ़ाइल Reset_128000v0D.asm: stm8/ TITLE MOTOROLA WORDS .NOLIST #include .LIST ; 243 ; $02EE...$03DF ; ( $03DF:$03E0 ) ; $02F0 ; $03E1...$03FE ; $03E1 ( 9600, A<=$0D SP<=$03E0 X<=$0000) ; $03E9 ( , A<=$0D SP<=$03E8 X<=$0000) ; $03FB segment byte at 0000-00F2 'ram0' dc.w $02F0 start: ; RESET ldw X, #$03FF ldw SP, X clrw X clrw Y clr A jp $8000 SKIP 230, $00 end ; Reset_128000v0D.asm

होस्ट प्रोग्राम के स्रोत कोड में, ये समान डंप निम्न रूप में मौजूद हैं:

public readonly static byte[] Read_128000v0D = { 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xE7, 0x03, 0xCC, 0x72, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x97, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x95, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x94, 0x97, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x95, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xE8, 0x03, 0x31, 0x52, 0x55, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xE7, 0x03, 0x31, 0x52, 0x55, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xC7, 0xA5, 0x20, 0xF7, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xF1, 0x35, 0x0B, 0x27, 0xF5, 0xA1, 0xB4, 0x20, 0x08, 0x50, 0x1B, 0x72, 0x07, 0x50, 0x1B, 0x72, 0xF2, 0x26, 0x5A, 0x90, 0x5C, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xC7, 0xF6, 0x08, 0x50, 0x1A, 0x72, 0x07, 0x50, 0x1A, 0x72, 0x97, 0x90, 0x31, 0x52, 0xC6, 0x95, 0x90, 0x00, 0xA6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x97, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xC7, 0x95, 0x40, 0x22, 0xEF, 0xA1, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x35, 0x52, 0x0C, 0x35, 0x32, 0x52, 0x01, 0x35, 0x33, 0x52, 0x00, 0x35, 0xF0, 0x02 };

public readonly static byte[] WriteBlocks_FLASH_128000v0D = { 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0xE7, 0x03, 0xCC, 0x72, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x97, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x95, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x94, 0x97, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x95, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xE8, 0x03, 0x31, 0x52, 0x55, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xE7, 0x03, 0x31, 0x52, 0x55, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xC7, 0x86, 0x20, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xF1, 0x35, 0x0B, 0x27, 0xF5, 0xA1, 0x95, 0x20, 0xBF, 0x26, 0xFF, 0x03, 0x5A, 0x72, 0x08, 0x50, 0x1B, 0x72, 0x07, 0x50, 0x1B, 0x72, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xFA, 0x35, 0xF2, 0x26, 0x5A, 0x90, 0x5C, 0xF7, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x08, 0x50, 0x1A, 0x72, 0x07, 0x50, 0x1A, 0x72, 0x5C, 0x50, 0xFE, 0x35, 0x5B, 0x50, 0x01, 0x35, 0x62, 0x50, 0xAE, 0x35, 0x62, 0x50, 0x56, 0x35, 0x40, 0x00, 0xAE, 0x90, 0xFF, 0x03, 0x31, 0x52, 0x55, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x97, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0xFB, 0x30, 0x52, 0x0F, 0x72, 0x31, 0x52, 0xC7, 0x95, 0x5F, 0x24, 0xF0, 0xA1, 0x31, 0x52, 0xC6, 0xFB, 0x30, 0x52, 0x0B, 0x72, 0x35, 0x52, 0x0C, 0x35, 0x32, 0x52, 0x01, 0x35, 0x33, 0x52, 0x00, 0x35, 0xF0, 0x02 };

public readonly static byte[] Reset_128000v0D = { 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x00, 0x80, 0xCC, 0x4F, 0x5F, 0x90, 0x5F, 0x94, 0xFF, 0x03, 0xAE, 0xF0, 0x02 };

पिछला लेख:

"फ्लैश मेमोरी में 18 बाइट्स को आकार देने के लिए एसटीएम 8 के लिए बूटलोडर को कैसे संपीड़ित करें ।

"वेबसाइट

http://nflic.ru/STM8/STM8uLoader/000.html के साथ ।

Https://sourceforge.net/projects/ovsp पर प्रोजेक्ट

करें ।

Https://github.com/ovsp/STM8uLoader पर प्रोजेक्ट

करें ।

मैं पाठकों से लक्षित आलोचना और आगे की कमी के लिए सुझाव मांगता हूं।