सभी को नमस्कार!

एक बार, ग्राहकों ने मुझसे पूछा कि क्या मेरी परियोजनाओं में मेरे पास पूर्णांक एफएफटी है, जिसके लिए मैंने हमेशा जवाब दिया कि यह

पहले से ही दूसरों द्वारा तैयार किए गए, यद्यपि मुड़े हुए के रूप में

किया गया था , लेकिन नि: शुल्क आईपी कोर (एलेटा / एक्सिलैक्स) - इसे लें और इसका उपयोग करें। हालांकि, ये कोर

इष्टतम नहीं हैं, "सुविधाओं" का एक सेट है और इसे और अधिक परिष्कृत करने की आवश्यकता है। इस संबंध में, एक और नियोजित छुट्टी पर चले गए, जो मैं औसत खर्च नहीं करना चाहता था, मैंने पूर्णांक एफएफटी के विन्यास योग्य कर्नेल को लागू करना शुरू कर दिया।

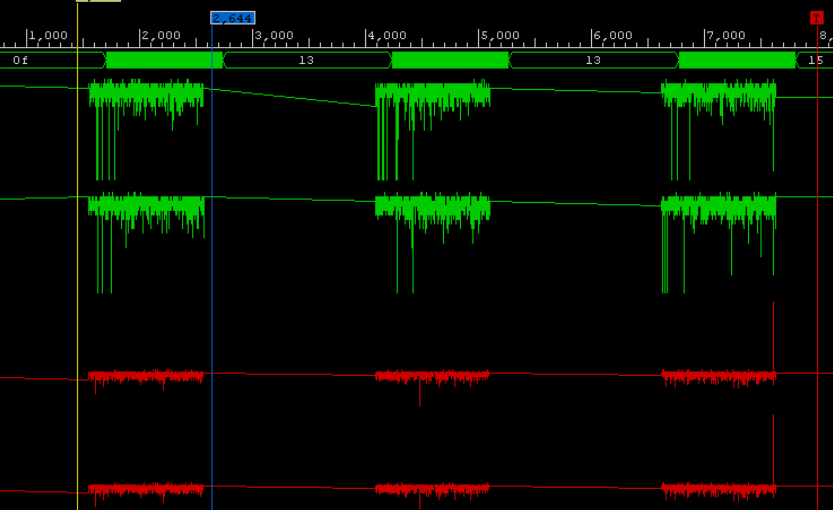

KDPV (डेटा ओवरफ़्लो त्रुटियों को डीबग करने की प्रक्रिया)

KDPV (डेटा ओवरफ़्लो त्रुटियों को डीबग करने की प्रक्रिया)लेख में मैं आपको यह बताना चाहता हूं कि आधुनिक FPGA क्रिस्टल पर पूर्णांक प्रारूप में तेजी से फूरियर रूपांतरण की गणना करते समय किन तरीकों और साधनों के गणितीय संचालन का एहसास होता है। किसी भी FFT का आधार "तितली" नामक एक नोड है। तितली गणितीय कार्यों को लागू करती है - इसके अलावा, गुणा और घटाव। यह "तितली" और इसके समाप्त नोड्स के कार्यान्वयन के बारे में है कि कहानी पहले जाएगी। आधुनिक Xilinx FPGA परिवारों के आधार पर - यह Ultrascale और Ultrascale + श्रृंखला है, साथ ही साथ पुरानी श्रृंखला 6- (Virtex) और 7- (Artix, Kintex, Virtex) प्रभावित हैं। आधुनिक परियोजनाओं में पुरानी श्रृंखला 2018 में कोई दिलचस्पी नहीं है। लेख का उद्देश्य एफएफटी उदाहरण का उपयोग करके डिजिटल सिग्नल प्रोसेसिंग के कस्टम कर्नेल के कार्यान्वयन की सुविधाओं को प्रकट करना है।

परिचय

यह किसी के लिए भी रहस्य नहीं है कि एफएफटी लेने के लिए एल्गोरिदम डिजिटल सिग्नल प्रोसेसिंग इंजीनियरों के जीवन में दृढ़ता से उलझे हुए हैं, और इसलिए इस उपकरण की लगातार आवश्यकता है। Altera / Xilinx जैसे अग्रणी FPGA निर्माताओं में पहले से ही लचीले विन्यास योग्य FFT / IFFT कोर हैं, लेकिन उनकी कई सीमाएँ और विशेषताएं हैं, और इसलिए मुझे अपने अनुभव का एक से अधिक बार उपयोग करना पड़ा है। इसलिए इस बार मुझे FPGA पर मूलांक -2 योजना के अनुसार पूर्णांक प्रारूप में FFT लागू करना पड़ा।

अपने अंतिम लेख में, मैंने पहले से ही फ्लोटिंग पॉइंट फॉर्मेट में

एफएफटी किया था , और वहां से आपको पता है कि एफएफटी को लागू करने के लिए दोहरे समानांतरवाद के साथ एल्गोरिथ्म का उपयोग किया जाता है, यानी

कर्नेल एक ही आवृत्ति पर दो जटिल नमूनों को संसाधित कर सकता है । यह एक प्रमुख FFT सुविधा है जो Xilinx FFT तैयार कर्नेल में उपलब्ध नहीं है।

उदाहरण: 800 मेगाहर्ट्ज की आवृत्ति पर जटिल संख्याओं के इनपुट स्ट्रीम के निरंतर संचालन के लिए एक एफएफटी नोड विकसित करना आवश्यक है। Xilinx का कोर इसे नहीं खींचेगा (आधुनिक FPGAs में प्राप्त करने योग्य प्रसंस्करण घड़ी आवृत्तियां 300-400 मेगाहर्ट्ज के क्रम की हैं), या इसे किसी भी तरह से इनपुट स्ट्रीम को कम करने की आवश्यकता होगी। कस्टम कोर आपको 800 मेगाहर्ट्ज पर एक एकल नमूने के बजाय 400 मेगाहर्ट्ज की आवृत्ति पर दो इनपुट नमूनों को देखने की अनुमति देता है।

Xilinx FFT कोर का एक और

ऋण बिट-रिवर्स ऑर्डर में इनपुट स्ट्रीम को स्वीकार करने में असमर्थता है । इस संबंध में, एक सामान्य क्रम में डेटा को पुनर्व्यवस्थित करने के लिए एक विशाल FPGA चिप मेमोरी संसाधन खर्च किया जाता है। संकेतों के तेजी से दृढ़ीकरण के कार्यों के लिए, जब दो एफएफटी नोड एक दूसरे के पीछे खड़े होते हैं, तो यह एक महत्वपूर्ण क्षण बन सकता है, अर्थात, कार्य केवल चयनित एफपीजीए चिप में झूठ नहीं होगा। कस्टम एफएफटी कोर आपको इनपुट पर सामान्य क्रम में डेटा प्राप्त करने की अनुमति देता है, और इसे बिट-रिवर्स मोड में आउटपुट करता है, जबकि उलटा एफएफटी का कोर - इसके विपरीत, बिट-रिवर्स ऑर्डर में डेटा प्राप्त करता है, और इसे सामान्य मोड में आउटपुट करता है। डेटा क्रमचय के लिए दो बफ़र्स एक ही बार में सहेजे जाते हैं !!!

चूंकि इस लेख की अधिकांश सामग्री

पिछले एक के साथ ओवरलैप हो सकती

है , इसलिए मैंने एफएफटी के कार्यान्वयन के लिए एफपीजीए पर पूर्णांक प्रारूप में गणितीय संचालन के विषय पर ध्यान केंद्रित करने का निर्णय लिया।

FFT कर्नेल पैरामीटर

- एनएफएफटी - तितलियों की संख्या (एफएफटी लंबाई),

- DATA_WIDTH - इनपुट डेटा की थोड़ी गहराई (4-32),

- TWDL_WIDTH - मोड़ कारकों की गहराई (8-27)।

- श्रृंखला - FPGA परिवार को परिभाषित करता है जिस पर FFT लागू किया गया है ("नया" - Ultrascale, "OLD" - 6/7 Xilinx FPGA श्रृंखला)।

सर्किट में किसी भी अन्य लिंक की तरह, एफएफटी में इनपुट कंट्रोल पोर्ट हैं - एक घड़ी सिग्नल और एक रीसेट, साथ ही इनपुट और आउटपुट डेटा पोर्ट। इसके अलावा, USE_FLY सिग्नल का उपयोग कर्नेल में किया जाता है, जो आपको डीबगिंग प्रक्रियाओं के लिए FFT तितलियों को गतिशील रूप से बंद करने या मूल इनपुट स्ट्रीम देखने की अनुमति देता है।

नीचे दी गई तालिका FPGA संसाधनों की मात्रा को दर्शाती है, जो DATA_WIDTH = 16 और दो बिट्स TWDL_WIDTH = 16 और 24 बिट्स के लिए NFFT FFT की लंबाई पर निर्भर करती है।

NFFT = 64K में कोर एक किन्टेक्स -7 क्रिस्टल (410T) पर प्रसंस्करण आवृत्ति

FREQ = 375 मेगाहर्ट्ज पर स्थिर है।

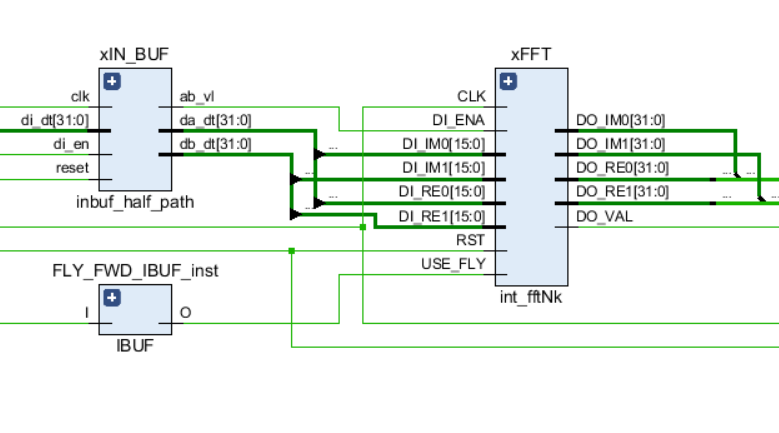

परियोजना की संरचना

FFT नोड का योजनाबद्ध ग्राफ निम्नलिखित आकृति में दिखाया गया है:

कुछ घटकों की विशेषताओं को समझने की सुविधा के लिए, मैं प्रोजेक्ट फाइलों की सूची और उनके संक्षिप्त विवरण को एक श्रेणीबद्ध क्रम में दूंगा:

- एफएफटी गुठली:

- int_fftNk - FFT नोड, रेडिक्स -2 सर्किट, फ्रीक्वेंसी डिक्मिनेशन (DIF), इनपुट स्ट्रीम सामान्य है, आउटपुट स्ट्रीम बिट-रिवर्स है।

- int_ifftNk - OBPF नोड, मूलांक -2 सर्किट, समय विघटन (DIT), इनपुट स्ट्रीम बिट-रिवर्स है, आउटपुट स्ट्रीम सामान्य है।

- तितलियों:

- int_dif2_fly - तितली मूलांक -2, आवृत्ति में गिरावट ,

- int_dit2_fly - तितली मूलांक -2, समय में विघटन ,

- जटिल गुणक:

- int_cmult_dsp48 - सामान्य विन्यास गुणक, में शामिल हैं:

- int_cmult18x25_dsp48 - डेटा और रोटेशन कारकों की छोटी बिट गहराई के लिए गुणक,

- int_cmult_dbl18_dsp48 - दोगुना गुणक, 18 बिट तक मोड़ कारकों की थोड़ी चौड़ाई,

- int_cmult_dbl35_dsp48 - दोगुनी गुणक, घूर्णन कारकों की बिट चौड़ाई 25 * बिट्स तक,

- int_cmult_trpl18_dsp48 - ट्रिपल गुणक, 18 बिट तक मोड़ कारकों की क्षमता,

- int_cmult_trpl52_dsp48 - ट्रिपल गुणक, 25 * बिट्स तक घूर्णन कारकों की क्षमता,

- मल्टीप्लायरों:

- mlt42x18_dsp48e1 - 42 और 18 बिट तक डीएसपी 48 ई 1 पर आधारित ऑपरेंड के बिट्स के साथ एक गुणक

- mlt59x18_dsp48e1 - ऑपरेंड बिट्स के साथ 59 तक और 18 बिट्स DSP2E1 पर आधारित है,

- mlt35x25_dsp48e1 - DSP48E1 पर आधारित 35 और 25 बिट्स के ऑपरेंड के बिट्स के साथ एक गुणक

- mlt52x25_dsp48e1 - 52 और 25 बिट तक डीएसपी 48 ई 1 पर आधारित ऑपरेंड के बिट्स के साथ एक गुणक

- mlt44x18_dsp48e2 - DSP48482 पर आधारित 44 और 18 बिट्स के ऑपरेंड के बिट्स के साथ गुणक,

- mlt61x18_dsp48e2 - ऑपरिपल बिट्स के साथ गुणक 61 और 18 बिट्स डीएसपीईईई 2 पर आधारित है,

- mlt35x27_dsp48e2 - 35 और 27 बिट तक के ऑपरेंड बिट्स के साथ गुणक DSPEEE2 पर आधारित है।

- mlt52x27_dsp48e2 डीएसपी 482 डी 2 पर आधारित ऑपरेंड बिट्स 52 और 27 बिट्स के साथ एक गुणक है।

- योजक:

- int_addsub_dsp48 - सार्वभौमिक योजक, ओपेरा बिट्स 96 बिट्स तक।

- विलंब रेखाएँ:

- int_delay_line - देरी की आधार रेखा, तितलियों के बीच डेटा का क्रमांकन प्रदान करता है,

- int_align_fft - FFT तितली के इनपुट पर इनपुट डेटा और टर्निंग फैक्टर का संरेखण,

- int_align_fft - OBPF तितली के इनपुट पर इनपुट डेटा और टर्निंग फैक्टर का संरेखण,

- घूर्णन कारक:

- rom_twiddle_int - रोटरी कारकों का एक जनरेटर, एक निश्चित लंबाई से एफएफटी डीएसपी एफपीजीए कोशिकाओं पर आधारित गुणांक मानता है,

- row_twiddle_tay - टेलर श्रृंखला (NFFT> 2K) ** का उपयोग करके रोटरी कारकों का जनरेटर।

- डेटा बफ़र:

- inbuf_half_path - इनपुट बफर, सामान्य मोड में स्ट्रीम प्राप्त करता है और FFT *** की आधी लंबाई द्वारा स्थानांतरित नमूनों के दो अनुक्रमों का उत्पादन करता है;

- outbuf_half_path - आउटपुट बफर, दो अनुक्रमों को इकट्ठा करता है और एफएफटी की लंबाई के बराबर एक निरंतर उत्पादन करता है,

- iobuf_flow_int2 - बफर दो मोड में काम करता है: यह इंटरलीव -2 मोड में एक स्ट्रीम प्राप्त करता है और आधी लंबाई से स्थानांतरित एफएफटी के दो अनुक्रमों का उत्पादन करता है। या इसके विपरीत, BITREV विकल्प पर निर्भर करता है।

- int_bitrev_ord प्राकृतिक ऑर्डर से बिट-रिवर्स के लिए एक सरल डेटा कनवर्टर है।

* - DSP48E1 के लिए: 25 बिट्स, DSP48E2 के लिए - 27 बिट्स।** - एफएफटी के एक निश्चित चरण से, एक निश्चित मात्रा में ब्लॉक मेमोरी का उपयोग घूर्णी गुणांक को स्टोर करने के लिए किया जा सकता है, और मध्यवर्ती गुणांकों की गणना डीएसपी 48 नोड्स द्वारा टेलर सूत्र का उपयोग करके पहले व्युत्पन्न की जा सकती है। इस तथ्य के कारण कि FFT के लिए मेमोरी संसाधन अधिक महत्वपूर्ण है, आप मेमोरी की खातिर कंप्यूटिंग इकाइयों को सुरक्षित रूप से त्याग सकते हैं।

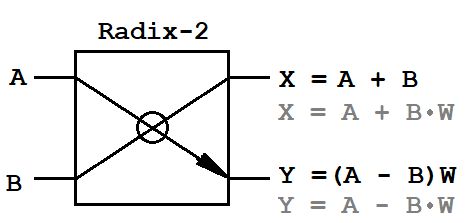

*** - इनपुट बफर और देरी लाइनों - कब्जे वाले FPGA स्मृति संसाधनों की मात्रा में एक महत्वपूर्ण योगदान देते हैं"तितली"हर कोई जो कम से कम एक बार तेजी से फूरियर ट्रांसफॉर्म एल्गोरिथ्म का सामना कर चुका है, जानता है कि यह एल्गोरिथम एक प्राथमिक ऑपरेशन पर आधारित है - एक "तितली"। यह इनपुट स्ट्रीम को ट्वीडल कारक द्वारा इनपुट को गुणा करके परिवर्तित करता है। एफएफटी के लिए दो शास्त्रीय रूपांतरण योजनाएं हैं - आवृत्ति में डीआईएफ (डीआईएफ, डेसीमेशन-इन-फ्रीक्वेंसी) और समय में डीआईएमएटी (डीआईटी, डीमिशन-इन-टाइम)। डीआईटी एल्गोरिदम को इनपुट अनुक्रम को आधी अवधि के दो अनुक्रमों में विभाजित करके और एनएफएफटी अवधि के समान और विषम नमूनों के दो अनुक्रमों में विभाजित किया जाता है। इसके अलावा, ये एल्गोरिदम तितली ऑपरेशन के लिए गणितीय कार्यों में भिन्न हैं।

ए, बी

ए, बी - जटिल नमूनों के इनपुट जोड़े,

एक्स, वाई - जटिल नमूनों के आउटपुट जोड़े,

डब्ल्यू - जटिल मोड़ कारक।

चूंकि इनपुट डेटा जटिल मात्रा में होते हैं, तितली को एक जटिल गुणक (गुणन के 4 संचालन और इसके अतिरिक्त 2 संचालन) और दो जटिल जोड़ (अतिरिक्त के 4 संचालन) की आवश्यकता होती है। यह संपूर्ण गणितीय आधार है जिसे FPGA पर लागू किया जाना चाहिए।

गुणक

यह ध्यान दिया जाना चाहिए कि FPGAs पर सभी गणितीय संचालन अक्सर अतिरिक्त कोड (2 के पूरक) में किए जाते हैं। FPGA गुणक को दो तरीकों से लागू किया जा सकता है - ट्रिगर्स और LUT टेबल का उपयोग करके तर्क पर, या विशेष DSP48 गणना इकाइयों पर, जो लंबे और दृढ़ता से सभी आधुनिक FPGAs में शामिल किए गए हैं। तार्किक ब्लॉकों पर, बूथ एल्गोरिथ्म या इसके संशोधनों का उपयोग करके गुणन को कार्यान्वित किया जाता है, एक उचित मात्रा में तार्किक संसाधन लेता है और उच्च डेटा प्रसंस्करण आवृत्तियों पर हमेशा समय की कमी को पूरा नहीं करता है। इस संबंध में, आधुनिक परियोजनाओं में एफपीजीए गुणक लगभग हमेशा डीएसपी 48 नोड्स के आधार पर और केवल कभी-कभी तर्क के आधार पर तैयार किए जाते हैं। एक DSP48 नोड एक जटिल तैयार सेल है जो गणितीय और तार्किक कार्यों को लागू करता है। बुनियादी संचालन: गुणा, जोड़, घटाव, संचय, काउंटर, तार्किक संचालन (XOR, NAND, AND, OR, NOR), वर्ग, संख्याओं की तुलना, बदलाव, आदि। निम्नलिखित आंकड़ा Xilinx Ultrascale + FPGA परिवार के लिए DSP48E2 सेल को दर्शाता है।

इनपुट पोर्ट के एक साधारण विन्यास के माध्यम से, नोड्स में गणना संचालन और नोड के अंदर देरी की स्थापना करके, आप एक उच्च गति गणितीय डेटा थ्रेशर बना सकते हैं।

ध्यान दें कि विकास के माहौल में सभी शीर्ष FPGA विक्रेताओं के पास DSP48 नोड के आधार पर गणितीय कार्यों की गणना के लिए मानक और मुफ्त आईपी कोर हैं। वे आपको आदिम गणितीय कार्यों की गणना करने और नोड के इनपुट और आउटपुट में विभिन्न देरी निर्धारित करने की अनुमति देते हैं। Xilinx के लिए, यह IP-Core "गुणक" (ver। 12.0, 2018) है, जो आपको 2 से 64 बिट तक इनपुट डेटा के किसी भी बिट गहराई में गुणक को कॉन्फ़िगर करने की अनुमति देता है। इसके अलावा, आप यह निर्दिष्ट कर सकते हैं कि गुणक कैसे लागू किया जाता है - तार्किक संसाधनों पर या अंतर्निहित DSP48 प्राइमेटिव्स पर।

पोर्ट ए और बी = 64 बिट्स पर इनपुट डेटा की थोड़ी गहराई के साथ

गुणक "खाती" कितना तर्क का अनुमान है । यदि आप नोड्स डीएसपी 48 का उपयोग करते हैं, तो उन्हें केवल 16 की आवश्यकता होगी।

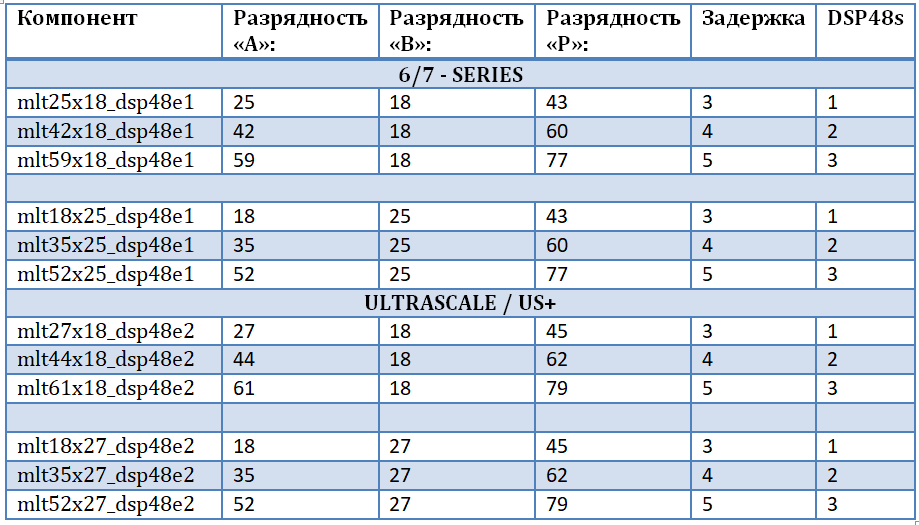

DSP48 कोशिकाओं पर मुख्य सीमा इनपुट डेटा की थोड़ी गहराई है। DSP48E1 नोड में, जो Xilinx 6 और 7 FPGAs का बेस सेल है, गुणन के लिए इनपुट पोर्ट्स की चौड़ाई: "A" 25 बिट्स है, "B" 18 बिट्स है। इसलिए, गुणा परिणाम 43-बिट संख्या है। Xilinx Ultrascale और Ultrascale + FPGA परिवार के लिए, नोड में कई बदलाव हुए हैं, विशेष रूप से, पहले बंदरगाह की क्षमता में दो बिट्स की वृद्धि हुई: "ए" - 27 बिट्स, "बी" - 18-बिट्स। इसके अलावा, नोड को ही DSP48E2 कहा जाता है।

किसी विशिष्ट परिवार और FPGA चिप से बंधे नहीं होने के लिए, "स्रोत कोड की शुद्धता" सुनिश्चित करने के लिए, और इनपुट डेटा की सभी संभव बिट गहराई को ध्यान में रखना, यह मल्टीप्लायरों के हमारे अपने सेट को डिजाइन करने का निर्णय लिया गया था। यह FFT तितलियों के लिए जटिल गुणक के सबसे कुशल कार्यान्वयन के लिए अनुमति देगा, अर्थात्, गुणक और DSP48 ब्लॉकों पर आधारित एक योजक-घटाव। गुणक का पहला इनपुट इनपुट डेटा है, गुणक का दूसरा इनपुट घूर्णन कारक (मेमोरी से हार्मोनिक सिग्नल) है। मल्टीप्लायरों का एक सेट बिल्ट-इन यूएनआईएसआईएम लाइब्रेरी का उपयोग करके कार्यान्वित किया जाता है, जिसमें से परियोजना में उनके आगे उपयोग के लिए डीएसपी 48 ई 1 और डीएसपी 48 ई 2 आदि को जोड़ना आवश्यक है। गुणक का एक सेट तालिका में प्रस्तुत किया गया है। यह ध्यान दिया जाना चाहिए कि:

- संख्याओं के गुणा के संचालन से ऑपरेंड की क्षमता के योग के रूप में उत्पाद की क्षमता में वृद्धि होती है।

- मल्टीप्लायरों 25x18 और 27x18 में से प्रत्येक की नकल की जाती है, वास्तव में - यह विभिन्न परिवारों के लिए एक घटक है।

- ऑपरेशन के समानांतर समानता का चरण जितना बड़ा होगा, कंप्यूटिंग में देरी उतनी ही अधिक होगी और संसाधनों की मात्रा अधिक होगी।

- "B" पर कम बिट गहराई के साथ, दूसरे इनपुट पर उच्च बिट गहराई वाले गुणक लागू किए जा सकते हैं।

- बिट गहराई बढ़ाने में मुख्य सीमा पोर्ट "बी" (डीएसपी 48 आदिम का वास्तविक पोर्ट) और 17-बिट द्वारा आंतरिक पारी रजिस्टर द्वारा शुरू की गई है।

नीचे बताए गए कारणों के लिए बिट गहराई में एक और वृद्धि कार्य के ढांचे में रुचि नहीं है:

मोड़ कारकों की थोड़ी गहराई

यह ज्ञात है कि हार्मोनिक सिग्नल का रिज़ॉल्यूशन जितना अधिक होता है, उतनी ही सटीक रूप से संख्या प्रकट होती है (आंशिक भाग में अधिक संकेत)। लेकिन पोर्ट बिट का आकार B <25 बिट्स है इस तथ्य के कारण कि एफएफटी नोड्स में घूर्णी कारकों के लिए, यह बिट गहराई "तितलियों" में हार्मोनिक सिग्नल तत्वों के साथ इनपुट स्ट्रीम की उच्च गुणवत्ता वाले गुणन को सुनिश्चित करने के लिए पर्याप्त है (आधुनिक एफपीजीए पर किसी भी वास्तविक रूप से प्राप्त एफएफटी लंबाई के लिए)। मेरे द्वारा कार्यान्वित किए जा रहे कार्यों में मोड़ गुणांकों की बिट गहराई का विशिष्ट मूल्य 16 बिट्स है, 24 - कम अक्सर, 32 - कभी नहीं।

इनपुट नमूनों की थोड़ी गहराई

इन विशिष्ट प्राप्त करने और रिकॉर्डिंग नोड्स (एडीसी, डीएसी) की क्षमता बड़ी नहीं है - 8 से 16 बिट्स तक, और शायद ही कभी - 24 या 32 बिट्स। इसके अलावा, बाद के मामले में, IEEE-754 मानक के अनुसार फ्लोटिंग पॉइंट डेटा प्रारूप का उपयोग करना अधिक कुशल है। दूसरी ओर, एफएफटी में "तितली" के प्रत्येक चरण गणितीय संचालन के कारण आउटपुट नमूनों में एक बिट डेटा जोड़ता है। उदाहरण के लिए, NFFT = 1024 की लंबाई के लिए, log2 (NFFT) = 10 तितलियों का उपयोग किया जाता है।

इसलिए, आउटपुट बिट गहराई इनपुट से दस बिट अधिक होगी, WOUT = WIN + 10. सामान्य रूप से, सूत्र इस तरह दिखता है:

WOUT = WIN + log2 (NFFT);

एक उदाहरण:

इनपुट स्ट्रीम जीत की थोड़ी गहराई = 32 बिट्स,

टीडब्ल्यूडी = 27, के मोड़ कारकों की थोड़ी गहराई

इस आलेख में कार्यान्वित गुणक की सूची से पोर्ट "ए" की क्षमता 52 बिट्स से अधिक नहीं है। इसका मतलब है कि तितलियों की अधिकतम संख्या FFT = 52-32 = 20 है। अर्थात, FFT को 2 ^ 20 = 1M तक की लंबाई के साथ महसूस करना संभव है। (हालांकि, व्यवहार में, यह संभव साधनों द्वारा सीमित संसाधनों के कारण संभव नहीं है यहां तक कि सबसे शक्तिशाली FPGA क्रिस्टल के लिए भी, लेकिन यह दूसरे विषय से संबंधित है और लेख में इस पर विचार नहीं किया जाएगा)।

जैसा कि आप देख सकते हैं, यह एक मुख्य कारण है कि मैंने इनपुट पोर्ट की उच्च बिट गहराई के साथ मल्टीप्लायरों को लागू नहीं किया।

मल्टीप्लायरों ने पूर्णांक एफएफटी की गणना के कार्य के लिए

आवश्यक इनपुट

बिट आकारों और घूर्णी कारकों

की पूरी श्रृंखला को कवर किया । अन्य सभी मामलों में, आप

अस्थायी बिंदु प्रारूप में FFT गणना का उपयोग कर सकते हैं!

"विस्तृत" गुणक का कार्यान्वयन

एक मानक DSP48 नोड की बिट गहराई में फिट नहीं होने वाली दो संख्याओं को गुणा करने के एक सरल उदाहरण के आधार पर, मैं दिखाऊंगा कि आप एक विस्तृत डेटा गुणक को कैसे लागू कर सकते हैं। निम्नलिखित आंकड़ा इसके ब्लॉक आरेख को दर्शाता है। गुणक अतिरिक्त कोड में दो हस्ताक्षरित संख्याओं के गुणन को लागू करता है, पहले ऑपरेंड एक्स की चौड़ाई 42 बिट्स है, दूसरी वाई 18 बिट्स है। इसमें दो DSP48E2 नोड्स होते हैं। दो रजिस्टरों का उपयोग ऊपरी नोड में देरी को बराबर करने के लिए किया जाता है। ऐसा इसलिए किया जाता है क्योंकि ऊपरी योजक में आपको DSP48 के ऊपरी और निचले नोड्स से संख्याओं को सही ढंग से जोड़ने की आवश्यकता होती है। नीचे योजक वास्तव में उपयोग नहीं किया जाता है। कम नोड के आउटपुट में समय के साथ आउटपुट संख्या को संरेखित करने के लिए उत्पाद की एक अतिरिक्त देरी होती है। कुल देरी 4 चक्र है।

काम में दो घटक होते हैं:

- सबसे छोटा हिस्सा: P1 = '0' & X [16: 0] * Y [17: 0];

- पुराना हिस्सा: पी 2 = एक्स [42:17] * वाई [17: 0] + (पी 1 >> 17);

योजक

एक गुणक की तरह, एक योजक हस्तांतरण श्रृंखला या DSP48 ब्लॉकों का उपयोग करके तार्किक संसाधनों पर बनाया जा सकता है। अधिकतम थ्रूपुट प्राप्त करने के लिए, एक दूसरी विधि बेहतर है। एक DSP48 आदिम 48 बिट्स तक अतिरिक्त ऑपरेशन को लागू करने की अनुमति देता है, 96 बिट्स तक दो नोड्स। वर्तमान कार्य के लिए, इस तरह की थोड़ी गहराई काफी पर्याप्त है। इसके अलावा, DSP48 आदिम में एक विशेष "SIMD MODE" मोड है, जो छोटी क्षमता के विभिन्न डेटा के साथ कई ऑपरेशनों में निर्मित 48-बिट ALU को समानांतर करता है। यही है, "वन" मोड में 48 बिट्स और दो ऑपरेंड की एक पूरी बिट ग्रिड का उपयोग किया जाता है, और "TWO" मोड में बिट ग्रिड को 24 बिट्स (4 ऑपरेंड) के कई समानांतर धाराओं में विभाजित किया जाता है। यह मोड, केवल एक योजक का उपयोग करके, इनपुट नमूनों के छोटे बिट डेप्थ पर (गणना के पहले चरणों में) कब्जे वाले FPGA चिप संसाधनों की मात्रा को कम करने में मदद करता है।

थोड़ी गहराई में वृद्धि

बिट्स एन और एम के साथ दो संख्याओं को एक बाइनरी अतिरिक्त कोड में

गुणा करने के संचालन से आउटपुट बिट क्षमता में

पी / एन एम। की वृद्धि होती है।उदाहरण: तीन-बिट संख्या N = M = 3 को गुणा करने के लिए, अधिकतम सकारात्मक संख्या +3 =

(011) 2 है , और अधिकतम नकारात्मक संख्या 4 =

(100) 2 है । संख्या के संकेत के लिए सबसे महत्वपूर्ण बिट जिम्मेदार है। इसलिए, गुणा करने पर अधिकतम संभव संख्या +16 =

(010000) 2 है , जो दो अधिकतम नकारात्मक संख्याओं को गुणा करने के परिणामस्वरूप बनाई जाती है -4। आउटपुट की बिट गहराई इनपुट बिट्स P = N + M = 6 बिट्स के योग के बराबर है।

बाइनरी अतिरिक्त कोड में बिट्स एन और एम के साथ दो नंबर

जोड़ने का ऑपरेशन आउटपुट बिट में एक बिट से वृद्धि की ओर जाता है।

उदाहरण: दो सकारात्मक संख्याएँ जोड़ें, N = M = 3, अधिकतम सकारात्मक संख्या 3 =

(011) 2 है , और अधिकतम ऋणात्मक संख्या 4 =

(100) 2 है ।

संख्या के संकेत के लिए सबसे महत्वपूर्ण बिट जिम्मेदार है। इसलिए, अधिकतम सकारात्मक संख्या 6 = (0110) 2 है , और अधिकतम नकारात्मक संख्या -8 = (1000) 2 है । आउटपुट का रिज़ॉल्यूशन एक बिट बढ़ जाता है।एल्गोरिथ्म सुविधाओं पर विचार

:. . , 16- -32768 = 0x8000, -32767 = 0x8001.

~0.003% .

, . : – 4 = (100)

2 , +3 = (011)

2। गुणन परिणाम = -12 = (110100) 2 । पांचवें बिट को त्याग दिया जा सकता है क्योंकि यह पड़ोसी की नकल करता है, चौथा एक संकेत सा है।नीचे से बिट ट्रंकेशन:, «» , , . M- , , . 0x8000 = -1, 0x7FFF = +1. , ( M ). , , 1 . , [N+M-1-1: M-1]. ( 1), – .

/ «»

.

, FFT DIT FFT DIF W0 = {Re, Im} = {1, 0}. , – , . : «» . : W0 = {Re, Im} = {1, 0} W1 = {Re, Im} = {0, -1}. , . DSP48 .

– -, , .

- , . . — — .

INT_FFTK

- .

- NFFT = 8-512K .

- NFFT.

- , .

- , .

- .

- !

- .

- : – , -.

- : - , – .

- . Radix-2.

- NFFT *.

- .

- (Virtex-6, 7-Series, Ultrascale).

- ~375MHz Kintex-7

- – VHDL.

- bitreverse +.

- Open Source IP-Cores.

INTFFTK VHDL ( ) m- Matlab / Octave

.

निष्कर्ष

, . , . , IP-CORE Xilinx. .

: Radix-4, Radix-8, Ultra-Long FFT , FFT-FP32 ( IEEE-754). , , . FFT Radix-8, ( ).

dsmv2014 , . आपका ध्यान के लिए धन्यवाद!

UPDATE 2018/08/22

SCALED FFT / IFFT . 1 (truncate LSB). = .

, , : . , - .

: — 6 . — 128 . NFFT = 1024 , DATA_WIDTH = 16, TWDL_WIDTH = 16.

अंजीर। 1 - : अंजीर। 2 - :

अंजीर। 2 - :

- — UNSCALED FFT,

- — SCALED FFT.

, SCALED « » , UNSCALED .