अंत में, मेरे हाथ FPGAs के अध्ययन तक पहुँच गए। और फिर किसी तरह यह गलत हो जाता है: मैं लिनक्स के लिए हार्डवेयर के लिए ड्राइवरों को लिखता हूं, मैं माइक्रोकंट्रोलर प्रोग्राम करता हूं, मैं सर्किट पढ़ता हूं (और थोड़ा डिजाइन करता हूं), मुझे और बढ़ने की जरूरत है।

चूंकि मुझे लगता था कि एलईडी को ब्लिंक करना दिलचस्प नहीं है, इसलिए मैंने एक साधारण काम करने का फैसला किया। अच्छी तरह से, UART के लिए रिसीवर और ट्रांसमीटर मॉड्यूल लिखें, उन्हें FPGA के अंदर संयोजित करें (एक ही समय में आईपी कोर का उपयोग कैसे करें यह समझें), अच्छी तरह से, और यह सब वास्तविक हार्डवेयर पर परीक्षण करें।

मैं तुरंत कहता हूं कि यह कार्य का एक सार्वभौमिक मानकीकृत कोर बनाने का कार्य नहीं था। यह सिर्फ एक परीक्षण परियोजना है, "FPGA क्या है और इसके साथ संवाद कैसे करें" के विषय पर।

तो, चलो रिसीवर के साथ शुरू करते हैं। एल्गोरिथ्म काफी

अच्छी तरह से वर्णित है , इसलिए मैं यहां केवल इसके मुख्य बिंदुओं को दोहराऊंगा।

- आरएक्स सिग्नल सैंपलिंग आवृत्ति आवश्यक UART ट्रांसमिशन दर से चार गुना अधिक है।

- रिसेप्शन की शुरुआत के लिए स्थिति को उच्च स्तर से निम्न स्तर तक इनपुट सिग्नल आरएक्स का संक्रमण माना जाता है, अगर रिसेप्शन वर्तमान में प्रगति पर नहीं है।

- प्रारंभ बिट की विश्वसनीय पहचान के लिए स्थिति को नमूना आवृत्ति की दूसरी घड़ी में कम स्थिति में आरएक्स सिग्नल की अवधारण माना जाता है। उसी समय, हम व्यावहारिक रूप से बिट पल्स के बीच में आते हैं, जो हमें हर 4 चक्रों पर दालों का नमूना लेने की अनुमति देगा।

- प्रारंभ या बिट्स में त्रुटि के मामले में, त्रुटि संकेत त्रुटि सेट करें। इसके आधार पर, हम फास्टसिंक सिग्नल बनाते हैं, जिसका उपयोग हम भविष्य में फास्ट रिसीवर सिंक्रोनाइज़ेशन के लिए करेंगे।

- स्टार्ट बिट की पहचान करने के बाद, हम सबसे कम उम्र के साथ शुरू होने वाले डेटा बिट्स का क्रमिक स्वागत शुरू करते हैं। प्राप्त डेटा को रजिस्टर में दाईं ओर एक बिट से शिफ्ट के साथ लिखा जाता है। रिसेप्शन के अंत की स्थिति शिफ्ट रजिस्टर के 0 वें स्थान पर एक शुरुआत बिट का पता लगाने के लिए होगी।

- जब रिसीवर आरएक्स सिग्नल उच्च स्तर पर जाता है (तो यह तार्किक "1" ट्रांसमिशन, स्टॉप बिट ट्रांसमिशन या ट्रांसमिशन लाइन की निष्क्रिय स्थिति) हो सकता है जब रिसीवर की त्वरित सिंक्रनाइज़ेशन एक त्रुटि का पता लगाने के बाद इसे अपनी मूल स्थिति में लाती है।

- रिसेप्शन के सफल समापन (स्टार्ट और स्टॉप बिट्स के सही मान) के लिए शर्त पूर्ण संकेत है। इससे (जब rdclk सिग्नल द्वारा क्लॉक किया जाता है), एक तैयार पल्स सिग्नल उत्पन्न होता है, जो rxdata बस पर वैध डेटा की उपस्थिति को इंगित करता है।

मैं तुरंत ध्यान नहीं दूंगा कि मैं क्लॉक क्लॉक सिग्नल (अप्रत्याशित रूप से, सही?) से तैयार रीड सिग्नल को देखना चाहता हूं, ताकि बाद के डेटा प्रोसेसिंग की गति को UART विनिमय दर से जोड़ न सके। एक समान कार्यान्वयन ट्रांसमीटर मॉड्यूल (

नीचे देखें ) में है। रिसीवर और ट्रांसमीटर मॉड्यूल का एक परीक्षण गुच्छा इंटेल के आईपी कोर फीफो पर आधारित है, और उपभोक्ता और डेटा जनरेटर के लिए विभिन्न गति का अनुकरण करने की क्षमता के साथ है। केवल सीमा यह है कि डेटा के निर्माता और उपभोक्ता की घड़ी की आवृत्ति घड़ी की आवृत्ति के क्लर्क से कम नहीं होनी चाहिए।

रिसीवर मॉड्यूल (वेरिलोग)// // UART // // rxdata , ready==1 error==0. // ready 1 rdclk. // // : // rx // 2- . , . // 8 - ( 9 ). // 2 - , // . // // . // . '0' , . '1' // idle (. '1') // start- (. '0') // stop- (. '1') module uart_rx( nreset, // (, 0) clk, // UART, .. UART rx, // UART rdclk, // (rxdata, ready) rxdata, // , ready==1 ready, // rxdata ( 1) error, // ( 1) busy, // ( , 1) idle); // ( 1) input wire nreset; // (, 0) input wire clk; // , .. UART input wire rx; // UART input wire rdclk; // output wire[7:0] rxdata; output wire ready; output error; output busy; output idle; // , rdclk reg[2:0] done = 3'b000; // , rdclk //assign ready = (done == 2'b10) ? 1'b1 : 1'b0; assign ready = (done[1] && !done[0]) ? 1'b1 : 1'b0; // reg error = 1'b0; // // error // rx, . wire fastsync = (error && rx); // reg idle = 1'b1; // : // d[9] - , .. == 1 // d[8:1] - // d[0] - , .. == 0 reg[9:0] d = 10'b1xxxxxxxx1; // . 2'b10 wire[1:0] status = { d[9], d[0] }; // . wire complete = (status == 2'b10) ? 1'b1 : 1'b0; // assign rxdata = d[8:1]; // reg busy = 0; // rx reg[1:0] cnt; always @(posedge clk, negedge nreset) begin if(!nreset) begin rxreset(); end else begin if(fastsync) begin rxreset(); end else begin if(busy == 1'b1) begin // -, rx if(cnt == 2'd0) begin // // // (.. ) d <= { rx, d[9:1] }; if(d[1] == 1'b0) begin // , busy <= 1'b0; // error <= (rx == 1'b1) ? 1'b0 : 1'b1; end else begin // if(rx && (d == 10'b1111111111)) begin // busy <= 1'b0; // error <= 1'b1; end else begin // // - - cnt <= 2'd3; end end end else begin // - cnt <= cnt - 2'd1; end end else begin // if(!error) begin // , if(rx == 1'b0) begin // - busy <= 1'b1; // . 1, .. // d[0]==0 d <= 10'b1111111111; // rx 1/2 // 1- - // 2- - (cnt 0) cnt <= 2'd0; // .. , idle <= 1'b0; end else begin // idle <= 1'b1; end end end end end end task rxreset; begin // error <= 1'b0; // (!?) idle <= 1'b1; // busy <= 0; // -, complete d <= 10'b1xxxxxxxx1; end endtask always @(negedge rdclk, negedge nreset) begin if(!nreset) begin done <= 3'b000; end else begin // complete. // ready // complete 0 1 rdclk. done <= { complete, done[2:1] }; end end endmodule

चूंकि इनपुट सिग्नल आरएक्स अतुल्यकालिक है और (संभवतः) अस्थिर है,

मुख्य मॉड्यूल में रिसीवर मॉड्यूल के सामने एक

बहुमत तत्व जुड़ा हुआ था। तत्व को वेरिलोग में भी लिखा गया है, लेकिन इसका कोड यहां समझ में नहीं आता है। इसके बजाय, एक संश्लेषित तत्व की एक सुंदर तस्वीर।

बहुसंख्यक तत्व की संश्लेषित योजना ट्रांसमीटर इकाई और भी सरल है और मुझे आशा है कि अतिरिक्त टिप्पणियों की आवश्यकता नहीं है।

ट्रांसमीटर मॉड्यूल (वेरिलॉग ब्लॉकिंग और नॉन-ब्लॉकिंग असाइनमेंट हमेशा अंदर) // // UART // // : // clk - 4 , // rdclk - txdata, write, fetch. .. clk // txdata - , write/fetch // write - (1=) // fetch - (1=) // tx - UART // idle - (1=, ) // // FIFO dcfifo_component.lpm_showahead = "ON" module uart_tx( nreset, // (, 0) clk, // UART, .. UART rdclk, // txdata, // write, // ( 1) idle, // ( 1) fetch, // , rdclk tx); // UART input wire nreset; // (, 0) input wire clk; // UART input wire rdclk; input wire[7:0] txdata; input wire write; output wire idle; output fetch; output tx; // reg tx = 1'b1; reg fetch = 1'b0; // 4 reg[1:0] div4 = 2'd0; // : reg[3:0] s = 4'd10; // assign idle = (s == 4'd10); // reg[7:0] d; // reg sendstart; // reg canfetch; // , clk reg gotdata = 1'b0; // clock domains reg[2:0] sync = 3'b000; // rdclk write reg wr = 1'b0; // getdata==1 // nextdata // gotdata==1. , // . // gotdata getdata. always @(posedge rdclk, negedge nreset) begin if(!nreset) begin wr <= 1'b0; sync <= 3'b000; // fetch <= 1'b0; end else begin // write wr <= write; // sync <= { gotdata, sync[2:1] }; // gotdata // . // . fetch <= (sync[1] && !sync[0]) ? 1'b1 : 1'b0; end end always @(posedge clk, negedge nreset) begin if(!nreset) begin // div4 <= 2'd0; s <= 4'd10; gotdata <= 1'b0; end else begin // sendstart = 1'b0; // canfetch = wr; if(div4 == 2'd0) begin case(s) 4'd0: begin // sendstart = 1'b1; // , canfetch = 1'b0; end 4'd9: begin // tx <= 1'b1; end 4'd10: begin // idle, end default: begin // , tx <= d[0]; // d <= { 1'b0, d[7:1] }; // , canfetch = 1'b0; end endcase end else begin // div4 <= div4 - 2'd1; if(s < 4'd9) begin // 9 ! canfetch = 1'b0; end end if(canfetch) begin // , d <= txdata; // gotdata <= 1'b1; if(idle ) begin // idle - sendstart = 1'b1; end else begin // s <= 4'd0; end end if(gotdata) begin // , gotdata <= 1'b0; end if(sendstart) begin // tx <= 1'b0; // s <= 4'd1; // div4 <= 2'd3; end else begin if(div4 == 2'd0) begin if(s < 4'd10) begin // s <= s + 4'd1; // div4 <= 2'd3; end end end end end endmodule

उपरोक्त ट्रांसमीटर कार्यान्वयन ने टिप्पणियों में एक गर्म चर्चा का कारण बना। हालांकि, परिणामस्वरूप, हर कोई सहमत था कि ऐसा करना संभव था, लेकिन ध्यान से। आपके मन की शांति के लिए, मॉड्यूल को सभी उल्लिखित दिशानिर्देशों को ध्यान में रखते हुए फिर से लिखा गया है। मेरी राय में, यह लागू एल्गोरिथ्म की मानवीय धारणा के दृष्टिकोण से पिछले एक की तुलना में अधिक जटिल नहीं है।

ट्रांसमीटर मॉड्यूल (वेरिलोग, वैचारिक रूप से सही) // // UART // // : // clk - 4 , // rdclk - txdata, write, fetch. .. clk // txdata - , write/fetch // write - (1=) // fetch - (1=) // tx - UART // idle - (1=, ) // // FIFO dcfifo_component.lpm_showahead = "ON" module uart_tx( nreset, // (, 0) clk, // UART, .. UART rdclk, // txdata, // write, // ( 1) idle, // ( 1) fetch, // , rdclk tx); // UART input wire nreset; // (, 0) input wire clk; // UART input wire rdclk; input wire[7:0] txdata; input wire write; output wire idle; output fetch; output tx; // reg tx = 1'b1; reg fetch = 1'b0; // 4 reg[1:0] div4 = 2'd0; // : reg[3:0] s = 4'd10; // assign idle = (s == 4'd10); // reg[7:0] d; // reg sendstart; // reg canfetch; // , clk reg gotdata = 1'b0; // clock domains reg[2:0] sync = 3'b000; // rdclk write reg wr = 1'b0; // getdata==1 // nextdata // gotdata==1. , // . // gotdata getdata. always @(posedge rdclk, negedge nreset) begin if(!nreset) begin wr <= 1'b0; sync <= 3'b000; // fetch <= 1'b0; end else begin // write wr <= write; // sync <= { gotdata, sync[2:1] }; // gotdata // . // . fetch <= (sync[1] && !sync[0]) ? 1'b1 : 1'b0; end end // (?) always // sendstart canfetch always @(*) begin // sendstart = 1'b0; if(nreset) begin // canfetch = wr; if(div4 == 2'd0) begin case(s) 4'd0: begin // sendstart = 1'b1; // , canfetch = 1'b0; end 4'd9: begin // end 4'd10: begin // idle, end default: begin // // , canfetch = 1'b0; end endcase end else begin if(s < 4'd9) begin // 9 ! canfetch = 1'b0; end end if(canfetch && idle) begin // idle - sendstart = 1'b1; end end else begin // reset canfetch = 1'b0; end end always @(posedge clk, negedge nreset) begin if(!nreset) begin // div4 <= 2'd0; s <= 4'd10; gotdata <= 1'b0; end else begin if(div4 == 2'd0) begin case(s) 4'd0: begin // sendstart end 4'd9: begin // tx <= 1'b1; end 4'd10: begin // idle, end default: begin // , tx <= d[0]; // d <= { 1'b0, d[7:1] }; end endcase end else begin // div4 <= div4 - 2'd1; end if(canfetch) begin // , d <= txdata; // gotdata <= 1'b1; if(!idle /*s == 4'd10*/) begin // s <= 4'd0; end end else begin // , gotdata <= 1'b0; end if(sendstart) begin // tx <= 1'b0; // s <= 4'd1; // div4 <= 2'd3; end else begin if((div4 == 2'd0) && (s < 4'd10)) begin // s <= s + 4'd1; // div4 <= 2'd3; end end end end endmodule

रिसीवर और ट्रांसमीटर का परीक्षण करने के लिए, मुख्य मॉड्यूल घुटने पर लिखा गया था। मैं आपसे इसे कसम नहीं खाने के लिए कहता हूं, मैं डिजाइन त्रुटियों (बाहरी अतुल्यकालिक संकेत nreset, FIFO रीसेट की कमी, आदि) को जानता हूं। लेकिन कार्यक्षमता को सत्यापित करने के उद्देश्य से, वे महत्वपूर्ण नहीं हैं।

मेरा डेमो बोर्ड 50Mhz सिग्नल स्रोत से देखा गया है। इसलिए, मुख्य मॉड्यूल में, मैंने PLL का उपयोग किया, जिसमें C0 के आउटपुट में मैंने UART (1.8432Mhz, वास्तव में 1.843198Mhz) के साथ काम करने के लिए एक आवृत्ति बनाई और, मनोरंजन के लिए, मैंने सूचना प्रसंस्करण सर्किट के सिमुलेशन को देखने के लिए 300hhz (आउटपुट c1 PLL) की आवृत्ति बनाई।

मुख्य मॉड्यूल (वेरिलोग) // // .. UART UART, // FPGA, // FIFO IP CORE DCFIFO. // //NB! // SDC- ! // ( if , // ). module uart( input wire clk50mhz, // 50Mhz input wire nreset, // input wire rx, // UART output wire tx, // UART output wire overflow ); // 1.8432Mhz ( 1.843198Mhz) wire clk_1843200; // 1.2288Mhz ( 1.228799Mhz) //wire clk_1228800; // 300Mhz, PLL wire clk300mhz; // UART uart_pll pll50mhz(.inclk0(clk50mhz), .c0(clk_1843200) /*, .c1(clk_1228800)*/, .c1(clk300mhz)); // UART 38400 // (1843200/38400)/4 = 12 ('b1100). // UART 57600 // (1843200/57600)/4 = 8 // UART 115200 // (1843200/115200)/4 = 4 // UART 230400 // (1843200/230400)/4 = 2 // UART 460800 // (1843200/460800)/4 = 1 (.. !) // UART wire uart_baud4; // // .data 1 . // uart_baud4 .clock/ // uart_baud4 .clock uart_osc uart_osc_1(.clock(clk_1843200), .data(5'd2/*5'd4*//*5'd12*/-5'd1), .sload(uart_baud4), .cout(uart_baud4)); //wire uart_baud4 = clk_1843200; // wire rxf; // mfilter mfilter_rx(.clk(clk50mhz /*clk_1843200*/), .in(rx), .out(rxf)); //wire rxf = rx; // wire[7:0] rxdata; wire rxready; wire error; uart_rx uart_rx_1(.nreset(nreset), .clk(uart_baud4), .rx(rxf), .rdclk(clk300mhz /*clk50mhz*/ /*clk_1843200*/), .rxdata(rxdata), .ready(rxready), .error(error)); wire[7:0] txdata; // , , wire txnone; // , wire fetch; wire full; // // uart_baud4 // clk50mhz uart_fifo_rx uart_fifo_rx_1(.data(rxdata), .rdclk(clk300mhz /*clk50mhz*/ /*clk_1843200*/ /*uart_baud4*/), .rdreq(fetch), .wrclk(clk300mhz /*clk50mhz*/ /*clk_1843200*/ /*uart_baud4*/), .wrreq(rxready), .rdempty(txnone), .q(txdata), .wrfull(full)); assign overflow = ~error; uart_tx uart_tx_1(.nreset(nreset), .clk(uart_baud4), .rdclk(clk300mhz /*clk50mhz*/ /*clk_1843200*/), .txdata(txdata), .write(~txnone), .fetch(fetch), .tx(tx)); endmodule

परीक्षण के लिए, ज़ीलैक्स से टेस्टकॉम ट्रैफ़िक जनरेटर का उपयोग किया गया था। दुर्भाग्य से, मेरे USB / UART एडाप्टर ने 230400BPS से अधिक गति के साथ काम करने से इनकार कर दिया, इसलिए इस गति से सभी परीक्षण किए गए।

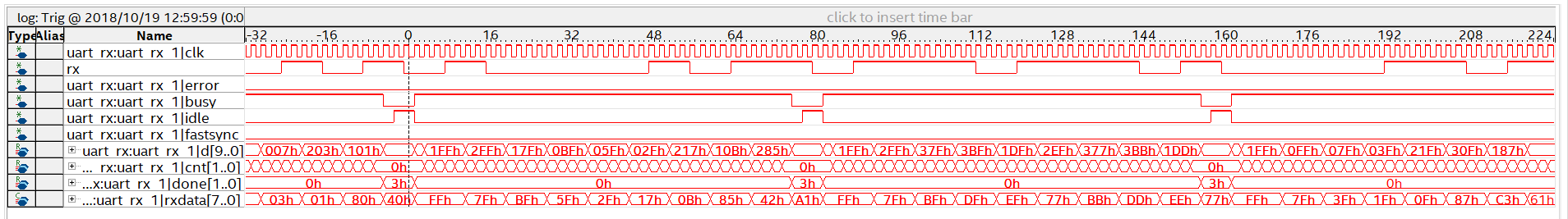

बहुमत तत्व का उपयोग करके इनपुट सिग्नल आरएक्स को फ़िल्टर करने के साथ परीक्षा परिणाम

सिग्नल टैप सिग्नल स्थिति

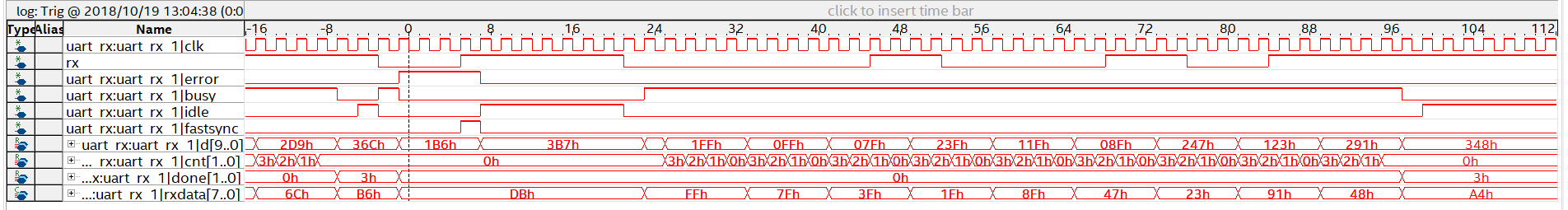

और यहां प्रवेश द्वार से बहुमत तत्व को हटा दिया गया है।लेकिन क्या, और कैसे मैं तेजी से तुल्यकालन योजना की जाँच करते समय मनमानी त्रुटियों का अनुकरण कर सकता हूं?

सिग्नल टैप सिग्नल स्थिति

टिप्पणी

क्षमा करें, मैंने क्वार्टस पाठ्यक्रम नहीं लिया और प्रश्न पूछने वाला कोई नहीं था। मैंने अपने आप पर ठोकर खाई और मैंने अन्य शुरुआती FPGAs को क्या चेतावनी दी: परियोजना में SDC फ़ाइल बनाना सुनिश्चित करें और इसमें घड़ी की आवृत्तियों का वर्णन करें। हां, परियोजना इसके बिना बनाई जा रही है, हालांकि चेतावनी दिखाई दे सकती है यदि सिंथेसाइज़र घड़ी की समय विशेषताओं को निर्धारित नहीं कर सकता है। पहले तो मैंने उन्हें नजरअंदाज कर दिया जब तक कि मैंने कोड को निष्पादित करते समय अपने रिसीवर मॉड्यूल में क्यों की समस्या का निर्धारण करने के लिए आधे दिन तक नहीं मारा

if(rx == 1'b0) begin busy <= 1'b1; d <= 10'b1111111111; cnt <= 2'd0; idle <= 1'b0; end else begin

व्यस्त और निष्क्रिय सिग्नल सही ढंग से सेट किए गए थे, लेकिन रजिस्टर डी की सामग्री कभी-कभी नहीं बदलती थी।

परिशिष्ट: परियोजना के लिए एसडीसी फ़ाइल set_time_format -unit ns -decimal_places 3 # 50Mhz, (50/50 duty cycle) create_clock -name {clk50mhz} -period 20.000 -waveform { 0.000 10.000 } ############################################################################## Now that we have created the custom clocks which will be base clocks,# derive_pll_clock is used to calculate all remaining clocks for PLLs derive_pll_clocks -create_base_clocks derive_clock_uncertainty # PLL ? # altpll_component.clk0_divide_by = 15625, # altpll_component.clk0_duty_cycle = 50, # altpll_component.clk0_multiply_by = 576, # altpll_component.clk0_phase_shift = "0", #create_generated_clock -name clk_1843200 -source [get_ports {clk50mhz}] -divide_by 15625 -multiply_by 576 -duty_cycle 50 -phase 0 -offset 0 # baudrate=38400 # 1/4 , .. duty=(1/4)*100=25% #create_generated_clock -name uart_baud4 -source [get_nets {pll50mhz|altpll_component|auto_generated|wire_pll1_clk[0]}] -divide_by 12 -duty_cycle 25 [get_nets {uart_osc_1|LPM_COUNTER_component|auto_generated|counter_reg_bit[0]}] # baudrate=230400 # 1/4 , .. duty=(1/4)*100=50% create_generated_clock -name uart_baud4 -source [get_nets {pll50mhz|altpll_component|auto_generated|wire_pll1_clk[0]}] -divide_by 2 -duty_cycle 25 [get_nets {uart_osc_1|LPM_COUNTER_component|auto_generated|counter_reg_bit[0]}] # baudrate=460800 # 1, PLL, . जो आधार घड़ियों हो जाएगा घड़ियां, # derive_pll_clock सभी शेष गणना करने के लिए प्रयोग किया जाता है set_time_format -unit ns -decimal_places 3 # 50Mhz, (50/50 duty cycle) create_clock -name {clk50mhz} -period 20.000 -waveform { 0.000 10.000 } ############################################################################## Now that we have created the custom clocks which will be base clocks,# derive_pll_clock is used to calculate all remaining clocks for PLLs derive_pll_clocks -create_base_clocks derive_clock_uncertainty # PLL ? # altpll_component.clk0_divide_by = 15625, # altpll_component.clk0_duty_cycle = 50, # altpll_component.clk0_multiply_by = 576, # altpll_component.clk0_phase_shift = "0", #create_generated_clock -name clk_1843200 -source [get_ports {clk50mhz}] -divide_by 15625 -multiply_by 576 -duty_cycle 50 -phase 0 -offset 0 # baudrate=38400 # 1/4 , .. duty=(1/4)*100=25% #create_generated_clock -name uart_baud4 -source [get_nets {pll50mhz|altpll_component|auto_generated|wire_pll1_clk[0]}] -divide_by 12 -duty_cycle 25 [get_nets {uart_osc_1|LPM_COUNTER_component|auto_generated|counter_reg_bit[0]}] # baudrate=230400 # 1/4 , .. duty=(1/4)*100=50% create_generated_clock -name uart_baud4 -source [get_nets {pll50mhz|altpll_component|auto_generated|wire_pll1_clk[0]}] -divide_by 2 -duty_cycle 25 [get_nets {uart_osc_1|LPM_COUNTER_component|auto_generated|counter_reg_bit[0]}] # baudrate=460800 # 1, PLL, .

लेख पर टिप्पणी लिखने वाले सभी को बहुत-बहुत धन्यवाद! इनमें से, मैंने बहुत उपयोगी इकट्ठा किया, हालांकि कभी-कभी कुछ परस्पर विरोधी जानकारी। मेरी राय में, उनका मूल्य ऊपर वर्णित एल्गोरिदम के कार्यान्वयन से बहुत अधिक है। और, निस्संदेह, वे उन लोगों के लिए उपयोगी होंगे जो FPGAs की दुनिया में चढ़ने की हिम्मत रखते हैं।बाहरी लिंक की सूची

- यूनिवर्सल एसिंक्रोनस ट्रांसीवर (विकिपीडिया)

- अधिकांश तत्व (विकिपीडिया)