अक्टूबर की शुरुआत में, Xilinx

ने प्रोग्राम वर्टेबल एरेज़ (

FPGAs ) पर निर्मित नई वर्सल चिप

पेश की । इस तरह के डिवाइस के संचालन का तर्क उपयोग के दौरान किसी भी समय संशोधित किया जा सकता है। यह उम्मीद की जाती है कि चिप एआई सिस्टम के काम में तेजी लाएगी और 5 जी नेटवर्क में एप्लिकेशन खोजेगी। प्रोसेसर की रिहाई 2019 के अंत के लिए निर्धारित है।

अगला, हम डिवाइस के बारे में बात करते हैं और यह अगली पीढ़ी के नेटवर्क को कैसे मदद करेगा।

/ फ़्लिकर / माइक मोज़ार्ट / सीसी

/ फ़्लिकर / माइक मोज़ार्ट / सीसी5G नेटवर्क की समस्या

5 जी तकनीक उच्च आवृत्तियों - 28 गीगाहर्ट्ज और उच्चतर का उपयोग करती है - इसलिए सिग्नल खराब रूप से लंबी दूरी पर प्रेषित होता है। इसके प्रसार का प्लस घरों की दीवारों द्वारा दृढ़ता से बाधा है। एक शहर में, यह कनेक्शन की गुणवत्ता में कमी का कारण बन सकता है।

विशेषज्ञों का

कहना है कि यह बड़ी संख्या में IoT उपकरणों के काम में बाधा बन जाएगा, जो कि 2020 से

अनुमानित संख्या में सक्रिय वृद्धि है (बस जब पूर्ण 5 जी नेटवर्क तैनात किया जाएगा)।

कनेक्टेड डिवाइस, जैसे कार या पहनने योग्य मेडिकल गैजेट, वास्तविक समय में संवाद करना चाहिए। कनेक्शन की अस्थिरता उन्हें पर्याप्त रूप से उनके आसपास की स्थिति का आकलन करने या महत्वपूर्ण डेटा (उदाहरण के लिए, मानव स्वास्थ्य की स्थिति के बारे में) सेवारत संगठन के सर्वर से रोक सकती है। कंपनियां विशेष रूप से वितरित एंटीना सिस्टम की व्यवस्था करके इस समस्या को हल करने की योजना बनाती हैं, हालांकि, इसके साथ कठिनाइयां पैदा होती हैं।

उदाहरण के लिए, अब न्यूयॉर्क में एक हजार से अधिक बेस स्टेशन स्थापित हैं। 5 जी नेटवर्क के साथ पूरे शहर को कवर करने के लिए,

एक और आधा मिलियन स्थापित करने की आवश्यकता होगी । परियोजना की लागत पिछले "जी-मानकों" के मामले की तुलना में बहुत अधिक होगी।

कैसे वर्साल इन समस्याओं को हल करने में मदद करता है

Xilinx डिवाइस एआई सिस्टम का उपयोग करके इंटरनेट कनेक्शन की स्थिरता के साथ समस्याओं को हल करने में मदद करेगा, जिसके साथ यह काम करने के लिए "ट्यून्ड" है। वर्सेल चिप 5 जी नेटवर्क में मशीन लर्निंग एल्गोरिदम को प्रोसेस करेगी जो मोबाइल एंटेना के

विकिरण पैटर्न को अनुकूलित करती है। यह नेत्रहीन क्षेत्रों से बचने और डेटा ट्रांसमिशन के उपयुक्त मोड का चयन करेगा।

एआई सिस्टम

हैंडओवर एल्गोरिदम में भी सुधार करेंगे, जो सत्रों को एक स्टेशन से दूसरे स्थान पर स्थानांतरित करने के लिए जिम्मेदार हैं। इसके अलावा, नेटवर्क स्वयं-मरम्मत और अनुकूलन करेगा, यदि कोई नोड विफल रहता है, तो डेटा को स्वचालित रूप से पुनर्निर्देशित करेगा। तो, 5G उपयोगकर्ता बिना कनेक्शन विफलता के किसी भवन या शहर में स्वतंत्र रूप से घूम सकेंगे।

Xilinx में पहले से ही 5G के लिए AI चिप्स के ग्राहक हैं। 2020 के ओलंपिक में नेटवर्किंग के लिए वर्सल प्रोसेसर का उपयोग किया जाएगा।

चिप वास्तुकला की विशेषताएं

Xilinx ने अक्टूबर में वर्सल कॉन्सेप्ट पेश किया। नया माइक्रोकिरसीट

विषम है , अर्थात यह एक साथ कई कंप्यूटिंग इकाइयों का उपयोग करता है। ये इकाइयाँ प्रोसेसर, कोप्रोसेसर, इंटीग्रेटेड सर्किट ASIC और FPGA हो सकती हैं।

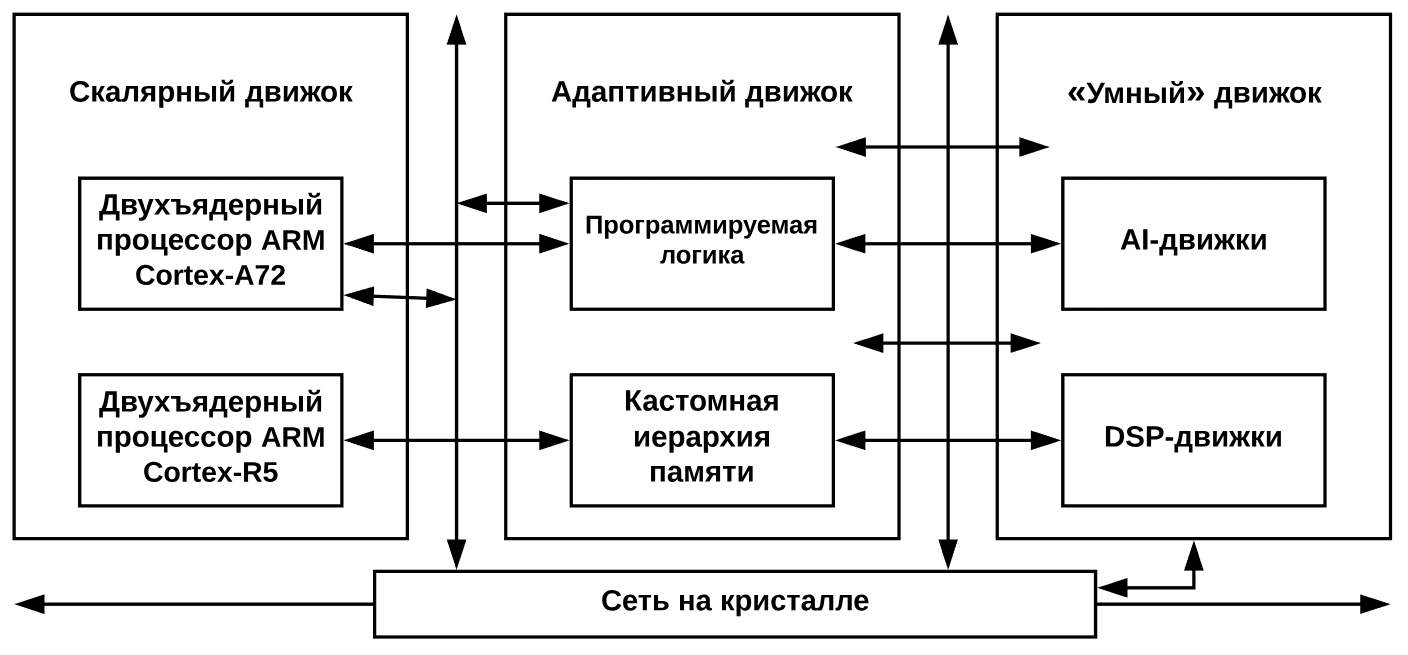

नई Xilinx चिप FPGA के उन्नत संस्करण पर आधारित है - अनुकूली कंप्यूटर त्वरक प्लेटफॉर्म (ACAP) वास्तुकला। इसमें चार बुनियादी घटक होते हैं: एक

अदिश इंजन, एक अनुकूली इंजन,

वेक्टर त्वरक ("स्मार्ट" इंजन), और सिस्टम तत्वों को जोड़ने के लिए एक चिप (NoC - Network-on-Chip) पर एक नेटवर्क।

स्केलर इंजन को दोहरे-कोर एआरएम कॉर्टेक्स-ए 72 और कॉर्टेक्स-आर 5 प्रोसेसर द्वारा दर्शाया गया है। प्रोग्राम करने योग्य

तर्क घटकों को जोड़ने के लिए

लुकअप टेबल ,

ट्रिगर , मेमोरी और विशेष ब्लॉक के साथ विन्यास योग्य

तर्क तत्वों पर बनाया गया है। यह सब आपको

स्मृति के एक

पदानुक्रम का निर्माण करने की अनुमति देता है, एक विशिष्ट कम्प्यूटेशनल कार्य के लिए तेज।

"स्मार्ट" इंजन

VLIW आर्किटेक्चर पर आधारित है, जिसे एक निर्देश में कई ऑपरेशनों के समानांतर निष्पादन के लिए आवश्यक है।

SIMD गणना का सिद्धांत भी लागू होता है। ऐसी संरचना एमओ समस्याओं को हल करने में मदद करती है और शास्त्रीय प्रणालियों की तुलना में 5-10 गुना तेजी से संकेतों को संसाधित करती है। NoC के लिए, इसकी घोषित बैंडविड्थ 1 Tbps है।

ACAP आर्किटेक्चर आरेख इस तरह दिखता है।

चिप्स का वर्साल परिवार

7-एनएम प्रोसेस तकनीक का उपयोग करके TSMC में उत्पादित किया जाएगा। अन्य वास्तुशिल्प विशेषताएं आधिकारिक पीडीएफ दस्तावेजों में पाई जा सकती हैं -

एएसएपी वास्तुकला अवलोकन और

वर्सल चिप समीक्षा ।

सिस्टम सी, सी ++ और पायथन में क्रमादेशित है। डेवलपर्स के अनुसार, उन्होंने इन

पीएल के लिए चुना, चूंकि

टीआईबीईई , सी, सी ++ और पायथन के अनुसार वे जावा के बाद सबसे लोकप्रिय हैं।

इसके अलावा, ये भाषाएं एक-दूसरे की पूरक हैं। C और C ++ संकलित हैं, जिसका अर्थ है कि कोड को नंगे धातु (विशेष रूप से, FPGA पर) पर चलाया जा सकता है। डेटा का विश्लेषण करने और एआई सिस्टम के साथ काम करने के लिए पायथन किसी और से बेहतर है। Xilinx को चुनने के अन्य कारण विषय (

पीडीएफ ) पर एक अलग अध्ययन में हैं।

इसी तरह के समाधान

FPGA- आधारित चिप्स को अन्य कंपनियों द्वारा भी विकसित किया जा रहा है, जैसे Intel। कंपनी के नवीनतम उत्पादों में से,

अररिया हाइब्रिड डिवाइस को प्रतिष्ठित किया जा सकता है। विकास दो चिप्स का एक मंच है: Xeon E5-2600 v4 और

Altera Arria 10 ।

इंटेल के अनुसार, डिवाइस सर्वर, डेटा सेंटर और क्लाउड सेवाओं के लिए उपयुक्त है, जहां लोड अक्सर स्पैस्मोडिक रूप से बढ़ता है। FPGA पर एक प्रोसेसर समानांतर में डेटा को संसाधित करने में मदद करेगा, जो समग्र सिस्टम प्रदर्शन को बढ़ाएगा। उदाहरण के लिए, Fujitsu, वर्ष के अंत तक इस चिप के साथ अपनी प्राइमरी सर्वर लाइन की आपूर्ति करने की

योजना बना रहा है।

अन्य बाजार के खिलाड़ियों - एएमडी, एआरएम, क्वालकॉम, सैमसंग और अन्य - ने 2012 में गैर-लाभकारी संगठन

एचएसए फाउंडेशन बनाया। विषम गणना वहां लोकप्रिय है: वे उद्योग मानकों को विकसित करते हैं, डेवलपर्स को बाजार में प्रवेश करने और शैक्षिक कार्यक्रमों को प्रायोजित करने में मदद करते हैं।

Xilinx का

मानना है कि AI सिस्टम के विकास और 5G नेटवर्क के प्रसार के साथ, FPGA प्लेटफार्मों की मांग बढ़ेगी। Xilinx के CEO विक्टर पेंग

ने ध्यान दिया कि चिप्स के बड़े पैमाने पर उत्पादन में एकमात्र बाधा CPU और GPU से प्रतिस्पर्धा है, जो FPGA के समाधान को "कैप्चर" बाजार से रोकता है। लेकिन, शायद,

2020 से पहले मांग में उछाल (अगर ऐसा होता है) की उम्मीद नहीं की जानी चाहिए।

VAS विशेषज्ञों के कॉर्पोरेट ब्लॉग से PS अतिरिक्त सामग्री:

PPS Habré पर हमारे ब्लॉग के कुछ नए लेख: