अभी कुछ समय पहले, कंपनी STM ने माइक्रोकंट्रोलर्स, क्रिस्टल STM32H7 की एक पंक्ति के मानकों के आधार पर एक बहुत शक्तिशाली बाजार में लॉन्च किया था। मुझे उसके लिए क्या आकर्षित किया:

- 400 मेगाहर्ट्ज तक कोर आवृत्ति में वृद्धि

- 1 एमबी तक रैम बढ़ी

- 16 बिट एडीसी

- पिन-टू-पिन संगतता F7 श्रृंखला के साथ

मैंने पूरी तरह से सोचा, मैंने STM32H743IIT6 क्रिस्टल को STM32F746IGT6 के बजाय बोर्ड पर टाँका और SW4STM32 में एक नई परियोजना शुरू की।

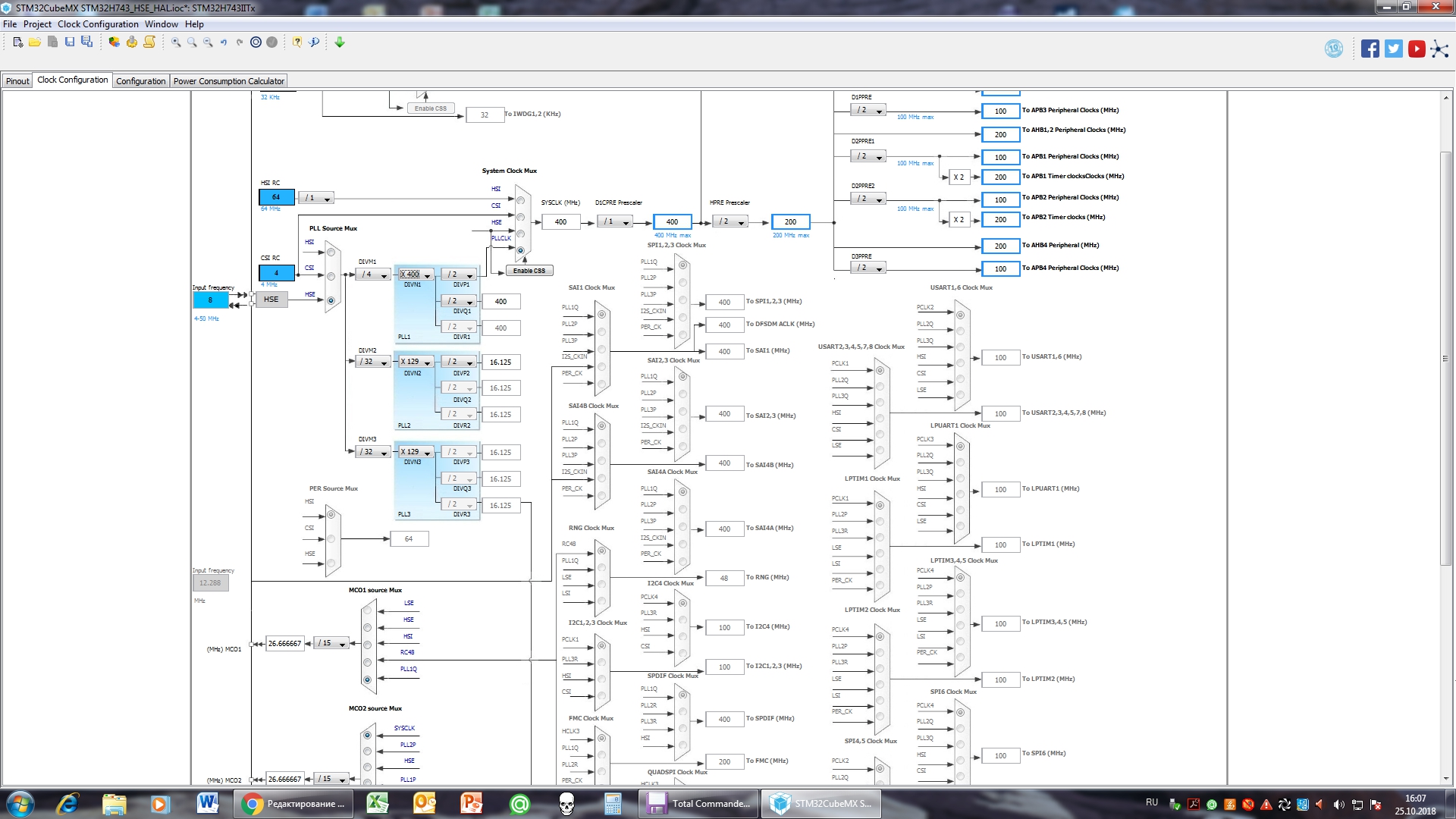

यह माइक्रोकंट्रोलर की घड़ी प्रणाली के डिवाइडर और कारकों के गुणांक की गणना करने के लिए STM32CubeMX प्रोग्राम के क्लॉक कॉन्फ़िगरेशन टैब का उपयोग करना सुविधाजनक है।

घड़ी सेटिंग्स:

- बाहरी क्वार्ट्ज - 8 मेगाहर्ट्ज

- PLL1 के लिए आवृत्ति स्रोत - बाहरी क्वार्ट्ज (HSE)

- PLL1 के लिए विभक्त - 4 (DIVM1)

- गुणक PLL1 - 400 (DIVN1)

- आउटपुट डिवाइडर - 2 (DIVP1, DIVQ1, DIVR1)

तदनुसार, कोर आवृत्ति (SYSCLK) 400 मेगाहर्ट्ज है।

STM32CubeMX के अलावा, STM32CubeH7 फर्मवेयर पैकेज भी है, जिसमें STM32H7 के लिए बाह्य उपकरणों के साथ काम करने के लिए बड़ी संख्या में उदाहरण हैं। यह उनसे कहा गया था कि माइक्रोकंट्रोलर की घड़ी प्रणाली के प्रारंभ का अनुक्रम लिया गया था।

सूचना और टिप्पणियाँ निम्नलिखित स्रोतों से ली गई हैं:

- SystemMlock_Config STM32CubeH7 फर्मवेयर पैकेज से

- संदर्भ मैनुअल STM32H743 / 753 और STM32H750 एआरएम-आधारित 32-बिट MCUs

- - डेटशीट STM32H743xI

तो चलिए शुरू करते हैं।

1. बाहरी क्वार्ट्ज को चालू करना और तत्परता की प्रतीक्षा करना।

// Enable HSE RCC->CR |= RCC_CR_HSEON; // Wait till HSE is ready while((RCC->CR & RCC_CR_HSERDY) == 0);

2. PLL1 के लिए आवृत्ति स्रोत का संकेत - बाहरी क्वार्ट्ज।

3. विभाजक मान 4 पर सेट है।

//PLLM = 4 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_5; //0 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_4; //0 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_3; //0 RCC -> PLLCKSELR |= RCC_PLLCKSELR_DIVM1_2; //1 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_1; //0 RCC -> PLLCKSELR &= ~RCC_PLLCKSELR_DIVM1_0; //0

4. कारक एन और भाजक पी, क्यू, आर

//PLL1DIVR bits //DIVN1[8:0] 0 - 8 PLLN = 400 //DIVP1[6:0] 9 - 15 PLLP = 2 //DIVQ1[6:0] 16 - 22 PLLQ = 2 //DIVR1[6:0] 24 - 30 PLLR = 2 RCC -> PLL1DIVR |= 0x0101038F;

5. आंशिक आवृत्ति विभक्त PLL (यदि आवश्यक हो)

// /* Configure PLL PLL1FRACN */ //__HAL_RCC_PLLFRACN_CONFIG(RCC_OscInitStruct->PLL.PLLFRACN)

6. इनपुट आवृत्ति रेंज PLL1 का संकेत

7. उत्पादन आवृत्ति रेंज PLL1 का संकेत

8. आउटपुट डिवाइडर पर स्विचिंग PLL1: P, Q, R

/* Enable PLL System Clock output. */ // __HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL1_DIVP); //Bit 16 DIVP1EN: PLL1 DIVP divider output enable RCC->PLLCFGR |= RCC_PLLCFGR_DIVP1EN; /* Enable PLL1Q Clock output. */ //__HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL1_DIVQ); RCC->PLLCFGR |= RCC_PLLCFGR_DIVQ1EN; /* Enable PLL1R Clock output. */ // __HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL1_DIVR); RCC->PLLCFGR |= RCC_PLLCFGR_DIVR1EN;

9. भिन्नात्मक विभक्त का समावेश।

10. PLL1 शुरू करें और तत्परता की प्रतीक्षा करें

PLL1 कॉन्फ़िगर और चल रहा है। अब SYSCLK आवृत्ति स्रोत का चयन करें और बस डिवाइडर सेट करें।

11. 2 एचपीआरई द्वारा विभक्त

//RCC_ClkInitStruct.AHBCLKDivider = RCC_HCLK_DIV2; // MODIFY_REG(RCC->D1CFGR, RCC_D1CFGR_HPRE, RCC_ClkInitStruct->AHBCLKDivider); //HPRE[3:0]: D1 domain AHB prescaler //1000: rcc_hclk3 = sys_d1cpre_ck / 2 RCC -> D1CFGR |= RCC_D1CFGR_HPRE_3; //1 RCC -> D1CFGR &= ~RCC_D1CFGR_HPRE_2; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_HPRE_1; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_HPRE_0; //0

12. बिना विभाजन के D1CPRE

//RCC_ClkInitStruct.SYSCLKDivider = RCC_SYSCLK_DIV1; //MODIFY_REG(RCC->D1CFGR, RCC_D1CFGR_D1CPRE, RCC_ClkInitStruct->SYSCLKDivider); //D1CPRE[3:0]: D1 domain Core prescaler //0xxx: sys_ck not divided (default after reset) RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_3; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_2; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_1; //0 RCC -> D1CFGR &= ~RCC_D1CFGR_D1CPRE_0; //0

13. PLL1 को SYSCLK स्रोत के रूप में सेट करें और तत्परता की प्रतीक्षा करें

//RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK; //MODIFY_REG(RCC->CFGR, RCC_CFGR_SW, RCC_ClkInitStruct->SYSCLKSource); //SW[2:0]: System clock switch //011: PLL1 selected as system clock (pll1_p_ck) RCC->CFGR &= ~RCC_CFGR_SW_2; //0 RCC->CFGR |= RCC_CFGR_SW_1; //1 RCC->CFGR |= RCC_CFGR_SW_0; //1 while((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL1);

14. डिवाइडर 2 D1PPRE द्वारा

//D1PCLK1 Configuration //RCC_ClkInitStruct.APB3CLKDivider = RCC_APB3_DIV2; //MODIFY_REG(RCC->D1CFGR, RCC_D1CFGR_D1PPRE, RCC_ClkInitStruct->APB3CLKDivider); //Bits 6:4 D1PPRE[2:0]: D1 domain APB3 prescaler //100: rcc_pclk3 = rcc_hclk3 / 2 RCC -> D1CFGR |= RCC_D1CFGR_D1PPRE_2; RCC -> D1CFGR &= ~RCC_D1CFGR_D1PPRE_1; RCC -> D1CFGR &= ~RCC_D1CFGR_D1PPRE_0;

15. 2 D2PPRE1 द्वारा डिवाइडर

//PCLK1 Configuration //RCC_ClkInitStruct.APB1CLKDivider = RCC_APB1_DIV2; //MODIFY_REG(RCC->D2CFGR, RCC_D2CFGR_D2PPRE1, (RCC_ClkInitStruct->APB1CLKDivider)); //Bits 6:4 D2PPRE1[2:0]: D2 domain APB1 prescaler //100: rcc_pclk1 = rcc_hclk1 / 2 RCC -> D2CFGR |= RCC_D2CFGR_D2PPRE1_2; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE1_1; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE1_0;

16. डिवाइडर 2 D2PPRE2 द्वारा

//PCLK2 Configuration //RCC_ClkInitStruct.APB2CLKDivider = RCC_APB2_DIV2; //MODIFY_REG(RCC->D2CFGR, RCC_D2CFGR_D2PPRE2, (RCC_ClkInitStruct->APB2CLKDivider)); //Bits 10:8 D2PPRE2[2:0]: D2 domain APB2 prescaler //100: rcc_pclk2 = rcc_hclk1 / 2 RCC -> D2CFGR |= RCC_D2CFGR_D2PPRE2_2; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE2_1; RCC -> D2CFGR &= ~RCC_D2CFGR_D2PPRE2_0;

17. 2 डीबीपीआरई द्वारा डिवाइडर

//D3PCLK1 Configuration //RCC_ClkInitStruct.APB4CLKDivider = RCC_APB4_DIV2; //MODIFY_REG(RCC->D3CFGR, RCC_D3CFGR_D3PPRE, (RCC_ClkInitStruct->APB4CLKDivider) ); //Bits 6:4 D3PPRE[2:0]: D3 domain APB4 prescaler //100: rcc_pclk4 = rcc_hclk4 / 2 RCC -> D3CFGR |= RCC_D3CFGR_D3PPRE_2; RCC -> D3CFGR &= ~RCC_D3CFGR_D3PPRE_1; RCC -> D3CFGR &= ~RCC_D3CFGR_D3PPRE_0;

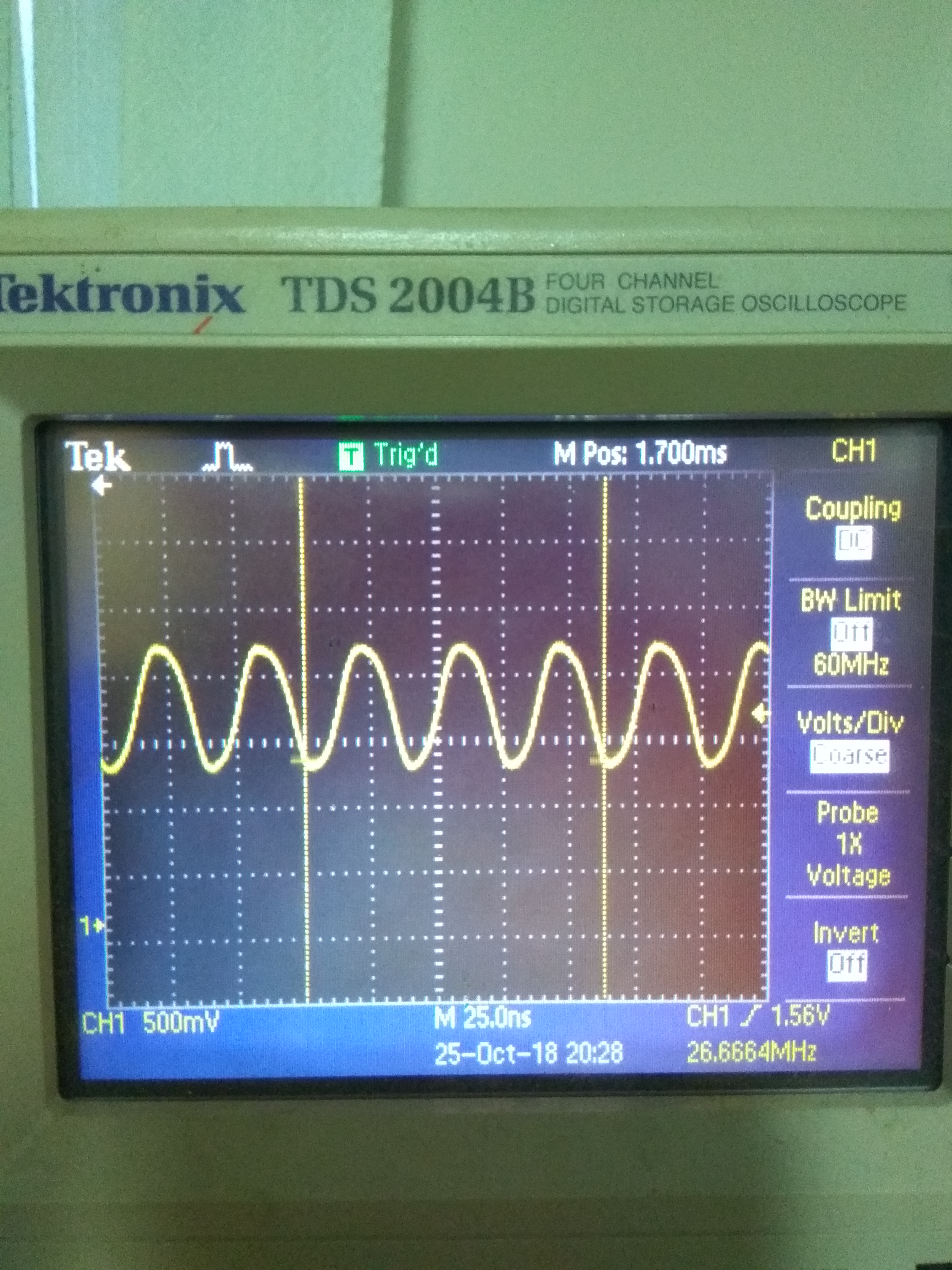

यह सुनिश्चित करने के लिए कि कॉन्फ़िगरेशन और प्रारंभ सफल रहे, हम MCO2 माइक्रोकंट्रोलर के आउटपुट का उपयोग करते हैं। इस आउटपुट में 15 के आउटपुट स्प्लिटर के साथ 26.666 मेगाहर्ट्ज की आवृत्ति होनी चाहिए।

बहुत बढ़िया। आवृत्ति मौजूद है, फिर सब कुछ सही ढंग से किया जाता है।