FPGA पर सरल डायरेक्ट-मैप्ड कैश सिमुलेशन

यह लेख इन्नोपोलिस विश्वविद्यालय के प्रथम वर्ष के स्नातक छात्रों के लिए एक कोर्स वर्क का एक हिस्सा है। एक टीम में सभी काम होते हैं। इस लेख का उद्देश्य विषय की समझ दिखाना या अनुकरण का उपयोग करके इसे समझने में मदद करना है।

गिट रिपोजिटरी लिंक

काम का सिद्धांत लेकिन उपयोगकर्ता की ओर से इस तरह दिखना चाहिए:

- किसी भी डेटा को मेमोरी में लिखने के लिए, आपको रैम को डेटा और एड्रेस के साथ एक्सेस करना होगा, जिसमें हम लिखना चाहते हैं।

- डेटा तक पहुंचने के लिए, हमें कैश करना होगा। यदि कैश आवश्यक डेटा नहीं ढूँढ सकता है, तो यह वहां से डेटा की प्रतिलिपि बनाकर रैम तक पहुंचता है।

वेरिलोग के साथ काम करते समय, यह समझा जाना चाहिए कि कार्यक्रम के प्रत्येक व्यक्तिगत ब्लॉक को एक मॉड्यूल के रूप में दर्शाया गया है। जैसा कि आप जानते हैं, कैश तेज़ मेमोरी का एक स्वतंत्र हिस्सा नहीं है, और इसके उचित संचालन के लिए इसे किसी अन्य मेमोरी ब्लॉक - रैम से डेटा लेना होगा। इसलिए, FPGA पर कैश के काम का अनुकरण करने के लिए, हमें पूरे रैम मॉड्यूल का अनुकरण करना होगा जिसमें कैश भी शामिल है, लेकिन मुख्य बिंदु कैश सिमुलेशन है।

कार्यान्वयन में ऐसे मॉड्यूल शामिल हैं:

- ram.v - रैम मेमोरी मॉड्यूल

- cache.v - कैश मेमोरी मॉड्यूल

- cache_and_ram.v - मॉड्यूल जो डेटा और मेमोरी के साथ संचालित होता है।

- testbench.v और testbench2.v - मॉड्यूल यह दिखाने के लिए कि मुख्य मॉड्यूल पूरी तरह से काम करते हैं।

रैम मॉड्यूल:

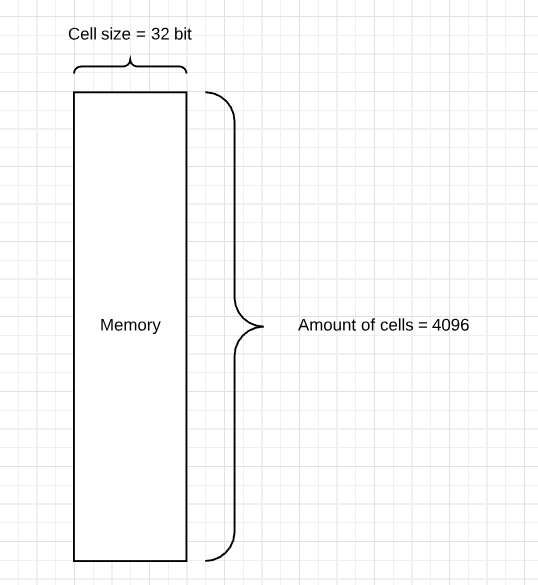

कोडmodule ram(); parameter size = 4096; //size of a ram in bits reg [31:0] ram [0:size-1]; //data matrix for ram endmodule

विवरणमॉड्यूल मेमोरी का प्रतिनिधित्व करता है जिसका उपयोग रैम के रूप में किया जाता है। इसमें कुछ डेटा स्टोर करने के लिए 4096 32-बिट एड्रेसेबल सेल हैं।

कैश मॉड्यूल:

कोड module cache(); parameter size = 64; // cache size parameter index_size = 6; // index size reg [31:0] cache [0:size - 1]; //registers for the data in cache reg [11 - index_size:0] tag_array [0:size - 1]; // for all tags in cache reg valid_array [0:size - 1]; //0 - there is no data 1 - there is data initial begin: initialization integer i; for (i = 0; i < size; i = i + 1) begin valid_array[i] = 6'b000000; tag_array[i] = 6'b000000; end end endmodule

विवरणतो कैश में डेटा की सिर्फ प्रतियां शामिल हैं

स्मृति; इसके पास बिट्स हैं जो हमें कैश के भीतर डेटा खोजने में मदद करते हैं और

इसकी वैधता का सत्यापन करें।

कैश और रैम मॉड्यूल:

कोड module cache_and_ram( input [31:0] address, input [31:0] data, input clk, input mode, //mode equal to 1 when we write and equal to 0 when we read output [31:0] out ); //previous values reg [31:0] prev_address, prev_data; reg prev_mode; reg [31:0] temp_out; reg [cache.index_size - 1:0] index; // for keeping index of current address reg [11 - cache.index_size:0] tag; // for keeping tag of ceurrent address ram ram(); cache cache(); initial begin index = 0; tag = 0; prev_address = 0; prev_data = 0; prev_mode = 0; end always @(posedge clk) begin //check if the new input is updated if (prev_address != address || prev_data != data || prev_mode != mode) begin prev_address = address % ram.size; prev_data = data; prev_mode = mode; tag = prev_address >> cache.index_size; // tag = first bits of address except index ones (In our particular case - 6) index = address % cache.size; // index value = last n (n = size of cache) bits of address if (mode == 1) begin ram.ram[prev_address] = data; //write new data to the relevant cache block if there is such one if (cache.valid_array[index] == 1 && cache.tag_array[index] == tag) cache.cache[index] = data; end else begin //write new data to the relevant cache's block, because the one we addressing to will be possibly addressed one more time soon if (cache.valid_array[index] != 1 || cache.tag_array[index] != tag) begin cache.valid_array[index] = 1; cache.tag_array[index] = tag; cache.cache[index] = ram.ram[prev_address]; end temp_out = cache.cache[index]; end end end assign out = temp_out; endmodule

विवरणमेमोरी मॉड्यूल में डेटा के साथ काम के लिए संचालन का प्रतिनिधित्व करता है। प्रत्येक घड़ी सकारात्मक बढ़त पर इनपुट हो जाता है। जाँचता है कि क्या नए इनपुट हैं - मोड के आधार पर (लिखने के लिए 1 / पढ़ने के लिए) प्रासंगिक संचालन को निष्पादित करता है। यदि मोड 1 है (लिखें):

• पता करने के लिए डेटा लिखें फिर जांचें कि क्या कैश में इनपुट पता मौजूद है, यदि ऐसा है - डेटा को बदलें, अन्यथा स्टैंडस्टिल।

यदि मोड 0 है (पढ़ें):

• जांचें कि क्या कैश में इनपुट पता मौजूद है, यदि ऐसा है - डेटा वापस लौटाएं, अन्यथा रैम से डेटा प्राप्त करें। नए डेटा के साथ कैश में पता ताज़ा करें।

testbenches:

Code1 module testbench; reg [31:0] address, data; reg mode, clk; wire [31:0] out; cache_and_ram tb( .address(address), .data(data), .mode(mode), .clk(clk), .out(out) ); initial begin clk = 1'b1; address = 32'b00000000000000000000000000000000; // 0 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b1; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000010000000100001010101; // 526421 mode = 1'b1; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000001100000110001101100010110; // 25369366 mode = 1'b1; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b1; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b1; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000000000000000000000000000000; // 0 mode = 1'b0; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000000000000000000000000; // 0 mode = 1'b0; #200 address = 32'b00000000000000000000000000000000; // 0 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b0; end initial $monitor("address = %d data = %d mode = %d out = %d", address % 4096, data, mode, out); always #25 clk = ~clk; endmodule

Code2 module testbench2; reg [31:0] address, data; reg mode, clk; wire [31:0] out; cache_and_ram tb( .address(address), .data(data), .mode(mode), .clk(clk), .out(out) ); initial begin clk = 1'b1; address = 32'b00000000000000000000000000000000; // 0 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b1; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000010000000100001010101; // 526421 mode = 1'b1; #200 address = 32'b00000000000000000000000000000000; // 0 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b0; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000010000000100001010101; // 526421 mode = 1'b0; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000001100000110001101100010110; // 25369366 mode = 1'b1; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000001100000110001101100010110; // 25369366 mode = 1'b0; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b1; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000000000000000011100011000000; // 14528 mode = 1'b1; #200 address = 32'b00000000000011110100011111010001; // 1001425 % size = 2001 data = 32'b00000000000000000000000000000000; // 0 mode = 1'b0; #200 address = 32'b10100111111001011111101111011100; // 2816867292 % size = 3036 data = 32'b00000000000000000000000000000000; // 0 mode = 1'b0; end initial $monitor("address = %d data = %d mode = %d out = %d", address % 4096, data, mode, out); always #25 clk = ~clk; endmodule

विवरणएक टेस्टबेंच चलाने के लिए, सभी फाइलों को मॉडलसिम प्रोजेक्ट में लोड करें और टेस्टबेंच फ़ाइलों में से एक का सिमुलेशन चलाएं।