कल मुझे साइबेरिया से दसवें ग्रेडर का एक पत्र मिला जो माइक्रोप्रोसेसर डेवलपर बनना चाहता है। इस क्षेत्र में उसे पहले से ही कुछ नतीजे मिले - उसने सबसे सरल स्कूल मेप्स प्रोसेसर में गुणन निर्देश को जोड़ा, इसे इंटेल एफपीजीए मैक्स 10 एफपीजीए के लिए संश्लेषित किया, अधिकतम आवृत्ति और साधारण कार्यक्रमों की उत्पादकता में वृद्धि को निर्धारित किया। उसने यह सब पहली बार नोवोसिबिर्स्क क्षेत्र के बर्मिस्ट्रोवो गांव में किया और फिर टॉम्स्क में एक सम्मेलन में।

अब दशा क्रिवरोचको (दसवें ग्रेडर का नाम) मॉस्को बोर्डिंग स्कूल में रहने के लिए चले गए और मुझसे पूछते हैं कि उन्हें और क्या डिजाइन करना चाहिए। मुझे लगता है कि अपने करियर में इस स्तर पर, उन्हें मल्टीप्लेक्शन के लिए सिस्टोलिक सरणी के आधार पर तंत्रिका नेटवर्क के लिए एक हार्डवेयर त्वरक डिज़ाइन करना चाहिए। Verilog हार्डवेयर विवरण भाषा और इंटेल FPGA FPGA का उपयोग करें, लेकिन सस्ते MAX10 नहीं, लेकिन एक बड़े सिस्टोलिक सरणी को समायोजित करने के लिए कुछ अधिक महंगा।

उसके बाद, स्कूलमप्स प्रोसेसर पर चलने वाले प्रोग्राम के साथ हार्डवेयर समाधान के प्रदर्शन की तुलना करें, साथ ही डेस्कटॉप कंप्यूटर पर चलने वाले पायथन प्रोग्राम के साथ। एक परीक्षण मामले के रूप में, एक छोटे मैट्रिक्स से संख्याओं की मान्यता का उपयोग करें।

वास्तव में, इस अभ्यास के सभी हिस्सों को पहले से ही अलग-अलग लोगों द्वारा विकसित किया गया है, लेकिन पूरे बिंदु को एक एकल प्रलेखित अभ्यास में डाल दिया गया है, जिसे तब ऑनलाइन पाठ्यक्रम और व्यावहारिक प्रतियोगिताओं के लिए आधार के रूप में इस्तेमाल किया जा सकता है:

1) eNano, RUSNANO का शैक्षिक विभाग, जिसने अतीत में छात्रों के लिए आधुनिक इलेक्ट्रॉनिक्स (RTL-to-GDSII मार्ग) के डिजाइन पर चार्ल्स दंचेक सेमिनार आयोजित किया था और वर्तमान में इस तरह के एक ऑनलाइन कोर्स पर काम कर रहा है (रजिस्टर ट्रांसफर + न्यूरल नेटवर्क के स्तर पर हार्डवेयर डिजाइन करना) में रुचि है। उन्नत छात्रों के लिए लाइट कोर्स। यहाँ चार्ल्स और मैं अपने कार्यालय में हैं:

2) ओलंपिक के लिए आधार

एनटीआई ओलंपिक में रुचि हो सकती है, जिसके साथ मैंने मास्को में कुछ हफ्ते पहले इस मुद्दे को उठाया था। इस तरह के एक उदाहरण के लिए, ओलिंपियाड्स में भाग लेने वाले विभिन्न सक्रियण कार्यों के लिए एक हार्डवेयर जोड़ सकते हैं। यहाँ NTI ओलंपिक के सहयोगी हैं:

इसलिए यदि दशा इसे विकसित करती है, तो वह सैद्धांतिक रूप से अपने वर्णित त्वरक को RUSNANO और NTI ओलंपियाड दोनों में पेश कर सकती है। मुझे लगता है कि यह उसके स्कूल के प्रशासन के लिए फायदेमंद होगा - इसे टीवी पर दिखाया जा सकता है या सामान्य रूप से इंटेल एफपीजीए प्रतियोगिता में भेजा जा सकता है। यहाँ

सांता क्लारा, कैलिफ़ोर्निया में इंटेल FPGA प्रतियोगिता के फाइनल में सेंट पीटर्सबर्ग के रूसियों के जोड़े हैं:

अब बात करते हैं प्रोजेक्ट के तकनीकी पक्ष की। सिस्टोलिक द्रव्यमान त्वरक के विचार का वर्णन

खबरा व्याचेस्लाव के संपादक

गोल्वानोव SLY_G के लेख में किया गया है।

TPU गहरी शिक्षा के लिए इतने उपयुक्त क्यों हैं?यह वही है जो डेटाफ्लो न्यूरल नेटवर्क ग्राफ आसान पहचान के लिए दिखता है:

एक आदिम कम्प्यूटेशनल तत्व जो गुणन और परिवर्धन करता है:

इस तरह के तत्वों की एक दृढ़ता से पाइप लाइन संरचना, मैट्रिक्स गुणन के लिए यह सिस्टोलिक सरणी है:

इंटरनेट पर वेरिलोग और वीएचडीएल पर एक सिस्टोलिक सरणी के कार्यान्वयन के साथ कोड का एक गुच्छा है, उदाहरण के लिए, कोड

इस ब्लॉग पोस्ट के तहत है :

module top(clk,reset,a1,a2,a3,b1,b2,b3,c1,c2,c3,c4,c5,c6,c7,c8,c9); parameter data_size=8; input wire clk,reset; input wire [data_size-1:0] a1,a2,a3,b1,b2,b3; output wire [2*data_size:0] c1,c2,c3,c4,c5,c6,c7,c8,c9; wire [data_size-1:0] a12,a23,a45,a56,a78,a89,b14,b25,b36,b47,b58,b69; pe pe1 (.clk(clk), .reset(reset), .in_a(a1), .in_b(b1), .out_a(a12), .out_b(b14), .out_c(c1)); pe pe2 (.clk(clk), .reset(reset), .in_a(a12), .in_b(b2), .out_a(a23), .out_b(b25), .out_c(c2)); pe pe3 (.clk(clk), .reset(reset), .in_a(a23), .in_b(b3), .out_a(), .out_b(b36), .out_c(c3)); pe pe4 (.clk(clk), .reset(reset), .in_a(a2), .in_b(b14), .out_a(a45), .out_b(b47), .out_c(c4)); pe pe5 (.clk(clk), .reset(reset), .in_a(a45), .in_b(b25), .out_a(a56), .out_b(b58), .out_c(c5)); pe pe6 (.clk(clk), .reset(reset), .in_a(a56), .in_b(b36), .out_a(), .out_b(b69), .out_c(c6)); pe pe7 (.clk(clk), .reset(reset), .in_a(a3), .in_b(b47), .out_a(a78), .out_b(), .out_c(c7)); pe pe8 (.clk(clk), .reset(reset), .in_a(a78), .in_b(b58), .out_a(a89), .out_b(), .out_c(c8)); pe pe9 (.clk(clk), .reset(reset), .in_a(a89), .in_b(b69), .out_a(), .out_b(), .out_c(c9)); endmodule module pe(clk,reset,in_a,in_b,out_a,out_b,out_c); parameter data_size=8; input wire reset,clk; input wire [data_size-1:0] in_a,in_b; output reg [2*data_size:0] out_c; output reg [data_size-1:0] out_a,out_b; always @(posedge clk)begin if(reset) begin out_a<=0; out_b<=0; out_c<=0; end else begin out_c<=out_c+in_a*in_b; out_a<=in_a; out_b<=in_b; end end endmodule

मैं ध्यान देता हूं कि यह कोड अनुकूलित नहीं है और आम तौर पर अनाड़ी (और यहां तक कि अव्यवसायिक रूप से लिखा गया है - पोस्ट में स्रोत @ (posedge clk) में ब्लॉक असाइनमेंट का उपयोग करता है - मैंने इसे ठीक किया)। उदाहरण के लिए दशा अधिक सुंदर कोड के लिए वेरिलॉग जेनरेट निर्माण का उपयोग कर सकती है।

तंत्रिका नेटवर्क के दो चरम कार्यान्वयन (प्रोसेसर पर और सिस्टोलिक सरणी पर) के अलावा, दशा अन्य विकल्पों पर विचार कर सकती है जो प्रोसेसर की तुलना में तेज़ हैं, लेकिन सिस्टोलिक सरणी की तरह गुणा संचालन के रूप में प्रचंड नहीं। सच है, यह अधिक संभावना स्कूली बच्चों के लिए नहीं है, लेकिन छात्रों के लिए है।

एक विकल्प एक निष्पादन उपकरण है, जो बड़ी संख्या में फ़ंक्शन ब्लॉक समानांतर में काम करता है, जैसा कि आउट-ऑफ-ऑर्डर प्रोसेसर में:

एक अन्य विकल्प तथाकथित मोटे अनाज को पुन: उपयोग करने योग्य सरणी है - अर्ध-प्रोसेसर तत्वों का एक मैट्रिक्स, जिसमें से प्रत्येक का एक छोटा कार्यक्रम है। ये प्रोसेसर तत्व आदर्श रूप से FPGA / FPGA कोशिकाओं के समान हैं, लेकिन व्यक्तिगत संकेतों के साथ काम नहीं करते हैं, लेकिन बसों और रजिस्टरों पर बिट / संख्याओं के समूहों के साथ -

हार्डवेयर AI में एक प्रमुख खिलाड़ी के जन्म से लाइव रिपोर्ट देखें

, जो सेंसर को गति देता है और NVidia के साथ प्रतिस्पर्धा करता है " ।

अब दशा से मूल पत्र:

शुभ दिन, यूरी।

2017 में, मैंने आपकी कार्यशाला में LSHUP में आपके स्कूल में अध्ययन किया और अक्टूबर 2017 में मैंने उसी वर्ष अक्टूबर में टॉम्स्क में एक सम्मेलन में भाग लिया जिसमें SchooolMIPS प्रोसेसर में गुणन इकाई को एम्बेड करने के लिए समर्पित था।

मैं अब यह काम जारी रखना चाहूंगा। फिलहाल, मैं इस विषय को एक छोटे शोध के रूप में लेने के लिए स्कूल में अनुमति प्राप्त करने में कामयाब रहा। क्या आपके पास इस काम की निरंतरता के साथ मेरी मदद करने का अवसर है?

पुनश्च चूंकि कार्य एक विशिष्ट प्रारूप में किया जाता है, एक परिचय लिखना और विषय की साहित्य समीक्षा की आवश्यकता होती है। कृपया उन स्रोतों से सलाह लें जिनसे आप इस विषय के विकास के इतिहास, वास्तुशिल्प दर्शन, आदि पर जानकारी ले सकते हैं, यदि आपके पास ऐसे संसाधन हैं।

इसके अलावा, फिलहाल मैं एक बोर्डिंग स्कूल में मॉस्को में रहता हूं, बातचीत करना आसान हो सकता है।

निष्ठा से,

दरिया क्रिवोरुचको।

दशा ने

डेविड हैरिस और सारा हैरिस द्वारा मेरी और पुस्तक

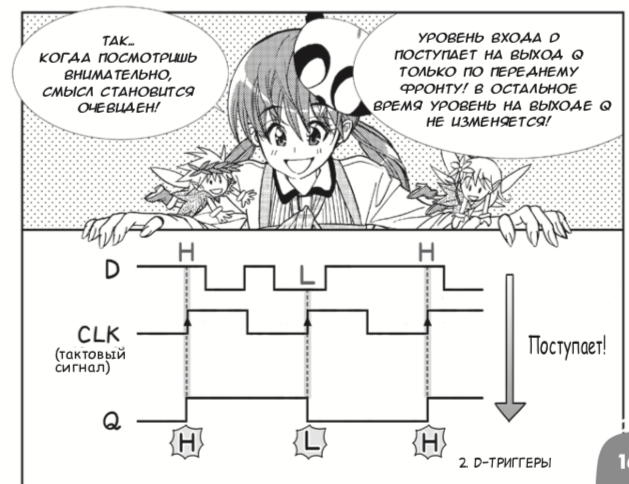

"डिजिटल सर्किटरी एंड कंप्यूटर आर्किटेक्चर" की मदद से वेरिलॉग और रजिस्टर-स्तरीय डिज़ाइन सिखाया। हालाँकि, यदि आप एक स्कूली छात्र / छात्रा हैं और बहुत सरल स्तर पर बुनियादी अवधारणाओं को समझना चाहते हैं, तो आपके लिए प्रकाशन गृह DMK-प्रेस ने Amano Hideharu और Meguro Koji द्वारा बनाए गए

डिजिटल सर्किट के

बारे में जापानी मंगा 2013 का रूसी अनुवाद जारी किया है। प्रस्तुति के तुच्छ रूप के बावजूद, पुस्तक तार्किक तत्वों और डी-ट्रिगर्स को सही ढंग से पेश करती है,

और फिर इसे FPGAs के लिए बांध देती है :

यहाँ नोवोसिबिर्स्क क्षेत्र में

यंग प्रोग्रामर्स के लिए समर स्कूल क्या दिखता है, जहां दशा ने वेरिलॉग, एफपीजीएएस, एक रजिस्टर ट्रांसफर डेवलपमेंट मेथडोलॉजी (रजिस्टर ट्रांसफर लेवल - आरटीएल) सीखा:

और यहाँ एक और दसवें ग्रेडर आर्सेनी चेगोडेव के साथ टॉम्स्क में सम्मेलन में दशा का भाषण है:

दशा की मेरे और स्टैनिस्लाव ज़ेल्नियो

स्पार्फ़ के साथ बात करने के बाद, FPGAs पर कार्यान्वयन के लिए schoolMIPS शैक्षिक प्रोसेसर कोर के मुख्य निर्माता:

SchoolMIPS परियोजना

https://github.com/MIPSfpga/schoolMIPS पर प्रलेखन के साथ है। इस प्रशिक्षण प्रोसेसर कोर के सरलतम विन्यास में, वेरिलोग में केवल 300 लाइनें हैं, जबकि मध्यम वर्ग के औद्योगिक एम्बेडेड कोर में लगभग 300 हजार लाइनें हैं। फिर भी, दशा यह महसूस करने में सक्षम थी कि उद्योग में डिजाइनरों का काम कैसा दिखता है, जो डिकोडर और निष्पादित डिवाइस को उसी तरह से बदलते हैं जब वे प्रोसेसर में नए निर्देश जोड़ते हैं:

अंत में, हम समारा विश्वविद्यालय इल्या कुद्रीवत्सेव के डीन की तस्वीरें प्रस्तुत करते हैं, जो भविष्य के आवेदकों के लिए एफपीजीए प्रोसेसर के साथ एक ग्रीष्मकालीन स्कूल और ओलंपियाड बनाने में रुचि रखते हैं:

और ज़ेलेनोग्राड एमआईईटी के कर्मचारियों की एक तस्वीर जो पहले से ही इस तरह के ग्रीष्मकालीन स्कूल की योजना बना रहे हैं:

RUSNANO की सामग्री, और NTI ओलंपिक की संभावित सामग्री और साथ ही HSE MIEM, मास्को स्टेट यूनिवर्सिटी और

कज़ान इन्नोपोलिस के कार्यक्रम में FPGAs और माइक्रोआर्किटेक्चर के कार्यान्वयन में पिछले कुछ वर्षों में जो उपलब्धियां हासिल की गई हैं

, वे एक जगह और दूसरी जगह अच्छी तरह से होनी चाहिए।