सरू के यूडीबी माइक्रोकंट्रोलर ब्लॉक पीएसओसी का उपयोग करके आरजीबी एलईडी को नियंत्रित करने के बारे में

सरू के यूडीबी माइक्रोकंट्रोलर ब्लॉक पीएसओसी का उपयोग करके आरजीबी एलईडी को नियंत्रित करने के बारे में मेरे

लेख में, यह सुझाव दिया गया था कि लेख की शुरुआत में संक्षेप में बताना अच्छा होगा कि यूडीबी क्या है। जैसा कि मैंने पहले ही लेख में उल्लेख किया है, मैं यूडीबी के बारे में संक्षेप में नहीं लिख सकता, लेकिन आप फ़र्मवेयर फ़ंक्शंस को लागू करने के लिए इस तरह के एक शक्तिशाली टूल के साथ घरेलू रीडर को परिचित करने के लिए कंपनी प्रलेखन को बस इसमें स्थानांतरित कर सकते हैं।

लेकिन पहले, आइए देखें कि पीएसओसी आखिर क्या है। PSoC चिप-सिस्टम को लागू करने के लिए चिपसेट का एक सरू परिवार है। विभिन्न परिवारों में एक अलग प्रोसेसर कोर है (PSoC 3 के लिए यह MCS-51 है, PSoC 4 के लिए यह Cortex M0 है, PSoC 5LP के लिए यह Cortex M3 है, और PSoC 6 के लिए यह एक बार में दो बार है: Cortex M0 + और Cortex M4) और प्रोग्राम तर्क का एक सेट है। इसके अलावा, यह तर्क विशुद्ध रूप से डिजिटल नहीं है, वहां एनालॉग चीजें हैं। विभिन्न एडीसी के एक सेट के अलावा, एनालॉग स्विच भी हैं। आप प्रोग्राम को एनालॉग सर्किट के माध्यम से पैरों से जोड़ सकते हैं, हालांकि, सर्किट का प्रतिरोध किलोग्राम में मापा जाएगा। PSoC के अंदर परिचालन एम्पलीफायरों हैं जिन्हें प्रोग्रामेटिक रूप से स्विच किया जा सकता है, जिसका अर्थ है कि आप उन पर विभिन्न एनालॉग ब्लॉक बना सकते हैं।

वैसे, PSoCs को 2.7 से 5.5 वोल्ट तक किसी भी वोल्टेज द्वारा संचालित किया जा सकता है। यही है, आपको किसी भी प्रकार के स्टेबलाइजर्स के बारे में बैटरी पावर या यूएसबी पावर के साथ सोचने की आवश्यकता नहीं है।

लेकिन मैंने एनालॉग चीजों के बारे में शुद्ध रूप से लाल शब्द के लिए लिखा। अब हम डिजिटल चीजों पर ध्यान केंद्रित करेंगे। अधिकांश आधुनिक नियंत्रकों में शक्तिशाली परिधीय इकाइयाँ होती हैं जो कई प्रकार के कार्य प्रदान करती हैं। लेकिन व्यवहार में, प्रत्येक विशिष्ट सॉफ़्टवेयर विकास में, ये ब्लॉक पूरी तरह से उपयोग नहीं किए जाते हैं, लेकिन केवल आंशिक रूप से। और PSoC में, अच्छे की एक गुच्छा के बजाय, प्रोग्राम तर्क को लागू किया जाता है, क्लासिक FPGAs के तर्क के समान। तदनुसार, उन ब्लॉकों को ठीक से लागू करना संभव है जो उन पर आवश्यक हैं, उन्हें उन मोड में शामिल करना आवश्यक है। और संसाधनों को अप्रयुक्त साधनों पर खर्च नहीं किया जाना चाहिए, उन्हें कुछ प्रकार की चीजों के कार्यान्वयन के लिए दूर करना।

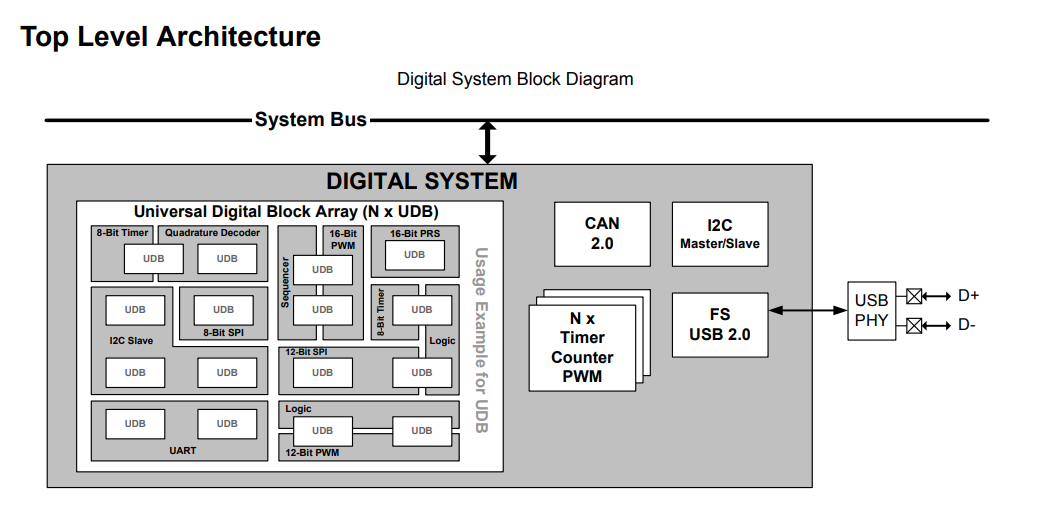

और यहाँ कुछ गलतफहमी अक्सर पैदा होती है। कई डेवलपर्स इस तथ्य के लिए उपयोग किए जाते हैं कि दो प्रकार के प्रोग्रामेबल लॉजिक इंटीग्रेटेड सर्किट (FPGAs) हैं: CPLD और FPGA। इसलिए, कई जिन्होंने PSoC के बारे में सुना है, उनका मानना है कि एक प्रकार का CPLD-box निहित है जिसे Veriolg में प्रोग्राम किया जा सकता है। वास्तव में, हाँ और नहीं। पीएलडी की एक निश्चित संख्या ("सी" के बिना, बस पीएलडी) वास्तव में वहां हैं, और आप वास्तव में उन्हें वेरिलोग पर प्रोग्राम कर सकते हैं। लेकिन वास्तव में, ये PLD UDB ब्लॉक का हिस्सा हैं। और यह UDB है जो PSoC में लागू प्रोग्रामेबल लॉजिक का मुख्य तत्व है। यह ब्लॉक बेहद मूल है और डेवलपर के लिए बस व्यापक अवसर प्रदान करता है। UDB ब्लॉक का उपयोग करने का सार बताते हुए मालिकाना दस्तावेज से प्राप्त आंकड़ों पर विचार करें।

चूंकि मैंने एक उदाहरण के रूप में PSoC 5LP परिवार का उपयोग करके सब कुछ अध्ययन किया है, इसलिए मैं इसे दस्तावेज़ में अनुवाद करूंगा। लेकिन शुरू करने से पहले, मैं इन नियंत्रकों की कीमत के बारे में कुछ शब्द कहूँगा। यदि आप अली एक्सप्रेस में जाते हैं और उनके लिए ब्रेडबोर्ड देखते हैं, तो आपको एक दुख की अनुभूति होती है। सच कहूँ तो, STM32-DISCOVERY की तुलना में वे अभी भी कुछ भी नहीं हैं, लेकिन STM32F103C8T6 प्रोटोटाइप की तुलना में वे थोड़े महंगे हैं। सबसे पहले, यह इस तथ्य के कारण है कि कॉर्पोरेट मॉक-अप में हमेशा एक नहीं, बल्कि दो ऐसे नियंत्रक होते हैं। JTAG फ़ंक्शन PSoC 5LP पर कार्यान्वित किए जाते हैं, भले ही लक्ष्य नियंत्रक और PSoC 4 (उत्तरार्द्ध में आमतौर पर USB पोर्ट नहीं है)।

लेकिन कीमत को दो से विभाजित करते हुए, हम अभी भी प्राप्त करते हैं कि यह STM32F103 की तुलना में अधिक है, जो प्रोसेसर कोर के समान है। फिर भी, यदि हम बाहर से बहुत ही STM32 में सबसे सरल CPLD भी जोड़ते हैं, तो कुल मूल्य PSoC के पक्ष में सामने आएगा। और हम इन दोनों मामलों के कनेक्शन में खोए हुए पैर जोड़ देंगे (PSoC में सभी कनेक्शन हैं)। और बोर्ड के वर्ग सेंटीमीटर की कीमत भी। तो यह पता चला है कि अगर आपको केवल प्रोसेसर कोर के साथ काम करने की आवश्यकता है, तो पीएसओसी वास्तव में आवश्यक नहीं है। यदि आपको फर्मवेयर या हार्डवेयर स्तर पर कुछ कार्यक्षमता लाने की आवश्यकता है, तो आपको PSoC की आवश्यकता है। उस पर, सिस्टम सस्ता और आसान आ जाएगा।

वास्तव में, मेरे पास हमारे RTOS MAX के कर्नेल के लिए हार्डवेयर समर्थन बनाने की कोशिश करने के लिए एक उन्मत्त विचार है। ऐसा करने के लिए, मैंने Altera V SoC के लिए नंगे धातु अनुप्रयोगों को विकसित करने की पद्धति का अध्ययन किया (अफसोस, यह निकला कि वास्तुकला की विशेषता ऐसी है कि ओएस धीमा हो सकता है, लेकिन आप इसे गति नहीं दे सकते हैं - हार्डवेयर के लिए एकल अनुरोध पागल विलंबता के साथ आते हैं)। इसके लिए मैंने PSoC में महारत हासिल करना शुरू कर दिया। मैं कर्नेल ओवरक्लॉकिंग तक नहीं पहुंचा हूं (केवल सामान्य विचार हैं), लेकिन मुझे वास्तव में यूडीबी प्रोग्रामिंग का विचार पसंद आया। निश्चित रूप से, मैं अब इस विचार को अधिकतम घरेलू प्रोग्रामर तक पहुँचाने में दिलचस्पी रखता हूँ। इसलिए, हम UDB पर सरू मालिकाना दस्तावेज के संबंधित भाग के अनुवाद के लिए आगे बढ़ते हैं। मूल दस्तावेज के अनुसार अध्यायों और आंकड़ों की संख्या को बनाए रखा जाता है।

चक्र की सामान्य सामग्री “UDB। यह क्या है? ”

भाग 1. परिचय। पीएलडी। (वर्तमान लेख)

भाग 2. दत्तपथ।भाग 3. दत्तपथ फीफो।भाग 4. दत्तपथ ALU।भाग 5. दत्तपथ। उपयोगी छोटी चीजें।भाग 6. प्रबंधन और स्थिति मॉड्यूल।भाग 7. समय और नियंत्रण मॉड्यूल रीसेट करेंभाग 8. UDB को संबोधित करते हुएUDB। यह क्या है? भाग 1

21. यूनिवर्सल डिजिटल ब्लॉक

इस अध्याय में, हम देखेंगे कि यूनिवर्सल डिजिटल ब्लॉक (UDB) प्रोग्राम योग्य डिजिटल परिधीय कार्यों के विकास को कैसे सक्षम करते हैं। UDB आर्किटेक्चर कॉन्फ़िगरेशन और कुशल कार्यान्वयन की ग्रैन्युलैरिटी के बीच संतुलन बनाता है। UDBs में प्रोग्रामेबल लॉजिक मैट्रिक्स (PLM, इंग्लिश PLD), स्ट्रक्चर्ड लॉजिक (ऑपरेशनल मशीन, इसके बाद डाटापथ के रूप में संदर्भित) और एक लचीली ट्रेसिंग स्कीम के समान गैर-कम्यूटेड लॉजिक का संयोजन होता है।

21.1 सुविधाएँ

- इष्टतम लचीलेपन के लिए, प्रत्येक UDB में निम्नलिखित घटक होते हैं:

• 8-निर्देश अनुदेश भंडार, कई रजिस्टर और फीफो बफ़र्स के साथ ALU (अंकगणित और तर्क इकाई, ALU) पर आधारित 8-बिट डाटापथ;

• दो पीएलडी, जिनमें से प्रत्येक में 12 इनपुट, आठ संयुग्मन शब्द (उत्पाद शर्तें, पीटी) और चार मैक्रोसेल आउटपुट हैं;

• प्रबंधन और स्थिति रजिस्टर;

• घड़ी और रीसेट मॉड्यूल। - PSoC 5LP में आकार में 24 UDB तक की सरणी होती है।

- UDB सरणी तत्वों के बीच लचीला अनुरेखण।

- UDB तत्वों को बड़ा कार्य बनाने के लिए विभाजित या जंजीर किया जा सकता है।

- टाइमर, काउंटर, पल्स चौड़ाई न्यूनाधिक (एक डेडबैंड जनरेटर के साथ PWM सहित), UART, I2C बस, SPI बस और CRC सत्यापन / पीढ़ी सहित कई डिजिटल कार्यों का लचीला कार्यान्वयन।

21.2 ब्लॉक आरेख

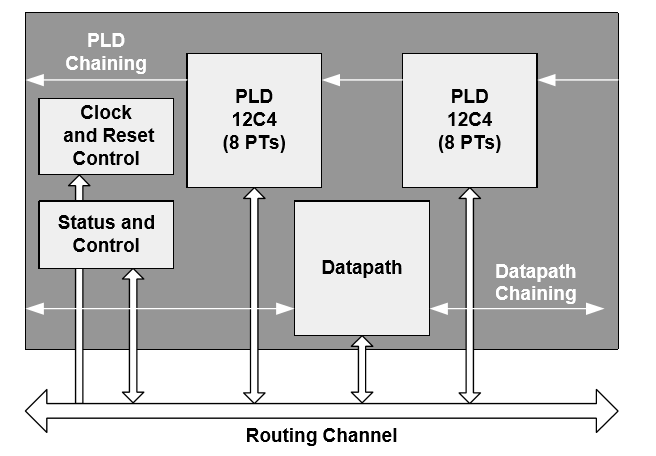

चित्र 21-1 दो मूलभूत तार्किक ब्लॉकों, PLD, डेटापथ और नियंत्रण, स्थिति, घड़ी और रीसेट कार्यों वाले निर्माण के रूप में UDB को दर्शाता है।

चित्र 21-1। UDB के ब्लॉक आरेख।

चित्र 21-1। UDB के ब्लॉक आरेख।21.3 यह कैसे काम करता है

UDB के मुख्य घटक हैं:

- पीएलडी (2)। ट्रेस संसाधनों से डेटा इन ब्लॉकों के इनपुट को खिलाया जाता है। वे संयोजन तर्क और डेटा स्निपिंग को लागू करते हैं, जो आपको परिमित राज्य मशीनों को लागू करने, डाटापथ ब्लॉक के संचालन को नियंत्रित करने, इनपुट स्थितियों को कॉन्फ़िगर करने और आउटपुट को नियंत्रित करने की अनुमति देता है।

- Datapath। इस ब्लॉक में गतिशील रूप से प्रोग्राम किए जाने वाले ALU, चार रजिस्टर, दो FIFO बफ़र, तुलनित्र और स्थिति निर्माण शामिल हैं।

- प्रबंधन और स्थिति (स्थिति और नियंत्रण)। ये मॉड्यूल केंद्रीय प्रोसेसर (सीपीयू) के माइक्रोप्रोग्राम की बातचीत और यूडीबी संचालन के साथ सिंक्रनाइज़ेशन के लिए एक तंत्र प्रदान करते हैं। नियंत्रण रजिस्टर आंतरिक तत्वों पर कार्य करते हैं, और स्थिति रजिस्टर बाहरी तत्वों की स्थिति को पढ़ते हैं।

- घड़ी और रीसेट नियंत्रण ये मॉड्यूल समय चयन और सक्षमता प्रदान करते हैं, साथ ही UDB के भीतर चयन को रीसेट करते हैं।

- चैनिंग सिग्नल। पीएलडी और डाटापथ में ऐसे संकेत हैं जो आपको उच्च-बिट फ़ंक्शन बनाने के लिए एक श्रृंखला में आसन्न ब्लॉकों को चेन करने की अनुमति देते हैं।

- ट्रेसिंग चैनल UDB एक ही UDB के भीतर ब्लॉक के बीच संचार के लिए ट्रेस करने योग्य चैनल के माध्यम से ट्रेस चैनल से जुड़े हुए हैं और सरणी में अन्य UDBs के साथ संचार के लिए।

- सिस्टम बस इंटरफ़ेस (Sysytem Bus Interface)। प्रत्येक UDB में सभी रजिस्टरों और रैम को सिस्टम एड्रेस स्पेस पर प्रोजेक्ट किया जाता है, और केंद्रीय प्रोसेसर का उपयोग करके और डायरेक्ट मेमोरी एक्सेस (इंग्लिश डायरेक्ट मेमोरी एक्सेस, डीएमए) के माध्यम से 8-बिट और 16-बिट के रूप में दोनों तक पहुंच प्राप्त की जा सकती है। डेटा।

21.3.1। पीएलडी

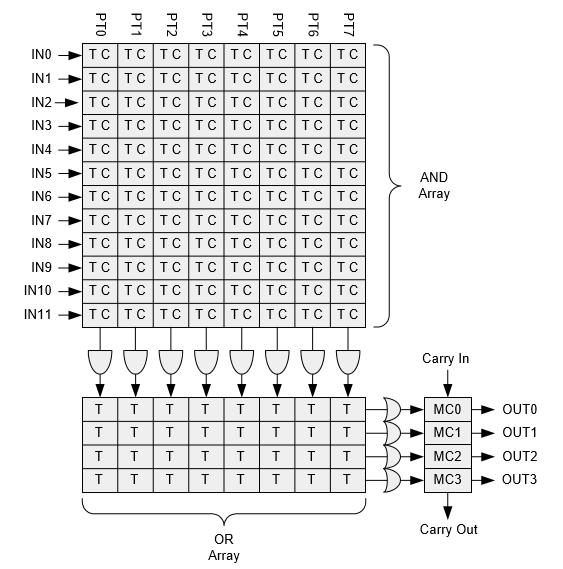

प्रत्येक UDB में दो 12C4 PLD हैं। चित्र 21-1 में दिखाए गए PLD ब्लॉक का उपयोग राज्य मशीनों को लागू करने, I / O डेटा को संसाधित करने और टेबल लॉजिक (Eng। लुकअप टेबल, LUT) बनाने के लिए किया जा सकता है। इसके अलावा, पीएलडी को अंकगणितीय कार्यों को करने के लिए कॉन्फ़िगर किया जा सकता है, डेटापथ अनुक्रम सेट कर सकता है, और स्थिति उत्पन्न कर सकता है। पीएलडी ब्लॉकों पर सामान्य तर्क को संश्लेषित और अनुमानित किया जा सकता है। यह खंड पीएलडी वास्तुकला का अवलोकन प्रदान करता है।

PLD में 12 इनपुट होते हैं जो एक एंड सरणी में 8 संयुग्मित शब्दों में जानकारी संचारित करते हैं। प्रत्येक संयोजी शब्द में, आप एक प्रत्यक्ष (सही, T) या उलटा (पूरक, C) इनपुट चुन सकते हैं। संयुग्मन शब्दों का आउटपुट OR सरणी के इनपुट में जाता है। 12C4 में 'C' अक्षर इंगित करता है कि OR शर्तें सभी इनपुटों के लिए स्थिर हैं, और प्रत्येक OR इनपुट किसी भी संयुग्मित शब्द के लिए प्रोग्रामेटिक एक्सेस प्राप्त कर सकता है। यह संरचना अधिकतम लचीलापन प्रदान करती है और सुनिश्चित करती है कि सभी इनपुट और आउटपुट को स्थानांतरित किया जा सकता है।

चित्र 21-2। पीएलडी 12C4 की संरचना।

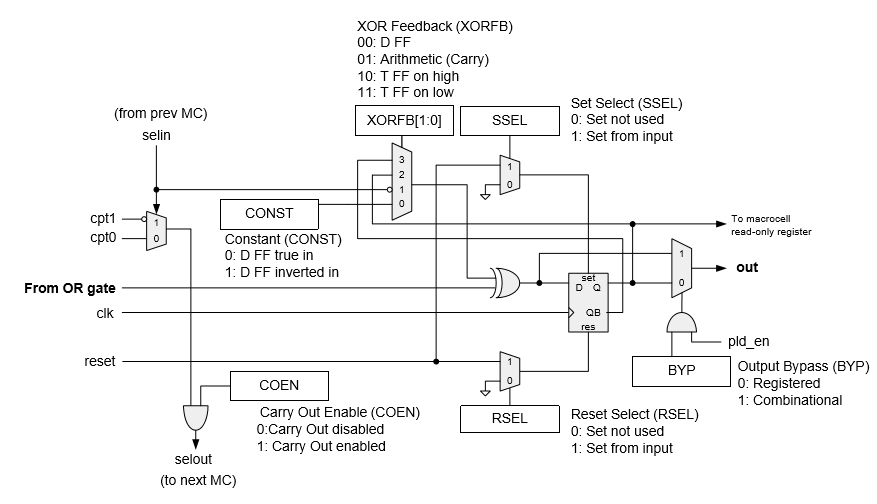

चित्र 21-2। पीएलडी 12C4 की संरचना।21.3.1.1 मैक्रो पीएलडी

मैक्रोकल्स की वास्तुकला को चित्र 21-3 में दिखाया गया है। आउटपुट ट्रेस सरणी को नियंत्रित करता है और इसे रच या रमन किया जा सकता है। लैचिंग के लिए, प्रत्यक्ष या उलटा इनपुट के साथ डी-ट्रिगर या उच्च या निम्न इनपुट स्तर के साथ टी-ट्रिगर का उपयोग किया जाता है। ट्रेस चैनल से एक बाहरी संकेत द्वारा आउटपुट ट्रिगर को इनिशियलाइज़ेशन या एसिंक्रोनसली सामान्य ऑपरेशन के दौरान सेट या रीसेट किया जा सकता है।

चित्र 21-3। मैक्रोसेल वास्तुकला।पढ़ें- केवल PLD मैक्रो सेल रजिस्टर

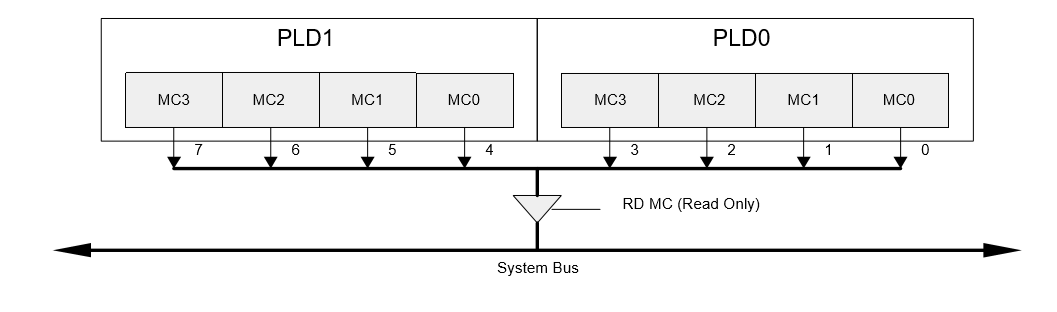

चित्र 21-3। मैक्रोसेल वास्तुकला।पढ़ें- केवल PLD मैक्रो सेल रजिस्टरट्रेस सरणी को नियंत्रित करने के अलावा, दोनों पीएलडी के मैक्रोसेल आउटपुट को 8-बिट रीड-ओनली रजिस्टर के रूप में एड्रेस स्पेस पर प्रोजेक्ट किया जाता है, जिसे सीपीयू या डीएमए का उपयोग करके एक्सेस किया जा सकता है।

चित्र 21-4। केवल पढ़ने के लिए PLD मैक्रोकोड रजिस्टर।

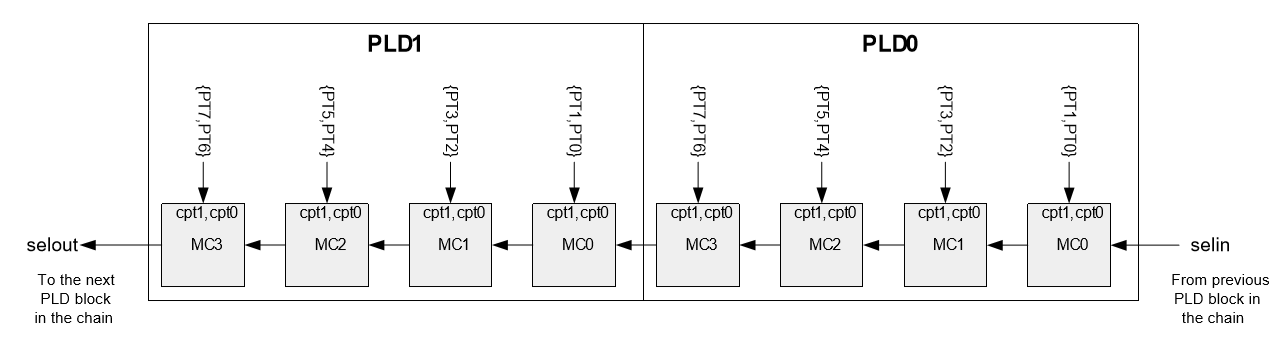

चित्र 21-4। केवल पढ़ने के लिए PLD मैक्रोकोड रजिस्टर।21.3.1.2 हाइफ़नेशन चेन PLD

PLD को UDB एड्रेसिंग में एक साथ बांधा गया है। जैसा कि चित्र 21-5 में दिखाया गया है, सेलिन कैरी चेन के इनपुट को पिछले UDB से सर्किट तक, दोनों PLD में प्रत्येक मैक्रो सेल के माध्यम से भेजा जाता है, फिर इसे SUTout श्रृंखला के आउटपुट के रूप में अगले UDB पर भेज दिया जाता है। अंकगणितीय कार्यों के कुशल प्लेसमेंट का समर्थन करने के लिए, विशेष संयुग्मन शब्द (पीटी) उत्पन्न होते हैं, जो एक जलसेक श्रृंखला के साथ मैक्रोकल्स में उपयोग किए जाते हैं।

चित्र 21-5। पीएलडी हाइफ़नेशन चेन और विशेष संयुग्मित अवधि इनपुट।

चित्र 21-5। पीएलडी हाइफ़नेशन चेन और विशेष संयुग्मित अवधि इनपुट।21.3.1.3 PLD कॉन्फ़िगरेशन

प्रत्येक PLD 16-बिट एक्सेस के साथ RAM के रूप में CPU या DMA से पहले दिखाई देता है। AND सरणी में प्रोग्रामिंग के लिए 12 × 8 × 2 बिट्स या 24 बाइट्स हैं, और OR सरणी में प्रोग्रामिंग के लिए 4 × 8 बिट्स या 4 बाइट्स हैं। इसके अलावा, प्रत्येक मैक्रो सेल में एक कॉन्फ़िगरेशन बाइट होती है, कुल पीएलडी प्रति 32 कॉन्फ़िगरेशन बाइट्स। चूंकि प्रत्येक UDB में 2 PLD हैं, प्रत्येक UDB का कुल कॉन्फ़िगरेशन 64 बाइट्स है।

अगली बार हम ऑपरेशनल ऑटोमेटा (डेटापैथ्स) पर विचार करेंगे।