लेख इसके लिए अगले आदिम प्रोसेसर और कोडांतरक का वर्णन करता है।

लेख इसके लिए अगले आदिम प्रोसेसर और कोडांतरक का वर्णन करता है।

सामान्य RISC / CISC के बजाय, प्रोसेसर के पास प्रति निर्देश का एक सेट नहीं है, केवल एक कॉपी निर्देश है।

इसी तरह के प्रोसेसर में मैक्सिम MAXQ श्रृंखला है।

सबसे पहले, ROM का वर्णन करें, प्रोग्राम मेमोरी

module rom1r(addr_r, data_r); parameter ADDR_WIDTH = 8; parameter DATA_WIDTH = 8; input [ADDR_WIDTH - 1 : 0] addr_r; output [DATA_WIDTH - 1 : 0] data_r; reg [DATA_WIDTH - 1 : 0] mem [0 : (1<<ADDR_WIDTH) - 1]; initial $readmemh("rom.txt", mem, 0, (1<<ADDR_WIDTH) - 1); assign data_r = mem[addr_r]; endmodule

डेटा मेमोरी के लिए ड्यूल पोर्ट रैम

module ram1r1w(clk_wr, addr_w, data_w, addr_r, data_r); parameter ADDR_WIDTH = 8; parameter DATA_WIDTH = 8; input clk_wr; input [ADDR_WIDTH - 1 : 0] addr_r, addr_w; output [DATA_WIDTH - 1 : 0] data_r; input [DATA_WIDTH - 1 : 0] data_w; reg [DATA_WIDTH - 1 : 0] mem [0 : (1<<ADDR_WIDTH) - 1]; assign data_r = mem[addr_r]; always @ (posedge clk_wr) mem[addr_w] <= data_w; endmodule

और प्रोसेसर ही

module cpu(clk, reset, port); parameter WIDTH = 8; parameter RAM_SIZE = WIDTH; parameter ROM_SIZE = WIDTH; input clk, reset; output [WIDTH-1 : 0] port;

कम से कम, उसे कमांड काउंटर के रजिस्टर के साथ-साथ एक सहायक रजिस्टर, अच्छी तरह से और आईओ पोर्ट रजिस्टर की आवश्यकता होती है, ताकि हमारे प्रोसेसर से कुछ दिखाई दे।

reg [WIDTH-1 : 0] reg_pc; reg [WIDTH-1 : 0] reg_reg; reg [WIDTH-1 : 0] reg_port; assign port = reg_port;

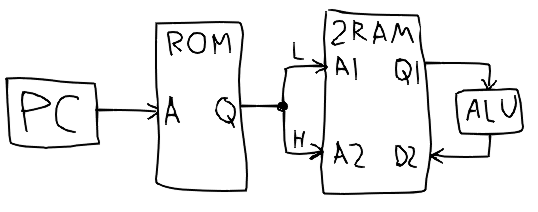

कमांड काउंटर प्रोग्राम मेमोरी के लिए एड्रेस होगा।

wire [WIDTH-1 : 0] addr_w, addr_r, data_r, data_w, data; rom1r rom (reg_pc, {addr_w, addr_r}); defparam rom.ADDR_WIDTH = ROM_SIZE; defparam rom.DATA_WIDTH = RAM_SIZE * 2;

दोहरी चौड़ाई की प्रोग्राम मेमोरी में दो पते होते हैं: जहां और जहां से डेटा को दोहरे पोर्ट डेटा मेमोरी में कॉपी करना है।

ram1r1w ram (clk, addr_w, data_w, addr_r, data_r); defparam ram.ADDR_WIDTH = RAM_SIZE; defparam ram.DATA_WIDTH = WIDTH;

हम विशेष पते निर्दिष्ट करेंगे: एक कमांड काउंटर, एक निरंतर जनरेटर, 0 के लिए एक चेक (सशर्त छलांग के लिए), इसके अलावा / घटाव संचालन, और एक इनपुट-आउटपुट पोर्ट, इस मामले में, केवल आउटपुट।

parameter PC = 0; parameter CG = 1; parameter TST = 2; parameter ADD = 3; parameter SUB = 4; parameter PORT = 5;

दो मेमोरी पोर्ट्स की डेटा बसें परस्पर जुड़ी नहीं हैं, बल्कि मल्टीप्लेक्सर्स के माध्यम से हैं, जो एक ही समय में ALU के रूप में काम करेंगी।

एक मल्टीप्लेक्सर - रीड पोर्ट के डेटा बस पर ताकि कुछ पते पर मेमोरी के बजाय, कमांड के काउंटर (रिश्तेदार संक्रमण के लिए), आईओ, आदि पढ़ें।

दूसरा रिकॉर्डिंग पोर्ट के डेटा बस पर है, इसलिए न केवल मेमोरी में डेटा स्थानांतरित करने के लिए, बल्कि उन्हें बदलने के लिए कुछ पते पर भी।

assign data = (addr_r == PC) ? reg_pc : (addr_r == PORT) ? reg_port : data_r; assign data_w = (addr_w == CG) ? addr_r : (addr_w == TST) ? |data : (addr_w == ADD) ? data + reg_reg : (addr_w == SUB) ? data - reg_reg : data;

सहायक रजिस्टर reg_reg, जो अंकगणित संचालन के लिए उपयोग किया जाता है, सीधे पहुंच योग्य नहीं है, लेकिन प्रत्येक निर्देश का परिणाम इसे कॉपी किया जाता है।

इस प्रकार, मेमोरी से दो मान जोड़ने के लिए, आपको पहले उनमें से किसी को कहीं भी पढ़ना होगा, उदाहरण के लिए, इसे अपने आप को कॉपी करें (और उसी समय reg_reg में), और योजक पते पर अगला राइट कमांड वहाँ पिछले मूल्य के साथ योग रिकॉर्ड करेगा।

निरंतर जनरेटर इस पते पर मेमोरी वैल्यू नहीं बल्कि एड्रेस लिखता है।

बिना शर्त कूद के लिए, आपको बस उस पते को कॉपी करना होगा जिसे आप reg_pc चाहते हैं, और सशर्त कूदने के लिए, एक और TST पता आरक्षित करें, जो किसी भी नॉनजरो मान को 1 में बदल देता है, और साथ ही परिणाम को 0 नहीं होने पर अगले कमांड को छोड़ने के लिए 1 के बजाय 2 से कमांड काउंटर बढ़ाता है।

always @ (posedge clk) begin if (reset) begin reg_pc <= 0; end else begin reg_reg <= data_w; if (addr_w == PC) begin reg_pc <= data_w; end else begin reg_pc <= reg_pc + (((addr_w == TST) && data_w[0]) ? 2 : 1); case (addr_w) PORT: reg_port <= data_w; endcase end end end endmodule

cpu.v module rom1r(addr_r, data_r); parameter ADDR_WIDTH = 8; parameter DATA_WIDTH = 8; input [ADDR_WIDTH - 1 : 0] addr_r; output [DATA_WIDTH - 1 : 0] data_r; reg [DATA_WIDTH - 1 : 0] mem [0 : (1<<ADDR_WIDTH) - 1]; initial $readmemh("rom.txt", mem, 0, (1<<ADDR_WIDTH) - 1); assign data_r = mem[addr_r]; endmodule module ram1r1w(write, addr_w, data_w, addr_r, data_r); parameter ADDR_WIDTH = 8; parameter DATA_WIDTH = 8; input write; input [ADDR_WIDTH - 1 : 0] addr_r, addr_w; output [DATA_WIDTH - 1 : 0] data_r; input [DATA_WIDTH - 1 : 0] data_w; reg [DATA_WIDTH - 1 : 0] mem [0 : (1<<ADDR_WIDTH) - 1]; assign data_r = mem[addr_r]; always @ (posedge write) mem[addr_w] <= data_w; endmodule module cpu(clk, reset, port); parameter WIDTH = 8; parameter RAM_SIZE = 8; parameter ROM_SIZE = 8; parameter PC = 0; parameter CG = 1; parameter TST = 2; parameter ADD = 3; parameter SUB = 4; parameter PORT = 5; input clk, reset; output [WIDTH-1 : 0] port; wire [WIDTH-1 : 0] addr_r, addr_w, data_r, data_w, data; reg [WIDTH-1 : 0] reg_pc; reg [WIDTH-1 : 0] reg_reg; reg [WIDTH-1 : 0] reg_port; assign port = reg_port; rom1r rom(reg_pc, {addr_w, addr_r}); defparam rom.ADDR_WIDTH = ROM_SIZE; defparam rom.DATA_WIDTH = RAM_SIZE * 2; ram1r1w ram (clk, addr_w, data_w, addr_r, data_r); defparam ram.ADDR_WIDTH = RAM_SIZE; defparam ram.DATA_WIDTH = WIDTH; assign data = (addr_r == PC) ? reg_pc : (addr_r == PORT) ? reg_port : data_r; assign data_w = (addr_w == CG) ? addr_r : (addr_w == TST) ? |data : (addr_w == ADD) ? data + reg_reg : (addr_w == SUB) ? data - reg_reg : data; always @ (posedge clk) begin if (reset) begin reg_pc <= 0; end else begin reg_reg <= data_w; if (addr_w == PC) begin reg_pc <= data_w; end else begin reg_pc <= reg_pc + (((addr_w == TST) && data_w[0]) ? 2 : 1); case (addr_w) PORT: reg_port <= data_w; endcase end end end endmodule

वह पूरा प्रोसेसर है।

कोडांतरक

अब हम उसके लिए एक सरल प्रोग्राम लिखेंगे जो पोर्ट पर मूल्यों को क्रमिक रूप से आउटपुट करता है और 5 पर रुक जाता है।

अपने आप को असेंबलर लिखने में बहुत आलसी था, यहां तक कि इस तरह के एक सरल (संपूर्ण वाक्य रचना ए = बी), इसलिए इसके बजाय, तैयार किए गए लुआ भाषा का उपयोग आधार के रूप में किया गया था, जो कि इसके आधार पर विभिन्न डोमेन विशिष्ट भाषाओं के निर्माण के लिए बहुत अच्छी तरह से अनुकूल है, उसी समय हमें मुफ्त में तैयार किया गया लुआ प्रीप्रोसेसर मिलता है। ।

सबसे पहले, विशेष पतों की घोषणा, प्रविष्टि जिसमें डेटा और काउंटर चर 7 पते पर बदलता है

require ("asm") PC = mem(0) CG = mem(1) TST = mem(2) ADD = mem(3) SUB = mem(4) PORT = mem(5) cnt = mem(7)

मैक्रोज़ के बजाय, आप सामान्य लुआ फ़ंक्शंस का उपयोग कर सकते हैं, हालांकि इस तथ्य के कारण कि वातावरण मेटा-टेबल _G असाइनमेंट्स (नीचे देखें) को पकड़ने के लिए बदल दिया गया था, वैश्विक चर उसी समय गिर गए थे: नॉन-फोकल वैरिएबल की घोषणा some_variable = 0xAA हमारा असेंबलर खुद को मानता है और पार्स करने की कोशिश करता है। इसके बजाय, एक वैश्विक प्रीप्रोसेसर चर घोषित करने के लिए, आपको रॉसेट (_G, some_variable, 0xAA) का उपयोग करना होगा, जो मेटामेथोड को स्पर्श नहीं करता है।

function jmp(l) CG = l PC = CG end

लेबल शब्द और स्ट्रिंग स्थिरांक द्वारा निरूपित किया जाएगा, Lua में, फ़ंक्शन के लिए एक एकल स्ट्रिंग तर्क के मामले में, कोष्ठक छोड़ा जा सकता है।

label "start"

पोर्ट काउंटर को पंजीकृत करें और रजिस्टर करें:

CG = 0 cnt = CG PORT = CG

लूप में, स्थिर 1 को लोड करें, इसे काउंटर चर में जोड़ें और इसे पोर्ट में दिखाएं:

label "loop" CG = 1 ADD = cnt

0 पर अतिप्रवाह में लापता को जोड़ें और, यदि शून्य नहीं है, तो शुरुआत पर जाएं, सीजी = "निकास" को छोड़ दें, अन्यथा हम एक अनंत लूप "निकास" में समाप्त होते हैं।

CG = -5 ADD = ADD

test.lua require ("asm") PC = mem(0) CG = mem(1) TST = mem(2) ADD = mem(3) SUB = mem(4) PORT = mem(5) cnt = mem(7) function jmp(l) CG = l PC = CG end label "start" CG = 0 cnt = CG PORT = CG label "loop" CG = 1 ADD = cnt

और अब कोडांतरक asm.lua ही है, क्योंकि यह 20 लाइनों में होना चाहिए:

मेम फ़ंक्शन में (विशेष पतों को घोषित करने के लिए), कोई व्यक्ति एक तर्क के रूप में निर्दिष्ट नहीं होने पर, अगले मुफ्त पते के स्वचालित असाइनमेंट को भी जोड़ देगा।

और टैग के लिए, आपको मौजूदा टैग को पुनः घोषित करने के लिए जांचना होगा

local output = {} local labels = {} function mem(addr) return addr end function label(name) labels[name] = #output end

लुआ के पास असाइनमेंट के लिए एक मेटामेथोड नहीं है, लेकिन मौजूदा मूल्यों को अनुक्रमित करने और _G वैश्विक पर्यावरण तालिका सहित नए जोड़ने के लिए मेटामेथोड हैं।

चूंकि __newindex केवल उन मानों के लिए काम करता है जो तालिका में मौजूद नहीं हैं, नए तत्वों को _G में जोड़ने के बजाय, आपको _G में जोड़े बिना उन्हें कहीं छुपाने की आवश्यकता है, और, तदनुसार, जब उन्हें __index के माध्यम से एक्सेस किया जाता है, तो उन्हें बाहर निकाल दें।

यदि नाम पहले से मौजूद है, तो इस निर्देश को बाकी हिस्सों में जोड़ें।

local g = {} setmetatable(_G, { __index = function(t, k, v) return g[k] end, __newindex = function(t, k, v) if g[k] then table.insert(output, {g[k], v}) else g[k]=v end end })

खैर, कोडांतरक प्रोग्राम को निष्पादित करने के बाद, जब कचरा कलेक्टर आखिरकार हमारे आउटपुट प्रोग्राम के साथ एक सरणी के लिए आता है, तो हम इसे प्रिंट करते हैं, उसी समय टेक्स्ट लेबल को सही पते के साथ बदल देते हैं।

setmetatable(output, { __gc = function(o) for i,v in ipairs(o) do if type(v[2]) == "string" then v[2] = labels[v[2]] or print("error: ", v[2]) end print(string.format("%02X%02X", v[1] & 0xFF, v[2] & 0xFF)) end end })

asm.lua local output = {} local labels = {} function mem(addr) return addr end function label(name) labels[name] = #output end local g = {} setmetatable(_G, { __index = function(t, k, v) return g[k] end, __newindex = function(t, k, v) if g[k] then table.insert(output, {g[k], v}) else g[k]=v end end }) setmetatable(output, { __gc = function(o) for i,v in ipairs(o) do if type(v[2]) == "string" then v[2] = labels[v[2]] or print("error: ", v[2]) end print(string.format("%02X%02X", v[1] & 0xFF, v[2] & 0xFF))

Lua53 test.lua> rom.txt ( या ऑनलाइन ) चलाकर हमें मशीन कोड्स में प्रोसेसर के लिए एक प्रोग्राम मिलता है।

rom.txt 0100 0701 0501 0101 0307 0703 0503 01FB 0303 0103 0203 010D 0001 010D 0001

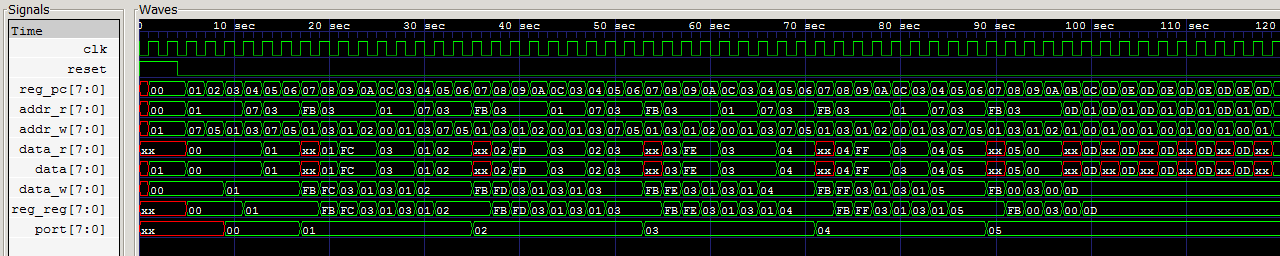

अनुकरण करने के लिए, हम एक सरल टेस्टबैंक बनाएंगे जो केवल रीसेट जारी करता है और कतरनों को खींचता है।

test.v `include "cpu.v" module test(); reg clk; reg reset; wire [7:0] port; cpu c(clk, reset, port); initial begin $dumpfile("test.vcd"); reset <= 1; clk <= 0; #4 reset <= 0; #150 $finish; end always #1 clk <= !clk; endmodule

Iverilog -o test.vvp test.v का उपयोग करके नकली होने के बाद, GTKWave में परिणामी test.vcd खोलें:

पोर्ट पांच में गिना जाता है, और फिर प्रोसेसर लूप करता है।

अब जब एक न्यूनतम काम करने वाला प्रोसेसर होता है, तो आप शेष अंकगणितीय, तार्किक संचालन, गुणन, विभाजन, फ्लोटिंग पॉइंट, त्रिकोणमिति, अप्रत्यक्ष मेमोरी एक्सेस के लिए रजिस्टर, स्टैक, हार्डवेयर चक्र, विभिन्न बाह्य उपकरणों, आवश्यकतानुसार, ... और आरा देखना शुरू कर सकते हैं। llvm के लिए बैकेंड।