FPGA (FPGA) तकनीक वर्तमान में बहुत लोकप्रियता हासिल कर रही है। अनुप्रयोगों की संख्या बढ़ रही है: डिजिटल सिग्नल को संसाधित करने के अलावा, ब्लॉकचैन प्रौद्योगिकियों, वीडियो प्रसंस्करण और IoT में मशीन सीखने में तेजी लाने के लिए FPGAs का उपयोग किया जाता है।

इस तकनीक में एक महत्वपूर्ण माइनस है: प्रोग्रामिंग के लिए, डिजिटल उपकरण वेरिलोग और वीएचडीएल की काफी जटिल और विशिष्ट विवरण भाषाओं का उपयोग किया जाता है। यह FPGA में एक नवागंतुक के प्रवेश को जटिल बनाता है और एक नियोक्ता के लिए श्रम बाजार पर इस विशिष्ट ज्ञान के साथ एक विशेषज्ञ को खोजना मुश्किल है। दूसरी ओर,

MyHDL ढांचे के साथ लोकप्रिय उच्च-स्तरीय पायथन प्रोग्रामिंग भाषा FPGA प्रोग्रामिंग को सरल और सुखद बनाती है। इसके अलावा, जो लोग पायथन को जानते हैं वे वेरिलॉग / वीएचडीएल के साथ अधिक विशेषज्ञों के परिमाण का एक आदेश हैं। लेखों की एक श्रृंखला के साथ मैं यह दिखाना चाहता हूं कि पायथन को जानते हुए FPGA के क्षेत्र में प्रवेश करना कितना आसान है और इस भाषा में वास्तविक जटिल FPGA प्रोजेक्ट बनाना शुरू करें। मैं ध्यान देता हूं कि अजगर सीधे FPGA पर निष्पादित नहीं होता है, लेकिन फर्मवेयर बनाने के लिए एक उपकरण है।

सबसे पहले, हमें अजगर संस्करण 3.6 खुद की आवश्यकता है (इसके बाद, सभी ऑपरेशन उबंटू 18.04 ओएस पर किए जाते हैं)।

Myhdl स्थापित करें:

pip3 install myhdl

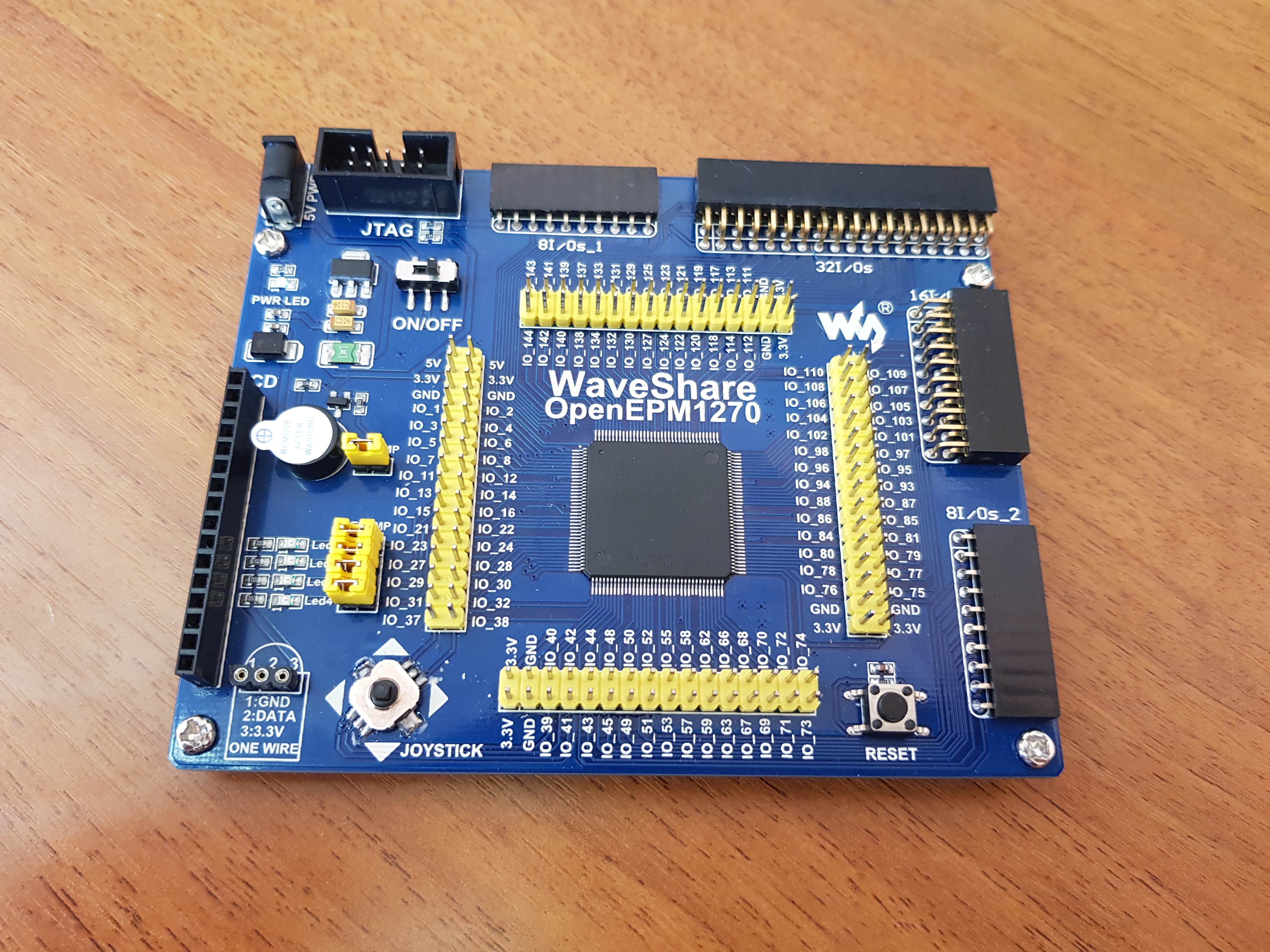

"हैलो वर्ल्ड!" हम एक साधारण प्रोग्राम लिखेंगे जो एक बटन दबाने पर एल ई डी को हल्का बनाता है। माइक्रोप्रोसेसरों की दुनिया में "हैलो वर्ल्ड!" यह एक ऐसा कार्यक्रम है जो एक एलईडी के साथ चमकता है; एफपीजीए दुनिया में, हैलो वर्ल्ड एक हजार एलईडी का चमकता है। बोर्ड पर केवल चार एलईडी हैं, इसलिए हम केवल बटन फ्लैश के आधार पर, उन्हें फ्लैश करेंगे। यह ध्यान रखना महत्वपूर्ण है कि माइक्रोकंट्रोलर के विपरीत, FPGA में सभी कोड एक ही समय में निष्पादित किए जाते हैं, सभी डायोड प्रकाश में आते हैं और एक ही समय में बाहर जाते हैं। और माइक्रोकंट्रोलर के मामले में क्रमिक रूप से नहीं। परीक्षण बोर्ड पर Altera Max II EPM1270T144C5 बोर्ड के साथ WaveShare OpenEPM1270 बोर्ड का उपयोग करता है।

एक नई अजगर फ़ाइल बनाएँ:

from myhdl import * from random import randrange def led_blinker(input1, led1, led2, led3, led4): @always_comb def on_off_led(): if input1 == 1: led1.next = 1 led2.next = 1 led3.next = 0 led4.next = 0 else: led1.next = 0 led2.next = 0 led3.next = 1 led4.next = 1 return on_off_led

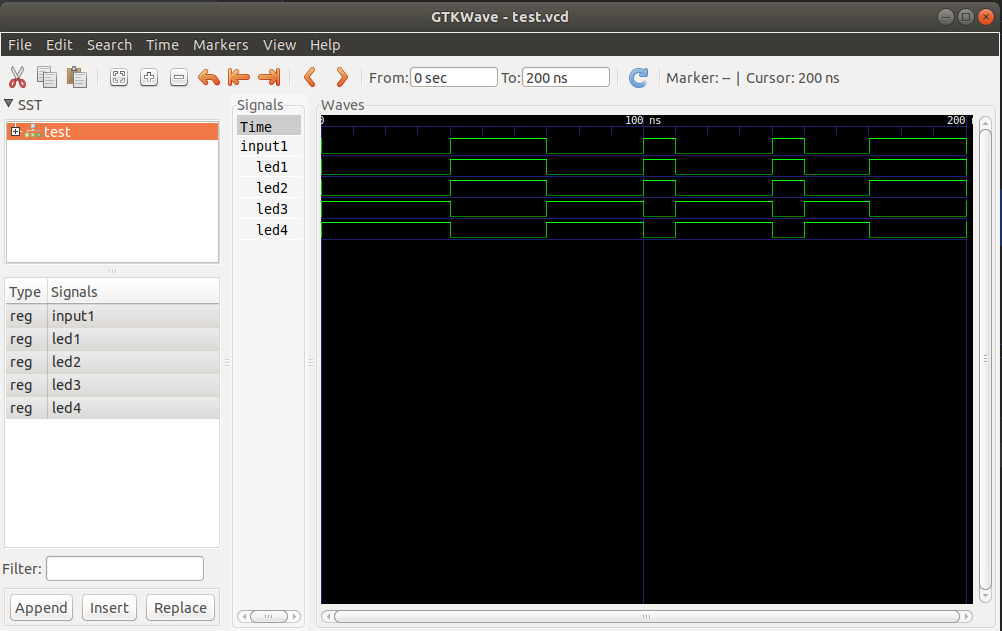

यह जानने के लिए कि क्या हमारा कोड सही तरीके से काम करता है, आपको एक सत्यापन उपकरण की आवश्यकता है। वास्तव में, FPGA के लिए कोई भी कार्यक्रम एक डिजिटल सिग्नल प्रोसेसर है, इसलिए डेवलपर को यह सुनिश्चित करने की आवश्यकता है कि उसने सही ढंग से संकेत दिया कि चिप के साथ क्या करना है। यह सिमुलेशन के माध्यम से किया जाता है, इसके लिए आपको एक प्रोग्राम स्थापित करने की आवश्यकता होती है जो संसाधित संकेतों को प्रदर्शित करेगा। इस तरह के बहुत सारे कार्यक्रम हैं, लेकिन मेरी राय में इस समय सबसे अच्छा मुफ्त GTKWave है। इसे टर्मिनल से डाला जाता है:

sudo apt-get install gtkwave

अगला, फर्मवेयर के साथ फाइल में, परीक्षण वातावरण का वर्णन किया जाना चाहिए। यह भी एक अजगर समारोह है:

def test(): input1, led1, led2, led3, led4 = [Signal(bool(0)) for i in range(5)] test = led_blinker(input1, led1, led2, led3, led4) @always(delay(10)) def gen(): input1.next = randrange(2) return test, gen

यहां परीक्षण वातावरण शून्य और लोगों का एक यादृच्छिक अनुक्रम उत्पन्न करता है (पायथन मॉड्यूल यादृच्छिक का उपयोग किया जाता है)।

def simulate(timesteps): tb = traceSignals(test) sim = Simulation(tb) sim.run(timesteps)

और हम सिम्युलेटर को इनिशियलाइज़ करते हैं, वहां test_inverter पर्यावरण फ़ंक्शन को खींचते हैं। इस प्रकार, हम रूसी गुड़िया इन्वर्टर → test_inverter → अनुकरण (मनमानी इकाइयों में समय) प्राप्त करते हैं।

कामकाजी फ़ोल्डर में स्क्रिप्ट चलाने के बाद, .vcd फ़ाइल बनाएं और इसे gtkwave के माध्यम से टर्मिनल में चलाएँ: gtkwave test_invereter.vcd।

नतीजतन, इनपुट सिग्नल इनपुट 1 का एक यादृच्छिक अनुक्रम उत्पन्न हुआ था, और led_blinker फ़ंक्शन ने इन संकेतों को कैसे संसाधित किया।

जब हमने यह सुनिश्चित कर लिया कि तर्क ठीक उसी तरह काम करता है जैसा हम चाहते थे, तो हमें इस समारोह को FPGA में फेंक देना चाहिए। मैं इंटेल (पूर्व में एल्टर) से चिप्स के साथ काम करने के लिए उपयोग किया जाता था, संचालन का यह क्रम सीएडी सिस्टम वाले अन्य निर्माताओं के चिप्स के लिए समान है। FPGA चिप पर एक बाइनरी फ़ाइल बनाई जाती है, जो चिप निर्माता के कंपाइलर द्वारा बनाई जाती है, Intel के लिए यह Xartx Vivado के लिए Quartus है। कंपाइलर केवल VHDL / Verilog में कोड के साथ काम कर सकते हैं, इसलिए पायथन कोड को इनमें से किसी भी भाषा में अनुवादित किया जाना चाहिए (यह कोई बात नहीं है)।

def convert(): input1, led1, led2, led3, led4 = [Signal(bool(0)) for i in range(5)] toVerilog(led_blinker, input1, led1, led2, led3, led4) convert()

इस उदाहरण में, कोड का अनुवाद वेरिलोग में किया गया है। परिणाम led_blinker.v फ़ाइल में है, और Quartus को FPGA फर्मवेयर बनाने के लिए इसे देने की आवश्यकता होगी:

module led_blinker ( input1, led1, led2, led3, led4 ); input input1; output led1; reg led1; output led2; reg led2; output led3; reg led3; output led4; reg led4; always @(input1) begin: LED_BLINKER_ON_OFF_LED if ((input1 == 1)) begin led1 = 1; led2 = 1; led3 = 0; led4 = 0; end else begin led1 = 0; led2 = 0; led3 = 1; led4 = 1; end end endmodule

FPGA फर्मवेयर के विकास के लिए इस दृष्टिकोण में, आप इस फ़ाइल को अनदेखा कर सकते हैं और बस इसे क्वार्टस में छोड़ सकते हैं।

आप

fpgasoftware.intel.com से

क्वार्टस डाउनलोड कर सकते हैं, हमें लाइट के एक नि: शुल्क संस्करण की आवश्यकता है, यह हमारे लिए पर्याप्त होगा। 9 जीबी का मूल संस्करण आकार डाउनलोड करें।

क्वार्ट्स को स्थापित करना औसत लिनक्स उपयोगकर्ता के लिए एक समस्या नहीं होनी चाहिए। स्थापना के बाद, आपको सिस्टम में कुछ पैरामीटर सेट करने की आवश्यकता है ताकि आप FPGA प्रोग्राम को चमकाने के लिए डिवाइस का उपयोग कर सकें - प्रोग्रामर:

1. एक udv नियम बनाएँ। ऐसा करने के लिए, निम्न सामग्री के साथ एक नई फ़ाइल /etc/udev/rules.d/51-altera-usb-blaster.rules बनाएं:

Udvadm का उपयोग करके रिबूट udev:

sudo udevadm control --reload

2. यूएसबी-ब्लास्टर डिवाइस पर गैर-रूट एक्सेस की अनुमति दें। ऐसा करने के लिए, लाइन के साथ फ़ाइल /etc/udev/rules.d/altera-usb-blaster.rules बनाएं:

ATTR{idVendor}=="09fb", ATTR{idProduct}=="6001", MODE="666"

यह प्रोग्रामर को rw-rw-rw- एक्सेस देता है।

3. Jtagd कॉन्फ़िगर करें। क्वार्टस काम करने के लिए jtagd डेमॉन का उपयोग करता है, जो प्रोग्रामर डिवाइस के साथ सॉफ्टवेयर को जोड़ता है। क्वार्टस के साथ अपनी निर्देशिका से विवरण की प्रतिलिपि बनाएँ:

sudo mkdir /etc/jtagd sudo cp <Quartus install path>/quartus/linux64/pgm_parts.txt /etc/jtagd/jtagd.pgm_parts

क्वार्टस चलाएं और एक नया प्रोजेक्ट बनाएं "फाइल" - "नया प्रोजेक्ट विज़ार्ड", प्रोजेक्ट का नाम टाइप करें।

इसके बाद Next पर क्लिक करें। और Add Files मेनू में, हम जेनरेट की गई वाइलॉग फाइल को एक्सटेंशन के साथ जोड़ते हैं। इस प्रकार, यदि वेरिलॉग फ़ाइल को पायथन फ़ाइल से संपादित किया जाता है, तो यह स्वचालित रूप से क्वार्टस द्वारा उठाया जाएगा। इसके बाद, हम डिवाइस चयन मेनू में जाते हैं, हमारे मामले में यह MAX II EMP1270T144C5 और अगले कुछ समय है। प्रोजेक्ट बना है।

प्रोजेक्ट नेविगेटर में, फ़ाइल मेनू पर जाएं और हमारी वेरिलॉग फ़ाइल "शीर्ष-स्तरीय इकाई के रूप में सेट करें" पर राइट-क्लिक करें।

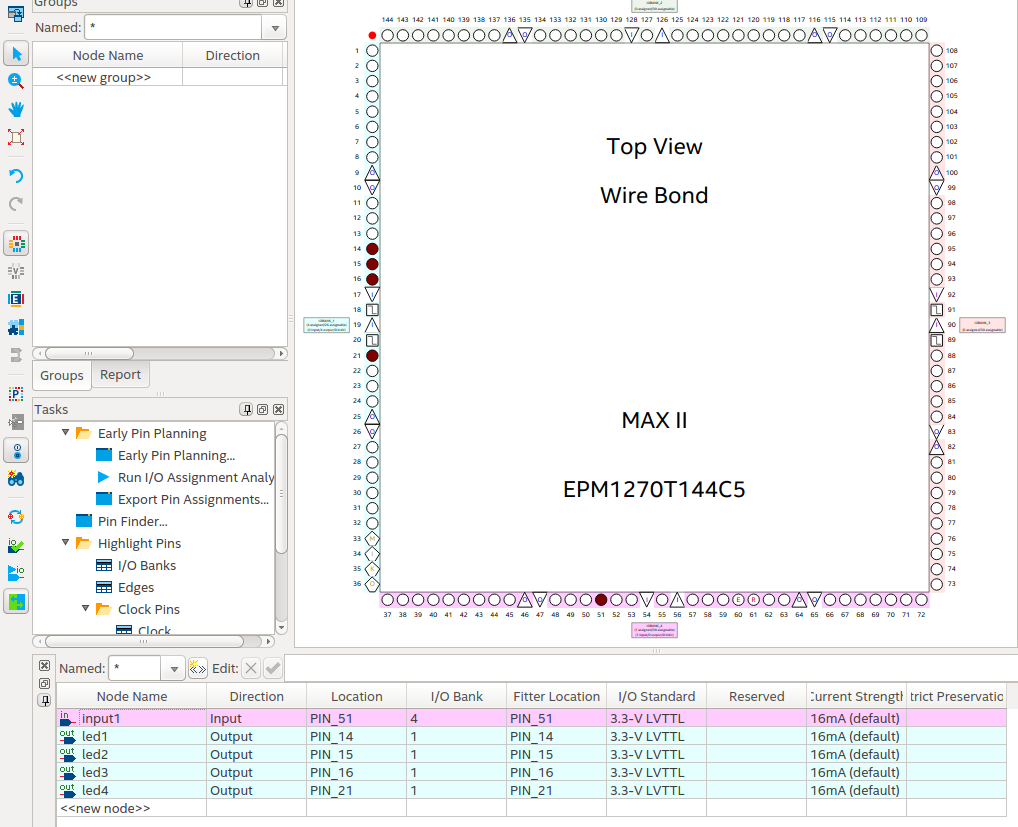

हम परियोजना को संकलित करते हैं। अब, "असाइनमेंट-पिन प्लानर" मेनू में, चिप पर पिन कॉन्फ़िगर करें:

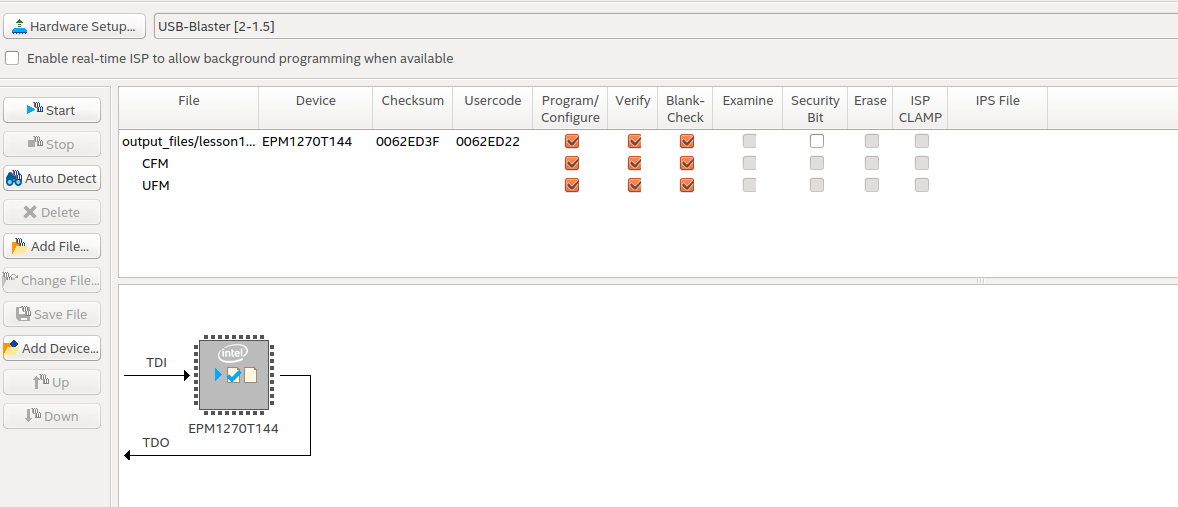

फिर से संकलित करें। अब सब कुछ प्रोग्रामिंग के लिए तैयार है: टूल-प्रोग्रामर। हम प्रोग्रामर और पावर को बोर्ड से जोड़ते हैं, हार्डवेयर सेटअप में हम अपने यूएसबी-ब्लास्टर का चयन करते हैं, चेकबॉक्स सेट करें जैसा कि चित्र में दिखाया गया है और प्रारंभ करें।

प्रोग्रामर के सफल होने की सूचना देने के बाद। आप बोर्ड पर परिणाम देख सकते हैं:

निष्कर्ष

इस पाठ में बताया गया है कि पायथन प्रोग्रामिंग भाषा में काम का माहौल और पहला सरल एफपीजीए प्रोजेक्ट कैसे बनाया जाए।

माना:

- कैसे स्थापित करें:

- उबंटू में यूएसबी ब्लास्टर प्रोग्रामर कॉन्फ़िगर किया गया;

- FPGA FPGA परियोजना विकसित;

- परीक्षण और परियोजना का सत्यापन;

- FPGA के लिए एक परियोजना संकलित;

- प्रोजेक्ट FPGA पर अपलोड किया गया।