पहले लेख की निरंतरता में, मैं उदाहरण के रूप में अजगर में FPGA (FPGA) के साथ काम करने का एक उदाहरण दिखाना चाहता हूं। यह आलेख परीक्षण पहलू को अधिक विस्तार से कवर करेगा। यदि

FHDA की दुनिया में देखने के लिए

MyHDL फ्रेमवर्क लोगों को परिचित सिंटैक्स और इकोसिस्टम का उपयोग करके अजगर पर काम करने की अनुमति देता है, तो अनुभवी FPGA डेवलपर्स अजगर का उपयोग करने का अर्थ नहीं समझते हैं। MyHDL और वेरिलॉग के लिए हार्डवेयर विवरण प्रतिमान समान हैं, और एक विशिष्ट भाषा चुनना आदत और स्वाद का विषय है। वेरिलोग / वीएचडीएल इस तथ्य के लिए खड़ा है कि फर्मवेयर इन भाषाओं में लंबे समय से लिखा गया है, और वास्तव में वे डिजिटल उपकरणों के विवरण के लिए मानक हैं। इस क्षेत्र में नौसिखिए के रूप में पायथन, परीक्षण वातावरण लिखने में प्रतिस्पर्धा कर सकता है। FPGA डेवलपर के समय का एक महत्वपूर्ण हिस्सा उनके डिजाइनों का परीक्षण करने में बिताया जाता है। अगला, मैं उदाहरण के द्वारा प्रदर्शित करना चाहता हूं कि यह MyHDL के साथ अजगर में कैसे किया जाता है।

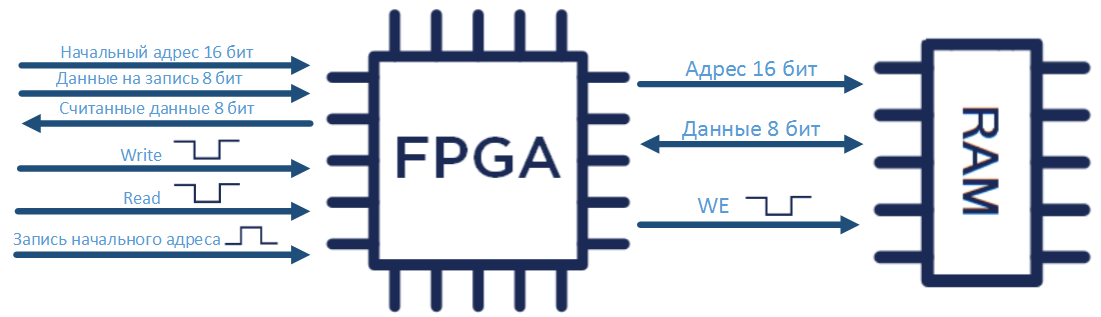

मान लीजिए कि FPGA पर मेमोरी के साथ काम करने वाले एक उपकरण का वर्णन करने के लिए एक कार्य है। सादगी के लिए, मैं एक समांतर इंटरफ़ेस के माध्यम से अन्य उपकरणों के साथ संचार करने वाली मेमोरी (और एक सीरियल एक के माध्यम से नहीं, उदाहरण के लिए 22C के लिए ले जाऊंगा)। इस तरह के microcircuits हमेशा इस तथ्य को ध्यान में रखते हुए व्यावहारिक नहीं होते हैं कि उनके साथ काम करने के लिए कई पिनों की आवश्यकता होती है, दूसरी तरफ, जानकारी का तेज़ और आसान विनिमय प्रदान किया जाता है। उदाहरण के लिए, घरेलू 1645RU1U और इसके एनालॉग।

मॉड्यूल विवरण

रिकॉर्ड इस तरह दिखता है: FPGA 16-बिट सेल एड्रेस, 8-बिट डेटा देता है, एक राइट सिग्नल WE (राइट सक्षम) लिखता है। चूंकि OE (आउटपुट इनेबल) और CE (चिप इनेबल्ड) हमेशा सक्षम होते हैं, रीडिंग तब होती है जब सेल एड्रेस बदल जाता है। लेखन और पढ़ना दोनों को क्रमिक रूप से एक पंक्ति में कई कोशिकाओं में किया जा सकता है, जो एक विशेष adr_start पते से शुरू होता है, जो adr_write सिग्नल के अग्रणी किनारे पर दर्ज होता है, और एक सेल एक मनमाने पते (यादृच्छिक अभिगम) पर होता है।

MyHDL पर, कोड इस तरह दिखता है (रिवर्स लॉजिक में सिग्नल लिखते और पढ़ते हैं):

from myhdl import * @block def ram_driver(data_in, data_out, adr, adr_start, adr_write, data_memory, read, write, we):

यदि फ़ंक्शन का उपयोग करके वेरिलॉग में परिवर्तित किया गया है:

def convert(hdl): data_memory = TristateSignal(intbv(0)[8:]) data_in = Signal(intbv(0)[8:]) data_out = Signal(intbv(0)[8:]) adr = Signal(intbv(0)[16:]) adr_start = Signal(intbv(0)[16:]) adr_write = Signal(bool(0)) read, write, we = [Signal(bool(1)) for i in range(3)] inst = ram_driver(data_in, data_out, adr, adr_start, adr_write, data_memory, read, write, we) inst.convert(hdl=hdl) convert(hdl='Verilog')

फिर हमें निम्नलिखित मिलते हैं:

`timescale 1ns/10ps module ram_driver ( data_in, data_out, adr, adr_start, adr_write, data_memory, read, write, we ); input [7:0] data_in; output [7:0] data_out; reg [7:0] data_out; output [15:0] adr; reg [15:0] adr; input [15:0] adr_start; input adr_write; inout [7:0] data_memory; wire [7:0] data_memory; input read; input write; output we; reg we; reg [7:0] mem_z; assign data_memory = mem_z; always @(write) begin: RAM_DRIVER_WRITE_DATA if ((!write)) begin mem_z <= data_in; we <= 0; end else begin mem_z <= 'bz; data_out <= data_memory; we <= 1; end end always @(posedge adr_write, posedge write, negedge read) begin: RAM_DRIVER_WRITE_START_ADR if (adr_write) begin adr <= adr_start; end else begin adr <= (adr + 1); end end endmodule

सिमुलेशन के लिए एक परियोजना को वेरिलॉग में बदलना आवश्यक नहीं है, इस कदम को एफपीजीए को चमकाने के लिए आवश्यक होगा।

मोडलिंग

तर्क के विवरण के बाद, परियोजना को सत्यापित किया जाना चाहिए। आप अपने आप को प्रतिबंधित कर सकते हैं, उदाहरण के लिए, इनपुट प्रभावों का अनुकरण करने और समय आरेख में मॉड्यूल की प्रतिक्रिया देखने के लिए। लेकिन इस विकल्प के साथ, मेमोरी चिप के साथ अपने मॉड्यूल की बातचीत की भविष्यवाणी करना अधिक कठिन है। इसलिए, बनाए गए डिवाइस के संचालन को पूरी तरह से सत्यापित करने के लिए, आपको एक मेमोरी मॉडल बनाने और इन दो उपकरणों के बीच बातचीत का परीक्षण करने की आवश्यकता है।

चूंकि काम अजगर में होता है, इसलिए दिया गया शब्दकोश (शब्दकोश) मेमोरी मॉडल के लिए खुद को बताता है। वह डेटा जिसमें {कुंजी: मान}, और इस स्थिति के लिए {पता: डेटा} के रूप में संग्रहीत किया जाता है।

memory = { 0: 123, 1: 456, 2: 789 } memory[0] >> 123 memory[1] >> 456

इसी उद्देश्य के लिए, सूची डेटा प्रकार उपयुक्त है, जहां प्रत्येक तत्व के अपने निर्देशांक हैं जो सूची में तत्व के स्थान को दर्शाते हैं:

memory = [123, 456, 789] memory[0] >> 123 memory[1] >> 456

अधिक दृश्यता के मद्देनजर स्मृति का अनुकरण करने के लिए शब्दकोशों का उपयोग करना बेहतर लगता है।

परीक्षण शेल का वर्णन (फ़ाइल test_seq_access.py में) संकेतों की घोषणा, प्रारंभिक अवस्थाओं के आरंभ और उनके ऊपर वर्णित मेमोरी ड्राइवर फ़ंक्शन में फेंकने के साथ शुरू होता है:

@block def testbench(): data_memory = TristateSignal(intbv(0)[8:]) data_in = Signal(intbv(0)[8:]) data_out = Signal(intbv(0)[8:]) adr = Signal(intbv(0)[16:]) adr_start = Signal(intbv(20)[16:]) adr_write = Signal(bool(0)) read, write, we = [Signal(bool(1)) for i in range(3)] ram = ram_driver(data_in, data_out, adr, adr_start, adr_write, data_memory, read, write, we)

निम्नलिखित मेमोरी मॉडल का वर्णन करता है। प्रारंभिक अवस्थाएँ आरम्भिक हैं, डिफ़ॉल्ट रूप से मेमोरी शून्य मानों से भरी होती है। मेमोरी मॉडल को 128 कोशिकाओं तक सीमित करें:

memory = {i: intbv(0) for i in range(128)}

और स्मृति के व्यवहार का वर्णन करें: जब हम निम्न स्थिति में होते हैं, तो संबंधित मेमोरी पते की पंक्ति में मान लिखें, अन्यथा मॉडल दिए गए पते पर मूल्य देता है:

mem_z = data_memory.driver() @always_comb def access(): if not we: memory[int(adr.val)] = data_memory.val if we: data_out.next = memory[int(adr.val)] mem_z.next = None

फिर, एक ही फ़ंक्शन में, आप इनपुट संकेतों के व्यवहार का वर्णन कर सकते हैं (अनुक्रमिक लिखने / पढ़ने के मामले के लिए): प्रारंभिक पता दर्ज किया जाता है → 8 सूचना कोशिकाओं को दर्ज किया जाता है → प्रारंभिक पता दर्ज किया जाता है → 8 दर्ज की गई सूचना कोशिकाओं को पढ़ा जाता है।

@instance def stimul(): init_adr = random.randint(0, 50) # yield delay(100) write.next = 1 adr_write.next = 1 adr_start.next = init_adr # yield delay(100) adr_write.next = 0 yield delay(100) for i in range(8): # 8 write.next = 0 data_in.next = random.randint(0, 100) yield delay(100) write.next = 1 yield delay(100) adr_start.next = init_adr # adr_write.next = 1 yield delay(100) adr_write.next = 0 yield delay(100) for i in range(8): # read.next = 0 yield delay(100) read.next = 1 yield delay(100) raise StopSimulation return stimul, ram, access

सिमुलेशन चलाएँ:

tb = testbench() tb.config_sim(trace=True) tb.run_sim()

कार्यक्रम शुरू करने के बाद, testbench_seq_access.vcd फ़ाइल कार्य फ़ोल्डर में उत्पन्न होती है, इसे gtkave में खोलें:

gtkwave testbench_seq_access.vcd

और हम तस्वीर देखते हैं:

रिकॉर्ड की गई जानकारी सफलतापूर्वक पढ़ी गई।

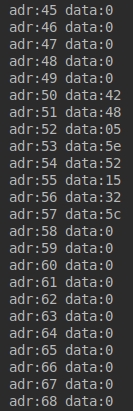

आप निम्न कोड को testbench में जोड़कर मेमोरी की सामग्री देख सकते हैं:

for key, value in memory.items(): print('adr:{}'.format(key), 'data:{}'.format(value))

कंसोल में निम्न प्रकट होता है:

परीक्षण

उसके बाद, आप कई स्वचालित परीक्षण कर सकते हैं जिनमें बढ़ी हुई संख्या में लिखने योग्य / पठनीय कोशिकाएँ होती हैं। ऐसा करने के लिए, कई परीक्षण चक्र और डमी शब्दकोशों को टेस्टबेंच में जोड़ा जाता है, जहां लिखित और पठनीय जानकारी और मुखर निर्माण को जोड़ा जाता है, जो दो शब्दकोशों के बराबर नहीं होने पर त्रुटि का कारण बनता है:

@instance def stimul(): for time in range(100): temp_mem_write = {} temp_mem_read = {} init_adr = random.randint(0, 50) yield delay(100) write.next = 1 adr_write.next = 1 adr_start.next = init_adr yield delay(100) adr_write.next = 0 yield delay(100) for i in range(64): write.next = 0 data_in.next = random.randint(0, 100) temp_mem_write[i] = int(data_in.next) yield delay(100) write.next = 1 yield delay(100) adr_start.next = init_adr adr_write.next = 1 yield delay(100) adr_write.next = 0 yield delay(100) for i in range(64): read.next = 0 temp_mem_read[i] = int(data_out.val) yield delay(100) read.next = 1 yield delay(100) assert temp_mem_write == temp_mem_read, " " for key, value in memory.items(): print('adr:{}'.format(key), 'data:{}'.format(value)) raise StopSimulation return stimul, ram, access

इसके बाद, आप रैंडम एक्सेस मोड में टेस्ट ऑपरेशन के लिए दूसरा टेस्टबेंच बना सकते हैं: test_random_access.py।

दूसरे परीक्षण का विचार समान है: हम एक यादृच्छिक पते पर यादृच्छिक जानकारी लिखते हैं और एक जोड़े {पता: डेटा} को temp_mem_write शब्दकोश में जोड़ते हैं। फिर हम इस शब्दकोश में पतों के चारों ओर जाते हैं और मेमोरी से जानकारी पढ़ते हैं, इसे temp_mem_read शब्दकोश में दर्ज करते हैं। और मुखर निर्माण के साथ अंत में, हम दो शब्दकोशों की सामग्री की जांच करते हैं।

import random from myhdl import * from ram_driver import ram_driver @block def testbench_random_access(): data_memory = TristateSignal(intbv(0)[8:]) data_in = Signal(intbv(0)[8:]) data_out = Signal(intbv(0)[8:]) adr = Signal(intbv(0)[16:]) adr_start = Signal(intbv(20)[16:]) adr_write = Signal(bool(0)) read, write, we = [Signal(bool(1)) for i in range(3)] ram = ram_driver(data_in, data_out, adr, adr_start, adr_write, data_memory, read, write, we) memory ={i:intbv(0) for i in range(128)} mem_z = data_memory.driver() @always_comb def access(): if not we: memory[int(adr.val)] = data_memory.val if we: data_out.next = memory[int(adr.val)] mem_z.next = None @instance def stimul(): for time in range(10): temp_mem_write = {} temp_mem_read = {} yield delay(100) for i in range(64): write.next = 1 adr_write.next = 1 adr_start.next = random.randint(0, 126) yield delay(100) adr_write.next = 0 yield delay(100) write.next = 0 data_in.next = random.randint(0, 100) temp_mem_write[int(adr_start.val)] = int(data_in.next) yield delay(100) write.next = 1 yield delay(100) for key in temp_mem_write.keys(): adr_start.next = key adr_write.next = 1 yield delay(100) adr_write.next = 0 yield delay(100) read.next = 0 temp_mem_read[key] = int(data_out.val) yield delay(100) read.next = 1 yield delay(100) assert temp_mem_write == temp_mem_read, ' random access' raise StopSimulation return stimul, ram, access tb = testbench_random_access() tb.config_sim(trace=True) tb.run_sim()

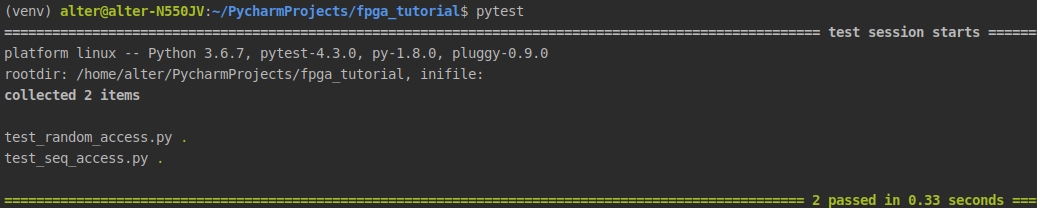

पायथन में परीक्षण निष्पादन को स्वचालित करने के लिए कई रूपरेखाएं हैं। मैं सादगी के लिए पूरी कोशिश करूंगा, इसे पाइप से स्थापित किया जाना चाहिए:

pip3 install pytest

जब कंसोल से "pysest" कमांड लॉन्च किया जाता है, तो फ्रेमवर्क उनके नाम में "test_ *" के साथ काम करने वाले फ़ोल्डर में सभी फ़ाइलों को ढूंढ और निष्पादित करेगा।

टेस्ट सफलतापूर्वक संपन्न हुए। मैं उपकरण के विवरण में गलती करूंगा:

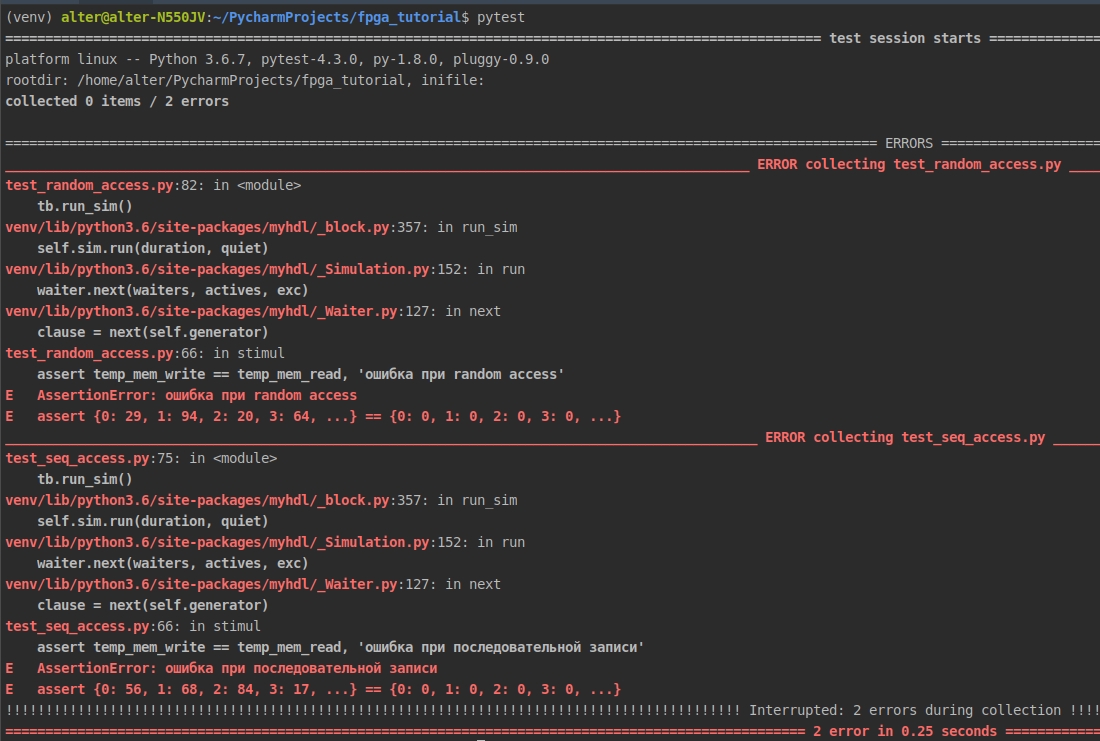

@block def ram_driver(data_in, data_out, adr, adr_start, adr_write, data_memory, read, write, we): mem_z = data_memory.driver() @always(adr_write.posedge, write.posedge, read.negedge) def write_start_adr(): if adr_write: adr.next = adr_start else: adr.next = adr + 1 @always(write) def write_data(): if not write: mem_z.next = data_in we.next = 1 # , else: mem_z.next = None data_out.next = data_memory we.next = 1

मैं परीक्षण चलाता हूं:

जैसा कि अपेक्षित था, दोनों परीक्षणों में, प्रारंभिक जानकारी (शून्य) पर विचार किया गया था, अर्थात नई जानकारी दर्ज नहीं की गई थी।

निष्कर्ष

MyHDL के साथ मिलकर अजगर का उपयोग करने से आप FPGAs के लिए विकसित फर्मवेयर के परीक्षण को स्वचालित कर सकते हैं और अजगर प्रोग्रामिंग भाषा की समृद्ध क्षमताओं का उपयोग करके लगभग किसी भी परीक्षण वातावरण का निर्माण कर सकते हैं।

लेख मानता है:

- एक मॉड्यूल बनाना जो मेमोरी के साथ काम करता है;

- मेमोरी मॉडल बनाना;

- परीक्षण मामले का निर्माण;

- pytest ढांचे के साथ परीक्षण स्वचालन।