एक छोटा सा परिचय:

टॉम्सक शहर में डिजिटल सर्किटरी पर एक स्कूल-सेमिनार पास करने के बाद अपना खुद का कोर लिखने का विचार आया। इस घटना में, वर्तमान हार्डवेयर विवरण भाषाओं ( वेरिलॉग एचडीएल और वीएचडीएल) के साथ-साथ एक छोटे प्रोसेसर कोर स्कूलएमआईपीएस के साथ परिचित हैं । कोर की संरचना को समझने के लिए, स्कूलीआईपीएस के विकास के मार्ग का अनुसरण करते हुए, अपनी खुद की साइकिल का आविष्कार करने का निर्णय लिया गया, लेकिन आधार के रूप में एक और कमांड सिस्टम लिया गया। RISC-V की बढ़ती लोकप्रियता और इसके कमांड सिस्टम के खुलेपन के कारण (MIPS में उस समय कर्नेल लिखे जाने के समय एक ओपन कमांड सिस्टम नहीं था), RISC-V निर्देशों का एक सेट, अर्थात् RV32I, भविष्य के कर्नेल के विकास के लिए चुना गया था। RV32I में बुनियादी निर्देशों (विशेष को छोड़कर 37) का एक छोटा सा सेट है और यदि वांछित है, तो इसका विस्तार किया जा सकता है, उदाहरण के लिए, पूर्णांक गुणन और विभाजन निर्देश (RV32M) या छोटे निर्देशों (RV32C) के लिए समर्थन जोड़कर। साथ ही, इस परियोजना की शिक्षा के रूप में कल्पना की गई थी, इसलिए कर्नेल की दृश्यता को अधिकतम रूप से प्रभावी ढंग से अपने काम को प्रदर्शित करने का निर्णय लिया गया था।

SchoolMIPS के अनुरूप, निम्नलिखित कर्नेल संस्करण लागू किए गए थे:

- एकल-चक्र संस्करण (00_simple_risc_v_cpu)।

- Lw / sw निर्देश (लोड शब्द / स्टोर शब्द) (01_simple_risc_v_cpu_lwsw) के समर्थन के साथ एक एकल-चक्र संस्करण।

- पाइपलाइन संस्करण (5-चरण कन्वेयर) (02_pipe_risc_v_cpu)।

वर्तमान में, अगले कर्नेल संस्करण का वर्णन किया गया है (03_pipe_risc_v_cpu_fc) RV32I कमांड्स का पूरा सेट (कुछ विशेष को ध्यान में रखे बिना)।

कर्नेल विवरण के दौरान, कार्य, डिबगिंग और सत्यापन की दृश्यता में सुधार के तरीकों पर विचार किया गया। वर्तमान में निम्नलिखित विधियों को लागू किया गया है:

एक डीबग पाठ VGA मॉड्यूल जोड़ना (दो एकल-चक्र कर्नेल शाखाओं के लिए)। इस मॉड्यूल का समावेश आपको मॉनिटर स्क्रीन पर 32 रजिस्टरों के मूल्य को एक साथ ट्रैक करने की अनुमति देता है, जो कि सात-खंड संकेतकों पर सूचना के आउटपुट का उपयोग करते समय संभव नहीं है। नीचे प्रस्तुत आंकड़ों में, कर्नेल लियोनार्डो संख्याओं की गणना करता है और संबंधित डीबगिंग मॉड्यूल पर जानकारी प्रदर्शित करता है;

hex_display और DebugScreenCoreसात-खंड संकेतकों पर सूचना उत्पादन:

वीजीए डिस्प्ले पर सूचना उत्पादन:

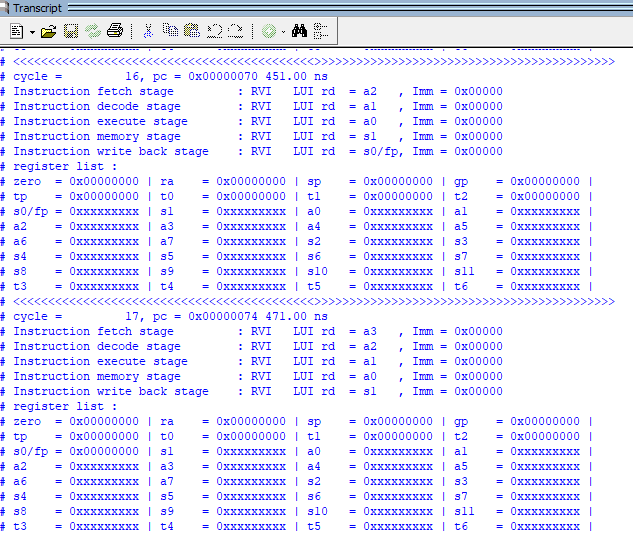

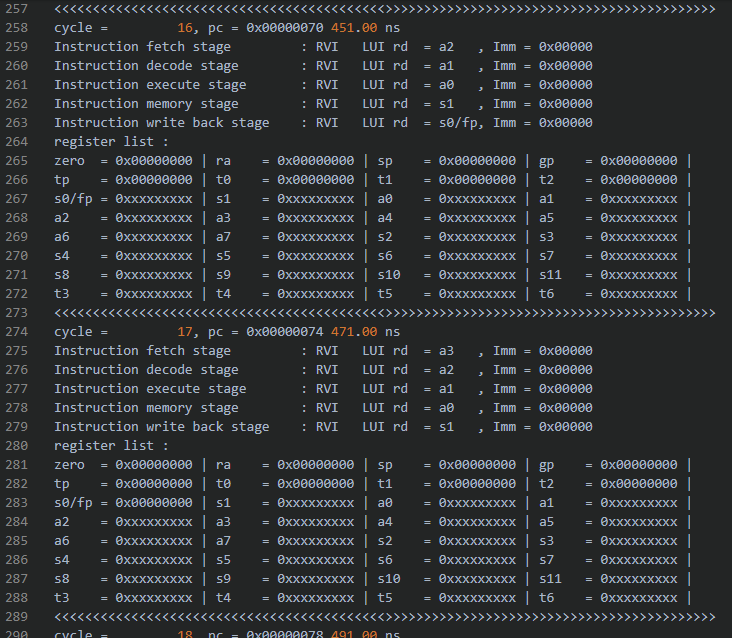

रजिस्टर फ़ाइल की स्थिति के बारे में सिम्युलेटर टर्मिनल में संदेश जोड़ना और वर्तमान में निर्देशों को निष्पादित करना। यह विधि आपको विकास के प्रारंभिक चरण में कर्नेल के संचालन का बेहतर विश्लेषण करने की अनुमति देती है, लेकिन हमेशा सुविधाजनक नहीं होती है;

अंतिमरजिस्टर फाइल का आरम्भिकरण:

सपा मूल्य बदलें:

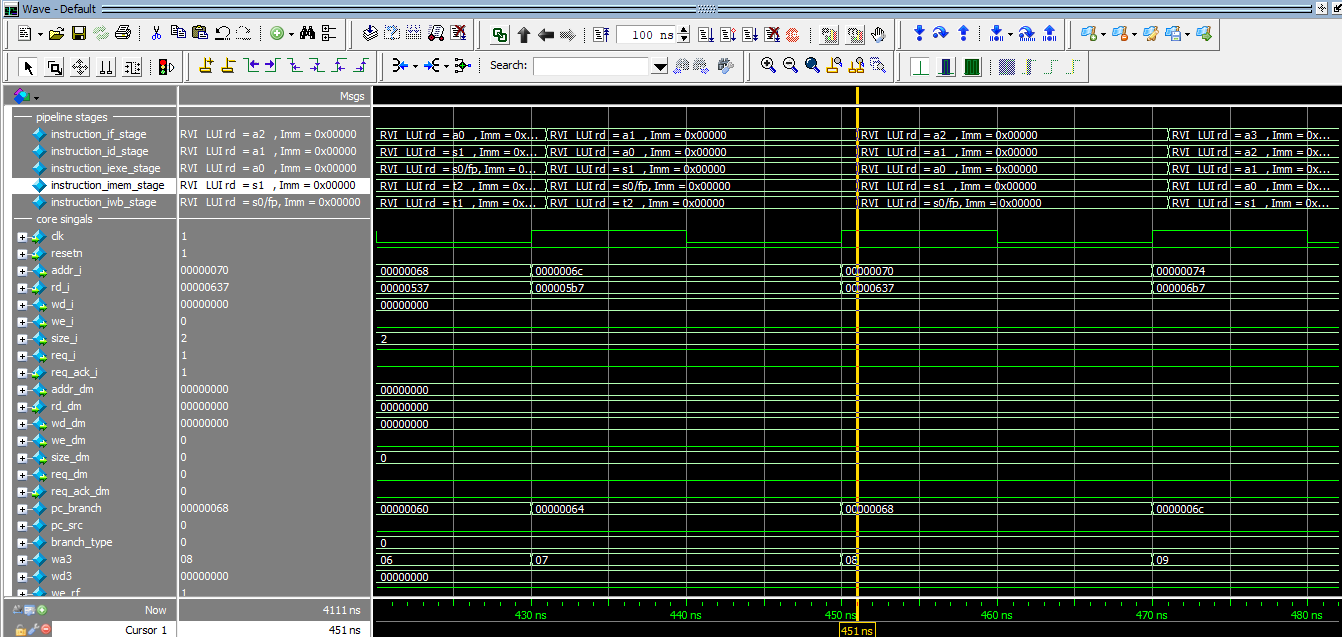

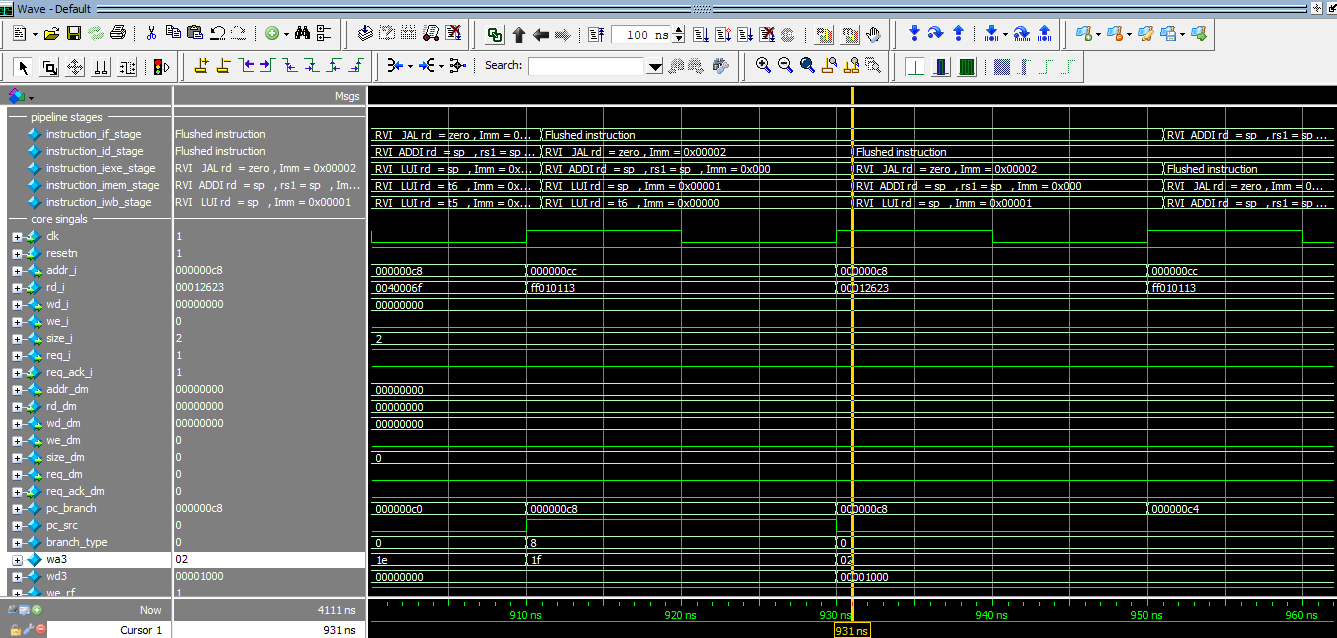

निष्पादन योग्य निर्देशों के प्रदर्शन के साथ वेवफॉर्म में स्ट्रिंग चर जोड़ना। इन स्ट्रिंग चर का उपयोग करके, डेवलपर पाइपलाइन के सभी चरणों में नियंत्रण संकेतों की सही सेटिंग को ट्रैक कर सकता है;

तरंगरजिस्टर फाइल का आरम्भिकरण:

सपा मूल्य बदलें:

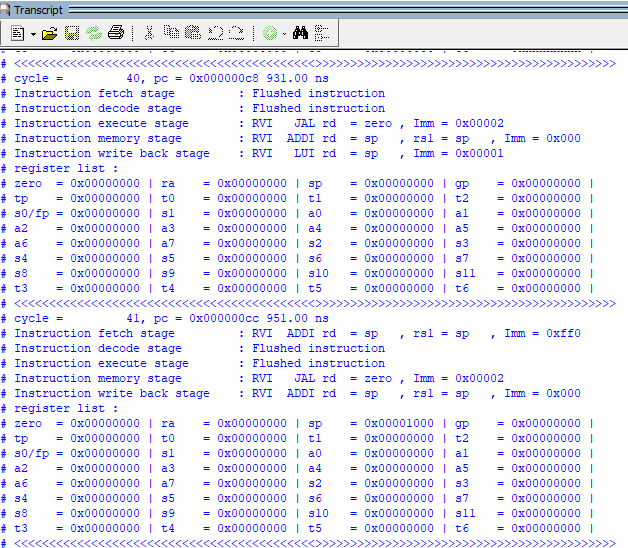

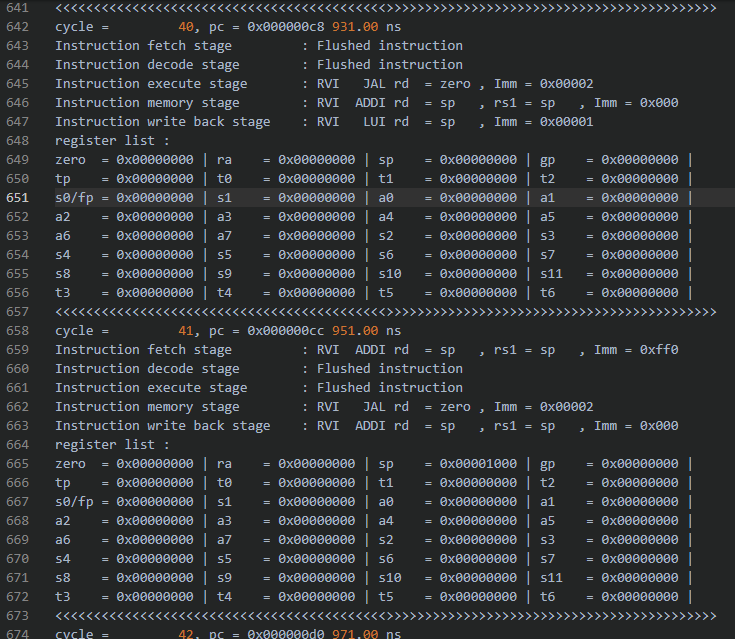

पाठ फ़ाइल में कर्नेल की स्थिति के बारे में डिबगिंग जानकारी लिखने की क्षमता जोड़ना। रजिस्टर फ़ाइल की स्थिति सारणीबद्ध रूप में प्रस्तुत की गई है, और कर्नेल द्वारा वर्तमान में निष्पादित अनुदेश / निर्देश भी इंगित किए गए हैं। यह 2 अंकों का एक एनालॉग है, लेकिन प्राप्त जानकारी के साथ अधिक हेरफेर करने की अनुमति देता है;

पाठ फ़ाइलरजिस्टर फाइल का आरम्भिकरण:

सपा मूल्य बदलें:

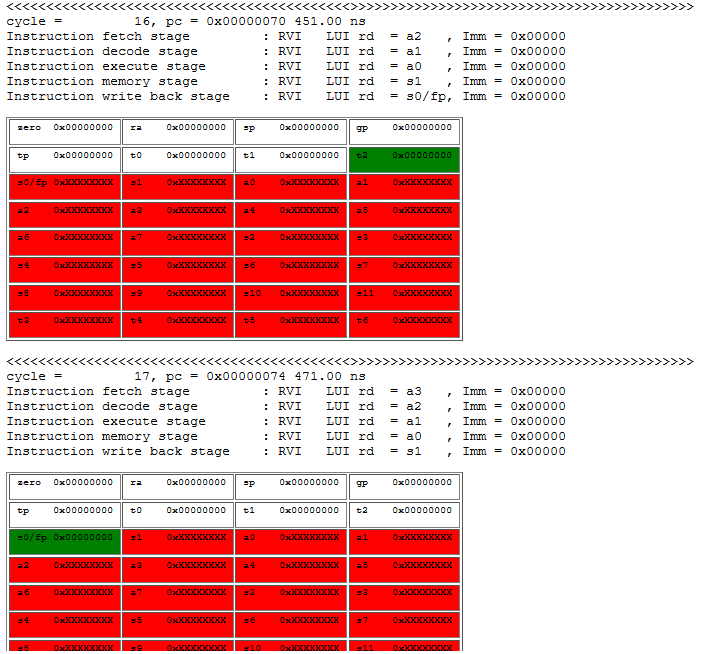

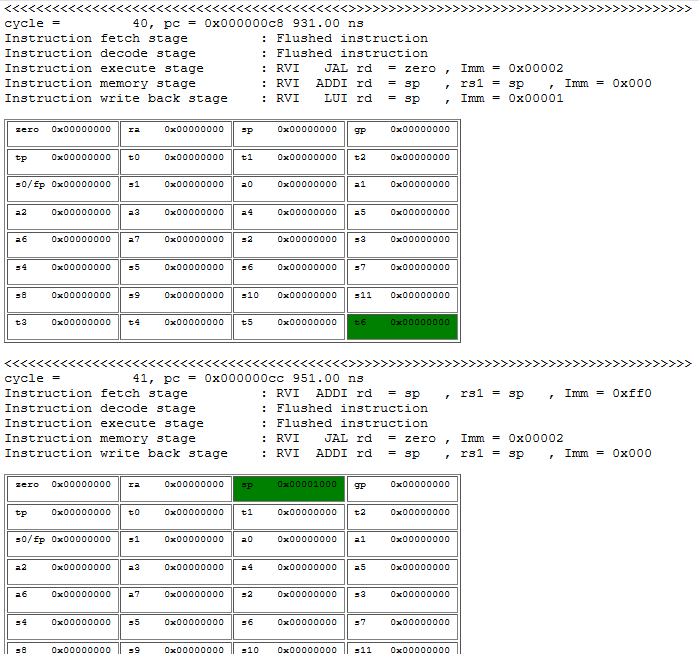

HTML फ़ाइल में कर्नेल की स्थिति के बारे में डिबगिंग जानकारी लिखने की क्षमता जोड़ना। कोशिकाओं के मूल्यों को बदलने के बारे में नोट्स के साथ रजिस्टर फाइल की स्थिति सारणीबद्ध रूप में प्रस्तुत की गई है, साथ ही वर्तमान में कर्नेल द्वारा निष्पादित किए जा रहे निर्देशों को प्रदर्शित किया गया है। यह पैराग्राफ 2 और 4 का एक एनालॉग है, लेकिन उनके अलावा यह आपको आसानी से डेटा में बदलाव का संकेत देता है। जैसा कि नीचे दिए गए चित्रों में देखा जा सकता है, यदि रजिस्टर मूल्य को परिभाषित नहीं किया गया था, तो रजिस्टरों को लाल रंग में हाइलाइट किया गया है (रजिस्टर s0 / fp - t6)। चक्र 17 पर, रजिस्टर s0 / fp का मान बदलता है और सेल को हरे रंग में हाइलाइट किया जाता है।

साइकल 41 पर, 0x00010000 मान को रजिस्टर में लोड किया गया है।

HTML फ़ाइलरजिस्टर फाइल का आरम्भिकरण:

सपा मूल्य बदलें:

गिरी शाखाओं की तुलना:वर्तमान में विभिन्न शाखाओं के लिए समर्थित कर्नेल निर्देश:

समर्थित सहायक:

कार्यक्रम लिखने के लिए समर्थित भाषाएँ:

कर्नेल के लिए आवश्यक FPGA संसाधन (nf_cpu):

EP4CE22F17C6 (de0_nano):

10M50DAF484C7G (de10_lite):

परियोजना का विकास।

भविष्य में क्या करने की योजना है:

- सभी आरवी 32 आई निर्देश (विवरण चरण में) जोड़ें;

- डिबगिंग लागू करें;

- एक डीएमए (डीएमए) नियंत्रक जोड़ें;

- अन्य टायर AXI, एवलॉन, विशबोन के लिए समर्थन जोड़ें;

- कैश (कैश) मेमोरी जोड़ें;

- विभिन्न परिधीयों (SPI, TWI (I2C), ईथरनेट (10 बेस-टी)) को एकीकृत करें;

- अवरोध नियंत्रक जोड़ें;

- अन्य डिबग बोर्डों में विभिन्न संस्करणों को पोर्ट करें;

- कर्नेल की दृश्यता बढ़ाने के लिए अन्य तरीके जोड़ें;

- उदाहरण के लिए, आरटीओएस चल रहा है।

कर्नेल के विकास के लिए सिफारिशें और सुझाव भी स्वीकार किए जाते हैं।

रिपॉजिटरी से लिंक: nanoFOX