पिछले भाग में, हमने Altera / Intel FPGA पर आधारित किसी भी RAM के बिना एक माइक्रोकंट्रोलर को इकट्ठा किया। हालांकि, बोर्ड में स्थापित SO-DIMM DDR2 1Gb के साथ एक कनेक्टर है, जो स्पष्ट रूप से, मैं उपयोग करना चाहता हूं। ऐसा करने के लिए, हमें एक मॉड्यूल में

पिछले भाग में, हमने Altera / Intel FPGA पर आधारित किसी भी RAM के बिना एक माइक्रोकंट्रोलर को इकट्ठा किया। हालांकि, बोर्ड में स्थापित SO-DIMM DDR2 1Gb के साथ एक कनेक्टर है, जो स्पष्ट रूप से, मैं उपयोग करना चाहता हूं। ऐसा करने के लिए, हमें एक मॉड्यूल में ALTMEMPHY इंटरफ़ेस के साथ DDR2 नियंत्रक को लपेटने की आवश्यकता है जो कि RocketChip में प्रयुक्त टाइललिंक मेमोरी प्रोटोकॉल के लिए समझ में आता है। कट के तहत - स्पर्श डिबगिंग, जानवर बल प्रोग्रामिंग और RAKE।

जैसा कि आप जानते हैं, कंप्यूटर विज्ञान में दो मुख्य समस्याएं हैं: कैश अमान्यकरण और परिवर्तनशील नामकरण। केडीपीवी में, आप एक दुर्लभ क्षण देखते हैं - दो मुख्य समस्याएं जिन्हें सीएस ने एक दूसरे से मुलाकात की और कुछ साजिश कर रहे हैं ।

अस्वीकरण: पिछले लेख से चेतावनी के अलावा, मैं दृढ़ता से अनुशंसा करता हूं कि आप प्रयोगों को दोहराने से पहले लेख को पढ़ें, ताकि एफपीजीए, मेमोरी मॉड्यूल या पावर सर्किट को नुकसान से बचा जा सके।

इस बार मैं चाहता था, अगर लिनक्स नहीं बूट करता है, तो कम से कम रैम को कनेक्ट करें, जो मेरे बोर्ड पर पहले से ही पूरी गीगाबाइट है (या आप चार तक डाल सकते हैं)। जीडीबी + ओपनओसीडी के एक समूह के माध्यम से पढ़ने और लिखने की क्षमता पर विचार करने के लिए एक सफलता मानदंड प्रस्तावित है, जिसमें 16 बाइट्स (स्मृति के लिए एक अनुरोध की चौड़ाई) द्वारा संरेखित पते शामिल हैं। पहली नज़र में, आपको बस कॉन्फ़िगरेशन को थोड़ा ठीक करने की आवश्यकता है, SoC जनरेटर बॉक्स से बाहर रैम का समर्थन नहीं कर सकता है। यह इसका समर्थन करता है, लेकिन एमआईजी इंटरफ़ेस (अच्छी तरह से, और संभवतः, माइक्रोसेमी से कुछ अन्य इंटरफ़ेस) के माध्यम से। मानक इंटरफ़ेस के माध्यम से, AXI4 भी इसका समर्थन करता है, लेकिन, जैसा कि मैं इसे समझता हूं, इसे प्राप्त करना इतना आसान नहीं है (कम से कम, प्लेटफ़ॉर्म डिज़ाइनर में महारत हासिल नहीं है)।

गीतात्मक विषयांतर: जहां तक मैं समझता हूं, एआरएम द्वारा विकसित "इंट्रा-चिप" AXI इंटरफेस की एक लोकप्रिय श्रृंखला है। यहाँ कोई सोचता है कि यह सब पेटेंट और बंद है। लेकिन जब मैंने पंजीकरण किया (बिना किसी "विश्वविद्यालय के कार्यक्रम" और कुछ और के बिना - केवल ई-मेल द्वारा और प्रश्नावली भरकर) और विनिर्देश तक पहुँच प्राप्त करने के बाद, मुझे सुखद आश्चर्य हुआ। बेशक, मैं एक वकील नहीं हूं, लेकिन ऐसा लगता है कि मानक बहुत खुला है: आपको या तो एआरएम से लाइसेंस प्राप्त गुठली का उपयोग करना होगा, या एआरएम के साथ संगत होने का दावा नहीं करना चाहिए, और फिर सब कुछ ठीक लगता है । लेकिन सामान्य तौर पर, लाइसेंस पढ़ें, वकीलों के साथ पढ़ें, आदि।

बंदर और टाइललिंक (कल्पित)

कार्य काफी सरल लग रहा था, और मैंने ddr2_64bit मॉड्यूल बोर्ड के विवरण को परियोजना से पहले से ही आपूर्तिकर्ता से खोला:

इंटेल संपत्ति और आम तौर पर module ddr2_64bit ( local_address, local_write_req, local_read_req, local_burstbegin, local_wdata, local_be, local_size, global_reset_n, pll_ref_clk, soft_reset_n, local_ready, local_rdata, local_rdata_valid, local_refresh_ack, local_init_done, reset_phy_clk_n, mem_odt, mem_cs_n, mem_cke, mem_addr, mem_ba, mem_ras_n, mem_cas_n, mem_we_n, mem_dm, phy_clk, aux_full_rate_clk, aux_half_rate_clk, reset_request_n, mem_clk, mem_clk_n, mem_dq, mem_dqs); input [25:0] local_address; input local_write_req; input local_read_req; input local_burstbegin; input [127:0] local_wdata; input [15:0] local_be; input [2:0] local_size; input global_reset_n; input pll_ref_clk; input soft_reset_n; output local_ready; output [127:0] local_rdata; output local_rdata_valid; output local_refresh_ack; output local_init_done; output reset_phy_clk_n; output [1:0] mem_odt; output [1:0] mem_cs_n; output [1:0] mem_cke; output [13:0] mem_addr; output [1:0] mem_ba; output mem_ras_n; output mem_cas_n; output mem_we_n; output [7:0] mem_dm; output phy_clk; output aux_full_rate_clk; output aux_half_rate_clk; output reset_request_n; inout [1:0] mem_clk; inout [1:0] mem_clk_n; inout [63:0] mem_dq; inout [7:0] mem_dqs; ...

लोकप्रिय ज्ञान कहता है: "रूसी में किसी भी दस्तावेज को शब्दों से शुरू करना चाहिए:" तो, यह काम नहीं करता है। " लेकिन यहां इंटरफ़ेस पूरी तरह से सहज नहीं है, इसलिए हम अभी भी इसे पढ़ते हैं । विवरण में हमें तुरंत बताया जाता है कि DDR2 के साथ काम करना आसान काम नहीं है। आपको पीएलएल को कॉन्फ़िगर करने की आवश्यकता है, कुछ अंशांकन, दरार- local_init_done - local_init_done , local_init_done सिग्नल local_init_done , आप काम कर सकते हैं। सामान्य तौर पर, यहां नामकरण तर्क लगभग निम्नलिखित है: local_ उपसर्गों के साथ नाम "उपयोगकर्ता" इंटरफ़ेस हैं, mem_ पोर्ट्स mem_ मेमोरी मॉड्यूल से जुड़े पैरों पर सीधे आउटपुट के लिए mem_ चाहिए, pll_ref_clk को मॉड्यूल सेट करते समय निर्दिष्ट आवृत्ति के साथ एक घड़ी के संदेश भेजने की आवश्यकता है - बाकी इसे से प्राप्त होगा। आवृत्तियों, अच्छी तरह से, इनपुट और आउटपुट के सभी प्रकार रीसेट और आवृत्ति आउटपुट, जो उपयोगकर्ता इंटरफ़ेस को सिंक्रोनाइज़ के साथ काम करना चाहिए।

आइए ddr2_64bit मॉड्यूल की मेमोरी और इंटरफ़ेस के लिए बाहरी संकेतों का विवरण बनाएं:

विशेषता मेम trait MemIf { val local_init_done = Output(Bool()) val global_reset_n = Input(Bool()) val pll_ref_clk = Input(Clock()) val soft_reset_n = Input(Bool()) val reset_phy_clk_n = Output(Clock()) val mem_odt = Output(UInt(2.W)) val mem_cs_n = Output(UInt(2.W)) val mem_cke = Output(UInt(2.W)) val mem_addr = Output(UInt(14.W)) val mem_ba = Output(UInt(2.W)) val mem_ras_n = Output(UInt(1.W)) val mem_cas_n = Output(UInt(1.W)) val mem_we_n = Output(UInt(1.W)) val mem_dm = Output(UInt(8.W)) val phy_clk = Output(Clock()) val aux_full_rate_clk = Output(Clock()) val aux_half_rate_clk = Output(Clock()) val reset_request_n = Output(Bool()) val mem_clk = Analog(2.W) val mem_clk_n = Analog(2.W) val mem_dq = Analog(64.W) val mem_dqs = Analog(8.W) def connectFrom(mem_if: MemIf): Unit = { local_init_done := mem_if.local_init_done mem_if.global_reset_n := global_reset_n mem_if.pll_ref_clk := pll_ref_clk mem_if.soft_reset_n := soft_reset_n reset_phy_clk_n := mem_if.reset_phy_clk_n mem_odt <> mem_if.mem_odt mem_cs_n <> mem_if.mem_cs_n mem_cke <> mem_if.mem_cke mem_addr <> mem_if.mem_addr mem_ba <> mem_if.mem_ba mem_ras_n <> mem_if.mem_ras_n mem_cas_n <> mem_if.mem_cas_n mem_we_n <> mem_if.mem_we_n mem_dm <> mem_if.mem_dm mem_clk <> mem_if.mem_clk mem_clk_n <> mem_if.mem_clk_n mem_dq <> mem_if.mem_dq mem_dqs <> mem_if.mem_dqs phy_clk := mem_if.phy_clk aux_full_rate_clk := mem_if.aux_full_rate_clk aux_half_rate_clk := mem_if.aux_half_rate_clk reset_request_n := mem_if.reset_request_n } } class MemIfBundle extends Bundle with MemIf

वर्ग dd2_64bit class ddr2_64bit extends BlackBox { override val io = IO(new MemIfBundle { val local_address = Input(UInt(26.W)) val local_write_req = Input(Bool()) val local_read_req = Input(Bool()) val local_burstbegin = Input(Bool()) val local_wdata = Input(UInt(128.W)) val local_be = Input(UInt(16.W)) val local_size = Input(UInt(3.W)) val local_ready = Output(Bool()) val local_rdata = Output(UInt(128.W)) val local_rdata_valid = Output(Bool()) val local_refresh_ack = Output(Bool()) }) }

यहां रेक का पहला गुच्छा मेरा इंतजार कर रहा था: सबसे पहले, ROMGenerator वर्ग को ROMGenerator , मैंने सोचा था कि मेमोरी कंट्रोलर को एक वैश्विक चर के माध्यम से डिजाइन की गहराई से बाहर निकाला जा सकता है, और छेनी किसी तरह तारों को खुद आगे कर देगा। यह काम नहीं किया इसलिए, मुझे एक MemIfBundle वायरिंग हार्नेस बनाना पड़ा जो पूरे पदानुक्रम में MemIfBundle । यह BlackBox बाहर क्यों नहीं रहता है, और यह एक बार में कनेक्ट नहीं होता है? तथ्य यह है कि BlackBox साथ सभी बाहरी पोर्ट val io = IO(new Bundle { ... }) में भरे हुए हैं। यदि पूरे MemIfBundle बंडल में एक चर में बनाया जाता है, तो इस चर के नाम को सभी बंदरगाहों के नामों के लिए एक उपसर्ग बनाया जाएगा, और नाम ब्लॉक के इंटरफेस के साथ मेल नहीं खाएंगे। संभवतः, यह किसी भी तरह पर्याप्त रूप से किया जा सकता है, लेकिन अब इसे इस तरह से छोड़ दें।

इसके अलावा, अन्य टाइललिंक उपकरणों के साथ सादृश्य द्वारा (मुख्य रूप से rocket-chip/src/main/scala/tilelink ), और विशेष रूप से BootROM , हम मेमोरी कंट्रोलर के लिए हमारे इंटरफ़ेस का वर्णन करेंगे:

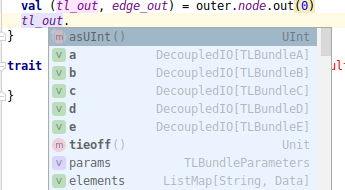

class AltmemphyDDR2RAM(implicit p: Parameters) extends LazyModule { val MemoryPortParams(MasterPortParams(base, size, beatBytes, _, _, executable), 1) = p(ExtMem).get val node = TLManagerNode(Seq(TLManagerPortParameters( Seq(TLManagerParameters( address = AddressSet.misaligned(base, size), resources = new SimpleDevice("ram", Seq("sifive,altmemphy0")).reg("mem"), regionType = RegionType.UNCACHED, executable = executable, supportsGet = TransferSizes(1, 16), supportsPutFull = TransferSizes(1, 16), fifoId = Some(0) )), beatBytes = 16 ))) override lazy val module = new AltmemphyDDR2RAMImp(this) } class AltmemphyDDR2RAMImp(_outer: AltmemphyDDR2RAM)(implicit p: Parameters) extends LazyModuleImp(_outer) { val (in, edge) = _outer.node.in(0) val ddr2 = Module(new ddr2_64bit) val mem_if = IO(new MemIfBundle)

ExtMem कुंजी ExtMem हम SoC ExtMem से बाहरी मेमोरी पैरामीटर निकालते हैं ( यह अजीब सिंटैक्स मुझे यह कहने की अनुमति देता है कि "मुझे पता है कि वे केस क्लास MemoryPortParameters का एक उदाहरण MemoryPortParameters (यह MemoryPortParameters कोड को संकलित करने के चरण में कुंजी के प्रकार की गारंटी है, इस शर्त के अनुसार) हम Option[MemoryPortParams] से सामग्री लेने के क्रम में गिर जाते हैं, None बराबर None , लेकिन तब Option[MemoryPortParams] ... में मेमोरी नियंत्रक बनाने के लिए कुछ भी नहीं था, इसलिए, मुझे केस क्लास की आवश्यकता नहीं है, और इसके कुछ क्षेत्रों की आवश्यकता है ")। अगला, हम टाइललिंक डिवाइस का प्रबंधक पोर्ट बनाते हैं (टाइललिंक प्रोटोकॉल मेमोरी से संबंधित लगभग हर चीज की बातचीत सुनिश्चित करता है: डीडीआर नियंत्रक और अन्य मेमोरी-मैप किए गए डिवाइस, प्रोसेसर कैश, शायद कुछ और, प्रत्येक डिवाइस में कई पोर्ट हो सकते हैं, प्रत्येक उपकरण प्रबंधक और ग्राहक दोनों हो सकते हैं)। beatBytes , जैसा कि मैं इसे समझता हूं, एक लेनदेन का आकार निर्धारित करता है, और हमारे पास नियंत्रक के साथ 16 बाइट्स का आदान-प्रदान होता है। HasAltmemphyDDR2 और HasAltmemphyDDR2Imp हम HasAltmemphyDDR2Imp में सही स्थानों पर HasAltmemphyDDR2Imp हैं, विन्यास लिखते हैं

class BigZeowaaConfig extends Config ( new WithNBreakpoints(2) ++ new WithNExtTopInterrupts(0) ++ new WithExtMemSize(1l << 30) ++ new WithNMemoryChannels(1) ++ new WithCacheBlockBytes(16) ++ new WithNBigCores(1) ++ new WithJtagDTM ++ new BaseConfig )

AltmemphyDDR2RAMImp में "उल्लू का स्केच" बनाने के बाद, मैंने डिज़ाइन को संश्लेषित किया (केवल ~ 30MHz पर कुछ, यह अच्छा है कि मैं 25MHz से घड़ी करता हूं) और, अपनी उंगलियों को मेमोरी मॉड्यूल और FPGA चिप पर डालकर, मैंने इसे बोर्ड पर अपलोड किया। तब मैंने देखा कि वास्तविक सहज ज्ञान युक्त इंटरफ़ेस क्या है: यह तब है जब आप मेमोरी लिखने के लिए gdb में एक कमांड देते हैं, और एक जमे हुए प्रोसेसर और पके हुए ब्लॉक उंगलियों को तेज गर्मी महसूस हो रही है, आपको तत्काल बोर्ड पर रीसेट बटन दबाने और नियंत्रक को ठीक करने की आवश्यकता है।

DDR2 नियंत्रक के लिए प्रलेखन पढ़ें

जाहिर है, बंदरगाहों की सूची से परे नियंत्रक पर प्रलेखन पढ़ने का समय आ गया है। तो, हमारे पास यहां क्या है? .. उफ़, यह पता चला है कि local_ / उपसर्ग के साथ I / local_ को समान रूप से local_ साथ सेट नहीं किया जाना चाहिए, जो कि 25MHz है, लेकिन या तो phy_clk साथ आधे दर नियंत्रक के लिए स्मृति आवृत्ति phy_clk , या, हमारे मामले में, aux_half_rate_clk (शायद अभी भी aux_full_rate_clk ?), जो पूर्ण मेमोरी आवृत्ति aux_full_rate_clk है, और यह एक मिनट के लिए 166MHz है।

इसलिए, आवृत्ति डोमेन की सीमाओं को पार करना आवश्यक है। पुरानी स्मृति के अनुसार , मैंने कुंडी का उपयोग करने का फैसला किया, या उनकी एक श्रृंखला:

+-+ +-+ +-+ +-+ --| |--| |--| |--| |---> +-+ +-+ +-+ +-+ | | | | ---+ | | | inclk | | | | | | --------+----+ | outclk | | ------------------+ output enable

लेकिन, घंटे के साथ छेड़छाड़ करने के बाद, मैं इस नतीजे पर पहुंचा कि मैं "स्केलर" लेचेस (हाई-फ़्रीक्वेंसी डोमेन और इसके विपरीत) पर दो कतारों को संभाल नहीं पा रहा हूँ, जिनमें से प्रत्येक में एंटीडायरेक्शनल सिग्नल ( ready और valid ) होंगे, और यहाँ तक कि सुनिश्चित करने के लिए भी। कुछ बीट एक बीट या दो सड़क से पीछे नहीं हटेंगे। कुछ समय बाद, मुझे एहसास हुआ कि एक सामान्य घड़ी संकेत के बिना ready - valid पर सिंक्रोनाइज़ेशन का वर्णन करना - गैर-अवरुद्ध डेटा संरचनाओं को बनाने के लिए एक कार्य है, जिसे आपको सोचने और औपचारिक रूप से बहुत कुछ साबित करने की आवश्यकता है, यह एक गलती करना आसान है, यह नोटिस करना मुश्किल है, और सबसे महत्वपूर्ण, सब कुछ पहले से ही है। हमारे सामने लागू किया गया: इंटेल में एक dcfifo आदिम है, जो विन्यास योग्य लंबाई और चौड़ाई की एक कतार है, जिसे विभिन्न आवृत्ति डोमेन से पढ़ा और लिखा जाता है। नतीजतन, मैंने ताजे छेनी के प्रयोगात्मक अवसर का लाभ उठाया, अर्थात्, मानकीकृत ब्लैक बॉक्स:

class FIFO (val width: Int, lglength: Int) extends BlackBox(Map( "intended_device_family" -> StringParam("Cyclone IV E"), "lpm_showahead" -> StringParam("OFF"), "lpm_type" -> StringParam("dcfifo"), "lpm_widthu" -> IntParam(lglength), "overflow_checking" -> StringParam("ON"), "rdsync_delaypipe" -> IntParam(5), "underflow_checking" -> StringParam("ON"), "use_eab" -> StringParam("ON"), "wrsync_delaypipe" -> IntParam(5), "lpm_width" -> IntParam(width), "lpm_numwords" -> IntParam(1 << lglength) )) { override val io = IO(new Bundle { val data = Input(UInt(width.W)) val rdclk = Input(Clock()) val rdreq = Input(Bool()) val wrclk = Input(Clock()) val wrreq = Input(Bool()) val q = Output(UInt(width.W)) val rdempty = Output(Bool()) val wrfull = Output(Bool()) }) override def desiredName: String = "dcfifo" }

और उन्होंने मनमाना डेटा प्रकारों का एक छोटा सा दूरबीन लिखा:

object FIFO { def apply[T <: Data]( lglength: Int, output: T, outclk: Clock, input: T, inclk: Clock ): FIFO = { val res = Module(new FIFO(width = output.widthOption.get, lglength = lglength)) require(input.getWidth == res.width) output := res.io.q.asTypeOf(output) res.io.rdclk := outclk res.io.data := input.asUInt() res.io.wrclk := inclk res } }

डिबगिंग

उसके बाद, कोड दो पहले से ही यूनिडायरेक्शनल tl_req माध्यम से डोमेन के बीच संदेशों को स्थानांतरित करने में बदल गया: tl_req / ddr_req और ddr_resp / tl_resp ( tl_ prefix के साथ एक को टाइललिंक के साथ जोड़ा जाता है, यह तथ्य कि ddr_ मेमोरी कंट्रोलर के साथ है)। समस्या यह है कि सब कुछ वैसे भी गतिरोध था, और कभी-कभी यह बहुत गर्म था। और अगर local_read_req का कारण local_read_req और local_write_req की एक साथ सेटिंग local_write_req , तो local_write_req से लड़ना इतना आसान नहीं था। उसी समय का कोड कुछ इस तरह था

class AltmemphyDDR2RAMImp(_outer: AltmemphyDDR2RAM)(implicit p: Parameters) extends LazyModuleImp(_outer) { val addrSize = log2Ceil(_outer.size / 16) val (in, edge) = _outer.node.in(0) val ddr2 = Module(new ddr2_64bit) require(ddr2.io.local_address.getWidth == addrSize) val tl_clock = clock val ddr_clock = ddr2.io.aux_full_rate_clk val mem_if = IO(new MemIfBundle) class DdrRequest extends Bundle { val size = UInt(in.a.bits.size.widthOption.get.W) val source = UInt(in.a.bits.source.widthOption.get.W) val address = UInt(addrSize.W) val be = UInt(16.W) val wdata = UInt(128.W) val is_reading = Bool() } val tl_req = Wire(new DdrRequest) val ddr_req = Wire(new DdrRequest) val fifo_req = FIFO(2, ddr_req, ddr_clock, tl_req, clock) class DdrResponce extends Bundle { val is_reading = Bool() val size = UInt(in.d.bits.size.widthOption.get.W) val source = UInt(in.d.bits.source.widthOption.get.W) val rdata = UInt(128.W) } val tl_resp = Wire(new DdrResponce) val ddr_resp = Wire(new DdrResponce) val fifo_resp = FIFO(2, tl_resp, clock, ddr_resp, ddr_clock)

समस्या का स्थानीयकरण करने के लिए, मैंने सभी कोड withClock(ddr_clock) के अंदर अंदर कोड टिप्पणी करने का निर्णय लिया withClock(ddr_clock) , यह ऐसा नहीं लगता है कि यह एक धारा बना रहा है) और इसे ठीक काम करने वाले स्टब के साथ बदलें:

withClock (ddr_clock) { ddr_resp.rdata := 0.U ddr_resp.is_reading := ddr_req.is_reading ddr_resp.size := ddr_req.size ddr_resp.source := ddr_req.source val will_read = Wire(!fifo_req.io.rdempty && !fifo_resp.io.wrfull) fifo_req.io.rdreq := will_read fifo_resp.io.wrreq := RegNext(will_read) }

जैसा कि मैंने बाद में महसूस किया, यह स्टब भी काम नहीं किया क्योंकि Wire(...) निर्माण, जिसे मैंने "विश्वसनीयता के लिए" जोड़ा, यह दिखाने के लिए कि यह एक नामित तार था, वास्तव में तर्क का उपयोग केवल प्रोटोटाइप बनाने के लिए किया गया था अर्थ का प्रकार, लेकिन इसे अभिव्यक्ति-तर्क से नहीं जोड़ा गया । इसके अलावा, जब मैंने पढ़ने की कोशिश की जो अभी भी उत्पन्न हुई थी, तो मुझे एहसास हुआ कि सिमुलेशन मोड में टाइललिंक प्रोटोकॉल के साथ गैर-अनुपालन के संबंध में मुखर चयन है। वे शायद बाद में मेरे काम आएंगे, लेकिन अभी तक सिमुलेशन चलाने की कोई कोशिश नहीं हुई है - इसे क्यों शुरू करें? Verilator को शायद Alter के IP Cores के बारे में नहीं पता है, ModelSim Starter Edition इस तरह के एक विशाल प्रोजेक्ट का अनुकरण करने की संभावना से इनकार करेगा, लेकिन मैंने सिमुलेशन के लिए एक नियंत्रक मॉडल की कमी की भी शपथ ली। और इसे उत्पन्न करने के लिए, आपको संभवतः पहले नियंत्रक के नए संस्करण पर स्विच करने की आवश्यकता है (क्योंकि पुराने क्वार्टर में पुराने को कॉन्फ़िगर किया गया था)।

वास्तव में, कोड के ब्लॉकों को लगभग काम करने वाले संस्करण से लिया गया था, न कि वह जो कुछ घंटों पहले सक्रिय रूप से डिबग किया गया था। लेकिन आप बेहतर;) वैसे, आप लगातार डिज़ाइन को फिर से इकट्ठा कर सकते हैं यदि मेमोरी नियंत्रक की बुनियादी कार्यक्षमता के दृष्टिकोण से WithNBigCores(1) सेटिंग को WithNBigCores(1) से बदल दिया जाए तो कोई अंतर नहीं लगता है। और एक छोटी सी चाल: हर बार एक ही कमांड को gdb में नहीं चलाने के लिए (कम से कम मुझे वहां सत्रों के बीच कमांड का इतिहास नहीं है), आप बस कमांड लाइन पर इस तरह से कुछ लिख सकते हैं

../../rocket-tools/bin/riscv32-unknown-elf-gdb -q -ex "target remote :3333" -ex "x/x 0x80000000" ../../rocket-tools/bin/riscv32-unknown-elf-gdb -q -ex "target remote :3333" -ex "set variable *0x80000000=0x1234"

और शेल के नियमित साधनों का उपयोग करके आवश्यकतानुसार चलाएं।

परिणाम

परिणामस्वरूप, नियंत्रक के साथ काम करने के लिए निम्न कोड प्राप्त किया गया था:

withClock(ddr_clock) { val rreq = RegInit(false.B)

यहां हम अभी भी पूर्णता की कसौटी को थोड़ा बदल देंगे: मैंने पहले ही देखा है कि कैसे, मेमोरी के साथ किसी भी काम के बिना, रिकॉर्ड किया गया डेटा मानो पढ़ा जाता है, क्योंकि यह एक कैश है। इसलिए, हम कोड का एक सरल टुकड़ा संकलित करते हैं:

#include <stdint.h> static volatile uint8_t *x = (uint8_t *)0x80000000u; void entry() { for (int i = 0; i < 1<<24; ++i) { x[i] = i; } }

../../rocket-tools/bin/riscv64-unknown-elf-gcc test.c -S -O1

नतीजतन, हम कोडांतरक सूची के निम्नलिखित टुकड़े को प्राप्त करते हैं, पहले 16 एमबी मेमोरी को आरंभ करते हुए:

li a5,1 slli a5,a5,31 li a3,129 slli a3,a3,24 .L2: andi a4,a5,0xff sb a4,0(a5) addi a5,a5,1 bne a5,a3,.L2

bootrom/xip/leds.S की शुरुआत में bootrom/xip/leds.S अब यह संभावना नहीं है कि सब कुछ केवल एक कैश पर ही रखा जा सकेगा। यह मेकफाइल को चलाने के लिए, क्वार्ट्स में परियोजना का पुनर्निर्माण, बोर्ड में इसे भरने, ओपनओसीडी + जीडीबी को जोड़ने और ... संभवतः, जयकार, जीत: बनी हुई है।

$ ../../rocket-tools/bin/riscv32-unknown-elf-gdb -q -ex "target remote :3333" Remote debugging using :3333 warning: No executable has been specified and target does not support determining executable automatically. Try using the "file" command. 0x0000000000010014 in ?? () (gdb) x/x 0x80000000 0x80000000: 0x03020100 (gdb) x/x 0x80000100 0x80000100: 0x03020100 (gdb) x/x 0x80000111 0x80000111: 0x14131211 (gdb) x/x 0x80010110 0x80010110: 0x13121110 (gdb) x/x 0x80010120 0x80010120: 0x23222120

क्या ऐसा है, हम अगली श्रृंखला में पता लगाएंगे (मैं प्रदर्शन, स्थिरता आदि के बारे में भी नहीं कह सकता)।

कोड: AltmemphyDDR2RAM.scala