यह लेख Verilog में RAM के सबसे सरल कार्यान्वयन पर चर्चा करता है।

कोड पार्सिंग के साथ आगे बढ़ने से पहले, यह अनुशंसा की जाती है कि आप वेरिलॉग के मूल सिंटैक्स को सीखें।

यहां आप प्रशिक्षण सामग्री पा सकते हैं ।

रैम

चरण 1: मॉड्यूल को संबंधित इनपुट / आउटपुट सिग्नल के साथ घोषित करना

module ram ( input [word_size - 1:0] data, input [word_size - 1:0] addr, input wr, input clk, output response, output [word_size - 1:0] out ); parameter word_size = 32;

- data - लिखने के लिए डेटा।

- addr - RAM में मेमोरी का पता।

- wr - स्थिति (पढ़ें / लिखें)।

- clk - घड़ी चक्र प्रणाली।

- प्रतिक्रिया - रैम की तत्परता (1 - यदि रैम ने पढ़ने / लिखने के अनुरोध को संसाधित किया, 0 - अन्यथा)।

- राम से पढ़ा हुआ डेटा।

यह कार्यान्वयन Altera Max 10 FPGA में एकीकृत किया गया था, जिसमें 32-बिट आर्किटेक्चर है, और इसलिए डेटा और पता (word_size) के लिए आकार 32 बिट्स है।

चरण 2: मॉड्यूल के अंदर रजिस्टरों की घोषणा करना

डेटा संग्रहीत करने के लिए एक सरणी घोषणा:

parameter size = 1<<32; reg [word_size-1:0] ram [size-1:0];

हमेशा ब्लॉक में उनके परिवर्तनों को ट्रैक करने के लिए हमें पिछले इनपुट मापदंडों को संग्रहीत करने की आवश्यकता है:

reg [word_size-1:0] data_reg; reg [word_size-1:0] addr_reg; reg wr_reg;

और अंतिम दो रजिस्टर हमेशा ब्लॉक में गणना के बाद आउटपुट सिग्नल अपडेट करने के लिए:

reg [word_size-1:0] out_reg; reg response_reg;

हम रजिस्टरों को शुरू करते हैं:

initial begin response_reg = 1; data_reg = 0; addr_reg = 0; wr_reg = 0; end

चरण 3: ब्लॉक के हमेशा तर्क को लागू करना

always @(negedge clk) begin if ((data != data_reg) || (addr%size != addr_reg)|| (wr != wr_reg)) begin response_reg = 0; data_reg = data; addr_reg = addr%size; wr_reg = wr; end else begin if (response_reg == 0) begin if (wr) ram[addr] = data; else out_reg = ram[addr]; response_reg = 1; end end end

हमेशा ब्लॉक नेगेडेजे द्वारा ट्रिगर किया जाता है, अर्थात। फिलहाल घड़ी 1 से 0. तक चलती है। यह कैश के साथ रैम को सही ढंग से सिंक्रनाइज़ करने के लिए किया जाता है। अन्यथा, ऐसे मामले हो सकते हैं जब रैम में 1 से 0 तक तैयार स्थिति को रीसेट करने का समय नहीं होता है और अगली घड़ी में, कैश यह तय करता है कि रैम ने अपने अनुरोध को सफलतापूर्वक संसाधित किया है, जो कि मौलिक रूप से गलत है।

ब्लॉक के हमेशा एल्गोरिथ्म का तर्क निम्नानुसार है: यदि डेटा अपडेट किया गया है, तो तत्परता स्थिति को 0 पर रीसेट करें और डेटा लिखें / पढ़ें, यदि लिखना / पढ़ना पूरा हो गया है, तो 1 के लिए तत्परता स्थिति को अपडेट करें।

अंत में, निम्न कोड अनुभाग जोड़ें:

assign out = out_reg; assign response = response_reg;

हमारे मॉड्यूल के आउटपुट सिग्नल का प्रकार तार है। इस प्रकार के संकेतों को बदलने का एकमात्र तरीका दीर्घकालिक असाइनमेंट है, जो हमेशा ब्लॉक के अंदर निषिद्ध है। इस कारण से, हमेशा ब्लॉक रजिस्टर का उपयोग करता है, जो बाद में आउटपुट सिग्नल को सौंपा जाता है।

प्रत्यक्ष मानचित्रण कैश

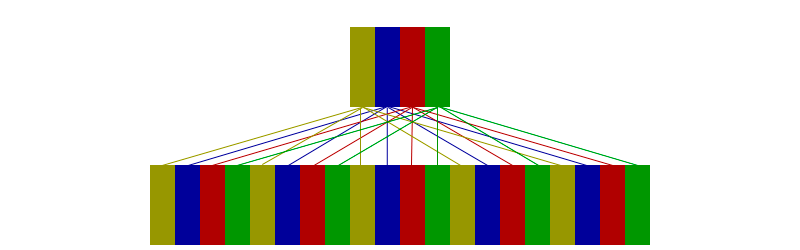

डायरेक्ट मैपिंग कैश कैश के सबसे सरल प्रकारों में से एक है। इस कार्यान्वयन में, कैश में n तत्व होते हैं, और RAM को सशर्त रूप से n द्वारा ब्लॉक में विभाजित किया जाता है, फिर कैश में i-th तत्व रैम में ऐसे सभी k-th तत्वों से मेल खाता है जो इस शर्त को संतुष्ट करते हैं कि मैं = k% n।

नीचे दी गई छवि आकार 4 का कैश और आकार 16 की रैम दिखाती है।

प्रत्येक कैश तत्व में निम्नलिखित जानकारी होती है:

- वैधता बिट - क्या कैश में जानकारी प्रासंगिक है।

- टैग रैम में ब्लॉक नंबर है जहां यह तत्व स्थित है।

- data - वह जानकारी जो हम लिखते / पढ़ते हैं।

जब पढ़ने का अनुरोध किया जाता है, तो कैश इनपुट पते को दो भागों में विभाजित करता है - एक टैग और एक सूचकांक। सूचकांक का आकार लॉग (n) है, जहां n कैश का आकार है।

चरण 1: मॉड्यूल को संबंधित इनपुट / आउटपुट सिग्नल के साथ घोषित करना

module direct_mapping_cache ( input [word_size-1:0] data, input [word_size-1:0] addr, input wr, input clk, output response, output is_missrate, output [word_size-1:0] out ); parameter word_size = 32;

कैश मॉड्यूल की घोषणा रैम के समान है, नए आउटपुट सिग्नल के अपवाद के साथ is_missrate है। यह आउटपुट इस बारे में जानकारी संग्रहीत करता है कि क्या अंतिम पढ़ा गया अनुरोध छूट गया था।

चरण 2: रजिस्टरों और रैम की घोषणा करना

रजिस्टर की घोषणा करने से पहले, हम कैश और इंडेक्स का आकार निर्धारित करते हैं:

parameter size = 64; parameter index_size = 6;

अगला, हम एक सरणी घोषित करते हैं जिसमें हम जो डेटा लिखते और पढ़ते हैं वह संग्रहीत किया जाएगा:

reg [word_size-1:0] data_array [size-1:0];

हमें कैश में प्रत्येक आइटम के लिए वैधता बिट्स और टैग संग्रहीत करने की आवश्यकता है:

reg validity_array [size-1:0]; reg [word_size-index_size-1:0] tag_array [size-1:0]; reg [index_size-1:0] index_array [size-1:0];

रजिस्टर जिसमें इनपुट पता विभाजित किया जाएगा:

reg [word_size-index_size-1:0] tag; reg [index_size-1:0] index;

रजिस्टरों जो पिछली घड़ी पर इनपुट मानों को संग्रहीत करते हैं (इनपुट डेटा में परिवर्तनों को ट्रैक करने के लिए):

reg [word_size-1:0] data_reg; reg [word_size-1:0] addr_reg; reg wr_reg;

हमेशा ब्लॉक में गणना के बाद आउटपुट सिग्नल अपडेट करने के लिए रजिस्टर:

reg response_reg; reg is_missrate_reg; reg [word_size-1:0] out_reg;

RAM के लिए इनपुट मान:

reg [word_size-1:0] ram_data; reg [word_size-1:0] ram_addr; reg ram_wr;

RAM के लिए आउटपुट मान:

wire ram_response; wire [word_size-1:0] ram_out;

रैम मॉड्यूल की घोषणा करना और इनपुट और आउटपुट सिग्नल कनेक्ट करना:

ram ram( .data(ram_data), .addr(ram_addr), .wr(ram_wr), .clk(clk), .response(ram_response), .out(ram_out));

पंजीकरण आरंभ करें:

initial integer i initial begin data_reg = 0; addr_reg = 0; wr_reg = 0; for (i = 0; i < size; i=i+1) begin data_array[i] = 0; tag_array[i] = 0; validity_array[i] = 0; end end

चरण 3: ब्लॉक के हमेशा तर्क को लागू करना

शुरू करने के लिए, प्रत्येक घड़ी के लिए हमारे पास दो राज्य हैं - इनपुट डेटा बदल गया है या नहीं बदला गया है। इसके आधार पर, हमारी निम्नलिखित स्थिति है:

always @(posedge clk) begin if (data_reg != data || addr_reg != addr || wr_reg != wr) begin end // 1: else begin // 2: end end

ब्लॉक 1. यदि इनपुट डेटा को बदल दिया जाता है, तो पहली चीज जो हम करते हैं वह है 0 की तत्परता स्थिति को रीसेट करना:

response_reg = 0;

अगला, हम रजिस्टरों को अपडेट करते हैं जो पिछली घड़ी के इनपुट मूल्यों को संग्रहीत करते हैं:

data_reg = data; addr_reg = addr; wr_reg = wr;

हम टैग और इंडेक्स में इनपुट पते को तोड़ते हैं:

tag = addr >> index_size; index = addr;

टैग की गणना करने के लिए, दाईं ओर एक बिटवाइज़ शिफ्ट का उपयोग किया जाता है, इंडेक्स के लिए, यह केवल इसे असाइन करने के लिए पर्याप्त है, क्योंकि पते के अतिरिक्त बिट्स पर ध्यान नहीं दिया जाता है।

अगला कदम लेखन और पढ़ने के बीच चयन करना है:

if (wr) begin // data_array[index] = data; tag_array[index] = tag; validity_array[index] = 1; ram_data = data; ram_addr = addr; ram_wr = wr; end else begin // if ((validity_array[index]) && (tag == tag_array[index])) begin // is_missrate_reg = 0; out_reg = data_array[index]; response_reg = 1; end else begin // is_missrate_reg = 1; ram_data = data; ram_addr = addr; ram_wr = wr; end end

रिकॉर्डिंग के मामले में, हम शुरू में कैश में डेटा को संशोधित करते हैं, फिर रैम के लिए इनपुट डेटा को अपडेट करते हैं। पढ़ने के मामले में, हम कैश में इस तत्व की उपस्थिति की जांच करते हैं और यदि यह मौजूद है, तो इसे out_reg पर लिखें, अन्यथा हम रैम तक पहुंचते हैं।

ब्लॉक 2. यदि पिछली घड़ी को निष्पादित करने के बाद डेटा नहीं बदला गया है, तो हमारे पास निम्नलिखित कोड हैं:

if ((ram_response) && (!response_reg)) begin if (wr == 0) begin validity_array [index] = 1; data_array [index] = ram_out; tag_array[index] = tag; out_reg = ram_out; end response_reg = 1; end

यहां हम रैम के एक्सेस के पूरा होने की प्रतीक्षा करते हैं (यदि कोई एक्सेस नहीं था, ram_response 1 है), डेटा को अपडेट करें यदि कोई रीड कमांड था और कैशे की तत्परता को 1 पर सेट करें।

और अंतिम, आउटपुट मानों को अपडेट करें:

assign out = out_reg; assign is_missrate = is_missrate_reg; assign response = response_reg;