परिचय

एक बार मुझे सीएएम (साहचर्य स्मृति) के एक छोटे से ब्लॉक को लागू करने की आवश्यकता थी। यह पढ़ने के बाद कि Xilinx BRAM (स्टेटिक मेमोरी ब्लॉक्स) पर या SRL16 (16-बिट शिफ्ट रजिस्टर) पर कैसे काम करता है, मैं थोड़ा दुखी था, क्योंकि उनके कार्यान्वयन में काफी जगह थी। मैंने खुद इसे करने की कोशिश करने का फैसला किया। पहला विकल्प माथे का कार्यान्वयन था। आगे देखते हुए, यह लगभग मेरे पास आया और, ठीक है, डिजाइन के लिए लक्ष्य आवृत्ति केवल 125 मेगाहर्ट्ज थी।

आर्किटेक्चर

शुरू करने के लिए, समस्या के बयान पर विचार करें। इसलिए, हमें 8-64 बिट्स की एक शब्द चौड़ाई और 16-1024 शब्दों की गहराई के साथ एक छोटा सा सीएएम चाहिए। मुझे सीएएम में एक द्विआधारी खोज की आवश्यकता थी, लेकिन बाद में यह पता चला कि टीसीएएम (टर्नरी साहचर्य स्मृति) से यह संसाधनों के मामले में काफी सस्ता है और समय को थोड़ा प्रभावित करता है। निम्न आवृत्ति सीमा Kintex7 परिवार पर 125 मेगाहर्ट्ज है। चलो शुरू हो जाओ! हमारा CAM इन पंक्तियों से बना होगा, जिनमें से प्रत्येक एक पते के अनुरूप होगा और एक शब्द को संग्रहीत करेगा:

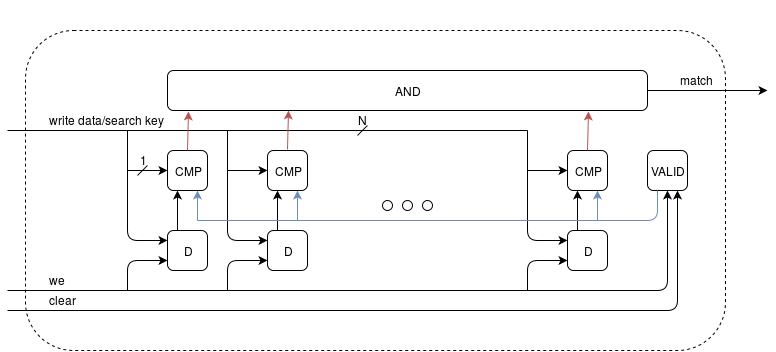

चित्रा 1. सीएएम की एक पंक्ति की संरचना

अंजीर में 1, डी डेटा भंडारण के लिए एक नियमित डी-ट्रिगर है; लाइन में इन ट्रिगर्स की संख्या सीएएम में इनपुट डेटा शब्द की चौड़ाई से मेल खाती है। वैलिड - डी-ट्रिगर, जो '1' को स्टोर करता है यदि लाइन में डेटा प्रासंगिक है। CMP एक तुलनित्र है जो वैलिड = '1' की तुलना में संबंधित खोज कुंजी बस बिट के मूल्य की तुलना करता है। डेटा लिखें - संबंधित डी ( एन - शब्द चौड़ाई सीएएम) से जुड़े बिटवाइज़ लिखने के लिए डेटा बस, हम - झंडा लिखते हैं, स्पष्ट - रीसेट वैलिड (डेटा लाइन का अमान्य)। और - तार्किक और तुलना के एन आउटपुट से, मैच - झंडा '1' में बदल रहा है अगर इस लाइन में खोज सफल है।

तो, हमारे पास एक पंक्ति है जिसमें हम खोज कर सकते हैं। अब उन्हें संयोजित करें:

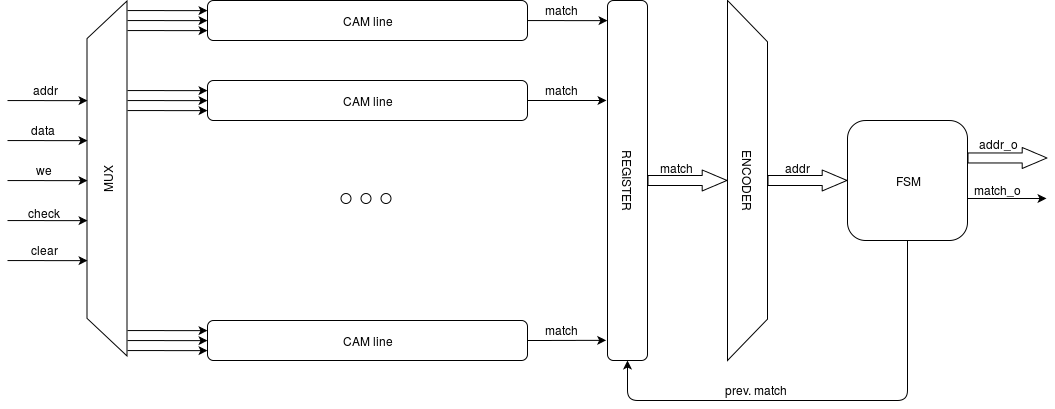

चित्रा 2. सीएएम संरचना

अंजीर। 2 में, CAM_line अंजीर से ही CAM लाइन है। MUX इनपुट एड्रेस मल्टीप्लेक्सर है, MATCH REGISTER एक रजिस्टर है जो फ्लैग वैल्यू को स्टोर करता है, ENCODER एक डिकोडर है जो मैच बस को सबसे कम मैच एड्रेस से मिलाता है। एफएसएम एक नियंत्रित परिमित राज्य मशीन है, जो प्रचलित है। मैच भेजे गए पते के समान बिट से मैचेस को हटाता है ताकि ENCODER अगले पाए गए पते पर स्विच हो जाए। हमारे सीएएम का इंटरफ़ेस निम्नानुसार होगा:

तालिका 1. सीएएम इंटरफ़ेस

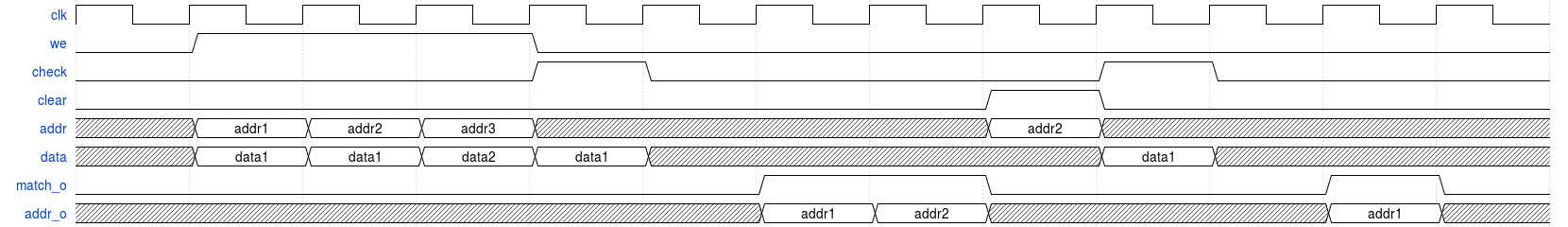

अंजीर में नीचे 3 इस इंटरफ़ेस के संचालन का एक समय आरेख है, जो पहले CAM में तीन शब्दों की रिकॉर्डिंग दिखाता है, फिर एक सफल खोज, मिटाता है और फिर से खोज करता है:

चित्रा 3. सीएएम को इंटरफ़ेस का समय आरेख

इसलिए, हमारे पास सीएएम का विवरण है, चलो संश्लेषण पर चलते हैं।

संश्लेषण

हम XilinP IS51 में प्राप्त परिणामों के साथ तुलना करने के लिए Xilinx ISE में संश्लेषित करेंगे।

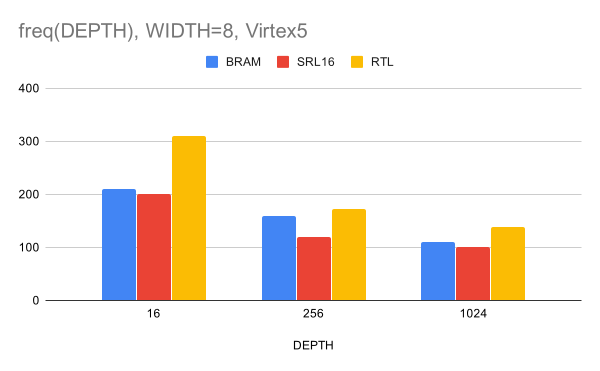

चित्रा 4. 8-बिट डेटा बस चौड़ाई के लिए सीएएम गहराई पर XST (ISE के हिस्से के रूप में सिंथेसाइज़र) के बाद आवृत्ति निर्भरता

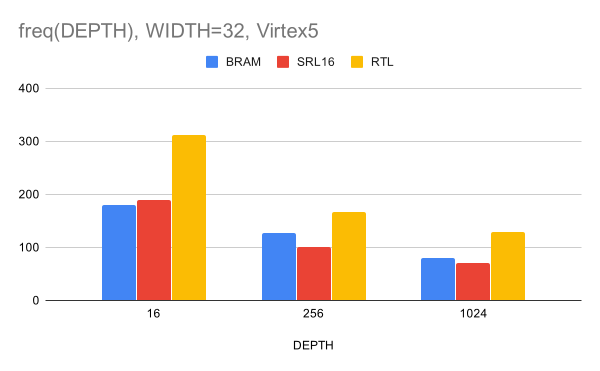

चित्रा 5. 32-बिट डेटा बस चौड़ाई के लिए XST बनाम सीएएम गहराई के बाद आवृत्ति

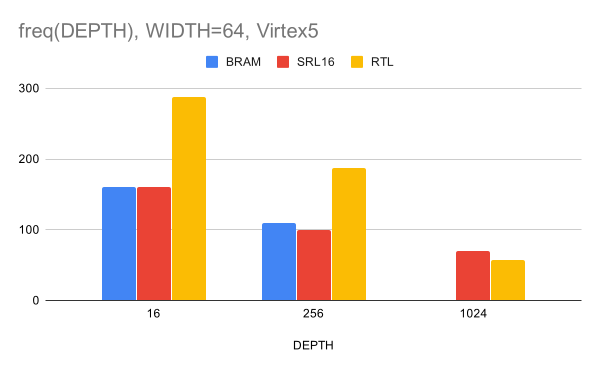

चित्र 6. 64-बिट डेटा बस चौड़ाई के लिए XST बनाम CAM गहराई के बाद आवृत्ति

अंजीर 6 में, वीरटेक्स 5 के लिए कोई डेटा नहीं है, क्योंकि इस आकार का सीएएम मौजूदा ब्रैम में फिट नहीं था। हम यह भी ध्यान देते हैं कि 64 बिट्स की चौड़ाई और 1024 की गहराई के लिए, हमारा परिणाम SRL16 पर कार्यान्वयन से थोड़ा खराब था। अब XC7K325T के लिए विवाडो संश्लेषण पर चलते हैं । परिणाम इस प्रकार हैं:

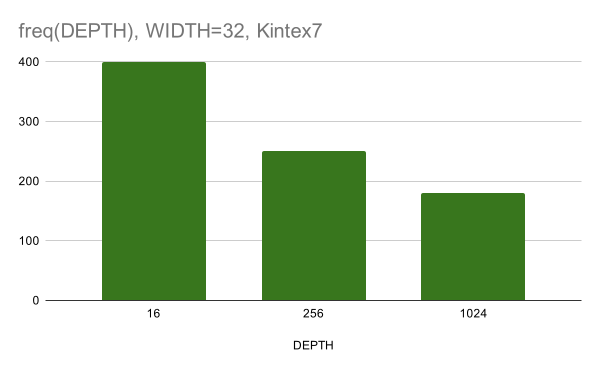

32 बिट डेटा बस चौड़ाई के लिए CAM गहराई पर PnR (चिप और सिग्नल ट्रेसिंग पर ब्लॉक की नियुक्ति) के बाद चित्रा 7. आवृत्ति निर्भरता

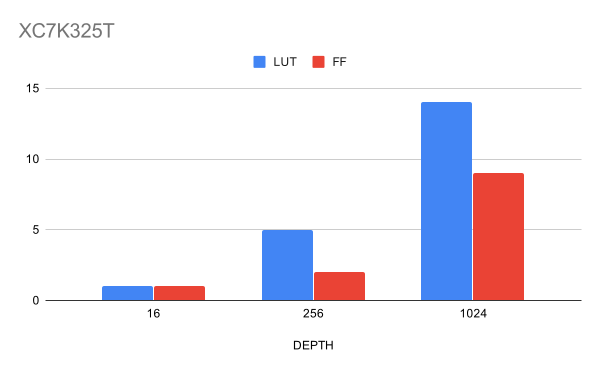

चित्रा 8.% में 32 बिट्स की डेटा चौड़ाई के लिए विभिन्न सीएएम गहराई के लिए संसाधनों का उपयोग

यह ध्यान रखना महत्वपूर्ण है कि विवाडो पर परिणाम PnR के बाद प्राप्त किए गए थे, जिसका अर्थ है कि डिज़ाइन में ट्रेसिंग के साथ कोई कठिनाई नहीं है।

TCAM

जैसा कि ऊपर उल्लेख किया गया है, सीएएम टीसीएएम से इस दृष्टिकोण के साथ मिलना कोई विशेष समस्या नहीं थी। यह डेटा बिट्स के लिए एक मास्किंग बस को जोड़ने के लिए और तुलनाकर्ताओं में बिट द्वारा इसे वितरित करने के लिए पर्याप्त है, ताकि जब कुंजी के साथ डेटा की तुलना करते हैं, तो वे इसके मूल्य को ध्यान में रखते हैं। इस तरह के परिवर्तन से आवृत्ति में गिरावट नहीं हुई या खपत संसाधनों में गंभीर वृद्धि हुई, इसलिए हमें मुफ्त में टीसीएएम मिला।

निष्कर्ष

इसलिए, हम कार्य पूरा करने में सक्षम थे। परिणामस्वरूप डिजाइन 7 वें Xilinx FPGA परिवार को लक्ष्य 125 मेगाहर्ट्ज से ऊपर की आवृत्ति के साथ पर्याप्त रूप से बड़े सीएएम प्राप्त करने की अनुमति देता है। XAPP1151 के साथ तुलना का परिणाम मेरे लिए अप्रत्याशित निकला, मैंने माना कि BRAM पर कार्यान्वयन, हालांकि यह संसाधनों के मामले में बहुत महंगा है, आवृत्ति में ललाट कार्यान्वयन से आगे निकल जाएगा। हालाँकि, जीत इतनी जल्दी नहीं मनाते हैं, यह दस्तावेज़ Xilinx CAM IP कोर का वर्णन करता है, जो उदाहरण के लिए, BRK पर आधारित 32K कोशिकाओं की गहराई और 155 MHz की आवृत्ति के साथ CAM प्राप्त करने की अनुमति देता है। यह परिणाम संभवतः लेख में प्रस्तावित संस्करण में प्राप्त किया जा सकता है, या तो पाइपलाइन के चरणों को जोड़कर, या छोटे से बड़े सीएएम को इकट्ठा करके, लेकिन मैं तुरंत भविष्यवाणी नहीं कर सकता कि यह चिप में फिट होगा या नहीं। भविष्य में मैं BRAM पर कुछ समान लागू करने की कोशिश करूंगा, लेकिन अभी के लिए, आपका ध्यान देने के लिए धन्यवाद।