सभी को शुभ दिन। इस लेख में हम FMC (लचीले मेमोरी कंट्रोलर) मॉड्यूल का उपयोग करके 16-बिट 8080 समानांतर इंटरफ़ेस के माध्यम से STM32F429L डिस्कवरी बोर्ड में TFT डिस्प्ले ER-TFT101-1 (10 इंच, RA8876 ड्राइवर) के कनेक्शन का विश्लेषण करेंगे।

प्रदर्शन विधानसभा के बारे में

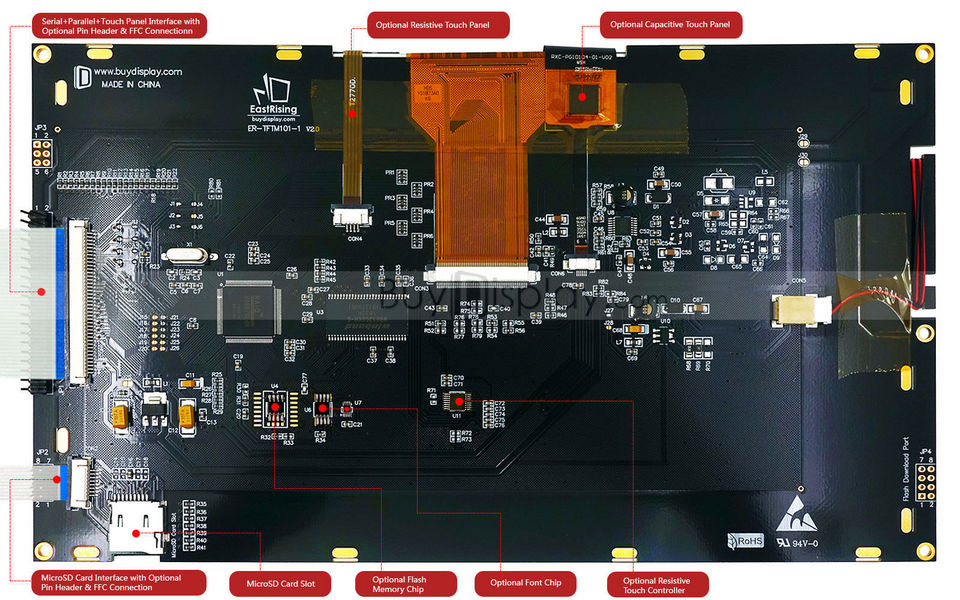

EastRising का ER-TFT101-1 एक 10-इंच TFT मैट्रिक्स की एक विधानसभा है जिसमें 1024x600 का रिज़ॉल्यूशन और RA8876 ड्राइवर वाला बोर्ड है। ड्राइवर के साथ बोर्ड में सभी आवश्यक बिजली की आपूर्ति है, एसडी-रैम मेमोरी 16 मेगाबाइट (16-बिट बस, 166 मेगाहर्ट्ज अधिकतम आवृत्ति, 64 एमबी अधिकतम क्षमता) है, एक मानक माइक्रोएसडी कार्ड स्लॉट है। EEPROM के तहत बाहरी फोंट के साथ खाली पैरों के निशान हैं और उन्हें प्रोग्रामिंग के लिए आउटपुट कनेक्टर्स के साथ छवियों के लिए फ्लैश मेमोरी के तहत। इसके अलावा, एक प्रतिरोधक या कैपेसिटिव टच पैनल विधानसभा पर वैकल्पिक रूप से स्थापित किया जा सकता है।

बोर्ड में टॉप-एंड RAOO RA8876 ड्राइवर है, जिसमें अधिकतम 120 मेगाहर्ट्ज की ऑपरेटिंग आवृत्ति है, जो कि अगर वांछित है, तो खुद एक नियंत्रण माइक्रोकंट्रोलर के रूप में काम कर सकता है। आप एक छोटा प्रोग्राम (केवल 12 निर्देश) लिख सकते हैं और इसे बाहरी फ्लैश मेमोरी में डाल सकते हैं। जब प्रदर्शन शुरू होता है, तो यह कार्यक्रम पहली जगह में चलना शुरू कर देगा, बाहरी इंटरफ़ेस के माध्यम से सभी नियंत्रण विकल्पों को अनिवार्य रूप से दोहराएगा।

RA8876 की अपनी रैम नहीं है और इसलिए यह बाहरी एसडी-रैम मेमोरी का उपयोग करता है। यह डीएमए का उपयोग करके फ्लैश मेमोरी से छवियों को पढ़ सकता है और इसे अपने फ्रेम बफर में लोड कर सकता है और इसका बहुत ही लचीला कॉन्फ़िगरेशन है। ड्राइवर मानक 18-बिट वाइड आरजीबी इंटरफ़ेस का उपयोग करके मैट्रिक्स से जुड़ा हुआ है। केवल 6 बिट प्रति रेड चैनल, 6 बिट प्रति ग्रीन और 6 बिट ब्लू चैनल का उपयोग किया जाता है। प्रत्येक चैनल के निचले दो बिट्स का उपयोग नहीं किया जाता है, जो सिद्धांत में 262,144 रंग देता है।

RA8876 का DMA मॉड्यूल STM के DMA2D से काफी मिलता-जुलता है - यह रंग रूपांतरण, पारदर्शिता और अन्य चिप्स के साथ एक स्थान से दूसरे स्थान पर मेमोरी के आयताकार वर्गों को कॉपी कर सकता है।

RA8876 में उनके डिस्प्ले (रोटेशन, स्केल आदि) के लिए लचीली सेटिंग्स के साथ अंग्रेजी और चीनी फोंट (8x16,12x24,16x32 पिक्सल) भी हैं और हार्डवेयर बटन के लिए एक अलग मैट्रिक्स इंटरफेस (5 x 5) (स्टैंड-अलोन के लिए) न केवल) सेटिंग्स का एक गुच्छा के साथ, जैसे कि लंबे और छोटे प्रेस, एक बटन दबाकर और एक ही समय में कई बटन दबाकर प्रदर्शन को जगाएं।

किसी भी पॉप-अप विंडो और मेनू को प्रदर्शित करने के लिए एक तस्वीर-इन-पिक्चर फ़ंक्शन (पारदर्शिता समर्थन के बिना) है।

चालक स्वयं ग्राफिक प्रिमिटिव्स को आकर्षित कर सकता है, जैसे कि वर्ग, वृत्त, वक्र, अंडाकार, त्रिकोण, गोल वर्ग, साथ और बिना भरें। वैसे, RA8875 में और RA8876 में त्रिकोण को भरने के लिए एक छोटा बग है, और प्रत्येक ड्राइवर का अपना है। लेकिन उच्च घंटी टॉवर से RAIO ने इसके बारे में कोई शाप नहीं दिया ... मैंने उन्हें किसी तरह एक पत्र लिखने की कोशिश की, इसलिए उन्होंने जवाब भी नहीं दिया। इस तरह की आदिम रेखाएं खींचना आपको एक धीमी माइक्रोकंट्रोलर के साथ भी सुंदर ग्राफिक्स बनाने की अनुमति देता है।

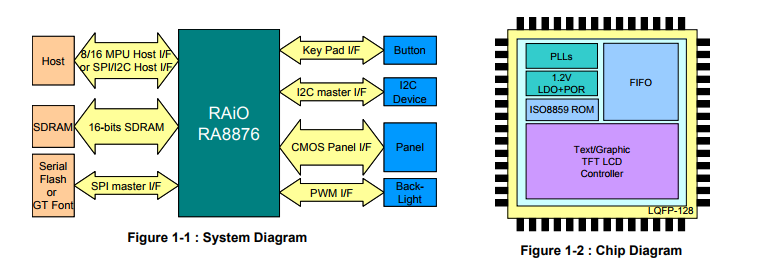

बाहरी दुनिया के साथ, RA8876 8080/6800 8/16 बिट, 3/4 तार SPI और I2C इंटरफेस के माध्यम से संचार करता है। इसके अलावा, ड्राइवर चिप स्वयं एक SPI और I2C मास्टर के रूप में कार्य कर सकता है। RA8876 में, दो PWM आउटपुट हैं जिनका उपयोग बैकलाइट के लचीले नियंत्रण के लिए किया जा सकता है। अधिकतम SPI सीएलके आवृत्ति 120 मेगाहर्ट्ज के चालक आवृत्ति के साथ 66 मेगाहर्ट्ज पर घोषित की जाती है, जो सिद्धांत रूप में एक पूर्ण स्क्रीन अपडेट के 6 फ्रेम प्रति सेकंड (1024 x 600 x 16 बिट पर) देती है। इस कनेक्शन का परीक्षण मेरे द्वारा किया गया था और यह दिखाया गया था कि अगर हमें वीडियो को स्क्रीन पर प्रदर्शित नहीं करना है तो उसे जीवन का अधिकार है।

हमारे मामले में, हम एफएमसी मॉड्यूल (लचीली मेमोरी कंट्रोलर) के माध्यम से 80 बिट प्रोटोकॉल की मदद से 16 बिट्स की चौड़ाई के साथ STM32F429ZIT6 के साथ डिस्प्ले को कनेक्ट करेंगे, जो हमें माइक्रोकंट्रोलर पर अधिक स्क्रीन फिलिंग स्पीड और कम लोड प्राप्त करने की अनुमति देगा।

8080 पिन और एफएमसी का विन्यास

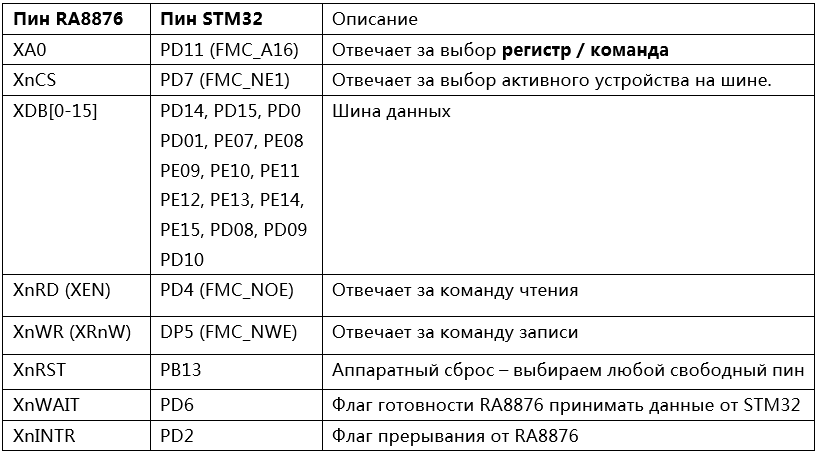

हम डिस्प्ले पर डेटाशीट में 8080 के लिए कनेक्शन आरेख देखेंगे:

हम क्यूएमएमएक्स में एसटीएम 32 से जुड़ने के लिए आवश्यक पिनों को देखते हैं। हम बैंक # 1 (NOR Flash / PSRAM / SRAM / ROM / LDC 1) में रुचि रखते हैं।

डेटा पत्रक में XnWAIT के बारे में, आप निम्नलिखित पढ़ सकते हैं:

निरंतर डेटा लिखने की गति प्रदर्शन अपडेट की गति निर्धारित करती है। यदि उपयोगकर्ता प्रतीक्षा प्रणाली सम्मिलित करने के लिए XnWait को अपनाए बिना चक्र-से-चक्र अंतराल 5 सिस्टम घड़ी की अवधि से बड़ा होना चाहिए। यदि विनिर्देशन xnwait तंत्र का उपयोग नहीं करता है, तो विनिर्देशन डेटा खो जाने या कार्य विफल हो सकता है।

वस्तुतः, 8080 प्रोटोकॉल के ऑपरेटिंग चक्रों के बीच, 5 RA8876 सिस्टम श्रेडों की देरी को सम्मिलित किया जाना चाहिए यदि उपयोगकर्ता RA8876 की रिहाई के लिए प्रतीक्षा करने के लिए XnWAIT तंत्र का उपयोग नहीं करता है। हम इस पिन का एक बार फिर से उपयोग करेंगे व्यवहार में, मैंने पांच चक्रों की देरी डालने की कोशिश की, और यह काम नहीं किया।

FMC इकाई के लिए एक पूर्ण पता बस के बजाय, हम केवल एक पिन A16 का उपयोग करते हैं।

- हम एक वैकल्पिक फ़ंक्शन # 12 के रूप में डेटा पिन (D0 - D15) को कॉन्फ़िगर करते हैं, जैसे कि पुश पूल, अधिकतम गति और बिना किसी भी निलंबित।

- पिंस XnWAIT, XnWR, XnRD, XA0 और XnCS को वैकल्पिक फ़ंक्शन # 12 के रूप में कॉन्फ़िगर किया गया है, जैसे पुश-पुल से प्लस (PULL UP) तक।

- हम एक निलंबित GPIO के रूप में एक नियमित GPIO के रूप में कॉन्फ़िगर करते हैं (यह स्वयं बोर्ड पर है)।

- XnINTR एक GPIO के रूप में इनपुट के साथ एक लिफ्ट से प्लस तक कॉन्फ़िगर करने योग्य है।

मैंने इसे PWM के माध्यम से नियंत्रित किए बिना बैकलाइट को 100% से जोड़ा। ऐसा करने के लिए, डिस्प्ले असेंबली कनेक्टर पर पिन # 14 VDD से जुड़ा हुआ है।

मैं पिन के लिए कॉन्फ़िगरेशन कोड प्रदान नहीं करता, क्योंकि मैं अपने स्वयं के कॉन्फ़िगरेशन पुस्तकालयों का उपयोग करता हूं, और GPIO कॉन्फ़िगरेशन पहले ही हब और अन्य स्रोतों पर एक सौ बार चबाया गया है।

इनिशियलाइज़ेशन लाइब्रेरी यहाँ है ।

एफएमसी सेटिंग्स

प्रत्येक बैंक के लिए तीन बैंक FMC मॉड्यूल (NOR Flash / PSRAM / SRAM / ROM / LDC 1) के बैंकों की स्थापना के लिए जिम्मेदार हैं। ये FMC_BCRx, FMC_BTRx और FMC_BWTRx हैं। STM32F429 MK परिभाषित में, FMC_BCRx और FMC_BTRx रजिस्टर को आठ तत्वों के साथ FMC_BTCR नामक एक सामान्य सरणी में संयोजित किया जाता है, जहाँ शून्य तत्व FMC_BCR1 है, पहला तत्व FMC_BCR1 है, दूसरा तत्व FMC_BCR2 है, और इसी तरह। FMC_BWTRx को सात तत्वों के साथ FMC_BWTR सरणी में संयोजित किया गया है, हालांकि चार होने चाहिए। मुझसे मत पूछो क्यों ...

FMC_BCRx में मूलभूत सेटिंग्स होती हैं, FMC_BTRx में सामान्य समयावधि होती है, और यदि डिवाइस को इसकी आवश्यकता होती है, तो FMC_BWTRx में पढ़ने के लिए अलग-अलग समय होते हैं।

STM32F429 और RA8876 की बातचीत के लिए समय आरेख और समय।

विन्यास में आसानी के लिए, हम 8080 प्रोटोकॉल समय को स्थिरांक में सम्मिलित करेंगे। मैंने खुद को आनुभविक रूप से समय के लिए चुना, मूल्य का थोड़ा सा कम करते हुए, क्योंकि डेटशीट के साथ टाइमिंग टेबल एक वैक्यूम में एक गोलाकार घोड़े की तरह है।

unsigned long ADDSET = 0; unsigned long ADDHLD = 1; unsigned long DATAST = 5; unsigned long BUSTURN = 0; unsigned long CLKDIV = 1; unsigned long DATLAT = 0; unsigned long ACCMOD = 0; RCC->AHB3ENR |= RCC_AHB3ENR_FMCEN;

रीसेट के बाद FMC_BTCRx रजिस्टर का मूल्य 0x0FFF FFFF है, अर्थात अधिकतम समय निर्धारित है। यदि आपके पास एक नया प्रदर्शन या मेमोरी है, तो समय कम करें और चलाने का प्रयास करें।

प्रारंभिक प्रदर्शन

प्रदर्शन के साथ काम करना स्मृति के कुछ क्षेत्रों को पढ़ने या लिखने के लिए नीचे आता है। एफएमसी बाकी कामों का ध्यान रखती है। कार्य को सरल बनाने के लिए, हम दो परिभाषित करते हैं:

#define LCD_DATA 0x60020000 #define LCD_REG 0x60000000

और अब हम निम्न-स्तरीय कार्यों का वर्णन करते हैं:

void LCD_CmdWrite (unsigned char cmd) { *(unsigned short *)(LCD_REG) = cmd; }; void LCD_DataWrite (unsigned short data) { *(unsigned short *)(LCD_DATA)= data; }; unsigned char LCD_StatusRead(void) { unsigned short data = *(unsigned short *)(LCD_REG); return data; }; unsigned char LCD_DataRead(void) { unsigned short data = * (unsigned short *)(LCD_DATA); return (unsigned char)data; }; void LCD_RegisterWrite(unsigned char cmd, unsigned char data) { *(unsigned short *)(LCD_REG) = cmd; *(unsigned short *)(LCD_DATA) = data; }; unsigned char LCD_RegisterRead (unsigned char cmd) { volatile unsigned char data = 0; LCD_CmdWrite (cmd); data = LCD_DataRead (); return data; };

इसके अलावा, प्रदर्शन आरंभीकरण स्वयं कार्य करता है। कोड डिस्प्ले प्रोवाइडर से लिया गया है और आपकी आवश्यकताओं के अनुसार इसे थोड़ा बदल दिया गया है। उपप्रकार एक बड़ी राशि पर कब्जा कर लेते हैं और इस लेख में मैं उन्हें नहीं दूंगा।

ड्राइवर को जीथब पर लिंक करें void RA8876_Init(void) { RA8876_PLL_Init ();

फ़्रेमबफ़र और सक्रिय क्षेत्र के बारे में थोड़ा अधिक। इन दो सेटिंग्स के लिए, हम निम्नलिखित परिभाषित करते हैं:

#define PAGE0_START_ADDR 0 #define PAGE1_START_ADDR (1024 * 600 * 2 * 1) #define PAGE2_START_ADDR (1024 * 600 * 2 * 2) #define PAGE3_START_ADDR (1024 * 600 * 2 * 3) #define PAGE4_START_ADDR (1024 * 600 * 2 * 4) #define PAGE5_START_ADDR (1024 * 600 * 2 * 5) #define PAGE6_START_ADDR (1024 * 600 * 2 * 6) #define PAGE7_START_ADDR (1024 * 600 * 2 * 7) #define PAGE8_START_ADDR (1024 * 600 * 2 * 8) #define PAGE9_START_ADDR (1024 * 600 * 2 * 9) #define PAGE10_START_ADDR (1024 * 600 * 2 * 10) #define PAGE11_START_ADDR (1024 * 600 * 2 * 11) #define PAGE12_START_ADDR (1024 * 600 * 2 * 12)

प्रत्येक पृष्ठ (PAGEx_START_ADDR) SDRAM में शुरुआती पता है। 16 मेगाबाइट मेमोरी में, हम 13 पूर्ण परतों को 1228800 बाइट्स (1024 * 600 * 2) आकार में रख सकते हैं।

Frame_Buffer_Start_Address फ़ंक्शन फ़्रेमबफ़र (वर्तमान में प्रदर्शित किया जा रहा है) के लिए प्रारंभिक मेमोरी क्षेत्र सेट करता है।

Canvas_Window_Start_Address फ़ंक्शन कैनवास के लिए प्रारंभिक मेमोरी क्षेत्र सेट करता है। इसके अलावा, कैनवास फ्रेम बफ़र से बड़ा हो सकता है, इसलिए आप स्क्रीन पर छवि को स्क्रॉल कर सकते हैं। उदाहरण के लिए, एक प्लेटफ़ॉर्म गेम के लिए, आप 13312 x 600 पिक्सेल को मापने वाला एक लंबा कैनवास बना सकते हैं और फिर इसे क्षैतिज रूप से स्क्रॉल कर सकते हैं, जिससे फ्रेमबफ़र को क्षैतिज रूप से पार कर सकते हैं।

यदि आप STM32 से LTDM के साथ ग्राफिक्स आउटपुट की तुलना करते हैं, तो यहां सब कुछ इतना रसीला नहीं है। इसी समय, चालक स्वयं इस प्रक्रिया में आपकी भागीदारी की आवश्यकता के बिना, केवल एक अंतिम (बफर) परत और LTDC को तुरंत दो को प्रदर्शित कर सकता है।

आदिम आरेखण

पूर्व-निर्मित सुविधाओं के साथ डिस्प्ले प्रदाता से कोड:

void Start_Line (void); void Start_Triangle (void); void Start_Triangle_Fill (void); void Line_Start_XY (unsigned short WX, unsigned short HY); void Line_End_XY (unsigned short WX, unsigned short HY); void Triangle_Point1_XY (unsigned short WX, unsigned short HY); void Triangle_Point2_XY (unsigned short WX, unsigned short HY); void Triangle_Point3_XY (unsigned short WX, unsigned short HY); void Square_Start_XY (unsigned short WX, unsigned short HY); void Square_End_XY (unsigned short WX, unsigned short HY); void Start_Circle_or_Ellipse (void); void Start_Circle_or_Ellipse_Fill (void); void Start_Left_Down_Curve (void); void Start_Left_Up_Curve (void); void Start_Right_Up_Curve (void); void Start_Right_Down_Curve (void); void Start_Left_Down_Curve_Fill (void); void Start_Left_Up_Curve_Fill (void); void Start_Right_Up_Curve_Fill (void); void Start_Right_Down_Curve_Fill (void); void Start_Square (void); void Start_Square_Fill (void); void Start_Circle_Square (void); void Start_Circle_Square_Fill (void); void Circle_Center_XY (unsigned short WX, unsigned short HY); void Ellipse_Center_XY (unsigned short WX, unsigned short HY); void Circle_Radius_R (unsigned short WX); void Ellipse_Radius_RxRy (unsigned short WX, unsigned short HY); void Circle_Square_Radius_RxRy (unsigned short WX, unsigned short HY);

उदाहरण के लिए, एक भरे हुए त्रिभुज को खींचने के लिए, हम तीन बिंदुएँ निर्धारित करते हैं: Triangle_Point1_XY, Triangle_Point2_XY, Triangle_Point2_XY और Start_Triangle_Fill फ़ंक्शन चलाएँ।

डीएमए के साथ काम करें

सुविधा के लिए, मैंने अपने कार्य को एक पारित पैरामीटर के रूप में संरचना के साथ लिखा:

struct GFX_BTE_options { unsigned long layer_s0_addr;

ऑपरेटिंग कोड का विवरण (संचालन कोड):0000: एमके का उपयोग करके आरओपी के साथ मेमोरी में लिखें।

0001: एमके का उपयोग करके ROP के बिना मेमोरी पढ़ें।

0010: ROP का उपयोग करके आगे की दिशा में एक मेमोरी ब्लॉक की प्रतिलिपि बनाएँ।

0011: ROP का उपयोग करके एक मेमोरी ब्लॉक को रिवर्स दिशा में कॉपी करना।

0100: एमके का उपयोग करके ROP के बिना मेमोरी (पारदर्शिता के साथ) लिखें।

0101: ROP के बिना आगे की दिशा में मेमोरी ब्लॉक (पारदर्शिता के साथ) को कॉपी (स्थानांतरित) करें।

0110: ROP का उपयोग करके एक पैटर्न भरें।

0111: टेम्पलेट को क्रोमेकी से भरें।

1000: रंग विस्तार

1001: पारदर्शिता के साथ बढ़ाया रंग

1010: अल्फा ब्लेंडिंग के साथ मेमोरी ब्लॉक को आगे बढ़ाना

1011: एमके के उपयोग से अल्फा सम्मिश्रण के साथ मेमोरी लिखना।

1100: एक ठोस रंग के साथ स्मृति क्षेत्र को भरता है।

1101: आरक्षित

1110: आरक्षित

1111: आरक्षित

रेखापुंज कोड (आरओपी कोड) का विवरण:0000b: 0 (काला)

0001b: ~ S0 S ~ S1 या ~ (S0 + S1)

0010 बी: ~ एस 0 1 एस 1

0011 बी: ~ एस 0

0100b: S0 0 ~ S1

0101 बी: ~ एस 1

0110b: S0 ^ S1

0111b: ~ S0 + ~ S1 या ~ (S0 S S1)

1000b: S0 ・ S1

1001b: ~ (S0 ^ S1)

1010 बी: एस 1

1011 बी: ~ एस 0 + एस 1

1100 बी: एस 0

११०१ बी: एस ० + ~ एस १

1110b: S0 + S1

1111 बी: 1 (सफेद)

S0 शून्य परत है, S1 पहली परत है। उनके बीच की बातचीत अंकगणित और बिट संचालन का उपयोग करके होती है।

इनलाइन फ़ॉन्ट आउटपुट

void GFX_Show_String_TMODE (short x, short y, char *ptr, unsigned short charColor, unsigned short bkColor) { Foreground_color_65k (charColor); Background_color_65k (bkColor); CGROM_Select_Internal_CGROM (); Font_Select_12x24_24x24 (); Text_Mode (); Goto_Text_XY (x, y); LCD_CmdWrite (0x04); while (*ptr != '\0') { LCD_DataWrite (*ptr); Check_Mem_WR_FIFO_not_Full (); ++ptr; } Check_2D_Busy (); Graphic_Mode ();

ड्राइवर का पूर्ण संस्करण लिंक पर जीथब पर पाया जा सकता हैआप सभी को पढ़ने के लिए धन्यवाद!