T1 - Komputer DIY 8-bit diskrit

Selalu ada banyak yang "buatan sendiri". Dengan munculnya jaringan, pecinta melakukan sesuatu dengan tangan mereka sendiri segera mengatur diri mereka sendiri, dan menciptakan banyak semua jenis komunitas, forum dan tempat-tempat lain di mana Anda dapat mengobrol dengan jenis Anda sendiri. Berkat ini, karya-karya menarik secara teratur muncul di Internet, beberapa di antaranya patut diperhatikan.Salah satu karya tersebut adalah, khususnya, proyek untuk membuat komputer 8-bit yang terpisah. Penulis proyek ini adalah Andrew Starr , dan proyek itu sendiri ada di sini di halaman ini . Seperti apa proyek itu?Menurut penulis, ini sebagian adalah perakitan kinetik, sebagian merupakan penghargaan untuk pencapaian ilmu pengetahuan dan teknologi, dan pencapaian tahun-tahun sebelumnya. Sebagian, ini adalah proyek pendidikan.Untuk membuat sistem ini, penulis menggunakan elemen-elemen berikut:

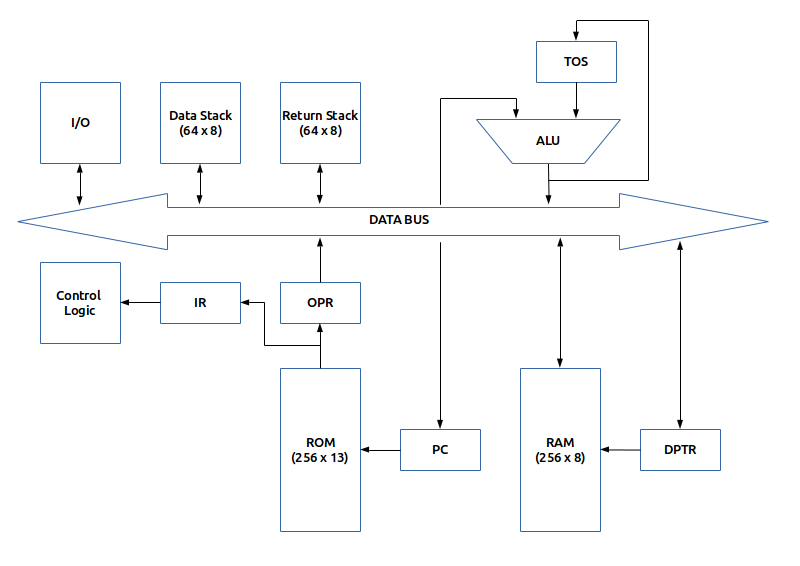

Selalu ada banyak yang "buatan sendiri". Dengan munculnya jaringan, pecinta melakukan sesuatu dengan tangan mereka sendiri segera mengatur diri mereka sendiri, dan menciptakan banyak semua jenis komunitas, forum dan tempat-tempat lain di mana Anda dapat mengobrol dengan jenis Anda sendiri. Berkat ini, karya-karya menarik secara teratur muncul di Internet, beberapa di antaranya patut diperhatikan.Salah satu karya tersebut adalah, khususnya, proyek untuk membuat komputer 8-bit yang terpisah. Penulis proyek ini adalah Andrew Starr , dan proyek itu sendiri ada di sini di halaman ini . Seperti apa proyek itu?Menurut penulis, ini sebagian adalah perakitan kinetik, sebagian merupakan penghargaan untuk pencapaian ilmu pengetahuan dan teknologi, dan pencapaian tahun-tahun sebelumnya. Sebagian, ini adalah proyek pendidikan.Untuk membuat sistem ini, penulis menggunakan elemen-elemen berikut:- Bus 8-bit

- 2 * 64 bit stack (data, return);

- Arsitektur Harvard : memori utama 256 byte dan memori program 256 kata;

- Kata perintah perangkat lunak 13-bit: 5 bit per opcode, operan 8 bit;

- Semua elemen memori dibuat menggunakan inti ferit;

- Memori program dibuat menggunakan transformator ferit;

- Elemen logika terbuat dari elemen diskrit dalam bentuk modul plug-in;

- Frekuensi jam target adalah 1 MHz.

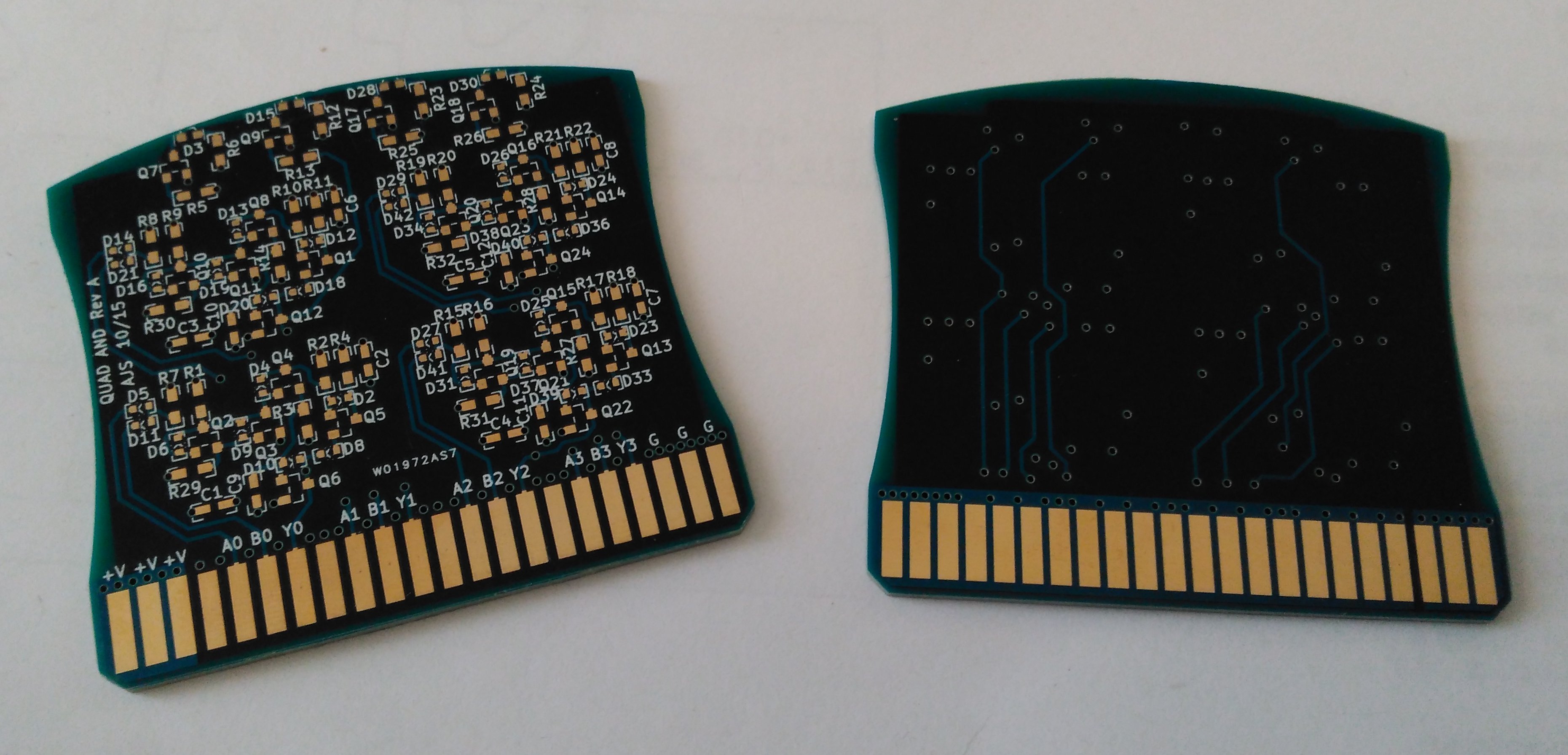

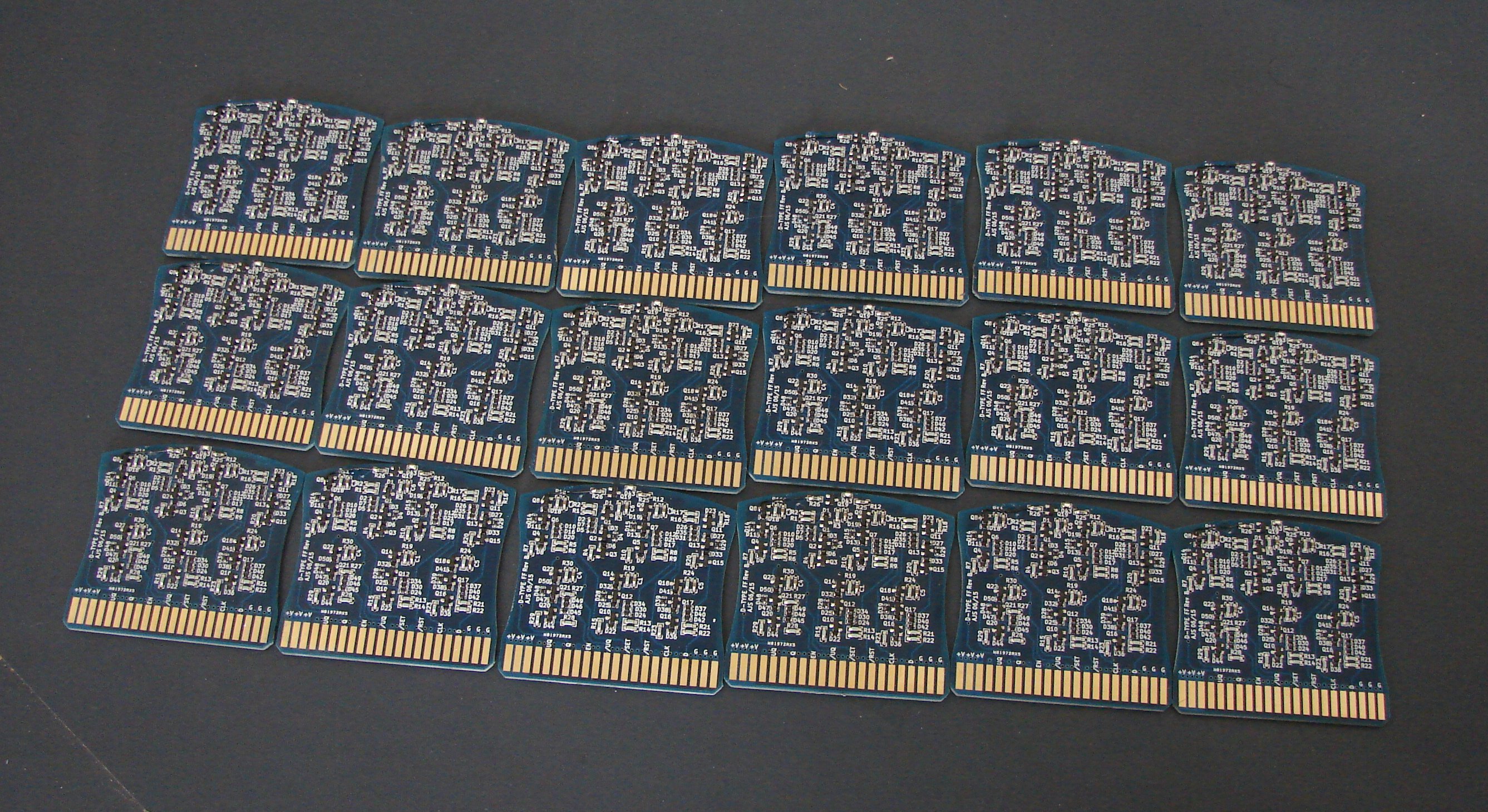

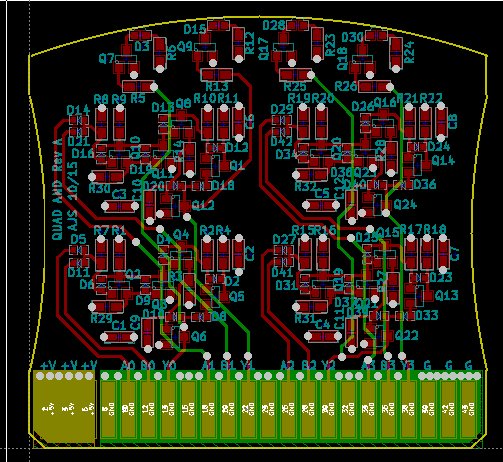

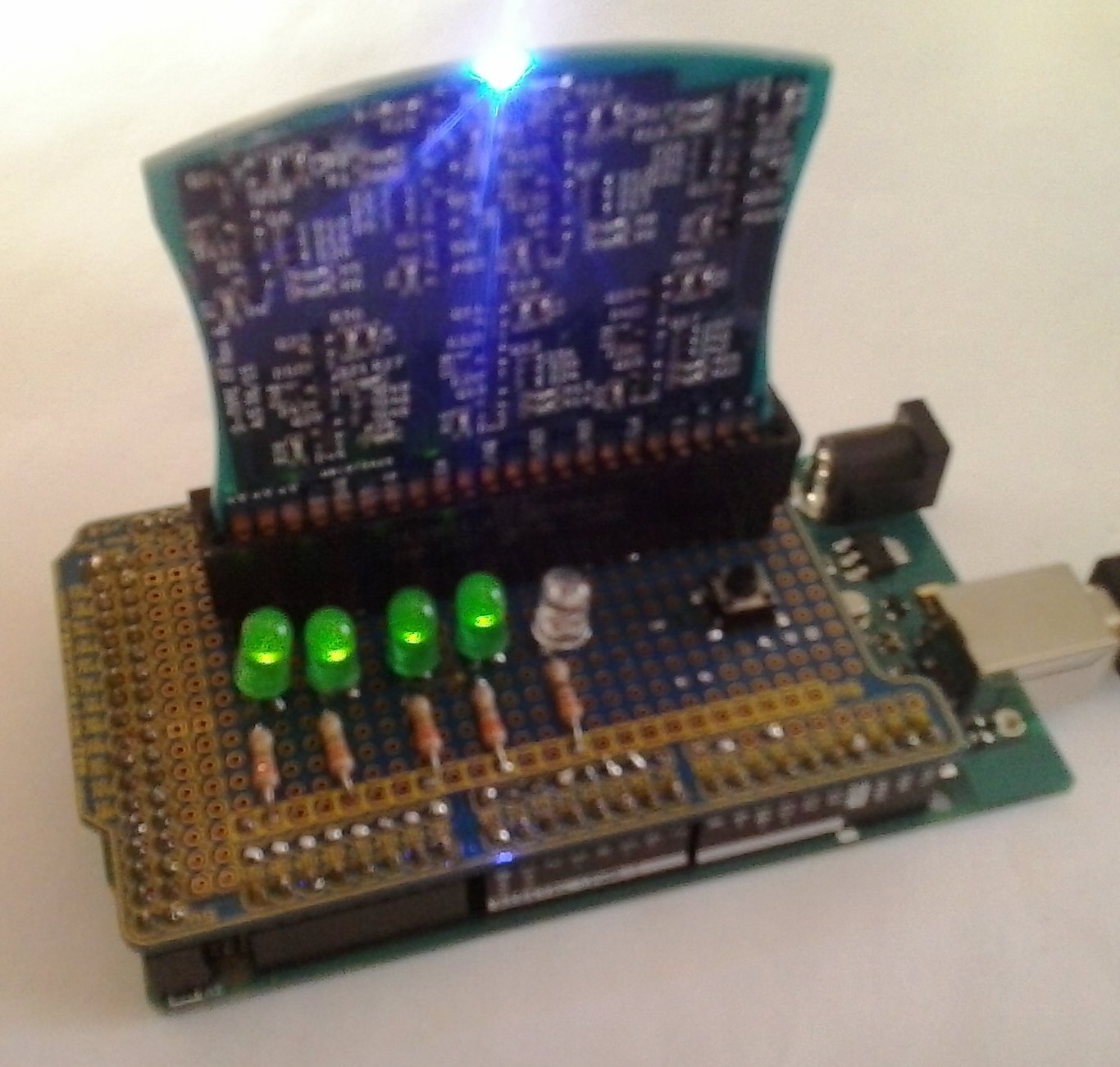

Dalam arsitektur Harvard, karakteristik perangkat memori untuk instruksi dan memori untuk data tidak harus sama. Secara khusus, lebar kata, clocking, teknologi implementasi, dan struktur alamat memori dapat bervariasi. Pada beberapa sistem, instruksi dapat disimpan dalam memori hanya-baca, sedangkan penyimpanan data biasanya membutuhkan memori baca dan tulis. Beberapa sistem memerlukan lebih banyak memori untuk instruksi daripada memori untuk data, karena data biasanya dapat dimuat dari memori eksternal atau lebih lambat. Kebutuhan seperti itu meningkatkan lebar bit (lebar) dari bus alamat memori instruksi dibandingkan dengan bus alamat memori data.Sistem arsitektur: Ia menggunakan mesin 2-stack standar dengan beberapa modifikasi yang memungkinkan menggunakan arsitektur Harvard dan bidang data opsional dalam instruksi.Sekarang penulis telah mengembangkan skema modul-AND, dan memesan modul yang sesuai, yang tiba beberapa hari yang lalu. Pengujian

Ia menggunakan mesin 2-stack standar dengan beberapa modifikasi yang memungkinkan menggunakan arsitektur Harvard dan bidang data opsional dalam instruksi.Sekarang penulis telah mengembangkan skema modul-AND, dan memesan modul yang sesuai, yang tiba beberapa hari yang lalu. Pengujian

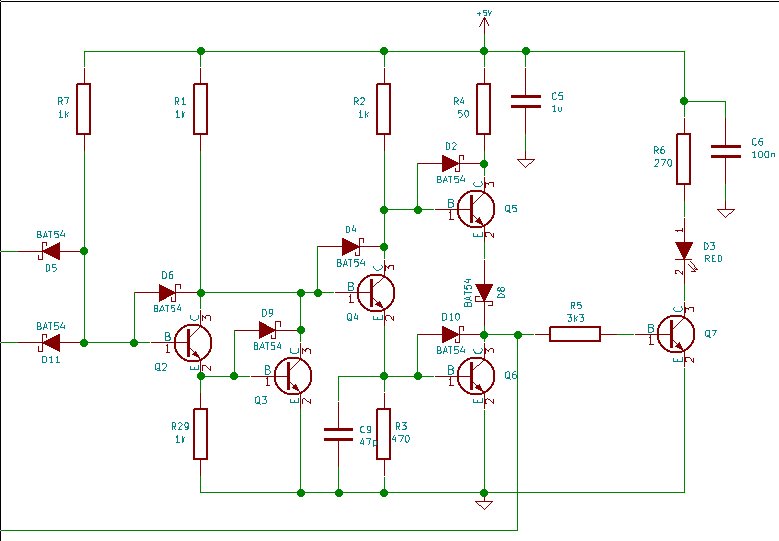

Skema

Skema

:

: Komponen lain juga siap, termasuk decoder alamat untuk memori tumpukan.

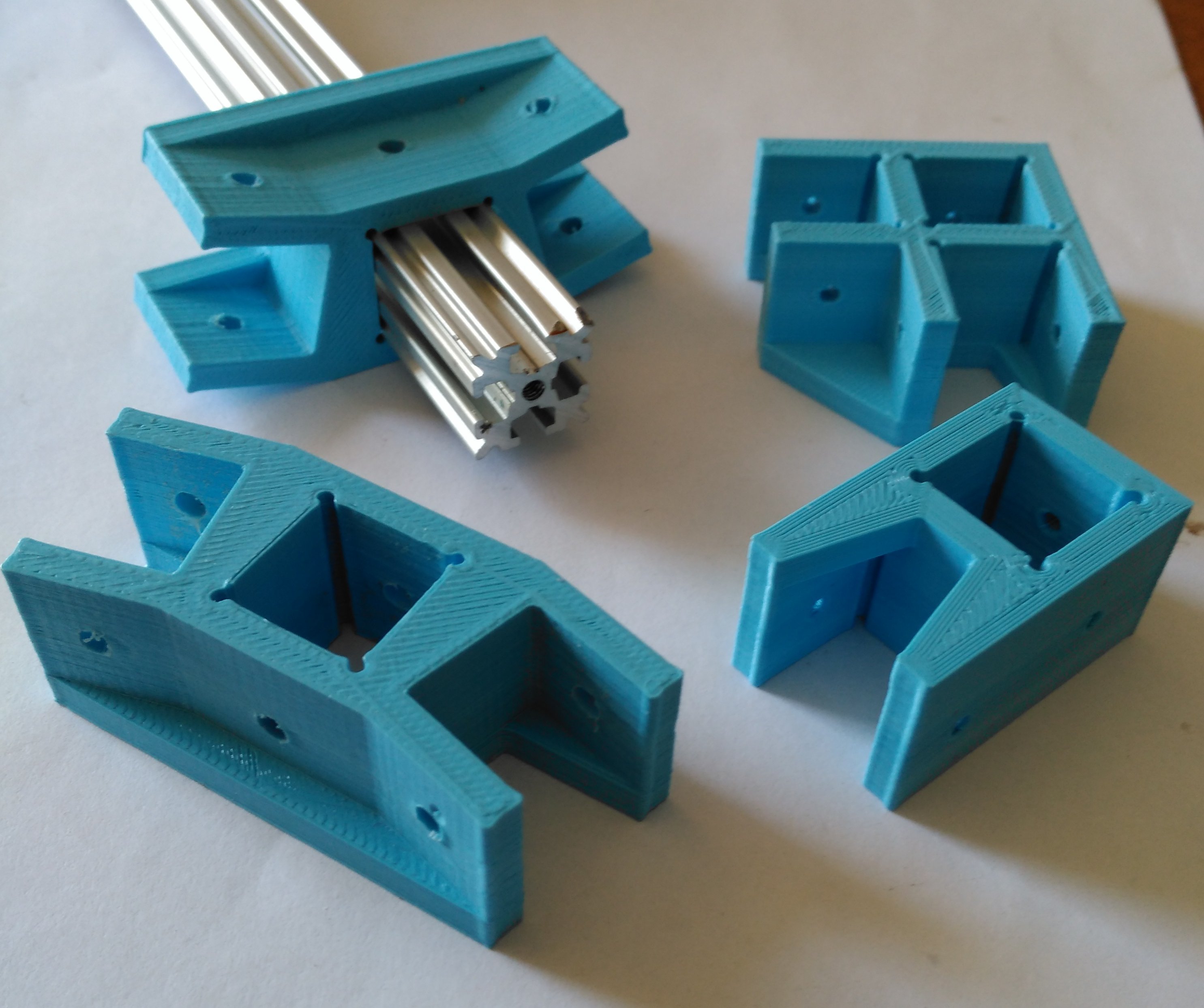

Komponen lain juga siap, termasuk decoder alamat untuk memori tumpukan. Antara lain, penulis juga mengembangkan kasus untuk ciptaannya:

Antara lain, penulis juga mengembangkan kasus untuk ciptaannya: Sekarang pekerjaan masih berlangsung, sehingga Anda dapat memantau pelaksanaan proyek di sini .

Sekarang pekerjaan masih berlangsung, sehingga Anda dapat memantau pelaksanaan proyek di sini .Source: https://habr.com/ru/post/id385409/

All Articles