Foto, materi, dan tikungan dan putaran seminar MIPSfpga di MEPhI

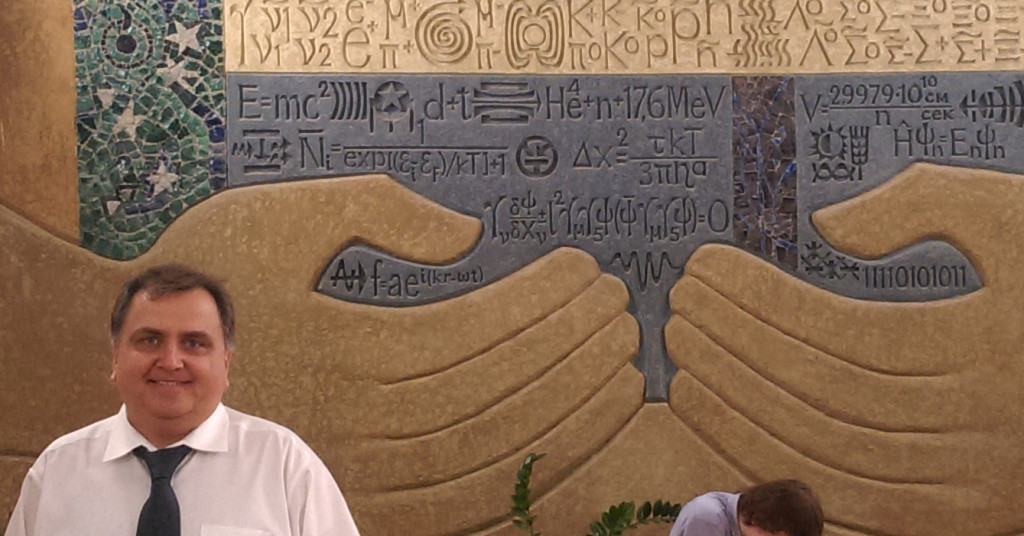

Pada akhir Oktober, sebuah seminar tentang MIPSfpga diadakan di MEPhI - salah satu dari serangkaian seminar yang diselenggarakan oleh universitas-universitas Rusia bersama dengan Imagination Technologies, Teknologi Microchip bekerja sama dengan Gamma St. Petersburg, perwakilan Kelompok Makro Xilinx di Rusia, dengan partisipasi pembicara dari MathWorks dan NIISI. Di bawah ini adalah campuran foto, tautan ke materi, catatan tentang persiapan seminar dan budaya mitos. Di bawah ini adalah gambar MEPhI di luar. Kata "nuklir" mengingatkan bahwa ada reaktor nuklir di Institut Teknik Fisika Moskow, jadi sulit untuk sampai ke sana, terutama dengan paspor Amerika - saya mendapat izin selama dua minggu, dan rektor menandatangani pesanan untuk seminar. Di pintu masuk ada penembak mesin dengan Kalashnikov (!) (Saya tidak diizinkan memotret pembuat senapan mesin) Inilah saya (Yuri Punchul) dengan penyelenggara seminar lainnya - Igor Ivanovich Shagurin dan Maxim Gorbunov: Igor Ivanovich Shagurin, Deputi. Kepala Departemen Mikro dan Nanoelektronika - penulis buku dan artikel tentang mikroprosesor Intel, Motorola dan PowerPC, pekerjaan laboratorium di MIPS . UPD: Klarifikasi dari seorang kawan dari NIIIS:

(Saya tidak diizinkan memotret pembuat senapan mesin) Inilah saya (Yuri Punchul) dengan penyelenggara seminar lainnya - Igor Ivanovich Shagurin dan Maxim Gorbunov: Igor Ivanovich Shagurin, Deputi. Kepala Departemen Mikro dan Nanoelektronika - penulis buku dan artikel tentang mikroprosesor Intel, Motorola dan PowerPC, pekerjaan laboratorium di MIPS . UPD: Klarifikasi dari seorang kawan dari NIIIS:

«, -32 -64 MIPS- — ( :) ). , — MIPS- . RISC , . MIPS-I. , , MIPS- , . , „ MIPS“ MIPS- . „

Yang menarik, Igor Ivanovich Shagurin pergi untuk mewakili elektronik Soviet di sebuah konferensi di San Francisco pada tahun 1970-an, ketika Uni Soviet adalah negara yang cukup terisolasi. Peserta konferensi VLSI pada 1970-an dibawa ke Muir Woods, daerah dengan Sequoia sempervirens Sequoia tertinggi di dunia, Maxim Gorbunov , seorang peneliti dari NIIIS / SRISA , sebuah lembaga yang juga terlibat dalam pengembangan mikroprosesor Rusia dengan arsitektur MIPS - COMDIV-32 dan KOMISI-64. Maxim berspesialisasi dalam merancang topologi VLSI yang tahan radiasi dan merupakan ketua bersama salah satu bagian dari konferensi RADECS internasional di Moskow:

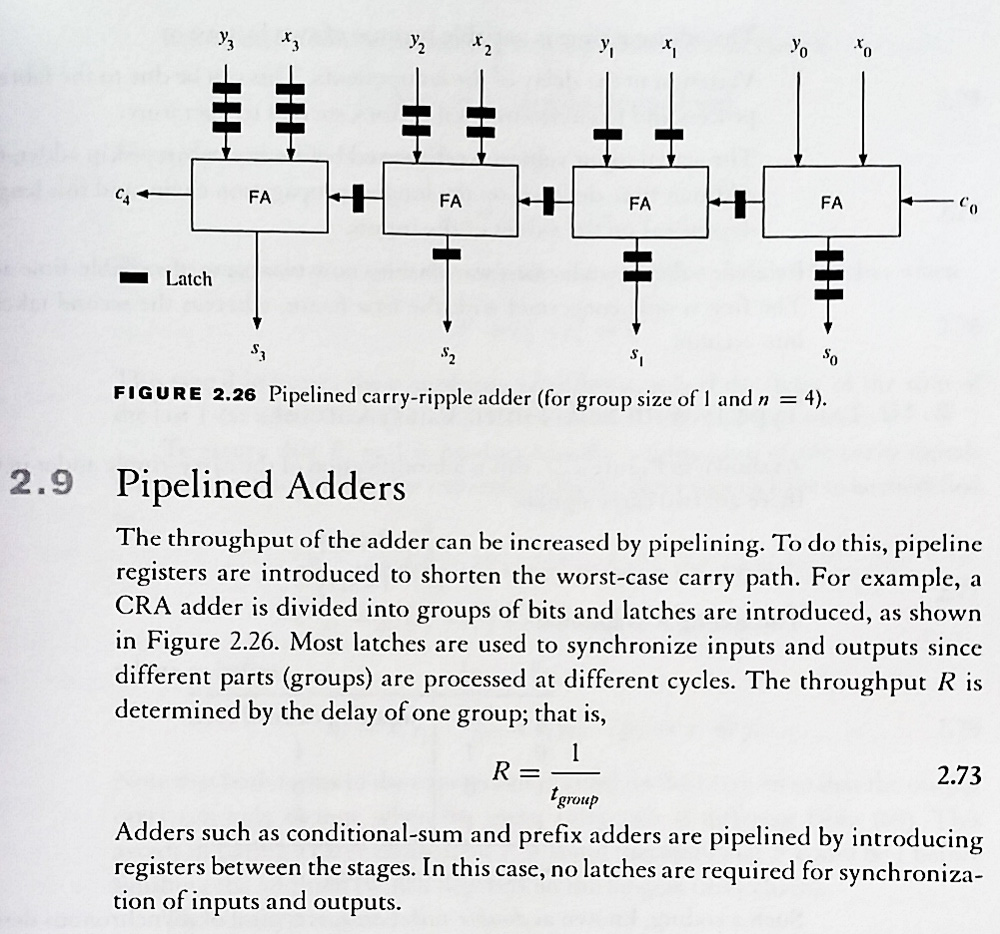

Sebelum seminar MIPSfpga di Institut Teknik Fisika Moskow, salah satu instruktur, Yegor Kuzmin, mulai bertanya kepada saya tentang kondisi lomba dalam skema tertentu untuk komputasi khusus yang muncul sebagai proyek siswa. Saya tidak yakin bahwa saya memahaminya dengan benar, tetapi menyatakan bahwa dalam desain sinkron yang terorganisasi dengan baik masalah seperti itu tidak muncul dan berjanji untuk mengirim sebagai contoh foto halaman dari buku "Digital Aritmatika", yang memahami organisasi dari penambah pipa, yang mengandung sedikit logika kombinatorial (sama seperti pada penambah dengan transfer sekuensial), tetapi pada saat yang sama menempatkan register (pemicu-D) sedemikian rupa sehingga penambah dapat memulai operasi tambahan baru setiap siklus clock, dengan frekuensi sinyal clock, ditentukan oleh penundaan satu-bit penambah kombinasional penuh:Digital Aritmatika Edisi 1 oleh Milos D. Ercegovac dan Tomás Lang Pada saat yang sama saya memotret beberapa halaman tentang sirkuit asinkron waktu-waktu, juga terkait dengan masalah ini .

Sebelum seminar MIPSfpga di Institut Teknik Fisika Moskow, salah satu instruktur, Yegor Kuzmin, mulai bertanya kepada saya tentang kondisi lomba dalam skema tertentu untuk komputasi khusus yang muncul sebagai proyek siswa. Saya tidak yakin bahwa saya memahaminya dengan benar, tetapi menyatakan bahwa dalam desain sinkron yang terorganisasi dengan baik masalah seperti itu tidak muncul dan berjanji untuk mengirim sebagai contoh foto halaman dari buku "Digital Aritmatika", yang memahami organisasi dari penambah pipa, yang mengandung sedikit logika kombinatorial (sama seperti pada penambah dengan transfer sekuensial), tetapi pada saat yang sama menempatkan register (pemicu-D) sedemikian rupa sehingga penambah dapat memulai operasi tambahan baru setiap siklus clock, dengan frekuensi sinyal clock, ditentukan oleh penundaan satu-bit penambah kombinasional penuh:Digital Aritmatika Edisi 1 oleh Milos D. Ercegovac dan Tomás Lang Pada saat yang sama saya memotret beberapa halaman tentang sirkuit asinkron waktu-waktu, juga terkait dengan masalah ini . Kemudian saya diperkenalkan dengan Vladimir Dementiev, yang, bersama dengan Andrei Andrianov, Dmitry Kozlovsky, melakukan kelas laboratorium di MEPhI untuk pemrograman mikrokontroler Microchip PIC32MX. Saya mengatakan kepada Vladimir bahwa Profesor Alex Dean dari University of North Carolina berkolaborasi dengan Imagination, Microchip dan Digilent dan sekarang sedang mengembangkan kursus baru tentang pemrograman mikrokontroler Microchip PIC32MZ PIC32MZKursus ini termasuk RTOS dan koneksi mikrokontroler bermodel baru ke cloud. Mikrokontroler PIC32MZ didasarkan pada inti mikroprosesor MIPS microAptiv UP, sama seperti yang digunakan dalam MIPSfpga. Oleh karena itu, saya mulai mengagitasi kawan-kawan MEPhI untuk mengambil bagian dalam ulasan dan (jika mereka suka) pengujian beta dari kursus ini: Tetapi kembali ke seminar kami. Topik seminar adalah MIPSfpga. Apa itu:

Kemudian saya diperkenalkan dengan Vladimir Dementiev, yang, bersama dengan Andrei Andrianov, Dmitry Kozlovsky, melakukan kelas laboratorium di MEPhI untuk pemrograman mikrokontroler Microchip PIC32MX. Saya mengatakan kepada Vladimir bahwa Profesor Alex Dean dari University of North Carolina berkolaborasi dengan Imagination, Microchip dan Digilent dan sekarang sedang mengembangkan kursus baru tentang pemrograman mikrokontroler Microchip PIC32MZ PIC32MZKursus ini termasuk RTOS dan koneksi mikrokontroler bermodel baru ke cloud. Mikrokontroler PIC32MZ didasarkan pada inti mikroprosesor MIPS microAptiv UP, sama seperti yang digunakan dalam MIPSfpga. Oleh karena itu, saya mulai mengagitasi kawan-kawan MEPhI untuk mengambil bagian dalam ulasan dan (jika mereka suka) pengujian beta dari kursus ini: Tetapi kembali ke seminar kami. Topik seminar adalah MIPSfpga. Apa itu:

MIPSfpga — MIPS microAptiv UP. Microchip PIC32MZ, « » — Samsung Artik 1.

MIPS microAptiv UP 25 , Verilog, , .

MIPS microAptiv UP — MIPSfpga — : (), () Field Programmable Gate Array (FPGA).

Jadi, pertama saya berbicara dan berbicara tentang:1. Imagination Technologies dan unit bisnis MIPS-nya.2. Program pendidikan Imagination Technologies3. Untuk menyegarkan konsep aliran RTL-ke-GDSII bagi mereka di antara hadirin yang tidak memiliki Verilog / VHDL untuk spesialisasi: Bagaimana IP blok dan sistem pada sebuah chip (SoC) dirancang.4. Saya berbicara sedikit tentang tiga baris inti mikroprosesor MIPS dan lebih detail tentang garis inti kelas mikrokontroler, berdasarkan pada salah satu di antaranya (MIPS microAptiv UP) paket MIPSfpga5. Karena salah satu latihan selanjutnya termasuk mendemonstrasikan cache, saya mengatakan beberapa kata-kata dan tentang cache di MIPS microAptiv UP

Setelah pidato pertama saya, Mikhail Peselnik, seorang pembicara dari MathWorks berpidato: Mikhail Peselnik mengimplementasikan subset MIPS di Simulink , yang menerima semacam penghargaan editorial MATLAB Pilihan Tengah Minggu: Contoh Mikhail menunjukkan bahwa bagi siswa arsitektur dan arsitektur mikro inti prosesor dapat dipelajari dengan berbagai cara - setidaknya pada Verilog dan VHDL, setidaknya dengan bantuan model C, setidaknya dengan bantuan Simulink. Tetapi setelah dasar-dasar arsitektur dan mikroarsitektur dipelajari, siswa harus bereksperimen dengan prosesor industri, dan di sini MIPSfpga memasuki lokasi, dengan mana:

Setelah pidato pertama saya, Mikhail Peselnik, seorang pembicara dari MathWorks berpidato: Mikhail Peselnik mengimplementasikan subset MIPS di Simulink , yang menerima semacam penghargaan editorial MATLAB Pilihan Tengah Minggu: Contoh Mikhail menunjukkan bahwa bagi siswa arsitektur dan arsitektur mikro inti prosesor dapat dipelajari dengan berbagai cara - setidaknya pada Verilog dan VHDL, setidaknya dengan bantuan model C, setidaknya dengan bantuan Simulink. Tetapi setelah dasar-dasar arsitektur dan mikroarsitektur dipelajari, siswa harus bereksperimen dengan prosesor industri, dan di sini MIPSfpga memasuki lokasi, dengan mana:

- Siswa dapat membangun prototipe sistem mereka sendiri pada sebuah chip, menggabungkan inti mikroprosesor, memori dan perangkat I / O yang dirancang oleh mereka

- , . « ».

- , , .

Tetapi untuk bereksperimen dengan pengembangan SoC dan dengan kernel, mereka harus memiliki perintah yang baik dari alat / alat implementasi. Karena itu, setelah Mikhail Mikhail Filippov, insinyur aplikasi dari Macro Group, perwakilan resmi Xilinx di Rusia, berbicara. Xilinx adalah perusahaan yang pernah menciptakan FPGA dan sampai hari ini tetap # 1 di FPGA paling cepat.Alexander Filippov membuat dua laporan:- 7-Series FPGAs baru dan MPSoC UltraScale - Produk XILINX untuk Sistem Chip yang Dapat Diprogram yang Kuat

- XILINX VIVADO Lingkungan Desain untuk Membuat Sistem pada Chip

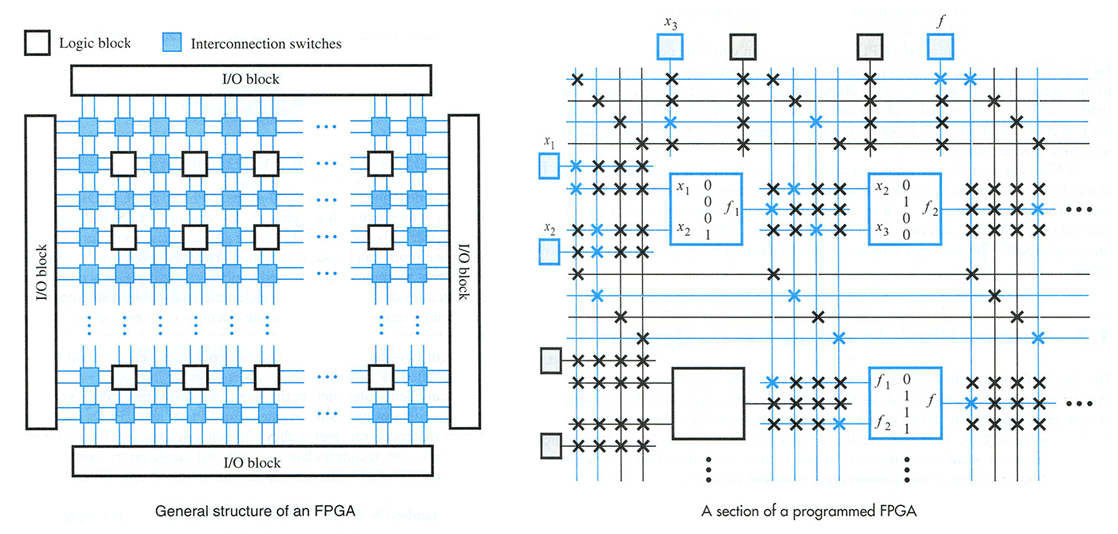

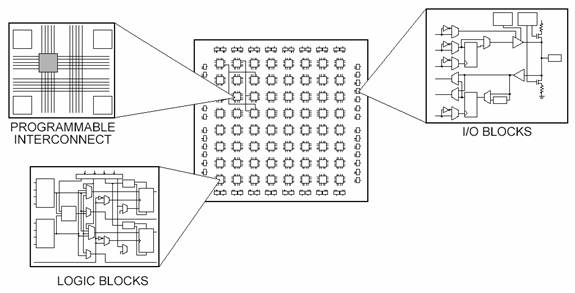

Apa FPGA / FPGA yang saya jelaskan di pos lain tentang Habr - Bagaimana cara mulai mengembangkan besi menggunakan FPGA - petunjuk langkah demi langkah . Tetapi mari kita ulangi informasi ini lagi:Dalam versi yang paling sederhana, FPGA terdiri dari matriks sel-sel homogen, yang masing-masingnya dapat diubah berfungsi menggunakan multiplexer yang terhubung ke bit memori konfigurasi. Satu sel dapat menjadi gerbang AND dengan empat input dan satu output, yang lain - register bit-tunggal, dll. Kami memuat urutan bit dari memori ke dalam memori konfigurasi - dan sirkuit elektronik yang diberikan terbentuk dalam FPGA, yang dapat berupa prosesor, pengontrol tampilan, dll.FPGA / FPGA bukan prosesor, dengan "memprogram" FPGA (mengisi memori konfigurasi FPGA) Anda membuat sirkuit elektronik (perangkat keras), sedangkan saat memprogram prosesor (perangkat keras tetap), Anda memasukkan rantai instruksi program berurutan yang ditulis ke dalamnya. (perangkat lunak).Di bawah ini adalah diagram unit FPGA paling sederhana, yang meliputi tabel pencarian (LUT) dan flip-flop. Benar, dalam skema ini, multiplexer yang mengubah fungsi sel, dan koneksi ke memori konfigurasi tidak ditampilkan.

Apa FPGA / FPGA yang saya jelaskan di pos lain tentang Habr - Bagaimana cara mulai mengembangkan besi menggunakan FPGA - petunjuk langkah demi langkah . Tetapi mari kita ulangi informasi ini lagi:Dalam versi yang paling sederhana, FPGA terdiri dari matriks sel-sel homogen, yang masing-masingnya dapat diubah berfungsi menggunakan multiplexer yang terhubung ke bit memori konfigurasi. Satu sel dapat menjadi gerbang AND dengan empat input dan satu output, yang lain - register bit-tunggal, dll. Kami memuat urutan bit dari memori ke dalam memori konfigurasi - dan sirkuit elektronik yang diberikan terbentuk dalam FPGA, yang dapat berupa prosesor, pengontrol tampilan, dll.FPGA / FPGA bukan prosesor, dengan "memprogram" FPGA (mengisi memori konfigurasi FPGA) Anda membuat sirkuit elektronik (perangkat keras), sedangkan saat memprogram prosesor (perangkat keras tetap), Anda memasukkan rantai instruksi program berurutan yang ditulis ke dalamnya. (perangkat lunak).Di bawah ini adalah diagram unit FPGA paling sederhana, yang meliputi tabel pencarian (LUT) dan flip-flop. Benar, dalam skema ini, multiplexer yang mengubah fungsi sel, dan koneksi ke memori konfigurasi tidak ditampilkan. Diagram yang menggambarkan struktur FPGA:

Diagram yang menggambarkan struktur FPGA: Dan satu lagi:

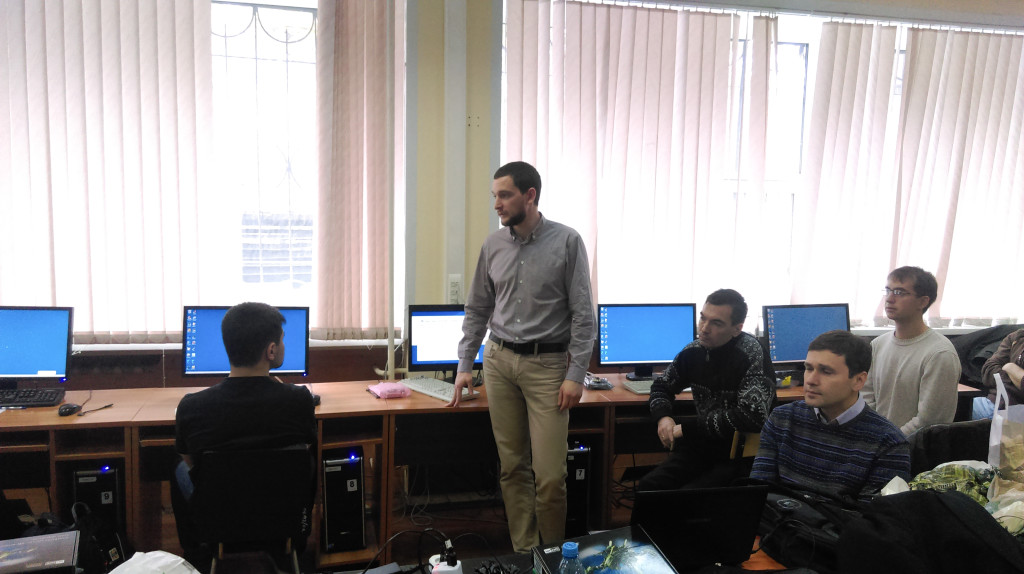

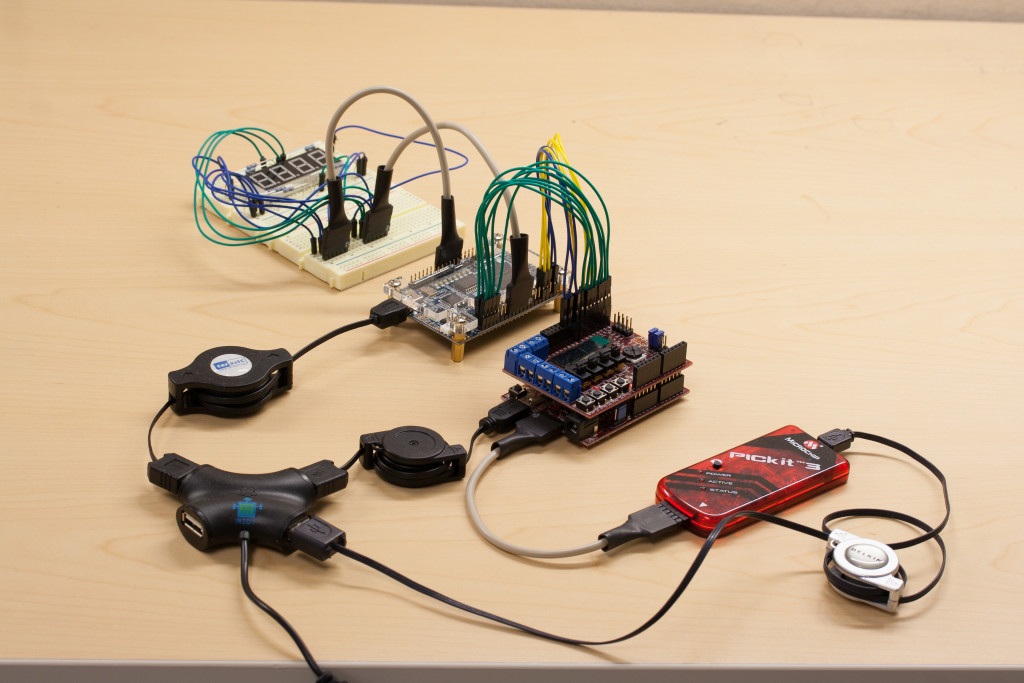

Dan satu lagi: Setelah makan siang di ruang makan Institut Teknik Fisika Moskow, kami memulai bagian praktis. Awalnya, ketika Imagination Technologies dan Xilinx mengadakan seminar semacam itu di Los Angeles, mereka menggunakannyaslide disiapkan oleh profesor David dan Sarah Harris dari California selatan . Seperti yang terlihat aslinya, Anda dapat melihat di video:Semua 8 video darilokakarya Los Angeles Untuk seminar di Rusia, inti dan lab binding Harris harus banyak dimodifikasi. Modifikasi dapat ditemukan di https://github.com/MIPSfpga/mipsfpga-plus . Perbedaannya meliputi:1. Semuanya diurutkan untuk motherboard murah dari Altera, tersedia di Rusia tanpa traktor ekspor-impor2. Program telah dimuat ke dalam sistem yang disintesis tanpa menggunakan BusBlaster, cukup melalui UART3. Sensor cahaya sebagai perangkat periferal alih-alih layar LCD4. Switchable sinyal clock frekuensi ultra-rendah, memungkinkan lab untuk memvisualisasikan operasi internal prosesor apa pun5. Menambahkan lab sederhana untuk memvisualisasikan kesalahan cache+ setiap hal kecil dan kosmetik - bootloader / bootloader yang lebih ringkas, kemungkinan transaksi sempit non-cacheable ke memori, dll.Lebih detail:1. Mengangkut di bawah AlteraPertama-tama, slide Harris menunjukkan segalanya untuk Xilinx, dan baru-baru ini, papan pengiriman dari Xilinx FPGA ke Rusia telah menjadi prosedur birokrasi yang agak rumit yang membutuhkan waktu 3-4 bulan. Hal yang sama terjadi dengan lisensi perangkat lunak untuk sintesis dan tempat-dan-rute Xilinx Vivado, bahkan dengan lisensi gratis. Beberapa universitas Rusia tidak memiliki papan Xilinx atau lisensi Vivado; yang lain hanya memiliki lisensi lama untuk pendahulu Vivado - perangkat lunak ISE 2013, yang tidak mendukung FPGA di papan yang saya bawa di Rusia.Singkatnya, untuk seminar di Rusia, kawan-kawan dan saya, di California, telah mengirim MIPSfpga ke beberapa papan murah yang tersedia di Rusia dari saingan Xilinx Altera (perusahaan ini sekarang bergabung dengan Intel). Papan pengganti disumbangkan untuk kebutuhan lokakarya oleh perusahaan Zelenograd, SPC Elvis . Papan utama di MEPhI, MIPT dan SSAU adalah Terasic DE0-CV berdasarkan Altera Cyclone V: Papan lain adalah Terasic DE0-Nano - selendang yang sangat kompak cocok untuk proyek-proyek seperti robot terbang, tetapi dengan sejumlah kecil peripheral di papan: Terasic DE0- kerugian Nano adalah sejumlah kecil perangkat periferal di papan itu sendiri, tetapi juga merupakan keuntungan, karena DE0-Nano dapat dihubungkan sebagai perancang dengan papan lain dan dibangun ke dalam perangkat yang berbeda:

Setelah makan siang di ruang makan Institut Teknik Fisika Moskow, kami memulai bagian praktis. Awalnya, ketika Imagination Technologies dan Xilinx mengadakan seminar semacam itu di Los Angeles, mereka menggunakannyaslide disiapkan oleh profesor David dan Sarah Harris dari California selatan . Seperti yang terlihat aslinya, Anda dapat melihat di video:Semua 8 video darilokakarya Los Angeles Untuk seminar di Rusia, inti dan lab binding Harris harus banyak dimodifikasi. Modifikasi dapat ditemukan di https://github.com/MIPSfpga/mipsfpga-plus . Perbedaannya meliputi:1. Semuanya diurutkan untuk motherboard murah dari Altera, tersedia di Rusia tanpa traktor ekspor-impor2. Program telah dimuat ke dalam sistem yang disintesis tanpa menggunakan BusBlaster, cukup melalui UART3. Sensor cahaya sebagai perangkat periferal alih-alih layar LCD4. Switchable sinyal clock frekuensi ultra-rendah, memungkinkan lab untuk memvisualisasikan operasi internal prosesor apa pun5. Menambahkan lab sederhana untuk memvisualisasikan kesalahan cache+ setiap hal kecil dan kosmetik - bootloader / bootloader yang lebih ringkas, kemungkinan transaksi sempit non-cacheable ke memori, dll.Lebih detail:1. Mengangkut di bawah AlteraPertama-tama, slide Harris menunjukkan segalanya untuk Xilinx, dan baru-baru ini, papan pengiriman dari Xilinx FPGA ke Rusia telah menjadi prosedur birokrasi yang agak rumit yang membutuhkan waktu 3-4 bulan. Hal yang sama terjadi dengan lisensi perangkat lunak untuk sintesis dan tempat-dan-rute Xilinx Vivado, bahkan dengan lisensi gratis. Beberapa universitas Rusia tidak memiliki papan Xilinx atau lisensi Vivado; yang lain hanya memiliki lisensi lama untuk pendahulu Vivado - perangkat lunak ISE 2013, yang tidak mendukung FPGA di papan yang saya bawa di Rusia.Singkatnya, untuk seminar di Rusia, kawan-kawan dan saya, di California, telah mengirim MIPSfpga ke beberapa papan murah yang tersedia di Rusia dari saingan Xilinx Altera (perusahaan ini sekarang bergabung dengan Intel). Papan pengganti disumbangkan untuk kebutuhan lokakarya oleh perusahaan Zelenograd, SPC Elvis . Papan utama di MEPhI, MIPT dan SSAU adalah Terasic DE0-CV berdasarkan Altera Cyclone V: Papan lain adalah Terasic DE0-Nano - selendang yang sangat kompak cocok untuk proyek-proyek seperti robot terbang, tetapi dengan sejumlah kecil peripheral di papan: Terasic DE0- kerugian Nano adalah sejumlah kecil perangkat periferal di papan itu sendiri, tetapi juga merupakan keuntungan, karena DE0-Nano dapat dihubungkan sebagai perancang dengan papan lain dan dibangun ke dalam perangkat yang berbeda:

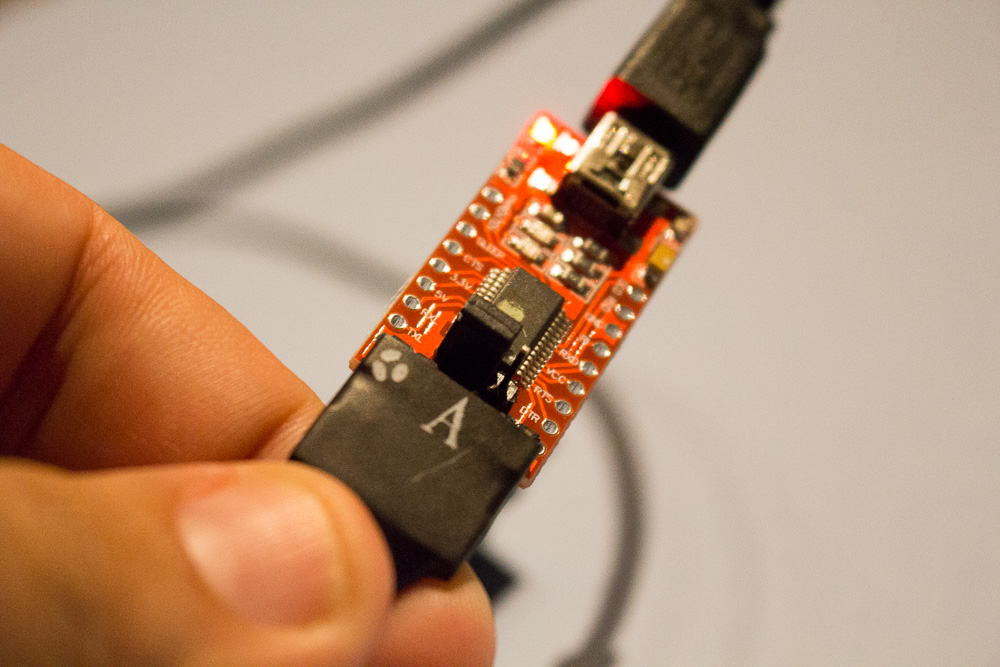

2. Unduh melalui UART Masalahslide kedua dari Harris adalah menggunakan adaptor debug dan perangkat lunak Bus Blaster untuknya yang disebut OpenOCD . Pada dasarnya, BusBlaster / OpenOCD adalah solusi yang cukup bagus dari jenisnya. Hal ini memungkinkan tidak hanya memuat program ke dalam sistem yang disintesis di dalam FPGA, tetapi juga men-debug mereka dari jarak jauh melalui antarmuka EJTAG, tambahan tingkat tinggi di atas antarmuka JTAG. Pada saat yang sama, BusBlaster harganya hanya $ 43, yang jauh lebih murah daripada adaptor EJTAG debugging industri.Sayangnya, kombinasi BusBlaster / OpenOCD cukup kasar, dan saya takut itu tidak akan bekerja pada beberapa konfigurasi komputer yang tidak terduga di Rusia (saya benar - itu tidak bekerja di MIPT dan SSAU). Selain,Di situs yang menjual kombinasi BusBlaster / OpenOCD untuk MIPS , terkadang papan habis.Untuk alasan ini dan lainnya, saya mulai mencari cara lain untuk memuat perangkat lunak ke dalam sistem (dalam FPGA, Anda perlu memuat secara terpisah konfigurasi / perangkat keras dan perangkat lunak untuk prosesor (dalam sistem yang disintesis dengan prosesor)). Troll internet anonim Alexey mencoba untuk membuat saya lemah untuk waktu yang lama, sehingga saya akan mengimplementasikan bootloader EJTAG melalui Altera USB Blaster, tetapi karena saya bukan ahli EJTAG, saya memilih solusi sederhana yang bekerja sejak era Soviet - untuk memuat program melalui port serial / UART. Benar, selama era Soviet ada port RS-232C, dan pada 1990-an chip dari FTDI muncul, yang memungkinkan untuk melakukan segalanya melalui kabel USB yang terhubung ke PC. Variasi berbeda dari adaptor semacam itu dapat dibeli seharga $ 5 di Moskow dan kurang dari $ 2 melalui Internet dari Tiongkok:

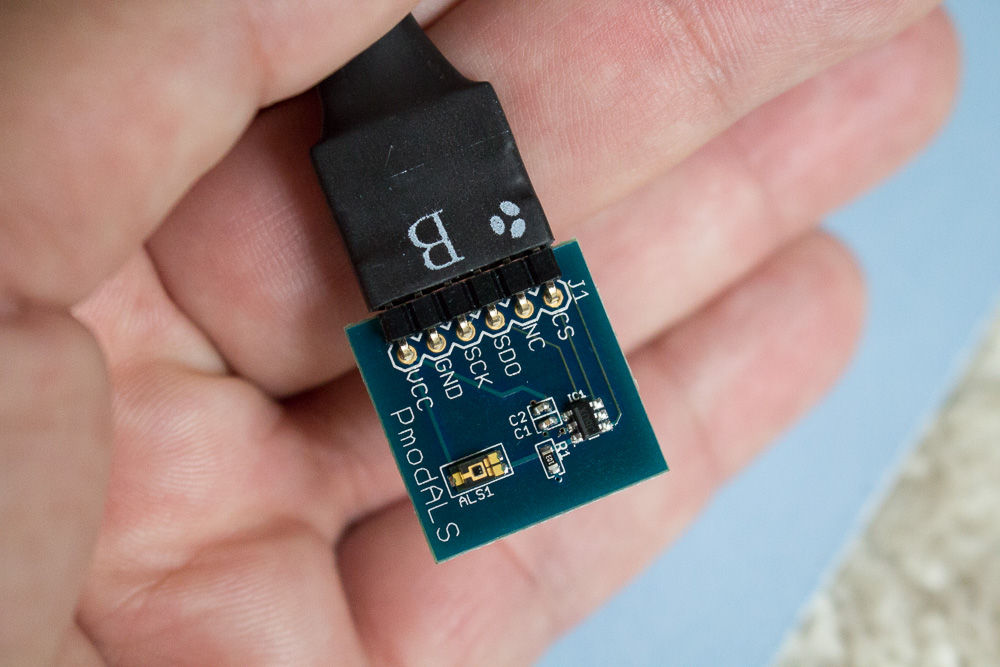

2. Unduh melalui UART Masalahslide kedua dari Harris adalah menggunakan adaptor debug dan perangkat lunak Bus Blaster untuknya yang disebut OpenOCD . Pada dasarnya, BusBlaster / OpenOCD adalah solusi yang cukup bagus dari jenisnya. Hal ini memungkinkan tidak hanya memuat program ke dalam sistem yang disintesis di dalam FPGA, tetapi juga men-debug mereka dari jarak jauh melalui antarmuka EJTAG, tambahan tingkat tinggi di atas antarmuka JTAG. Pada saat yang sama, BusBlaster harganya hanya $ 43, yang jauh lebih murah daripada adaptor EJTAG debugging industri.Sayangnya, kombinasi BusBlaster / OpenOCD cukup kasar, dan saya takut itu tidak akan bekerja pada beberapa konfigurasi komputer yang tidak terduga di Rusia (saya benar - itu tidak bekerja di MIPT dan SSAU). Selain,Di situs yang menjual kombinasi BusBlaster / OpenOCD untuk MIPS , terkadang papan habis.Untuk alasan ini dan lainnya, saya mulai mencari cara lain untuk memuat perangkat lunak ke dalam sistem (dalam FPGA, Anda perlu memuat secara terpisah konfigurasi / perangkat keras dan perangkat lunak untuk prosesor (dalam sistem yang disintesis dengan prosesor)). Troll internet anonim Alexey mencoba untuk membuat saya lemah untuk waktu yang lama, sehingga saya akan mengimplementasikan bootloader EJTAG melalui Altera USB Blaster, tetapi karena saya bukan ahli EJTAG, saya memilih solusi sederhana yang bekerja sejak era Soviet - untuk memuat program melalui port serial / UART. Benar, selama era Soviet ada port RS-232C, dan pada 1990-an chip dari FTDI muncul, yang memungkinkan untuk melakukan segalanya melalui kabel USB yang terhubung ke PC. Variasi berbeda dari adaptor semacam itu dapat dibeli seharga $ 5 di Moskow dan kurang dari $ 2 melalui Internet dari Tiongkok: Saya akan segera mencatat bahwa Anda dapat memuat program ke dalam SoC yang disintesis dengan berbagai cara. Dalam salah satu dari mereka, yang lebih tradisional, sistem memiliki program kecil yang tetap dalam memori (bootloader), yang dimulai setelah mengatur ulang sistem dan memuat program yang lebih besar melalui UART / port serial. Metode ini digunakan oleh Anton Pavlov dari NIIIS, yang mendemonstrasikannya di seminar di Universitas Negeri Moskow dan Institut Teknik Fisika Moskow, dan juga menulis tentang dia di geektimes "MIPSfpga: di luar kanon . "Saya melakukan pemuatan dengan cara alternatif, di mana memori diisi dengan mesin negara, sepenuhnya diimplementasikan dalam perangkat keras. Mesin menerima file teks dalam format S-Record Motorola dari PC melalui UART, parsing (semua yang ada di perangkat keras) dan isi memori dengan data, saat prosesor dalam keadaan reset. Kemudian prosesor bangun dan mulai membaca program dari memori sistem. Semua yang perlu dilakukan pada sisi PC adalah untuk mengkonversi file ELF yang dapat dieksekusi ke format Motorola S-Record dan mengirimkannya ke port COM virtual dengan perintah "ketik" windows-shell.3. Sensor cahaya sebagai periferal bukan layar LCDDi laboratorium Harris yang asli, mereka menggunakan indikator tujuh segmen dan layar LCD SPI sebagai contoh periferal. Contoh dengan indikator tujuh segmen membosankan - setiap siswa memahami bahwa jika Anda tahu cara berkedip dengan satu lampu, maka Anda tahu bagaimana cara berkedip dengan tujuh lampu. Contoh SPI sedikit lebih baik, terutama dalam hal siswa pemula, tetapi mengapa kita perlu tampilan kedua jika sudah ada indikator tujuh segmen? Singkatnya, sebelum bepergian ke Rusia, saya membeli 20 sensor cahaya, juga dengan antarmuka SPI, dan menggunakannya sebagai pengganti layar: Pada saat yang sama, antarmuka untuk itu sangat sederhana - di sini adalah modul antarmuka yang saya tulis (catatan: kode ini tidak termasuk semua modifikasi sistem untuk memasangkannya dengan AHB-Lite bus, sehingga perangkat lunak melihat nilainya):

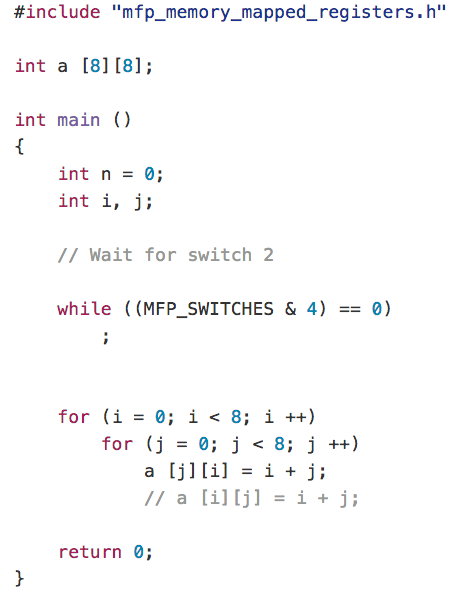

Saya akan segera mencatat bahwa Anda dapat memuat program ke dalam SoC yang disintesis dengan berbagai cara. Dalam salah satu dari mereka, yang lebih tradisional, sistem memiliki program kecil yang tetap dalam memori (bootloader), yang dimulai setelah mengatur ulang sistem dan memuat program yang lebih besar melalui UART / port serial. Metode ini digunakan oleh Anton Pavlov dari NIIIS, yang mendemonstrasikannya di seminar di Universitas Negeri Moskow dan Institut Teknik Fisika Moskow, dan juga menulis tentang dia di geektimes "MIPSfpga: di luar kanon . "Saya melakukan pemuatan dengan cara alternatif, di mana memori diisi dengan mesin negara, sepenuhnya diimplementasikan dalam perangkat keras. Mesin menerima file teks dalam format S-Record Motorola dari PC melalui UART, parsing (semua yang ada di perangkat keras) dan isi memori dengan data, saat prosesor dalam keadaan reset. Kemudian prosesor bangun dan mulai membaca program dari memori sistem. Semua yang perlu dilakukan pada sisi PC adalah untuk mengkonversi file ELF yang dapat dieksekusi ke format Motorola S-Record dan mengirimkannya ke port COM virtual dengan perintah "ketik" windows-shell.3. Sensor cahaya sebagai periferal bukan layar LCDDi laboratorium Harris yang asli, mereka menggunakan indikator tujuh segmen dan layar LCD SPI sebagai contoh periferal. Contoh dengan indikator tujuh segmen membosankan - setiap siswa memahami bahwa jika Anda tahu cara berkedip dengan satu lampu, maka Anda tahu bagaimana cara berkedip dengan tujuh lampu. Contoh SPI sedikit lebih baik, terutama dalam hal siswa pemula, tetapi mengapa kita perlu tampilan kedua jika sudah ada indikator tujuh segmen? Singkatnya, sebelum bepergian ke Rusia, saya membeli 20 sensor cahaya, juga dengan antarmuka SPI, dan menggunakannya sebagai pengganti layar: Pada saat yang sama, antarmuka untuk itu sangat sederhana - di sini adalah modul antarmuka yang saya tulis (catatan: kode ini tidak termasuk semua modifikasi sistem untuk memasangkannya dengan AHB-Lite bus, sehingga perangkat lunak melihat nilainya):

4.Jam beralih ke frekuensi sangat rendah Ketika MIPSfpga muncul dan profesor universitas Rusia mulai mempelajarinya, beberapa dari mereka mulai mengeluh bahwa paket dalam bentuk aslinya tidak terlalu menarik bagi siswa tingkat lanjut, karena laboratorium yang disiapkan oleh David dan Sarah Harris menggunakan prosesor seperti "kotak hitam", hanya menghubungkan perangkat ke sana. Dengan kata lain, Harris sepenuhnya mengabaikan bahwa prosesor diberikan dalam kode sumber, dan oleh karena itu dimungkinkan untuk mengimplementasikan laboratorium dengan itu yang akan memungkinkan koneksi menjadi output dari register prosesor sewenang-wenang (tidak hanya register yang terlihat oleh programmer, tetapi umumnya dari pemicu-D), untuk menghubungkan misalnya untuk LED, dan amati apa yang terjadi pada prosesor saat menjalankan program tertentu.Seperti yang Anda pahami, agar pengamatan seperti itu “hidup”, prosesor harus bekerja pada frekuensi clock yang sangat rendah, misalnya, clock per detik. Bagaimana cara melakukannya? Inti MIPS microAptiv UP yang diimplementasikan di ASIC pada teknologi 28 nm dapat beroperasi pada frekuensi di atas 500 MHz, dan pada teknologi 65 nm lebih dari 300 MHz. Ketika diimplementasikan pada FPGA, frekuensinya jauh lebih rendah, tetapi masih tinggi - 50-60 MHz. Frekuensi generator sinyal jam pada papan adalah 50-100 MHz, dengan kemungkinan menambah atau mengurangi frekuensi menggunakan loop-terkunci loop (PLL) / loop-terkunci loop (PLL) .Sayangnya, menggunakan PLL, Anda dapat mengurangi frekuensinya menjadi ~ 100 KHz, tetapi Anda harus mengurangi frekuensinya menjadi 1 Hz dengan cara lain. Pada awalnya saya mencoba melakukan ini menggunakan blok dari Altera yang disebutALTCLKCTRL , tetapi karena alasan tertentu tidak berhasil. Kemudian saya mencoba untuk membagi sinyal clock menggunakan penghitung, tetapi (saya sudah tahu itu) solusi ini dengan sendirinya tidak bekerja, karena synthesizer tidak mengerti bahwa sinyal output adalah sinyal clock dan mulai membaginya secara salah, akibatnya prosesor tidak bekerja. Saya berkonsultasi dengan beberapa kawan dan kami mulai menggunakan makro Alter "global" (dan setara dengan Xilinx BUFG). 5. Menambahkan lab visualisasi miss cache sederhana

4.Jam beralih ke frekuensi sangat rendah Ketika MIPSfpga muncul dan profesor universitas Rusia mulai mempelajarinya, beberapa dari mereka mulai mengeluh bahwa paket dalam bentuk aslinya tidak terlalu menarik bagi siswa tingkat lanjut, karena laboratorium yang disiapkan oleh David dan Sarah Harris menggunakan prosesor seperti "kotak hitam", hanya menghubungkan perangkat ke sana. Dengan kata lain, Harris sepenuhnya mengabaikan bahwa prosesor diberikan dalam kode sumber, dan oleh karena itu dimungkinkan untuk mengimplementasikan laboratorium dengan itu yang akan memungkinkan koneksi menjadi output dari register prosesor sewenang-wenang (tidak hanya register yang terlihat oleh programmer, tetapi umumnya dari pemicu-D), untuk menghubungkan misalnya untuk LED, dan amati apa yang terjadi pada prosesor saat menjalankan program tertentu.Seperti yang Anda pahami, agar pengamatan seperti itu “hidup”, prosesor harus bekerja pada frekuensi clock yang sangat rendah, misalnya, clock per detik. Bagaimana cara melakukannya? Inti MIPS microAptiv UP yang diimplementasikan di ASIC pada teknologi 28 nm dapat beroperasi pada frekuensi di atas 500 MHz, dan pada teknologi 65 nm lebih dari 300 MHz. Ketika diimplementasikan pada FPGA, frekuensinya jauh lebih rendah, tetapi masih tinggi - 50-60 MHz. Frekuensi generator sinyal jam pada papan adalah 50-100 MHz, dengan kemungkinan menambah atau mengurangi frekuensi menggunakan loop-terkunci loop (PLL) / loop-terkunci loop (PLL) .Sayangnya, menggunakan PLL, Anda dapat mengurangi frekuensinya menjadi ~ 100 KHz, tetapi Anda harus mengurangi frekuensinya menjadi 1 Hz dengan cara lain. Pada awalnya saya mencoba melakukan ini menggunakan blok dari Altera yang disebutALTCLKCTRL , tetapi karena alasan tertentu tidak berhasil. Kemudian saya mencoba untuk membagi sinyal clock menggunakan penghitung, tetapi (saya sudah tahu itu) solusi ini dengan sendirinya tidak bekerja, karena synthesizer tidak mengerti bahwa sinyal output adalah sinyal clock dan mulai membaginya secara salah, akibatnya prosesor tidak bekerja. Saya berkonsultasi dengan beberapa kawan dan kami mulai menggunakan makro Alter "global" (dan setara dengan Xilinx BUFG). 5. Menambahkan lab visualisasi miss cache sederhana Sekarang Anda dapat melakukan percobaan yang menarik - misalnya, untuk membuat LED berkedip selama cache hilang, dan kemudian mengamati secara real time klik dan hilang cache saat mengisi array dua dimensi. Jika Anda mengisi baris demi baris array, maka kedipan akan berbeda dari jika Anda mengisi kolom: Perlu dicatat bahwa tidak semuanya berjalan lancar:

Sekarang Anda dapat melakukan percobaan yang menarik - misalnya, untuk membuat LED berkedip selama cache hilang, dan kemudian mengamati secara real time klik dan hilang cache saat mengisi array dua dimensi. Jika Anda mengisi baris demi baris array, maka kedipan akan berbeda dari jika Anda mengisi kolom: Perlu dicatat bahwa tidak semuanya berjalan lancar: 1. GPIO di DE0-Nano berbeda dari GPIO di DE0-CV dan papan Xilinx. Secara khusus, untuk beberapa alasan saya tidak dapat mendeklarasikan seluruh port GPIO sebagai satu masukan dan kemudian menggunakan bit individualnya sebagai input atau sebagai output. Meskipun pada DE0-CV ini berjalan dengan baik. Saya tidak punya waktu untuk membagi keluaran GPIO yang berbeda antara sinyal logis yang berbeda (pada Verilog), jadi saya tidak menyortir laboratorium dengan sensor cahaya pada DE0-Nano. Untuk alasan yang sama, saya tidak mengekspor antarmuka dengan Bus Blaster ke DE0-CV.2. Lebih buruk lagi, mengunduh melalui UART untuk DE0-Nano tidak bekerja di MEPhI, meskipun sebelumnya itu bekerja di Moscow State University dan di laptop saya. Alasannya masih belum jelas 100%:2.1. Mungkin ada masalah ketidakcocokan versi Windows (7 dengan patch) dan kabel USB-to-UART yang digunakan untuk DE0-Nano. Kabelnya adalah kloning kabel murah dari Cina yang didasarkan pada chipset PL2303TA, meskipun saya belum mencobanya sebelum seminar. Diketahui bahwa versi sebelumnya dari kabel semacam itu yang didasarkan pada chipset dengan PL2303HX memiliki masalah kompatibilitas dengan Windows 8 ( lihat ). Yang paling keji yang saya miliki dengan saya laptop dengan versi Windows 7, dan laptop dengan versi Windows 8, dan berbagai alternatif untuk kabel ini. Tetapi saya tidak memeriksa semua kombinasi sebelum seminar, meskipun saya bisa melakukannya malam sebelumnya - sayangnya.2.2. Dua hari sebelum lokakarya, saya membuat perubahan pada pembagi jam. Itu tidak layak dilakukan juga.2.3. Yah, setidaknya semuanya bekerja dengan baik pada DE0-CV.3. Di MEPhI, saya menunjukkan versi contoh cache yang lebih kompleks daripada sebelumnya di Moscow State University. Itu adalah kesalahan - dalam contoh kompleks, kompiler mengoptimalkan sesuatu, dan pola lampu tidak sejelas pada contoh sederhana asli. Situasi ini agak diselamatkan oleh pembicara tambahan yang diundang dari NIIMI Anton Pavlov, yang, meskipun ia tidak punya waktu di MEPhI, menunjukkan beberapa presentasinya sendiri tentang ikatan MIPSfpga yang disebut myMIPSfpga, yang ia juga gambarkan dalam catatan "MIPSfpga: di luar kanon . " Antara lain, Anton telah mengirim MIPSfpga ke papan Rusia rover 3 Mars

1. GPIO di DE0-Nano berbeda dari GPIO di DE0-CV dan papan Xilinx. Secara khusus, untuk beberapa alasan saya tidak dapat mendeklarasikan seluruh port GPIO sebagai satu masukan dan kemudian menggunakan bit individualnya sebagai input atau sebagai output. Meskipun pada DE0-CV ini berjalan dengan baik. Saya tidak punya waktu untuk membagi keluaran GPIO yang berbeda antara sinyal logis yang berbeda (pada Verilog), jadi saya tidak menyortir laboratorium dengan sensor cahaya pada DE0-Nano. Untuk alasan yang sama, saya tidak mengekspor antarmuka dengan Bus Blaster ke DE0-CV.2. Lebih buruk lagi, mengunduh melalui UART untuk DE0-Nano tidak bekerja di MEPhI, meskipun sebelumnya itu bekerja di Moscow State University dan di laptop saya. Alasannya masih belum jelas 100%:2.1. Mungkin ada masalah ketidakcocokan versi Windows (7 dengan patch) dan kabel USB-to-UART yang digunakan untuk DE0-Nano. Kabelnya adalah kloning kabel murah dari Cina yang didasarkan pada chipset PL2303TA, meskipun saya belum mencobanya sebelum seminar. Diketahui bahwa versi sebelumnya dari kabel semacam itu yang didasarkan pada chipset dengan PL2303HX memiliki masalah kompatibilitas dengan Windows 8 ( lihat ). Yang paling keji yang saya miliki dengan saya laptop dengan versi Windows 7, dan laptop dengan versi Windows 8, dan berbagai alternatif untuk kabel ini. Tetapi saya tidak memeriksa semua kombinasi sebelum seminar, meskipun saya bisa melakukannya malam sebelumnya - sayangnya.2.2. Dua hari sebelum lokakarya, saya membuat perubahan pada pembagi jam. Itu tidak layak dilakukan juga.2.3. Yah, setidaknya semuanya bekerja dengan baik pada DE0-CV.3. Di MEPhI, saya menunjukkan versi contoh cache yang lebih kompleks daripada sebelumnya di Moscow State University. Itu adalah kesalahan - dalam contoh kompleks, kompiler mengoptimalkan sesuatu, dan pola lampu tidak sejelas pada contoh sederhana asli. Situasi ini agak diselamatkan oleh pembicara tambahan yang diundang dari NIIMI Anton Pavlov, yang, meskipun ia tidak punya waktu di MEPhI, menunjukkan beberapa presentasinya sendiri tentang ikatan MIPSfpga yang disebut myMIPSfpga, yang ia juga gambarkan dalam catatan "MIPSfpga: di luar kanon . " Antara lain, Anton telah mengirim MIPSfpga ke papan Rusia rover 3 Mars yang saya, sebagai orang yang disiksa oleh ekspor-impor (Scylla: kontrol ekspor Amerika + Charybdis: bea cukai Rusia), saya akan mencoba menggunakan untuk acara pendidikan berikut di Rusia: Selama istirahat dan setelah seminar, Maxim Gorbunov menunjukkan kepada saya berbagai pemandangan mistis, yang meliputi tiga panel dalam semangat era Galaksi Andromeda dan Molecular Cafe multi-volume merah dan putih berasal dari 1960: UPD: Seperti dalam komentar mulai membahas gereja mifishnuyu, dan saya akan membuat tentang hal itu (saya tidak dimasukkan l Fragmen ini aslinya, karena ia tidak yakin apakah itu sesuai untuk geektimes):

yang saya, sebagai orang yang disiksa oleh ekspor-impor (Scylla: kontrol ekspor Amerika + Charybdis: bea cukai Rusia), saya akan mencoba menggunakan untuk acara pendidikan berikut di Rusia: Selama istirahat dan setelah seminar, Maxim Gorbunov menunjukkan kepada saya berbagai pemandangan mistis, yang meliputi tiga panel dalam semangat era Galaksi Andromeda dan Molecular Cafe multi-volume merah dan putih berasal dari 1960: UPD: Seperti dalam komentar mulai membahas gereja mifishnuyu, dan saya akan membuat tentang hal itu (saya tidak dimasukkan l Fragmen ini aslinya, karena ia tidak yakin apakah itu sesuai untuk geektimes):

Saya pergi ke gereja mitos, di mana ada begitu banyak jeritan di Internet sekitar tiga tahun yang lalu, karena itu karyawan bahkan meninggalkan Institut Teknik Fisika Moskow sebagai protes. Sebagai orang yang netral, mis. seorang yang benar-benar tidak percaya, bukan pendukung militan dari satu atau sisi lain dari konflik, saya harus mengatakan bahwa 1) gereja mitos agak sederhana dan tidak vulgar, serupa semangatnya dengan Katedral Ortodoks di San Francisco; 2) MEPhI bukan universitas Rusia pertama dengan agama, kursus Ortodoksi muncul di Institut Fisika dan Teknologi Moskow pada tahun 1988 (kemudian seluruh perguruan tinggi fisika dan teknologi datang kepadanya, para siswa mendengarkan ceramah pertama berdiri, tetapi setelah tiga bulan tidak ada lagi selusin siswa yang tersisa); 3) ada banyak gereja di universitas-universitas Amerika. Bersambung.

Saya pergi ke gereja mitos, di mana ada begitu banyak jeritan di Internet sekitar tiga tahun yang lalu, karena itu karyawan bahkan meninggalkan Institut Teknik Fisika Moskow sebagai protes. Sebagai orang yang netral, mis. seorang yang benar-benar tidak percaya, bukan pendukung militan dari satu atau sisi lain dari konflik, saya harus mengatakan bahwa 1) gereja mitos agak sederhana dan tidak vulgar, serupa semangatnya dengan Katedral Ortodoks di San Francisco; 2) MEPhI bukan universitas Rusia pertama dengan agama, kursus Ortodoksi muncul di Institut Fisika dan Teknologi Moskow pada tahun 1988 (kemudian seluruh perguruan tinggi fisika dan teknologi datang kepadanya, para siswa mendengarkan ceramah pertama berdiri, tetapi setelah tiga bulan tidak ada lagi selusin siswa yang tersisa); 3) ada banyak gereja di universitas-universitas Amerika. Bersambung.

Source: https://habr.com/ru/post/id387157/

All Articles