Distribusi gajah: papan FPGA untuk proyek pendidikan dengan MIPSfpga

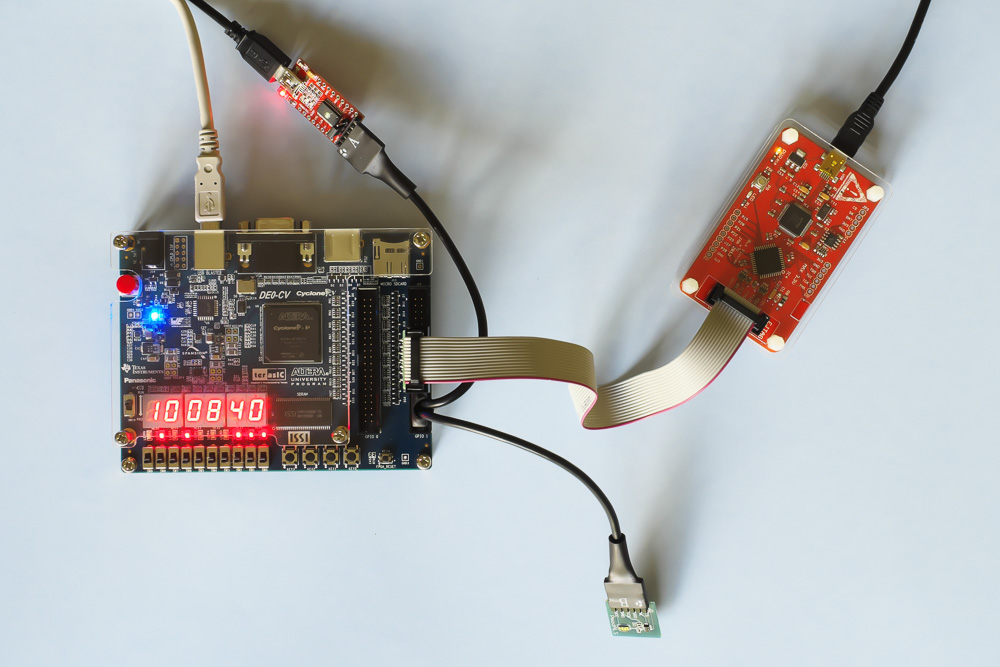

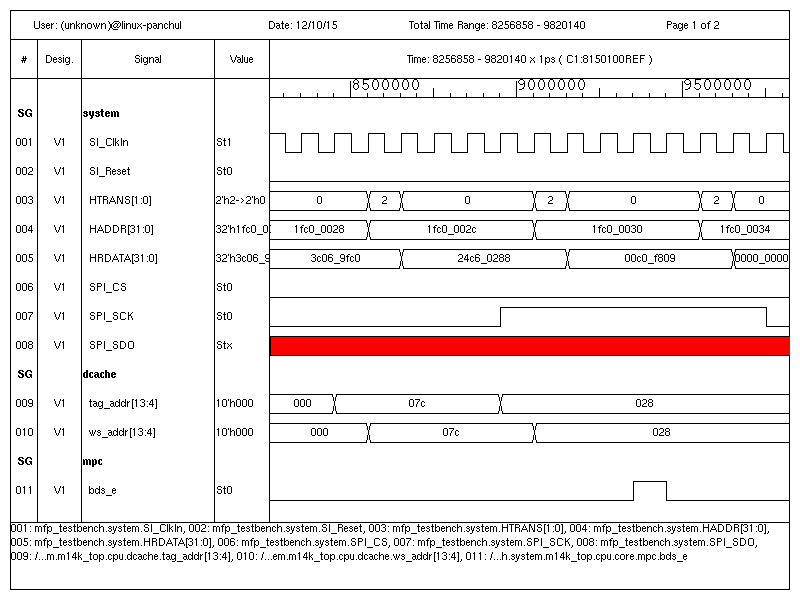

Sebulan yang lalu, seminar tentang MIPSfpga ( 1 , 2 , 3 , 4 ) diadakan di universitas-universitas Rusia , dan seorang pria dari NIIIS bernama Anton Pavlov menulis catatan tentang perbaikannya sendiri MIPSfpga "MIPSfpga: di luar kanon . " Karena para profesor bertemu dengan produk baru untuk mengajar siswa elektronik secara keseluruhan secara positif, muncul ide untuk membantu memulai dengan papan, dan pada saat yang sama dengan beberapa orang dan organisasi.Secara khusus, untuk menghormati Tahun Baru, saya bekerja sama dengan Vitaliy Kravchenko dari univeda.ruKami sedang merencanakan distribusi kecil gajah, yaitu, papan DE0-CV Terasic gratis dengan FPGA Altera Cyclone V. Sehingga Anda dapat mengulangi perbuatan Anton Pavlov. Karena distribusi khusus ini dilakukan _ tidak_ dengan uang Teknologi Imajinasi, bukan dengan uang Altera dan bukan dengan uang Pusat Ilmiah dan Produksi Elvis, tetapi dengan uang donatur swasta, termasuk saya secara pribadi, gajah akan didistribusikan dengan kondisi agak spesifik yang dijelaskan di bawah ini. Tujuan acara: 1. Untuk meningkatkan tingkat keterlibatan universitas Rusia dalam penelitian dunia di bidang mikroarsitektur prosesor, desain SoCs dan sistem multi-core heterogen 2. Untuk meningkatkan jumlah teks Rusia tentang MIPS Insider sehingga pengunjung dari industri elektronik dan akademisi internasional mulai memahami bahwa Rusia akan datang bahwa Rusia akan datang 3. Untuk membuat, atas nama masyarakat, banyak materi pelatihan di sekitar MIPSfpga, yang dapat digunakan oleh para guru universitas Rusia dan profesor universitas di negara lain - AS, Jepang, Cina, dll.Ketentuan:1. Diinginkan bahwa penerima pembayaran menjadi guru, mahasiswa pascasarjana atau mahasiswa universitas Rusia.2. Diharapkan bahwa universitas ini bukan Universitas Negeri Moskow, Institut Fisika dan Teknologi Moskow, MEPhI, MIET dan ITMO, yang dapat menerima biaya ini dari sumber lain.3. Sangat diinginkan bahwa sebelum menerima papan, seorang teman kreatif tidak hanya akan mengirim saya deskripsi proyek, tetapi juga kode dalam Verilog atau VHDL, C dan / atau assembler, yang dengannya ia mensimulasikan prototipe sistem yang disintesis di masa depan dalam lingkungan ModelSim atau Icarus. Diagram waktu juga dapat diterima.4. Kode proyek setelah selesai diunggah ke http://github.com/MIPSfpga - lihat http://github.com/MIPSfpga/mipsfpga-plus5 sebagai contoh, juga dijelaskan di bagian Wiki:5.1. Apa yang ada di setiap file5.2. Hierarki modul perangkat keras5.3. Cara mensimulasikan - instruksi dengan tangkapan layar5.4. Diagram waktu simulasi5.5. Cara mensintesis - instruksi dengan tangkapan layar5.6. Hasil sintesis - ukuran dan frekuensi maksimum5.7. Deskripsi bagian perangkat lunak5.8. Foto-foto FPGA yang berfungsi6. Ini diletakkan di http://geektimes.ru dalam bentuk artikel7. Hal yang sama juga tercantum di http://silicon-russia.com8. Hal yang sama juga diungkapkan di http://community.imgtec.com / forum / cat / mips-insider / mipsfpga9. Bahasa (6), (7), (8) dapat berupa bahasa Rusia atau Inggris10. Jika Anda tidak melakukan apa pun dengan papan selama sebulan, itu ditarik dari Anda dan ditransfer ke orang lain11. Jika kami (Saya dan UnivEDA) akan melakukan acara apa pun di Rusia seperti kompetisi atau pelatihan, kami juga akan membebankan biaya kepada Anda. mengambil waktu kembaliContoh proyek dengan papan:1. Antarmuka antara MIPSfpga dan sensor dengan antarmuka SPI, I2C, UART dan lain-lain. Sensor untuk kelembaban, suhu, suara, kompas, pengintai, dll.2. Antarmuka antara MIPSfpga dan eksternal terkait dengan memori FPGA - SDRAM, DDR, dll. (dalam contoh saat ini, memori sistem dibangun dari blok memori di dalam FPGA)3. Antarmuka antara MIPSfpga dan perangkat yang lebih besar adalah layar VGA, mouse, keyboard, joystick.4. Visualisasi cache dengan menjalankan prosesor pada frekuensi 1 jam per detik dan mengeluarkan sinyal yang terkait dengan transaksi (permintaan, kehilangan, dll.).5. Visualisasi operasi konveyor dan perangkat aritmatika dengan memulai prosesor dengan frekuensi 1 jam per detik dan mengeluarkan sinyal kontrol konveyor, dll.6. Menambahkan perintah ke prosesor menggunakan antarmuka CorExtend / User Defined Instructions (UDI). Contohnya adalah perintah enkripsi khusus.7. Pekerjaan laboratorium dengan demonstrasi operasi interupsi dalam mode yang berbeda dan penangan interupsi.8. Jembatan antara bus AHB-Lite dan bus lainnya - AXI, APB, OCP, Wishbone, PLB, dll.9. Sistem multiprosesor tanpa koherensi cache tingkat pertama dan (untuk yang paling canggih) dengan cache koheren dan implementasi protokol seperti MESI.10. Porting ke MIPSfpga berbagai program dan sistem operasi - dari RTOS sederhana ke berbagai varian Linux (MIPSfpga mendukung TLB MMU).Silakan kirim saran ke yuri.panchul@imgtec.com dengan salinan yuri@panchul.com

3. Untuk membuat, atas nama masyarakat, banyak materi pelatihan di sekitar MIPSfpga, yang dapat digunakan oleh para guru universitas Rusia dan profesor universitas di negara lain - AS, Jepang, Cina, dll.Ketentuan:1. Diinginkan bahwa penerima pembayaran menjadi guru, mahasiswa pascasarjana atau mahasiswa universitas Rusia.2. Diharapkan bahwa universitas ini bukan Universitas Negeri Moskow, Institut Fisika dan Teknologi Moskow, MEPhI, MIET dan ITMO, yang dapat menerima biaya ini dari sumber lain.3. Sangat diinginkan bahwa sebelum menerima papan, seorang teman kreatif tidak hanya akan mengirim saya deskripsi proyek, tetapi juga kode dalam Verilog atau VHDL, C dan / atau assembler, yang dengannya ia mensimulasikan prototipe sistem yang disintesis di masa depan dalam lingkungan ModelSim atau Icarus. Diagram waktu juga dapat diterima.4. Kode proyek setelah selesai diunggah ke http://github.com/MIPSfpga - lihat http://github.com/MIPSfpga/mipsfpga-plus5 sebagai contoh, juga dijelaskan di bagian Wiki:5.1. Apa yang ada di setiap file5.2. Hierarki modul perangkat keras5.3. Cara mensimulasikan - instruksi dengan tangkapan layar5.4. Diagram waktu simulasi5.5. Cara mensintesis - instruksi dengan tangkapan layar5.6. Hasil sintesis - ukuran dan frekuensi maksimum5.7. Deskripsi bagian perangkat lunak5.8. Foto-foto FPGA yang berfungsi6. Ini diletakkan di http://geektimes.ru dalam bentuk artikel7. Hal yang sama juga tercantum di http://silicon-russia.com8. Hal yang sama juga diungkapkan di http://community.imgtec.com / forum / cat / mips-insider / mipsfpga9. Bahasa (6), (7), (8) dapat berupa bahasa Rusia atau Inggris10. Jika Anda tidak melakukan apa pun dengan papan selama sebulan, itu ditarik dari Anda dan ditransfer ke orang lain11. Jika kami (Saya dan UnivEDA) akan melakukan acara apa pun di Rusia seperti kompetisi atau pelatihan, kami juga akan membebankan biaya kepada Anda. mengambil waktu kembaliContoh proyek dengan papan:1. Antarmuka antara MIPSfpga dan sensor dengan antarmuka SPI, I2C, UART dan lain-lain. Sensor untuk kelembaban, suhu, suara, kompas, pengintai, dll.2. Antarmuka antara MIPSfpga dan eksternal terkait dengan memori FPGA - SDRAM, DDR, dll. (dalam contoh saat ini, memori sistem dibangun dari blok memori di dalam FPGA)3. Antarmuka antara MIPSfpga dan perangkat yang lebih besar adalah layar VGA, mouse, keyboard, joystick.4. Visualisasi cache dengan menjalankan prosesor pada frekuensi 1 jam per detik dan mengeluarkan sinyal yang terkait dengan transaksi (permintaan, kehilangan, dll.).5. Visualisasi operasi konveyor dan perangkat aritmatika dengan memulai prosesor dengan frekuensi 1 jam per detik dan mengeluarkan sinyal kontrol konveyor, dll.6. Menambahkan perintah ke prosesor menggunakan antarmuka CorExtend / User Defined Instructions (UDI). Contohnya adalah perintah enkripsi khusus.7. Pekerjaan laboratorium dengan demonstrasi operasi interupsi dalam mode yang berbeda dan penangan interupsi.8. Jembatan antara bus AHB-Lite dan bus lainnya - AXI, APB, OCP, Wishbone, PLB, dll.9. Sistem multiprosesor tanpa koherensi cache tingkat pertama dan (untuk yang paling canggih) dengan cache koheren dan implementasi protokol seperti MESI.10. Porting ke MIPSfpga berbagai program dan sistem operasi - dari RTOS sederhana ke berbagai varian Linux (MIPSfpga mendukung TLB MMU).Silakan kirim saran ke yuri.panchul@imgtec.com dengan salinan yuri@panchul.com

Source: https://habr.com/ru/post/id387803/

All Articles