Kata Pengantar

Saya sangat senang untuk menceritakan secara terperinci tentang sirkuit terintegrasi pertama saya dan berbagi tikungan dan belokan proyek ini, yang saya lakukan selama setahun terakhir. Saya berharap kesuksesan saya akan menginspirasi orang lain dan membantu memulai revolusi dalam produksi keripik rumah. Ketika saya memulai proyek ini, saya tidak tahu apa yang saya lakukan, tetapi pada akhirnya saya belajar lebih banyak daripada yang pernah saya pikirkan tentang fisika, kimia, optik, elektronik dan banyak bidang lainnya.

Selain itu, upaya saya hanya disertai dengan ulasan dan dukungan paling positif dari seluruh dunia. Saya dengan tulus berterima kasih kepada semua orang yang membantu saya, memberikan saran dan menginspirasi untuk proyek ini. Terutama kepada orang tua saya yang luar biasa yang tidak hanya selalu mendukung dan mendorong saya sesegera mungkin, tetapi juga telah menyediakan tempat kerja dan memasang biaya listrik ... Terima kasih!

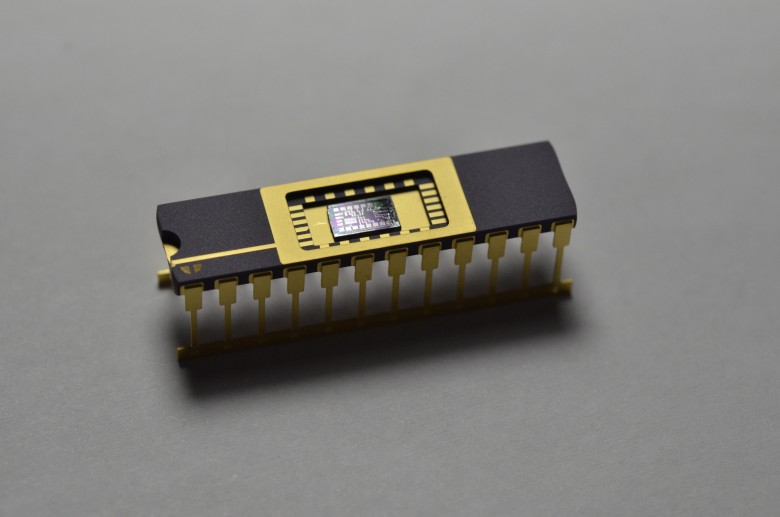

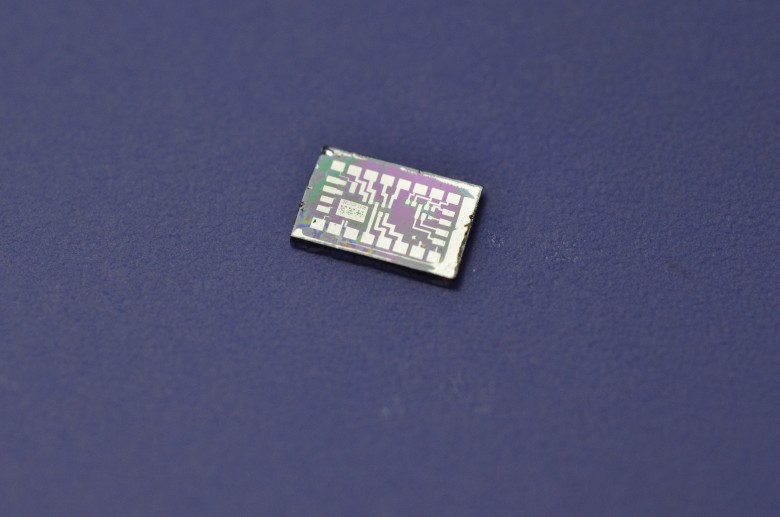

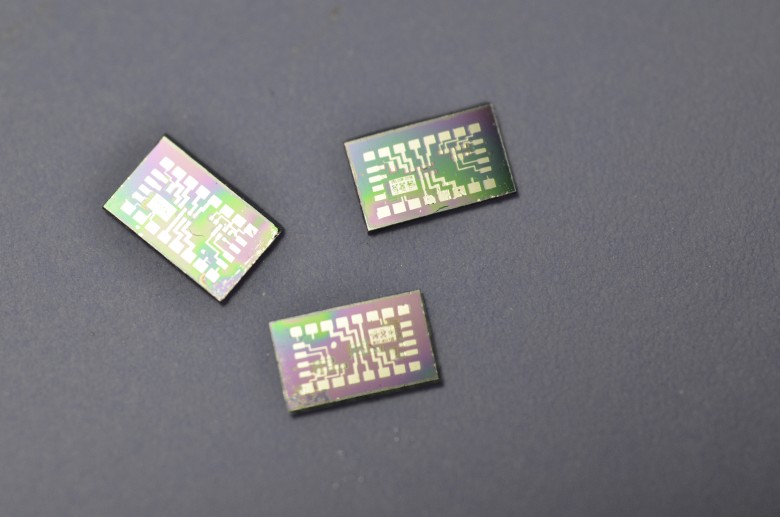

Tanpa basa-basi lagi, saya menghadirkan sirkuit terintegrasi pertama (IC) yang diproduksi dengan metode litografi di rumah (garasi) kondisi - chip PMOS dari penguat diferensial ganda Z1.

Saya katakan "dibuat dengan metode litograf" karena Jerry Ellsworth membuat transistor dan gerbang logika pertama (dengan koneksi yang diletakkan dengan hati-hati menggunakan epoksi pengolah tangan) dan menunjukkan kepada dunia bahwa ini mungkin. Terinspirasi oleh karyanya, saya menghadirkan sirkuit terintegrasi yang diciptakan oleh proses fotolitografi standar yang dapat diskalakan. Tak perlu dikatakan, ini adalah langkah maju yang logis dibandingkan dengan pekerjaan saya sebelumnya, di mana saya

mereproduksi transistor efek medan Jerry .

Desain

Saya

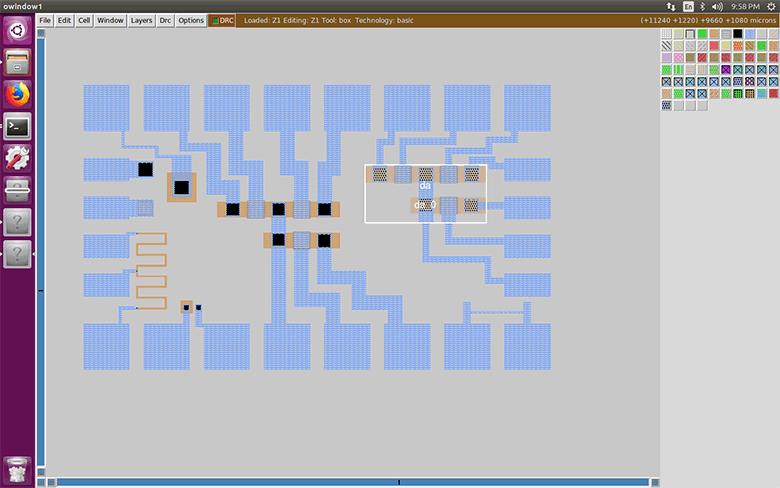

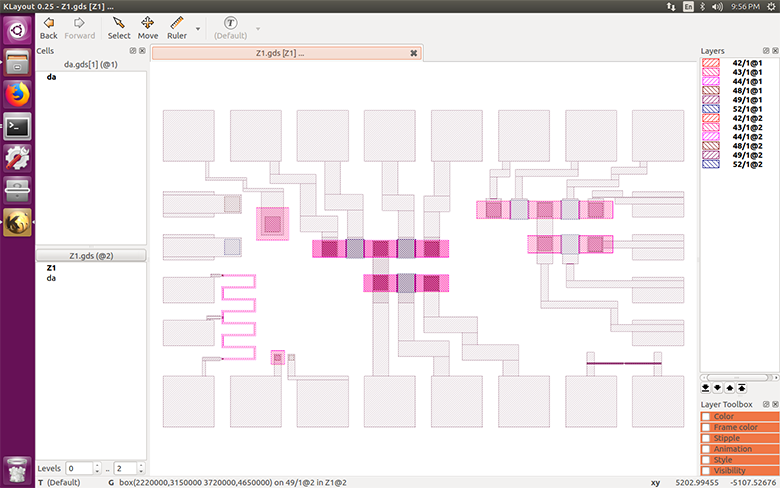

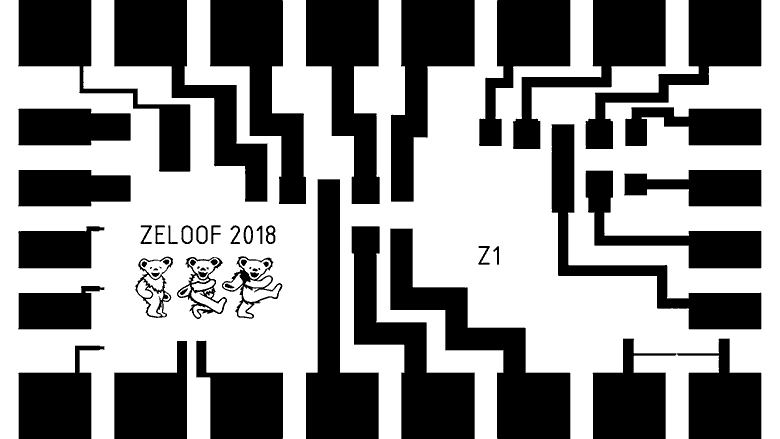

mengembangkan amplifier Z1 ketika saya mencari chip sederhana untuk menguji dan menyesuaikan proses saya. Tata letak dibuat di

Magic VLSI untuk proses PMOS dengan empat topeng (wilayah aktif / didoping, oksida gerbang, jendela kontak dan lapisan logam atas). PMOS memiliki keunggulan dibandingkan NMOS ketika mempertimbangkan pengotor ion karena pembuatan di garasi. Masker dirancang dengan rasio aspek 16: 9 untuk menyederhanakan proyeksi.

Tata Letak VLSI Ajaib

Tata Letak VLSI Ajaib Generasi topeng

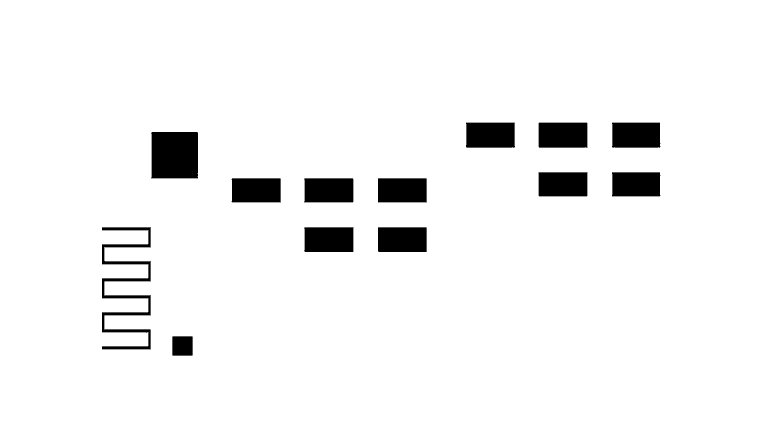

Generasi topeng Area aktif

Area aktif Bidik

Bidik Kontak

Kontak Logam

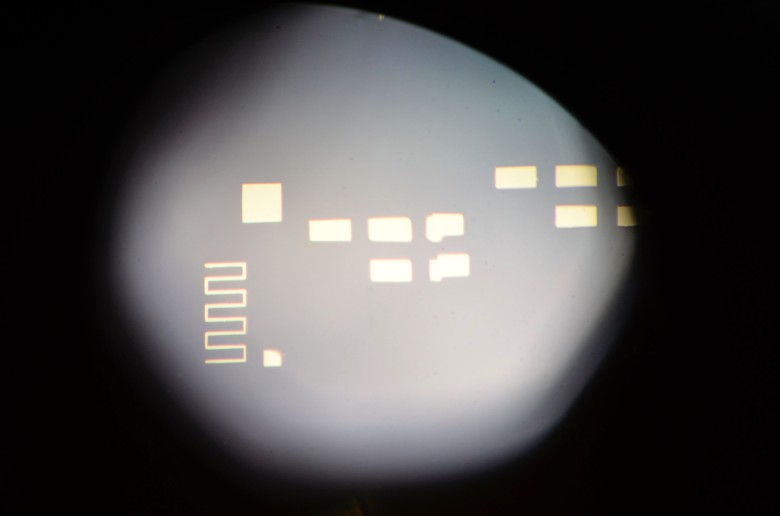

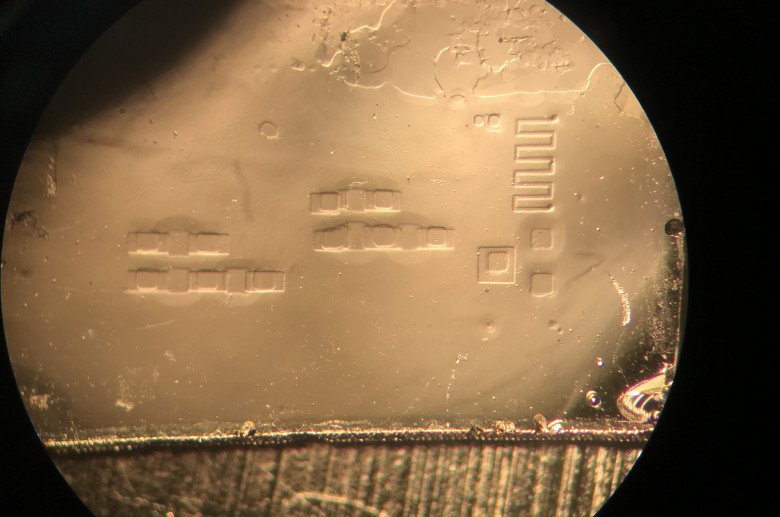

LogamUkuran rana sekitar 175 mikron, meskipun elemen berukuran hingga 2 mikron dibuat pada chip untuk verifikasi. Setiap bagian penguat (tengah dan kanan) berisi tiga transistor (dua untuk rangkaian

dorong-tarik dengan resistansi katoda umum dan satu sebagai penghambat sumber / beban saat ini), yang berarti total enam transistor per IC. Sisi kiri resistor, kapasitor, dioda, dan elemen uji lainnya untuk mempelajari karakteristik proses. Setiap node dari pasangan diferensial keluar dengan pin terpisah pada kerangka output, sehingga dapat dipelajari, dan jika perlu, tambahkan offset eksternal.

Pembuatan

Proses pembuatan terdiri dari 66 langkah individu dan memakan waktu sekitar 12 jam. Hasil panen mencapai 80% untuk barang-barang besar, tetapi sangat tergantung pada jumlah kopi yang Anda minum pada hari tertentu. Saya juga merekam video di YouTube tentang

teori produksi sirkuit mikro, dan

tentang pembuatan transistor MOS secara terpisah .

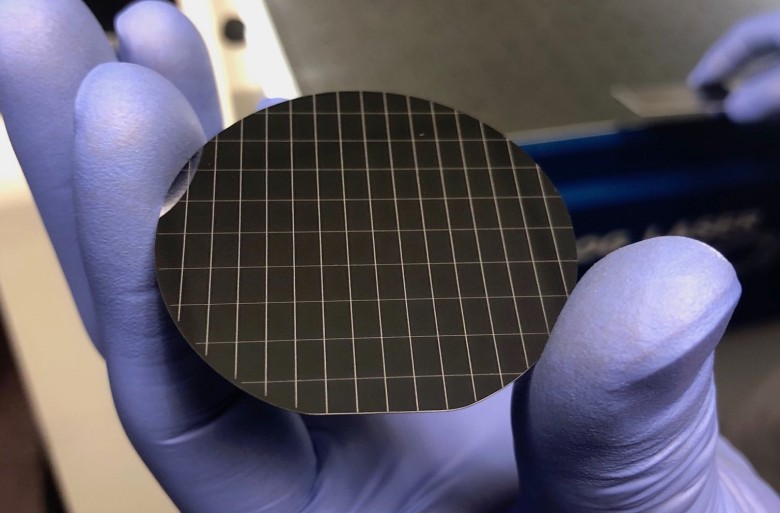

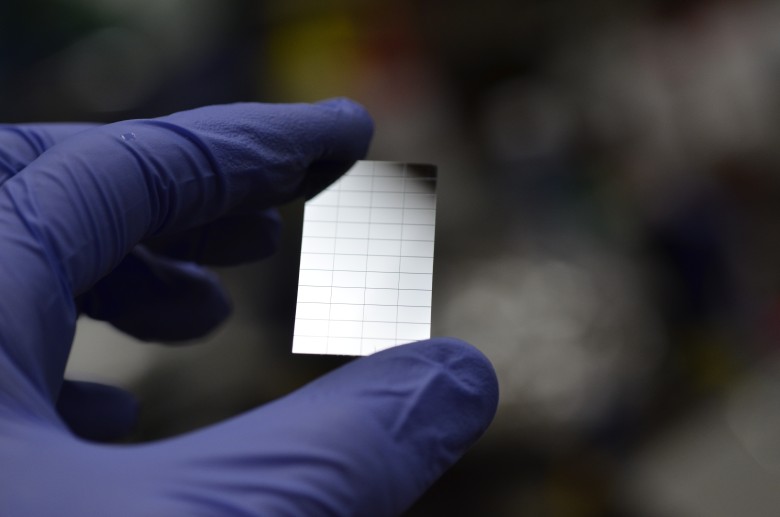

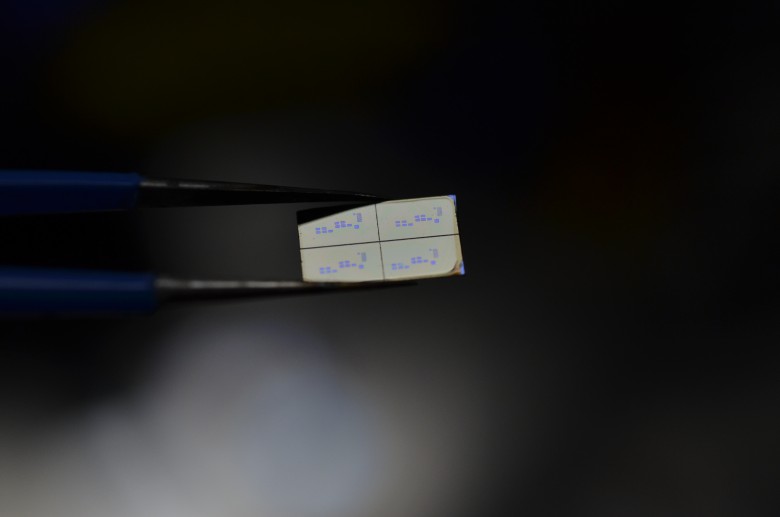

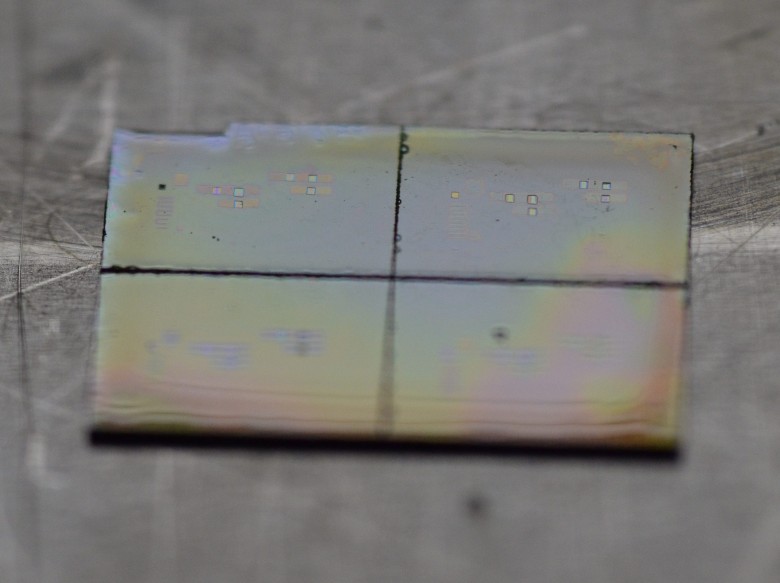

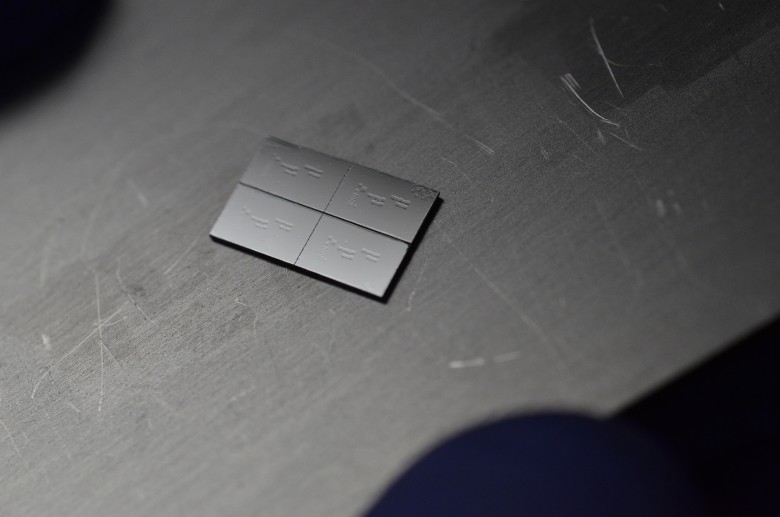

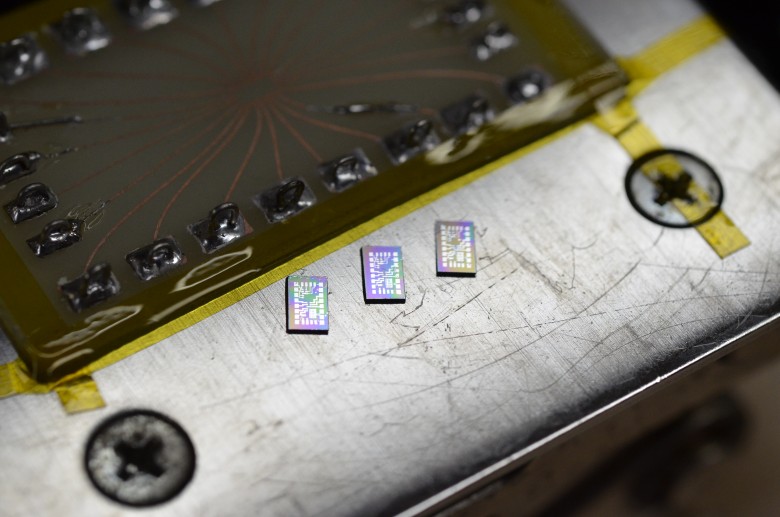

50 mm (2 ") wafer silikon dipecah menjadi kristal 5,08 x 3,175 mm (sekitar 16 mm²)

dengan laser serat Epilog . Ukuran kristal dipilih agar sesuai dengan paket DIP 24-pin Kyocera.

Plat tipe N 50 mm

Plat tipe N 50 mm Plat tipe N 50 mm

Plat tipe N 50 mmPertama, oksida asli dikeluarkan dari pelat dengan perendaman cepat dalam hidrogen fluorida encer, diikuti dengan perawatan intensif dengan campuran etsa piranha (campuran asam sulfat dan hidrogen peroksida), campuran RCA 1 (air, amonia, hidrogen peroksida), campuran RCA 2 (air, asam klorida, hidrogen peroksida) dan perendaman berulang dalam hidrogen fluorida.

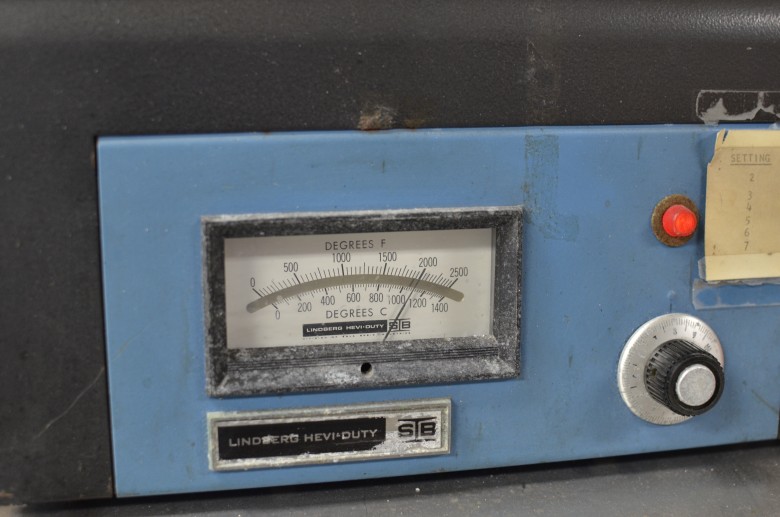

Oksida pelindung

ditumbuhkan secara termal dalam uap air dari udara sekitar (oksidasi basah) hingga ketebalan 5.000-8.000 Å.

Oksidasi Termal Basah

Oksidasi Termal Basah Oksidasi Termal Basah

Oksidasi Termal Basah Tabung tungku

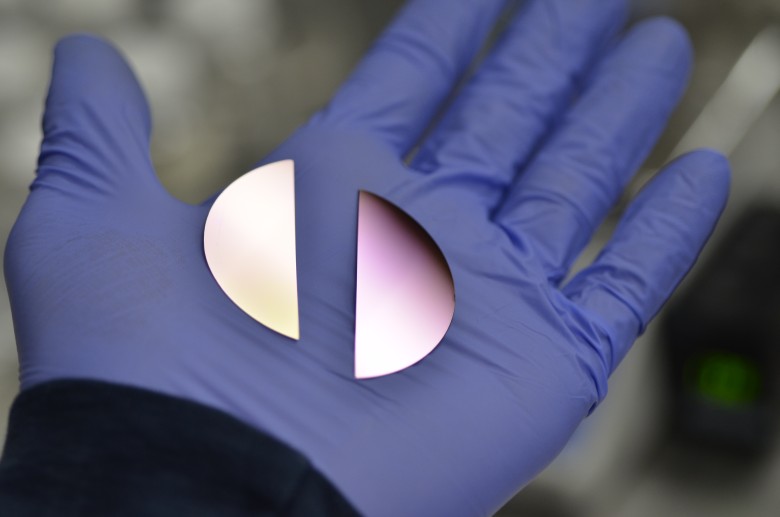

Tabung tungku Piring teroksidasi

Piring teroksidasiPlat teroksidasi siap dibentuk di daerah aktif / didoping (tipe-P). The photoresist

AZ4210 diterapkan pada

payudara berputar pada sekitar 3000 rpm, membentuk film sekitar 3,5 mikron tebal, yang dikeringkan dengan lembut pada 90 ° C di atas piring panas.

Proses litografi secara terperinciTopeng inti diproses oleh

stepper photolithographic saya

Mark IV dalam ultraviolet dengan langkah 365 nm - dan strukturnya dikerjakan dalam larutan kalium hidroksida.

Tolak struktur

Tolak struktur Tolak struktur

Tolak struktur 30 menit pengeringan

30 menit pengeringan Etsa Inti

Etsa IntiSetelah ini, struktur tahanan dipadatkan dan

beberapa trik lainnya digunakan untuk memastikan adhesi yang baik dan ketahanan kimia selama etsa hidrogen fluorida berikutnya, yang mentransfer struktur ini ke lapisan oksida gerbang dan membuka jendela untuk telanjang silikon untuk doping. Daerah-daerah ini nantinya akan menjadi sumber dan tiriskan dari transistor.

Partikel menutup rana

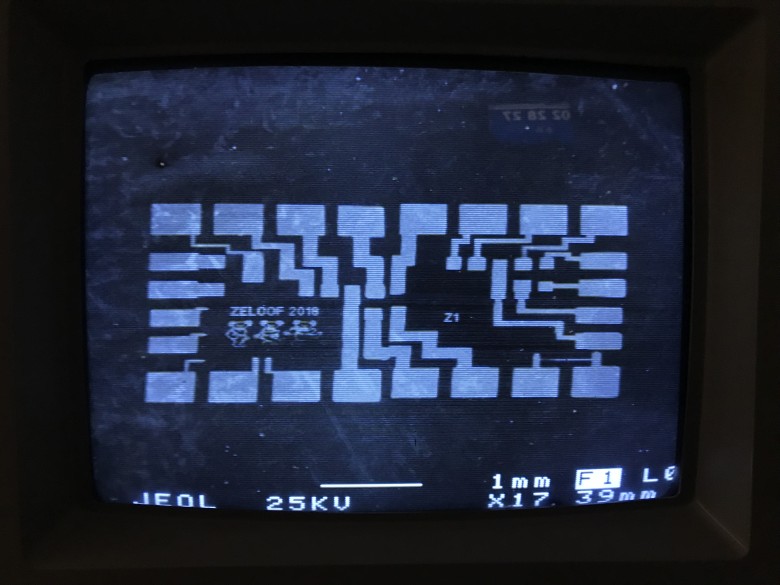

Partikel menutup rana Paduan kristal dengan gerbang terukir

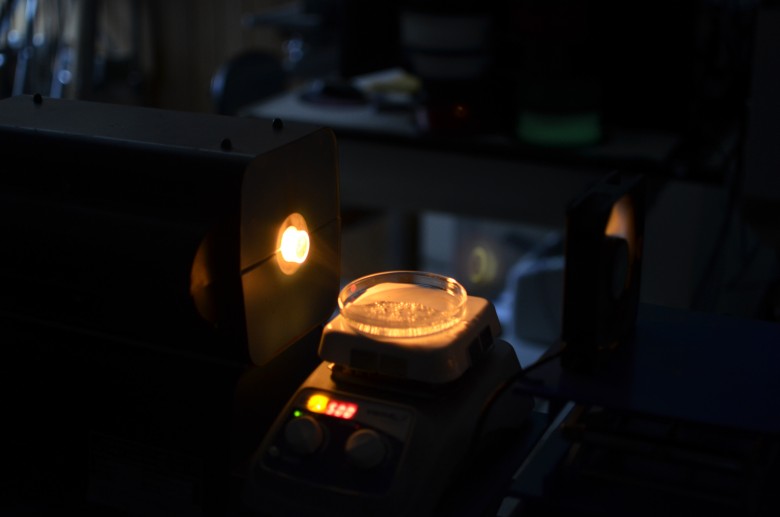

Paduan kristal dengan gerbang terukirSetelah ini, paduan dilakukan, yaitu pengenalan kotoran dari sumber padat atau cair. Sebagai sumber padat, disk boron nitrida digunakan, terletak di dekatnya (kurang dari 2 mm) dari pelat dalam tungku tabung. Sebagai alternatif, Anda dapat menyiapkan sumber cairan asam fosfat atau borat dalam air atau pelarut - dan menggunakan obat sesuai dengan proses standar

pra-aplikasi / perendaman dalam hidrogen fluorida / difusi / penghilangan glasir .

Langkah-langkah pola di atas kemudian diulang dua kali untuk oksida gerbang dan lapisan kontak. Gerbang oksida harus jauh lebih tipis (kurang dari ~ 750 Å) daripada oksida pelindung, sehingga zona antara saluran / sumber tergores - dan oksida yang lebih tipis tumbuh di sana. Kemudian, karena seluruh pelat dioksidasi pada langkah doping, jendela kontak harus dietsa untuk membuat kontak lapisan logam dengan zona sumber / saluran pembuangan.

Sekarang semua transistor dibentuk dan siap untuk interkoneksi dengan akses ke kerangka output. Lapisan pelindung aluminium (400-500 nm)

disemprotkan atau

disemprotkan secara termal ke piring. Alternatifnya adalah proses pengangkatan, ketika photoresist pertama kali dibentuk dan kemudian logam diendapkan.

Logam disemprotkan

Logam disemprotkan Logam disemprotkan

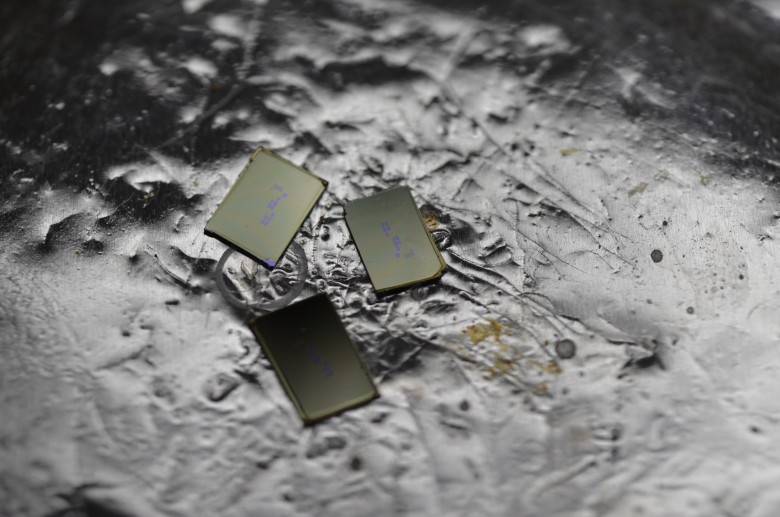

Logam disemprotkanKemudian, pola fotolitografi terbentuk pada lapisan logam dan terukir dalam asam fosfat panas terjadi untuk menyelesaikan pembuatan sirkuit terpadu. Langkah terakhir sebelum pengujian adalah inspeksi visual dan pelunakan aluminium suhu tinggi untuk membentuk persimpangan ohmik.

Chip sekarang siap untuk pengemasan dan pengujian.

Saya tidak memiliki instalasi microwelder (saya menerima donasi!), Jadi sekarang proses pengujian terbatas untuk meraba pelat dengan pinset tajam atau menggunakan papan flip-chip (sulit untuk disejajarkan) dengan koneksi ke karakterograf. Penguat diferensial juga diuji secara empiris di sirkuit untuk memverifikasi operabilitas.

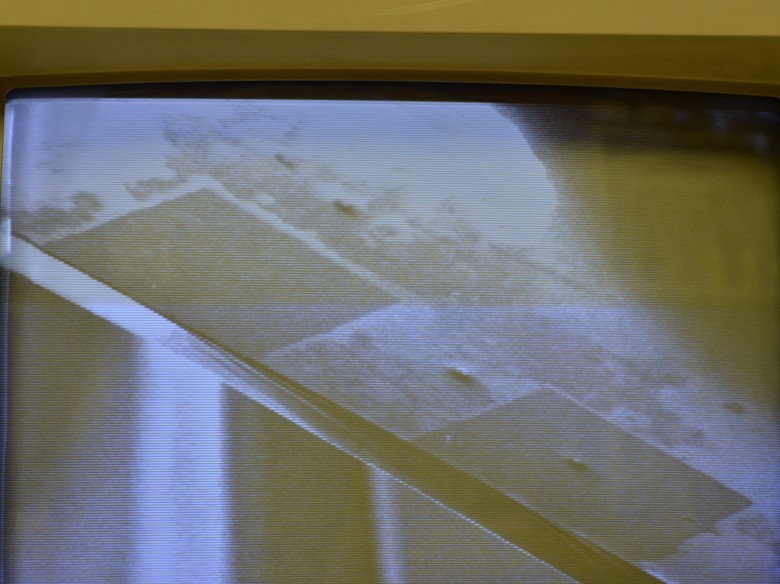

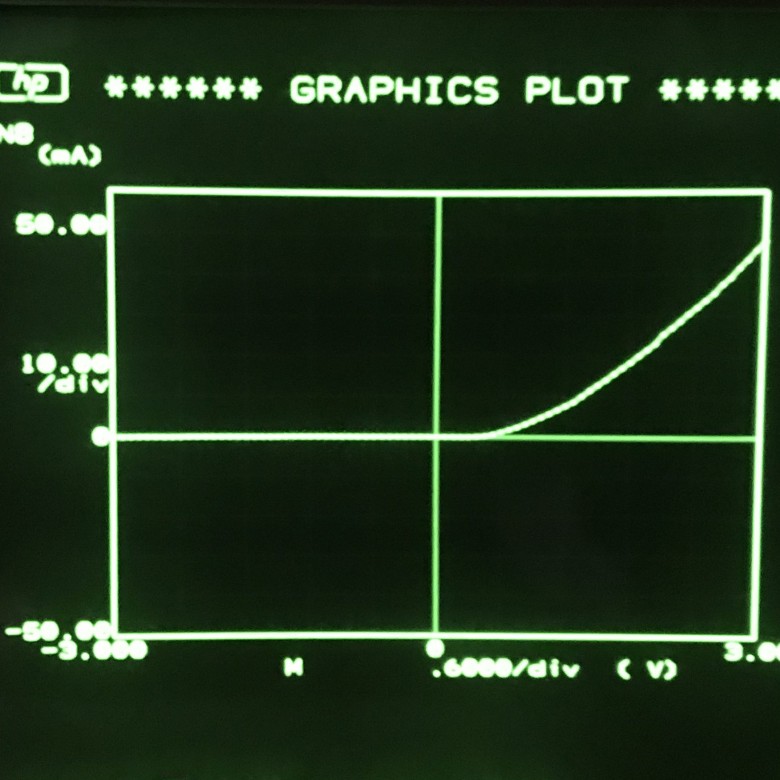

Kurva IV

Kurva IV Kurva IVFET Id / Vds curve dari perangkat NMOS sebelumnya

Kurva IVFET Id / Vds curve dari perangkat NMOS sebelumnyaTentu saja, kurva ini jauh dari ideal (termasuk karena resistensi kontak yang berlebihan dan faktor-faktor serupa lainnya), tetapi saya mengharapkan peningkatan kinerja jika saya mendapatkan instalasi microwelding. Ini sebagian dapat menjelaskan beberapa perbedaan dari kristal ke kristal. Segera saya akan menambahkan kurva IV baru, transistor dan karakteristik penguat diferensial ke

halaman ini .