Dalam setiap artikel tentang Habré yang ditujukan untuk mikroprosesor domestik, dengan satu atau lain cara, masalah blok IP berlisensi dan seberapa banyak kehadiran dan ketidakhadiran mereka mengurangi nilai, domestikitas, atau keamanan pembangunan ditingkatkan. Pada saat yang sama, banyak komentator tidak memahami subjek diskusi dengan sangat baik, jadi mari kita coba mencari tahu bagaimana lisensi bekerja di industri mikroelektronika, apa blok lisensi yang baik dan buruk, dan apa proses pengembangan sirkuit mikro, jika sebagian besar blok dibeli di dalamnya.

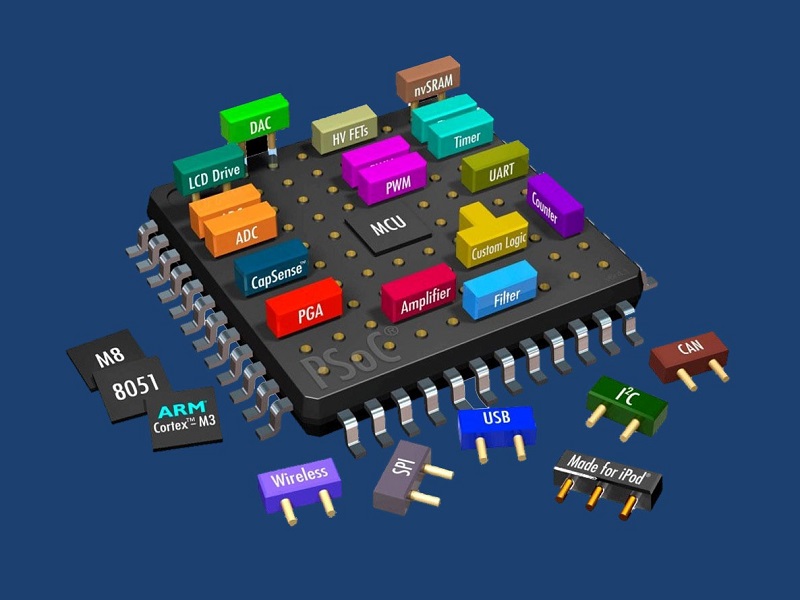

Setiap sirkuit mikro modern adalah apa yang dengan bangga disebut "sistem pada chip" beberapa waktu lalu: bahkan regulator linier berkaki tiga dan sumber tegangan memiliki penyesuaian digital yang tersembunyi dari pengguna, apa yang dapat kita katakan tentang mikroprosesor dan mikrokontroler yang berisi puluhan blok berbeda, pengembangan masing-masing yang membutuhkan keterampilan khusus dan pengalaman luas untuk menghindari jebakan yang tidak ditulis dalam buku dan artikel. Selain itu, setiap proyek, sebagai suatu peraturan, memiliki fitur pembunuh sendiri, yang olehnya pengembang mengharapkan untuk mendapatkan keunggulan dibandingkan pesaing, dan fitur pembunuh inilah yang harus dilakukan sebaik mungkin, dan semua blok lainnya seharusnya tidak lebih buruk daripada yang lain.

Perhatian, pertanyaannya adalah: apakah perlu mempertahankan tim pengembangan yang mahal yang dapat secara mandiri membuat semua blok yang diperlukan sendiri?

Sebuah pertanyaan yang bahkan lebih menarik: jika Anda sendiri telah mengembangkan sistem instruksi mikroprosesor, apakah Anda perlu memuat tim programmer yang

akan menulis kompiler untuk itu , port kernel segar dari sistem operasi populer, melakukan banyak kerja keras lainnya, dan kemungkinan besar itu tidak akan menempatkan kreasi Anda pada satu sejajar dengan arsitektur populer, di mana lebih banyak orang bekerja?

Dan yang paling penting: apakah jawaban positif untuk dua pertanyaan sebelumnya akan memberikan keunggulan kompetitif bagi produk Anda?

Penyimpangan lirisPada 5 Juni, Morris Chang pensiun, seorang pria yang belum pernah Anda dengar, tetapi tanpanya tidak akan ada elektronik modern. Morris Chang lahir di Cina, pada puncak perang saudara yang ia tinggalkan ke Amerika Serikat, lulus dari MIT, dan kemudian bekerja selama bertahun-tahun di Texas Instruments dan General Instruments. Pada tahun-tahun itu, bagian integral dari perusahaan mikroelektronik adalah produksinya sendiri, peralatan yang harganya beberapa kali lipat lebih murah daripada sekarang, tetapi biayanya sangat mahal. Inilah bagaimana Chang sendiri menulis tentang hal itu:

Ketika saya berada di TI dan Instrumen Umum, saya melihat banyak perancang IC ingin meninggalkan dan mendirikan bisnis mereka sendiri, tetapi satu-satunya hal, atau hal terbesar yang menghentikan mereka meninggalkan perusahaan itu adalah mereka tidak dapat mengumpulkan cukup uang. untuk membentuk perusahaan mereka sendiri. Karena pada waktu itu ada anggapan bahwa setiap perusahaan membutuhkan manufaktur, membutuhkan manufaktur wafer, dan itu adalah bagian yang paling padat modal dari perusahaan semikonduktor, dari perusahaan IC. Dan saya melihat semua orang yang ingin pergi, tetapi dihentikan oleh kurangnya kemampuan untuk mengumpulkan banyak uang untuk membangun wafer yang luar biasa.

Pada tahun 1985, Morris Chang akan pensiun, tetapi sebaliknya menerima tawaran pemerintah Taiwan untuk bekerja di Institut Penelitian Teknologi Industri, sebuah lembaga penelitian yang seharusnya membantu mewujudkan revolusi industri di Taiwan dan menutup celah antara ekonomi maju dan negara-negara maju. Pada tahun 1987, bersamaan dengan pekerjaannya di ITRI, Chang menciptakan TSMC, sebuah perusahaan yang tumbuh menjadi pabrikan sirkuit terpadu terbesar di dunia. Model bisnis TSMC pada awalnya didasarkan pada kenyataan bahwa perusahaan tidak mengembangkan apa pun, tetapi hanya menghasilkan perkembangan orang lain, dan ini adalah salah satu langkah pertama dalam menciptakan ekosistem modern untuk pengembangan dan produksi sirkuit mikro, yang dikenal sebagai model Fabless.

Akhir dari penyimpangan lirikApa itu Fabless?

Fabless adalah model untuk pengembangan dan produksi sirkuit mikro di mana perusahaan pengembang tidak memiliki produksi sendiri dan menggunakan layanan dari pabrik pihak ketiga yang juga berkolaborasi dengan pengembang lain (dan kadang-kadang memiliki produk sendiri).

Kehadiran pabrik pihak ketiga dapat secara radikal mengurangi ambang batas untuk memasuki pasar mikroelektronika (yang pernah diimpikan Morris Chang pada satu waktu), dari ratusan hingga jutaan dolar, karena tidak adanya kebutuhan untuk membeli dan memelihara peralatan untuk produksi. Hal ini juga memungkinkan untuk mengurangi ambang batas ini lebih jauh karena pembentukan pasar untuk pemasok blok fungsional yang kompleks (mereka juga Silicon IP). Jika Anda menghasilkan chip di pabrik Anda sendiri, maka Anda hanya dapat mengandalkan kekuatan Anda sendiri dan harus mengandung tim yang dapat membuat semua blok yang diperlukan. Jika pabrik digunakan tidak hanya oleh Anda, tetapi juga oleh perusahaan lain, maka seseorang telah menyelesaikan sebagian besar tugas khas sebelum Anda, dan Anda dapat menggunakan hasil pekerjaan orang lain - atau menjual kembali solusi Anda sendiri kepada orang lain, setelah sebelumnya menyetujui harga dan ketentuan sehingga tidak ada yang tinggal di pihak yang kalah. Tentu saja, Anda tidak mungkin menjual pengetahuan Anda untuk mengarahkan pesaing, tetapi ada banyak situasi di mana Anda bisa menghasilkan tanpa terlibat dalam konflik kepentingan. Itu keluar dari kemungkinan dan keinginan untuk menggunakan kembali hasil dari penyelesaian masalah-masalah khas yang muncul pasar blok-IP, yang ukurannya pada 2017 mendekati empat miliar dolar dan terus tumbuh dengan cepat.

Bagaimana ini menguntungkan?

IP Pembeli - terutama penghematan. Menurut berbagai perkiraan, pembelian IP-blok biasanya dua sampai lima kali lebih murah daripada pengembangan diri. Selain itu, pembelian biasanya memungkinkan Anda untuk secara signifikan mengurangi waktu pengembangan, karena Anda tidak perlu memproduksi chip tes secara mandiri dan memperbaiki kesalahan.

Untuk pengembang IP - peluang untuk membangun bisnis yang bekerja di atas solusi khusus dan secara signifikan mengurangi biaya melakukan bisnis. Bagian penting dari biaya rangkaian mikro adalah biaya pemasaran, pengemasan, pengujian, dukungan teknis, perangkat lunak aplikasi, dan akhirnya, templat foto untuk produksi massal, dll. dll. Jika Anda tidak menghasilkan produk jadi, tetapi hanya menjual balok, maka Anda tidak memiliki semua pengeluaran ini.

Pabrik - kesempatan untuk menarik lebih banyak pelanggan. Pabrik-pabrik besar berusaha untuk menciptakan ekosistem pemasok blok IP di sekitar mereka, karena penggunaannya dapat secara signifikan mempercepat desain dan, sama pentingnya, mengotomatiskannya sebanyak mungkin. Portofolio yang kaya komponen siap pakai adalah bantuan besar dalam desain produk akhir, karena memungkinkan Anda untuk hanya melakukan apa yang Anda ketahui sendiri dan tidak menghabiskan sumber daya berharga untuk mengembangkan segala sesuatu secara umum - terutama dalam situasi di mana sudah ada solusi siap pakai yang dikembangkan oleh orang-orang. yang berinvestasi dalam pengembangannya secara signifikan lebih banyak waktu dan pengalaman daripada yang Anda mampu. Karenanya, beragam pilihan IP siap pakai dapat menjadi faktor serius dalam memilih pabrik tertentu untuk produksi proyek Anda.

Bagaimana cara kerjanya?

Mari kita lihat lisensi core menggunakan contoh sistem kustom bola pada sebuah chip. Sistem akan berisi inti prosesor, bus untuk menggabungkan inti dan periferal, sejumlah memori cache, antarmuka untuk berkomunikasi dengan dunia luar (katakanlah CAN dan I2C), PLL, DAC dan ADC. Untuk kemurnian percobaan, anggaplah bahwa semuanya akan dibeli sama sekali, tanpa pengembangan independen. "Asumsi bodoh," katamu, dan kamu tidak akan benar. Pada kenyataannya, tentu saja, situasi seperti itu sangat jarang, tetapi masih sangat mungkin untuk membayangkan bahwa fitur pembunuh dari produk tidak akan menjadi beberapa blok itu sendiri, tetapi kombinasi spesifik dari blok yang ada. Misalnya, Anda adalah pembeli pertama suatu blok (oleh karena itu, pesaing belum memilikinya) atau Anda membuat blok yang ada untuk digunakan dalam segmen yang tidak biasa untuknya (oleh karena itu, pesaing di segmen ini tidak memiliki yang serupa).

Jadi, mari kita mulai dengan ...

... tidak, bukan dari inti prosesor, tetapi dari pengikatan analog. Sebagai contoh, ambil analog-to-digital converter (ADC) - unit khas kebanyakan mikrokontroler dan sistem lain yang menangani data dari dunia luar.

ADC adalah blok analog, yang berarti parameternya sangat tergantung tidak hanya pada sirkuitnya, tetapi juga pada bagaimana tepatnya sirkuit ini diimplementasikan pada sebuah chip. Jika kita mengambil file yang sudah jadi dengan topologi dari satu proses teknis dan memproduksinya di pabrik lain dengan standar desain yang sama, kita bisa mendapatkan parameter yang sama sekali berbeda (belum lagi transfer ke standar desain lainnya). Namun, budaya "pemasok kedua", yang dikenal sejak pertengahan abad ini, masih ada; misalnya, pabrik Towerjazz menawarkan salinan dari beberapa proses pembuatan TSMC.

ADC adalah contoh yang bagus dari blok Hard IP yang terkait dengan proses tertentu. Untuk membeli unit seperti itu, Anda harus tahu persis apa teknologi produk akhir Anda akan diproduksi, dan, sebagaimana disebutkan di atas, ketersediaan Hard IP yang diperlukan dapat menjadi keunggulan kompetitif yang serius bagi pabrik.

Bagaimana Hard IP dikirimkan? Ini adalah pertanyaan yang menarik, dan untuk menjawabnya perlu dibahas dalam bentuk apa blok tersebut sedang dikembangkan. Dalam kasus sebagian besar blok analog, pengembangan sirkuit dilakukan pada tingkat masing-masing transistor, yaitu file output akan menjadi file sirkuit listrik dan file dengan topologi. Selain itu, fitur dari skema dan topologi dapat memiliki nilai komersial yang serius, yang, tentu saja, saya tidak ingin memberikan ke samping. Dan agar klien tidak dapat membalikkan skema dengan topologi, topologi biasanya juga tidak ditransmisikan, oleh karena itu, dalam kasus biasa, file yang dikirim terlihat seperti ini:

- Alih-alih rangkaian listrik, klien menerima model perilaku tingkat tinggi yang tidak mengungkapkan fitur implementasi. Model seperti itu dapat ditulis dalam Verilog-A. Alternatifnya adalah bahwa beberapa sistem CAD (misalnya, Cadence Virtuoso) mendukung enkripsi sirkuit listrik, yaitu, klien akan dapat menggunakan sirkuit Anda (atau file Verilog-A), tetapi tidak akan dapat membuka dan melihat konten.

- Tata letak dimensi topologi, dengan kesimpulan eksternal yang ditandai dan deskripsi tentang berapa banyak tingkat metalisasi yang ditempati blok.

- Lingkungan pengujian untuk verifikasi parameter utama.

- Dokumentasi

Dalam hal ini, tentu saja, partisipasi pihak ketiga diperlukan, di mana Anda dapat mentransfer topologi tanpa takut kompetisi dan rekayasa balik. Pihak ketiga ini adalah pabrik, dan peran perantaranya antara pelanggan dan kontraktor adalah bagian penting dari ekosistem pengembangan chip yang luar biasa. Pabrik, tentu saja, harus memiliki reputasi sejernih kristal (ini tentang bookmark) dan, idealnya, tidak boleh menghasilkan yang serupa dengan sendirinya, karena bekerja di sebuah pabrik dari perusahaan yang bersaing dalam hal apapun merupakan kesenangan yang meragukan. Samsung berhasil memproduksi prosesor pada saat yang sama untuk dirinya dan Apple, tetapi pabrik besar lainnya biasanya berkonsentrasi pada produksi mereka sendiri (seperti Intel), atau sepenuhnya mengabaikan pengembangan diri (seperti TSMC). Omong-omong, keinginan untuk menyingkirkan konflik kepentingan ini adalah salah satu pendorong untuk mengalokasikan Globalfoundries (pemain terbesar kedua di pasar pabrik) dari AMD.

Penyimpangan lirisNgomong-ngomong, di Rusia, tidak ada pabrik bermain murni di Rusia. Terlebih lagi, untuk benar-benar semua pemain pasar, produksi produk mereka sendiri adalah prioritas, dan semua chip dalam negeri yang diproduksi oleh pengembang yang luar biasa diproduksi di fasilitas pesaing potensial mereka - atau di pabrik murni di luar negeri.

Akhir dari penyimpangan lirikLebih jauh, ada detail penting lain dari interaksi pemasok-pabrik: pabrik memasukkan blok IP Anda ke dalam basis datanya sendiri dan selanjutnya memeriksa semua proyek yang masuk untuk mengetahui keberadaan topologi Anda (yang dapat diperoleh seseorang dari Anda maupun secara ilegal), dan tanyakan kepada Anda apakah orang yang meminta produksi memiliki lisensi (karena banyak lisensi murah menyiratkan penggunaan unit hanya dalam satu proyek). Kehadiran cek oleh pabrik memungkinkan pengembang Hard IP untuk memilih opsi lisensi yang mudah - terkait dengan jumlah proyek, jumlah chip yang terjual, waktu peluncuran chip ke dalam produksi, dll. dll. Tetapi lebih lanjut tentang jenis-jenis lisensi di bagian selanjutnya.

Seperti Hard IP dalam sistem tipikal pada sebuah chip, Anda akan memerlukan ADC, PLL, lapisan fisik antarmuka I / O.

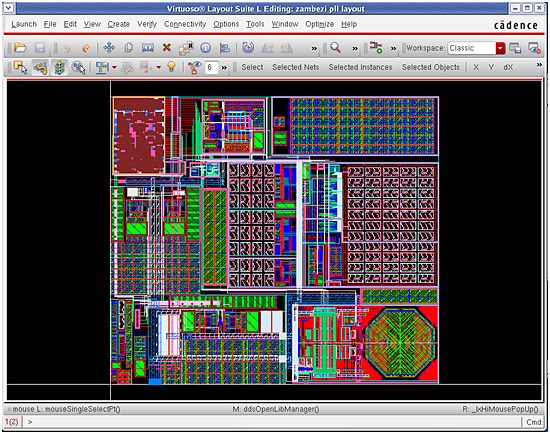

CAD CAD Cadence Virtuoso Layout Suite dengan topologi blok Hard IP analog (ini PLL, kalau ada yang tertarik). Batas antara masing-masing subunit (yang biasanya dibuat oleh orang yang berbeda) dan, misalnya, elemen yang sangat jarang untuk sirkuit terpadu - induktor di sudut kanan bawah, terlihat jelas. Dan di kiri atas adalah blok digital (mungkin kontrol) dan antarmuka multi-bit ke sisanya.

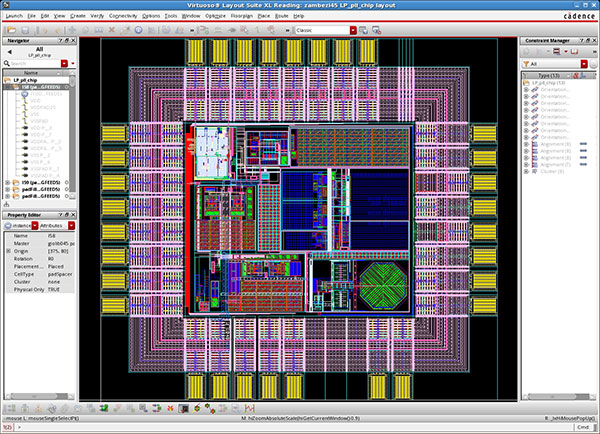

Itu sama, tetapi sudah dalam bentuk chip jadi (misalnya, untuk pengujian). Bantalan I / O dan cincin yang menghubungkannya dari tanah dan persediaan terlihat jelas.

Istilah "Hard IP" juga digunakan dalam kaitannya dengan blok IP untuk FPGA. Dalam hal ini, dipahami bahwa kode blok telah dioptimalkan untuk digunakan dalam model FPGA tertentu dan disintesis untuk penempatan di dalamnya.

IP lunak

Blok selanjutnya yang akan kita pertimbangkan adalah inti prosesor. Sebenarnya, hampir semua sirkuit digital dapat menggantikannya, misalnya, unit pengkodean sinyal dengan kode Reed-Solomon, tetapi inti prosesor paling banyak didengar dan membentuk setengah dari seluruh pasar (termasuk karena kompleksitas dan biaya tinggi).

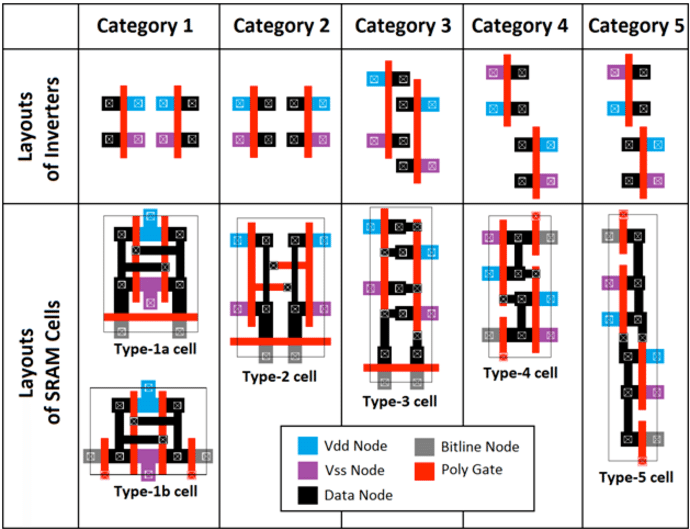

Perbedaan utama antara pengembangan sirkuit digital dan pengembangan yang analog adalah bahwa sirkuit digital biasanya ditulis dalam bahasa tingkat tinggi khusus - Verilog atau VHDL, dan kemudian sistem CAD khusus mensintesis sirkuit listrik dan topologi dari kode ini. Jadi, hingga saat sintesis, kode tidak terikat dengan teknologi tertentu, dan blok yang sama dapat diproduksi di pabrik yang berbeda (atau dijahit ke dalam FPGA) atau dalam versi berbeda dari teknologi yang sama (misalnya, dioptimalkan untuk kecepatan tinggi atau konsumsi daya rendah) . Ini, pada kenyataannya, digunakan oleh perusahaan pengembangan, seperti, misalnya, ARM. Blok digital semacam itu yang tidak terikat pada teknologi tertentu disebut Soft IP.

Berikut adalah skema satu bit adder:

Dan inilah tampilan delapan-bit adder dalam desain chip:

module adder(

input wire [7:0]a,

input wire [7:0]b,

output wire [7:0]out,

output wire carry

);

assign {carry, out} = a + b;

endmodule

, , , . , IP- .

Soft IP? :

• Clean, readable, synthesizable Verilog HDL, VHDL

• Cadence Encounter RTL Compiler synthesis scripts

• Documentation – integration and user guide, release notes

• Sample verification testbench

Encrypted source along with a complete certification data package (CDP) including all artifacts required for chip-level compliance.

, — , ( IP ). , . , - -, , .

, LEON3:

- , Cobham Gaisler, LEON3 GPL

- LEON3FT ( ): The LEON3FT core is distributed together with a special FT version of the GRLIP IP library, distributed as encrypted RTL.

- ( ) , LEON2FT, .

, , Verilog-, . Verilog- , , , , . digital watermarks, , IP.

, “Clean, readable, synthesizable” , , IP . , , , ( , hardware trojans) , , , .

, : soft IP , , ? , Soft IP, , .. .… :

ARM, , , , , ( ), IP , - , , . . (, , , ). Apple Imagination Technology in-house , Apple , Imagination ( ).

, — ( IP ) ( ).

soft IP FPGA, , . , Xilinx IP, ( ) , , ( , ).

, , .

— IP- . , -, . , IP, , IP , , IP ( , ); , - .

— . , ( IP).

— . , , , . — . , , .

— , , (, ARM Cortex). — , .

— . (, , ) , — ( , , ). ? , ( - , , ) . , , , , , — .

? : , , , . , Apple, ARM - , , (, ARM ) — .

: , , , , , , ( — ). , , . , , Apple, , , ! ARM, , Apple . , ARM . , , Apple — PowerPC, , PowerPC x86, Apple Intel.

Soft IP , - , IP . :

- , “ — ”, .

- - IP ( ), IP, IP ( IP hardening) . ? , , , .

soft IP ( ), , , .. ..

Configurable IP

IP, hard soft — , . - , - . ? , IP-? ?

( , FPGA) , , , . , , IP- Hard IP, Soft IP ( , ).

— -.

Foundation IP

«-hard» IP- — foundation IP, . — , . , , , , , . , , ( ) , (, ) . «generic» , , , , , .

Foundation IP -, , , .

BarsMonster .

Verification IP

, , — , . , , , . , , . , - . “”. .

, — Verification IP. — , , ( ). Synopsys , , Synopsys — IP-. IP Design&Reuse Synopsys 828 Silicon IP ( ARC — ARM) 116 Verification IP .

verification IP CAN, ( APB AHB ARM) - . , , , .

?

, , , , ? .

:

- , ( verification IP ).

- — .

- ( , ).

- Soft IP , .

- , , .

- , , .

- , .

- , ( ).

, , ( ). , - , « - BGA 400-700 ». , Hard IP- 400-700 , , , 4-8 (, Soft IP). — ? , . , «-» .

— Synopsys IC Compiler , .

, — , , , , , , .

, , fabless- IP- , , , . , , ( “”) , , : , , , , , , - . , , — .

: Open Source?/ Open Source . , - ( ) , - . , , - . , , .

—

Opencores.org, — OpenRISC, ( FPGA), ASIC ( Samsung). Opencores, , - , ( ARM), FPGA. FPGA Proven, — ASIC Proven.

—

RISC-V. ( OpenPOWER OpenSPARC) , - , , ( ).

RISC-V — , MIPS, , , , ( , MIPS). RISC-V Foundation Google, Samsung, NXP, NVIDIA . , , , , OpenPOWER, , , ARM , ARM, , , ( Intel). - . RISC-V (

RISC-V), - , . , ,

RISC-V — Falcon NVIDIA.

: ?OpenCores, IP- ( ) . :

TSMC IP Alliance, IP .

Design&Reuse, IP-, ( ).

ChipEstimate, D&R, .

— ?, , , - .

— “” (), “” ( ), “” “” (211), “Neuromatrix” ( “”), RISC-V (Syntacore), ARM, MIPS, SPARC, MCS96, MCS51, C166, AVR, MSP430.

,

“ ” ( ):

IP-:

: ARM Cortex-M4F, ARM Cortex-M0, ARM946E-S c AMBA, ARM VFP9-S, SPARC v.8 c AMBA. 8- RISC .

IP- (PLL) TSMC, KeyASIC AnalogBits, Sidense Memory, - (eFuse) TSMC, IP- , ROM RAM ..

“ ” , IP- - (-, IP-).

IP? IP- (

“ ”,

“”,

211), . Design&Reuse ChipEstimate “ ” ( ) NTLab. , .