Pada artikel ini, kami akan berbagi pengalaman kami dalam mengembangkan kartu antarmuka unit antarmuka berdasarkan SoC ARM + FPGA Xilinx Zynq 7000. Papan dirancang untuk merekam sinyal ucapan dalam format PRI / BRI analog dan digital (ISDN, E1 / T1). Perangkat terakhir itu sendiri akan digunakan untuk mencatat negosiasi dalam penerbangan sipil.

Besi: pemilihan platform perangkat keras perangkat

Pilihan platform perangkat keras ditentukan oleh dukungan protokol PRI / BRI, yang hanya dapat diimplementasikan pada sisi FPGA. Mikrokontroler (MCU) dan mikroprosesor (MPU) tidak cocok.

Seseorang dapat memilih dua solusi untuk masalah ini:

- Sintesis inti Microblaze IP

- SoC Zynq-7000.

Kami memilih sistem dengan chip Zynq 7000 (SoC), karena lebih mudah untuk menulis aplikasi perangkat lunak dan menyediakan lebih banyak fungsi untuk tugas saat ini dan masa depan.

Secara total, daftar besi berikut dikumpulkan di bawah proyek:

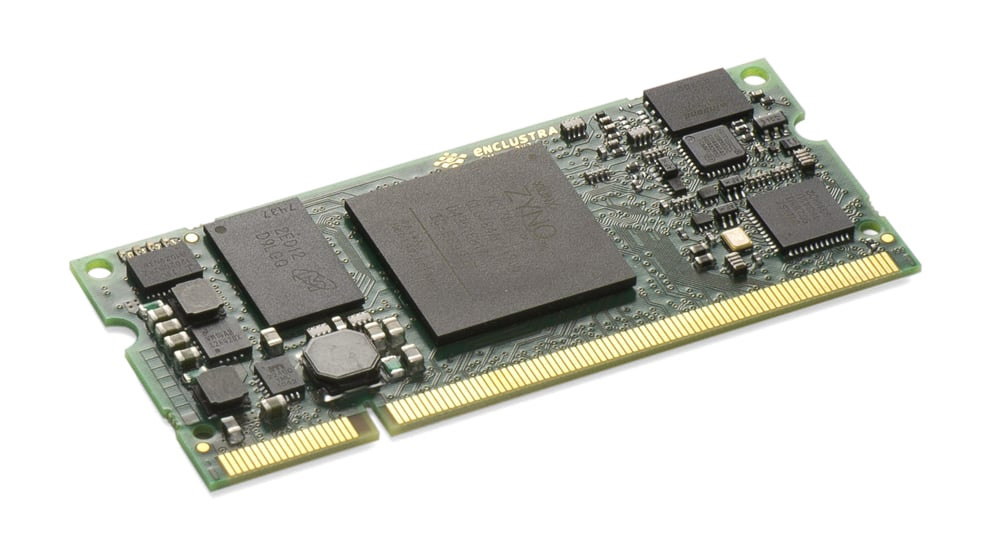

1.Xilinx Zynq 7020 (

Mars-ZX3 dan

Mars EB1 )

Enclustra Mars ZX3 SOM

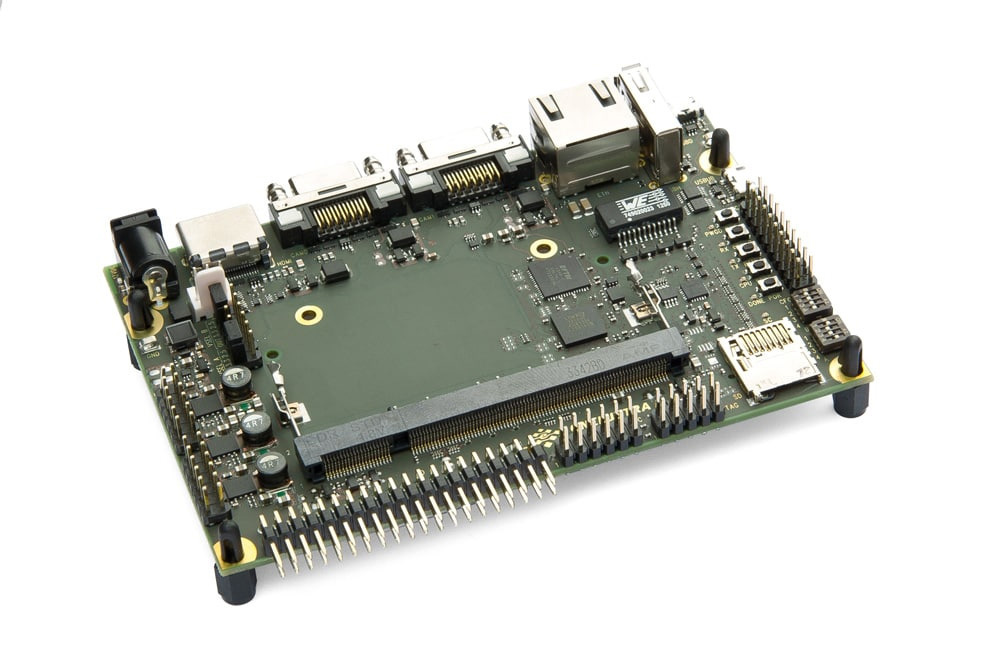

Enclustra Mars ZX3 SOM Enclustra Mars EB1 Alas Tiang2. TI TLV320AIC34

Enclustra Mars EB1 Alas Tiang2. TI TLV320AIC34 (

tlv320aic34evm-k dan motherboard USB).

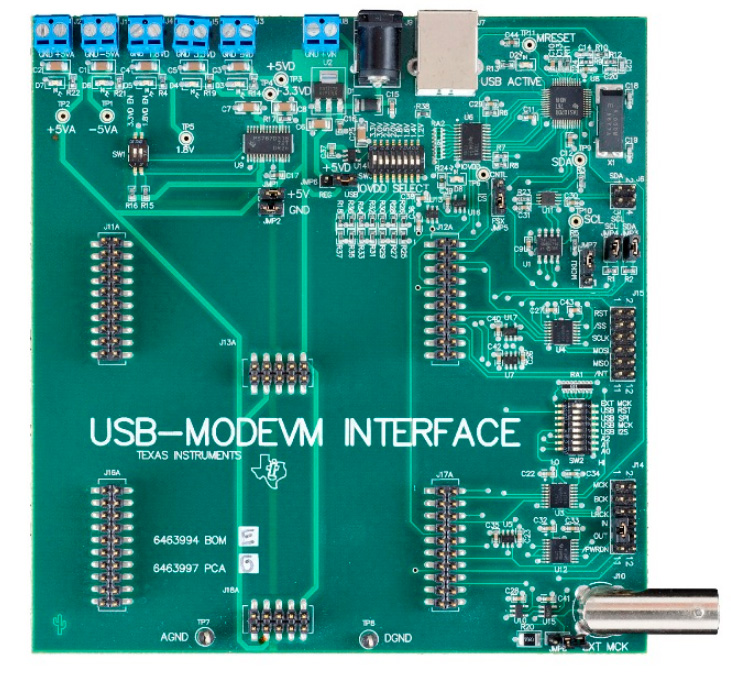

Papan debug untuk tlv320aic34 (tlv320aic34evm-k)

Papan debug untuk tlv320aic34 (tlv320aic34evm-k) Papan ekspansi USB-MODEVM untuk tlv320aic34evm-k3. IDT82P2288 - PRI, XHFC-4SU - sirkuit mikro BRI,

Papan ekspansi USB-MODEVM untuk tlv320aic34evm-k3. IDT82P2288 - PRI, XHFC-4SU - sirkuit mikro BRI, tidak ada kit debugging, jadi kami hanya meletakkan fondasi sebagai inti ip untuk pengujian, dan baptisan api terjadi tepat dalam proses, setelah membuat papan prototipe.

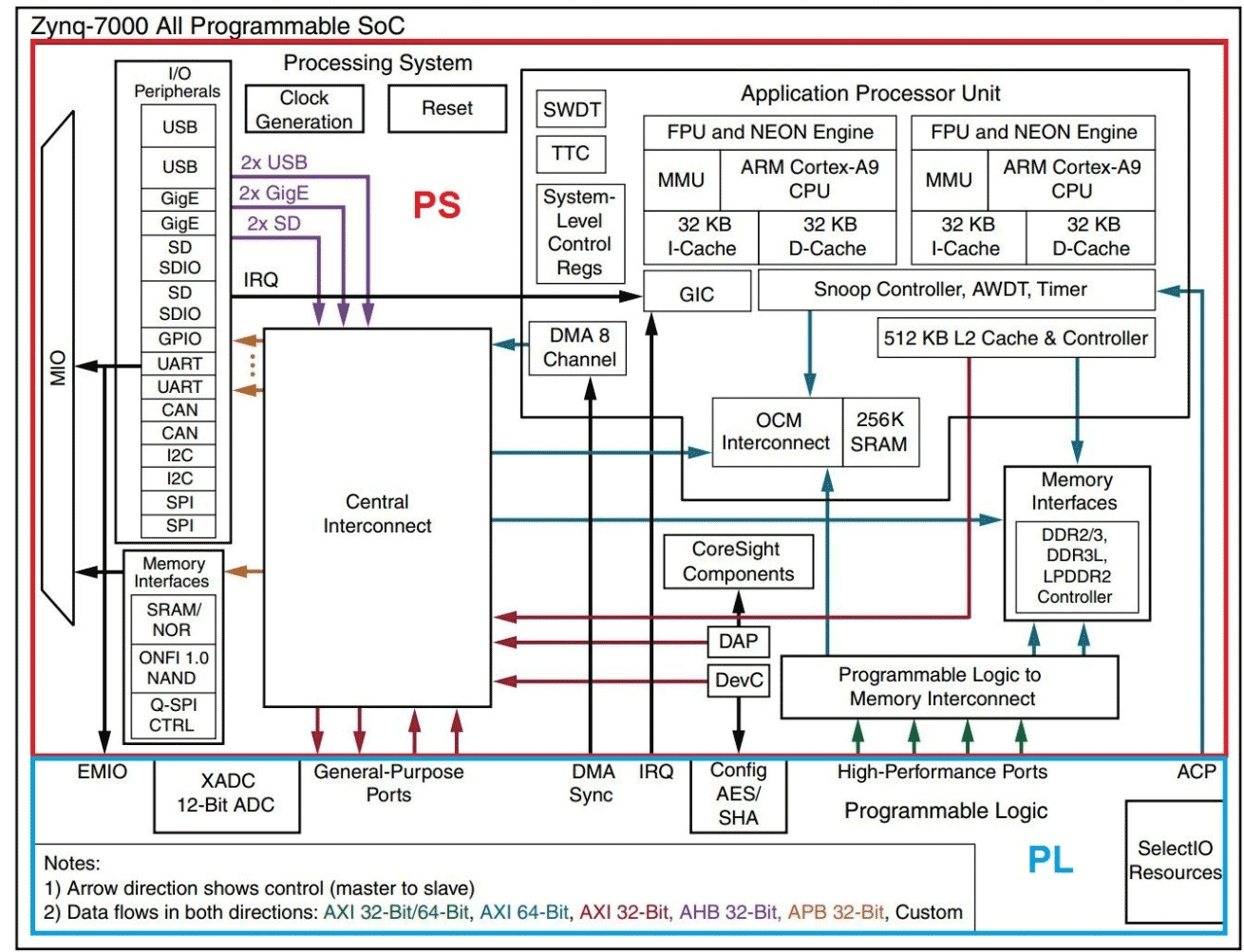

Bekerja dengan sistem pada chip Xilinx Zynq 7000

Struktur internal SoC Xilinx Zynq 7000

Struktur internal SoC Xilinx Zynq 7000 Langkah-langkah untuk menghasilkan file boot untuk Xilinx Zynq

Langkah-langkah untuk menghasilkan file boot untuk Xilinx ZynqMenjalankan / mengunduh executable untuk Zynq berbeda dari unduhan biasa untuk MPU. Pekerjaan biasa dengan prosesor Cortex-A adalah memuat u-boot, kernel linux, rootfs. Dan pada Zynq, bitstream muncul, file firmware untuk FPGA. Bitstream berisi deskripsi blok perangkat keras pada FPGA dan komunikasi internal dengan prosesor. File ini dimuat saat startup sistem. Juga di sisi linux ada mekanisme yang memungkinkan Anda untuk mem-flash bagian PL segera selama operasi, perangkat seperti itu disebut xdevcfg (

ZYNQ FPGA manager sejak 2018.1 ).

Antarmuka PRI / BRI

Fitur jaringan digital PRI / BRI

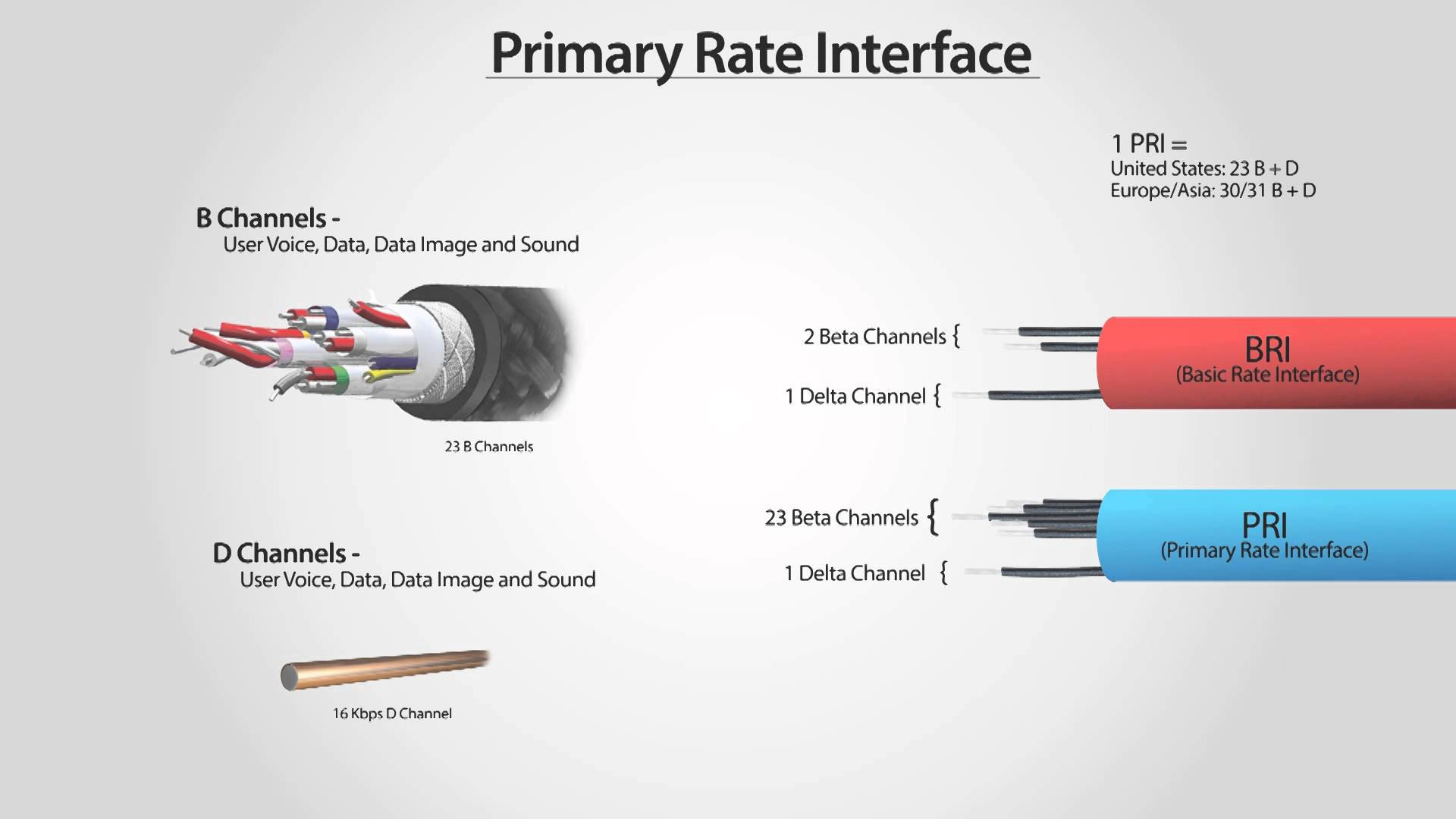

Fitur jaringan digital PRI / BRIPrimary Rate Interface (PRI) adalah antarmuka jaringan ISDN standar yang mendefinisikan disiplin menghubungkan stasiun ISDN ke batang broadband yang menghubungkan pertukaran lokal dan sentral atau switch jaringan.

Jenis frame yang ditransmisikan untuk PRI

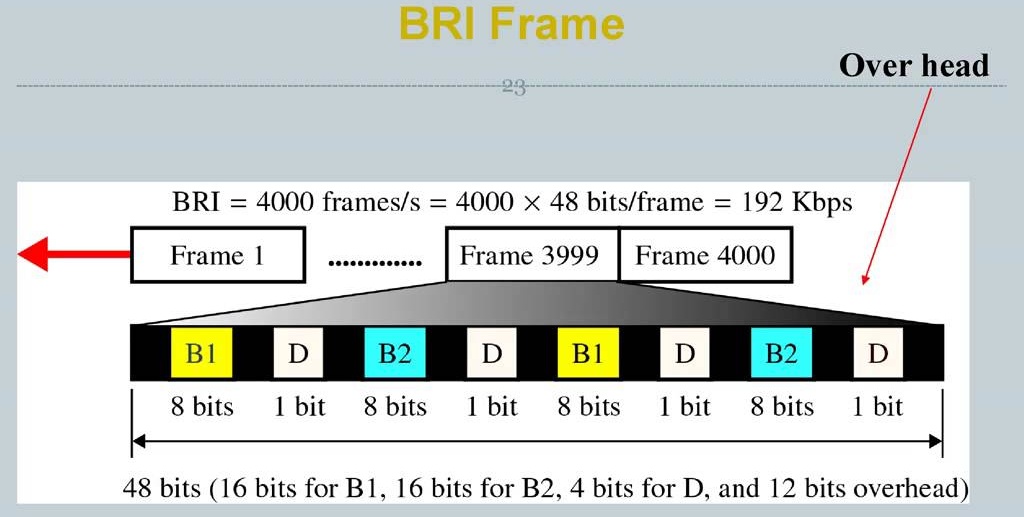

Jenis frame yang ditransmisikan untuk PRI Tampilan frame yang ditransmisikan untuk BRI

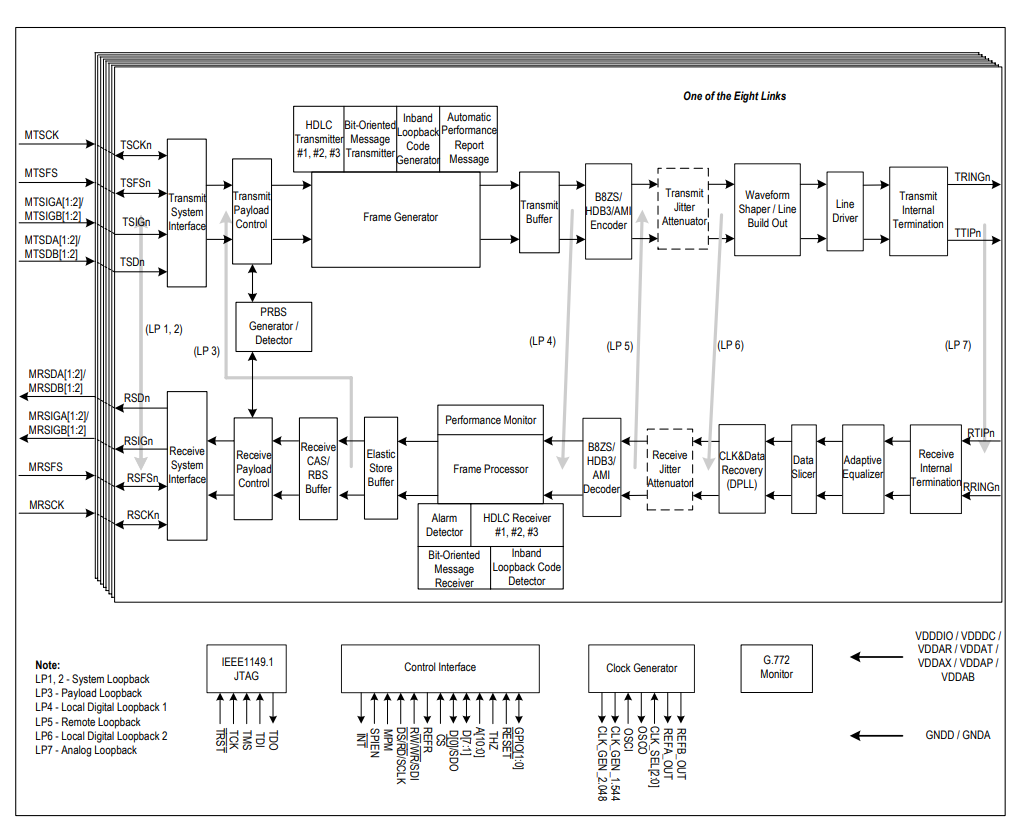

Tampilan frame yang ditransmisikan untuk BRI Struktur internal fisika PRI - IDT82P2288

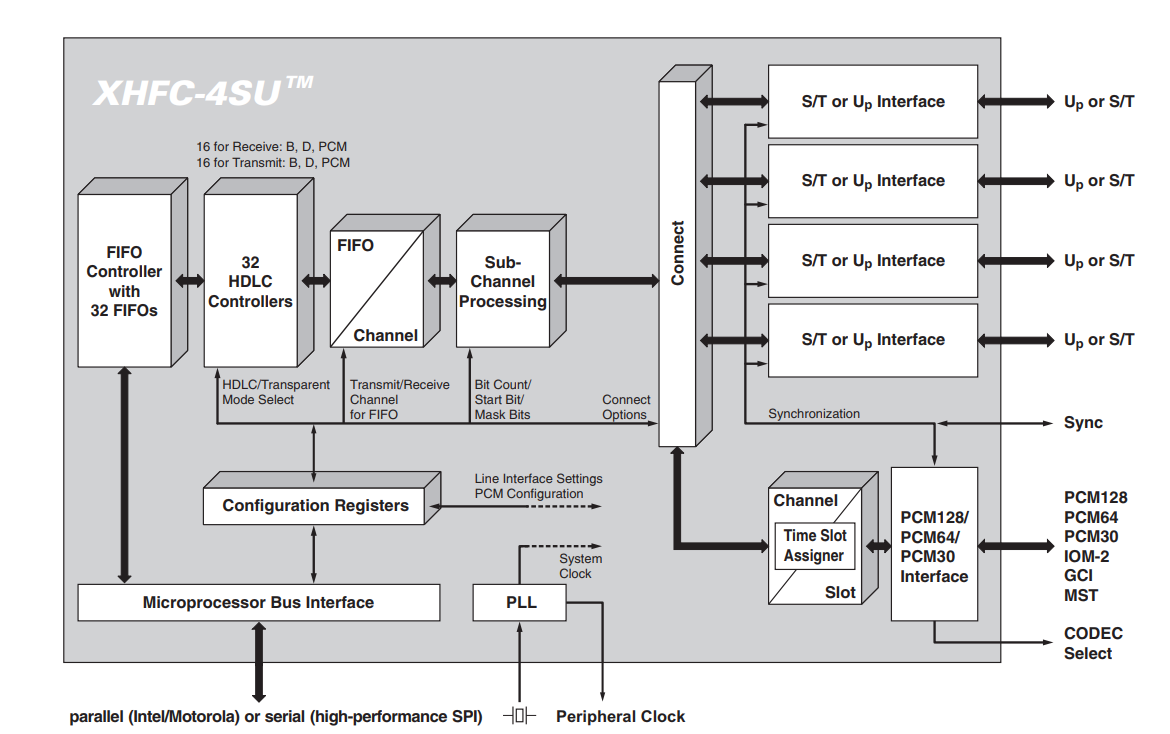

Struktur internal fisika PRI - IDT82P2288 Struktur internal fisika BRI - XHFC-4SU

Struktur internal fisika BRI - XHFC-4SUCodec Audio TLV320AIC34

Codec audio TLV320AIC34 audio empat saluran berdaya rendah untuk audio portabel dan telepon adalah solusi yang baik untuk digunakan dalam telepon analog.

Tlv320aic34 A-bagian, codec audio berisi dua blok fungsi tersebut

Tlv320aic34 A-bagian, codec audio berisi dua blok fungsi tersebutData dapat dikirim melalui antarmuka I2S, serta melalui DSP, PCM, TDM.

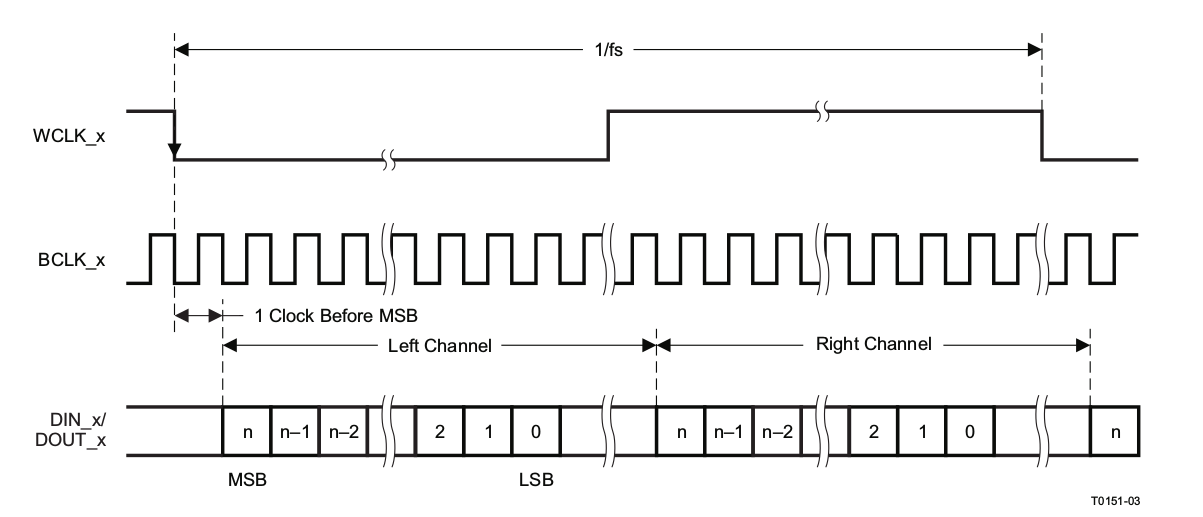

I2S adalah standar antarmuka serial bus, digunakan untuk menghubungkan perangkat audio digital dan secara elektrik mewakili 3 konduktor yang beralih dari perangkat aktif ke perangkat pasif, serta 4 sinyal yang sesuai dengan mereka sebagai berikut:

- Jam Bit (BCLK).

- Frame sinyal jam (sesuai dengan kata-kata) sinkronisasi (WCLK).

- Sinyal data yang dapat mengirim atau menerima 2 saluran yang terbagi waktu (DIN / DOUT).

Saluran untuk menerima dan mentransmisikan data dibagi, yaitu, ada saluran terpisah untuk menerima data dan saluran untuk transmisi. Pengontrol menerima data yang dikirimkan oleh codec audio, tetapi kebalikannya juga dimungkinkan.

Bingkai I2S, fitur antarmuka I2S

Bingkai I2S, fitur antarmuka I2SSetelah memilih semua komponen perangkat keras, kami memecahkan masalah menghubungkan codec audio dan Xilinx Zynq 7020.

Cari core I2S

Mungkin saat yang paling sulit ketika bekerja dengan aliran audio di Xilinx Zynq 7020 adalah bahwa pada bagian prosesor sistem ini pada dasarnya tidak ada bus I2S pada chip, jadi saya harus menemukan inti I2S. Tugas ini diperumit dengan syarat bahwa ip core harus bebas.

Kami memilih beberapa inti IP. Ditemukan untuk core logam telanjang I2S

Digilent . Kami menemukan beberapa inti ip pada

opencores dan, mungkin, opsi terbaik bagi kami adalah inti ip

Perangkat Analog . Mereka menghasilkan ip-core untuk peralatan mereka, untuk interaksi FPGA / FPGA.

Kami tertarik pada ip-core yang disebut

AXI-I2S-ADI. Perangkat Analog sendiri mempromosikan ip core ini untuk platform perangkat kerasnya.

Total daftar kasus penggunaan:

- Bare metal - IP core untuk I2S (audio Digilent ZYBO)

- opencores.org

- Pengontrol AXI-I2S-ADI (Perangkat Analog)

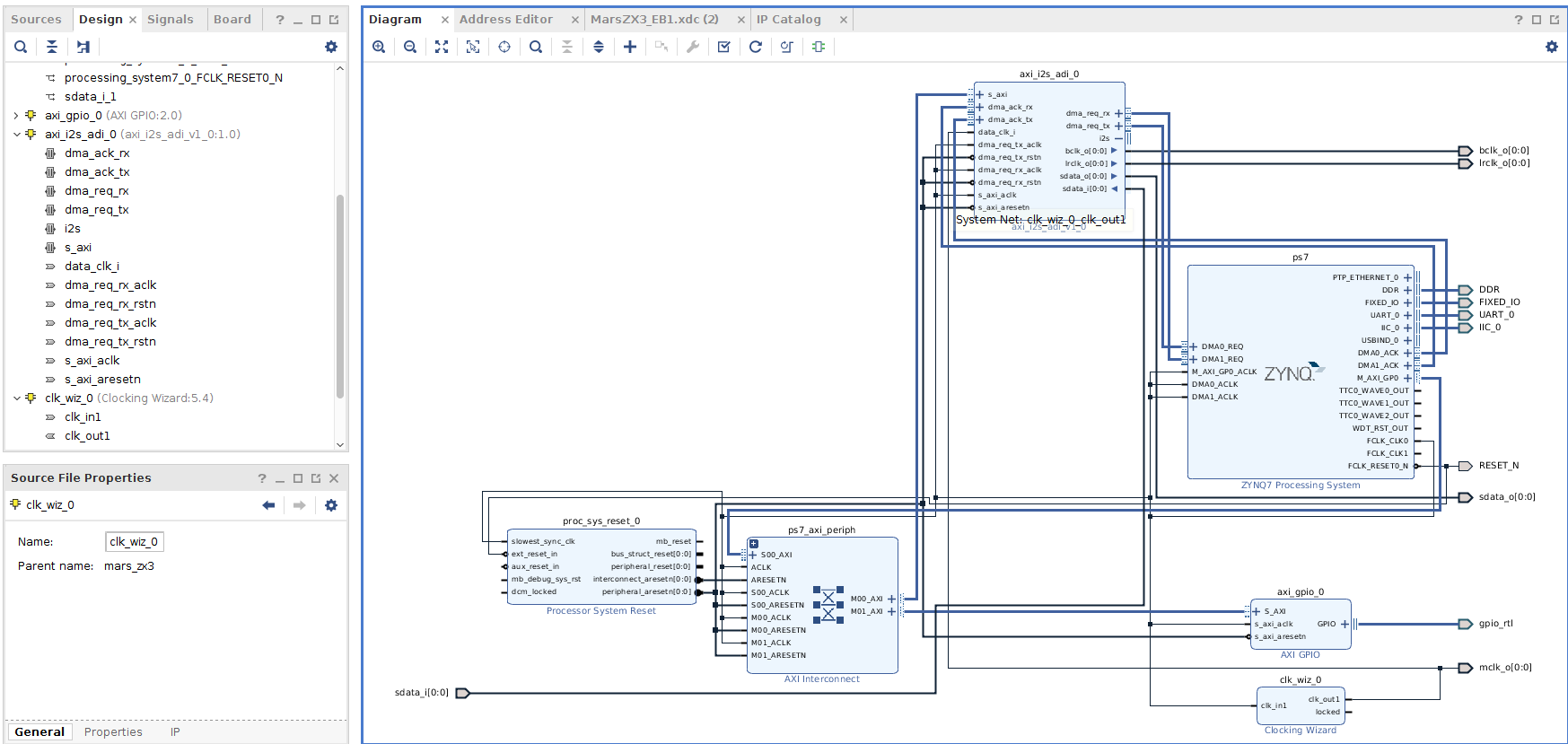

AXI-I2S-ADI IP Core

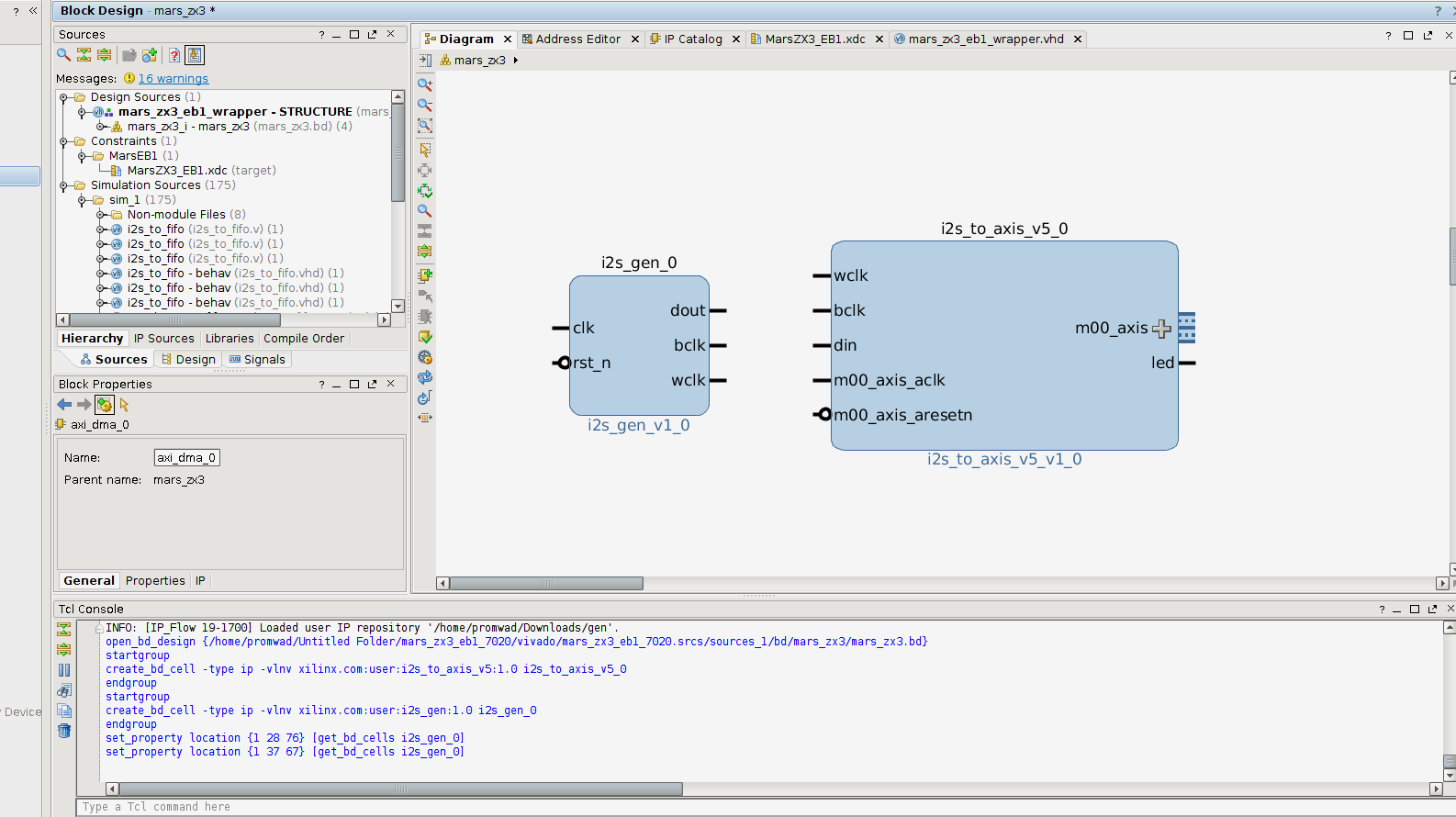

Inti IP itu sendiri terlihat seperti ini: ia memiliki garis bclk, wclk, din, dout. Terhubung ke DMA Xilinx Zynq 7000, dalam contoh kami, bagian DMA PS digunakan. Semua pertukaran data terjadi melalui DMA. DMA dapat berupa unit mandiri atau bagian integral dari PS SoC.

Ketika mengkonfigurasi ip-kernel ini, penting untuk tidak lupa mengirimkan frekuensi master mclk ke tlv320aic34 sendiri, sebagai opsi saat menggunakan kit debugging untuk tlv320aic34 - kirimkan frekuensi master eksternal.

Blok fungsi dengan axi-i2s-adi yang terhubung

Blok fungsi dengan axi-i2s-adi yang terhubungSetelah prosedur konfigurasi, tugasnya adalah untuk meluncurkan fungsionalitas di OS Linux.

Luncurkan dan konfigurasikan hierarki perangkat untuk tlv320aic34

Mengkonfigurasi i2c (tlv320aic34 dikonfigurasikan pada antarmuka ini):

i2c0: i2c@e0004000 { ... tlv320aic3x: tlv320aic3x@18 { #sound-dai-cells = <0>; compatible = "ti,tlv320aic3x"; reg = <0x18>; gpio-reset = <&axi_gpio_0 0 0>; ai3x-gpio-func = <&axi_gpio_0 1 0>, /* AIC3X_GPIO1_FUNC_DISABLED */ <&axi_gpio_0 2 0>; /* AIC3X_GPIO2_FUNC_DIGITAL_MIC_INPUT */ AVDD-supply = <&vmmc2>; DRVDD-supply = <&vmmc2>; IOVDD-supply = <&vmmc2>; DVDD-supply = <&vmmc2>; ai3x-micbias-vg = <1>; }; ... };

Mengkonfigurasi i2s (data audio dikirim melalui antarmuka ini):

i2s_clk: i2s_clk { #clock-cells = <0>; compatible = "fixed-clock"; clock-frequency = <11289600>; clock-output-names = "i2s_clk"; }; axi_i2s_adi_0: axi_i2s_adi@43C00000 { compatible = "adi,axi-i2s-1.00.a"; reg = <0x43C00000 0x1000>; xlnx,bclk-pol = <0x0>; xlnx,dma-type = <0x1>; xlnx,has-rx = <0x1>; xlnx,has-tx = <0x1>; xlnx,lrclk-pol = <0x0>; xlnx,num-ch = <0x1>; xlnx,s-axi-min-size = <0x000001FF>; xlnx,slot-width = <0x18>; }; &axi_i2s_adi_0 { #sound-dai-cells = <0>; compatible = "adi,axi-i2s-1.00.a"; clocks = <&clkc 15>, <&i2s_clk>; clock-names = "axi", "ref"; dmas = <&dmac_s 0 &dmac_s 1>; dma-names = "tx", "rx"; };

Mengatur kartu suara di bagan perangkat (kartu audio):

sound { compatible = "simple-audio-card"; simple-audio-card,name = "TLV320AIC34"; simple-audio-card,format = "i2s"; simple-audio-card,bitclock-master = <&dailink0_master>; simple-audio-card,frame-master = <&dailink0_master>; simple-audio-card,widgets = ... simple-audio-card,routing = ... dailink0_master: simple-audio-card,cpu { clocks = <&i2s_clk>; sound-dai = <&axi_i2s_adi_0>; }; simple-audio-card,codec { clocks = <&i2s_clk>; sound-dai = <&tlv320aic3x>; }; }; };

Setelah semua manipulasi untuk mengkonfigurasi dan mengkonfigurasi codec di pohon perangkat di Linux, kartu audio yang didambakan muncul dan kami dapat mendengar musik (trek musik pertama kami adalah Highway to Hell, AC / DC).

Inilah yang harus kami lakukan untuk ini:

- Menghasilkan frekuensi yang diperlukan menggunakan clk_wiz (pemandu jam)

- DTS yang dikonfigurasi dengan benar untuk tlv320aic34

- Dukungan tambahan untuk driver tlv320aic3x

- Menambahkan paket audio ke buildroot untuk memutar aliran audio (aplay, madplay, dll.)

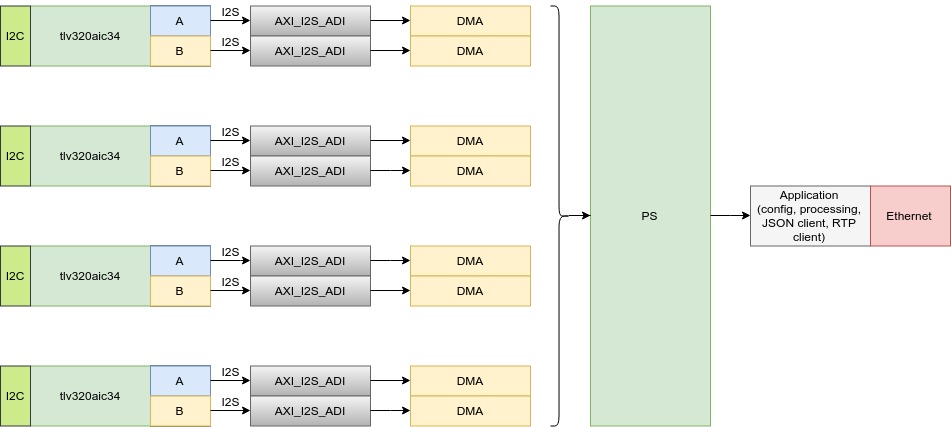

Dalam proses pengembangan perangkat akhir, kami dihadapkan dengan tugas untuk menghubungkan 4 tlv320aic34 microcircuits. Chip tlv320aic34 yang dijelaskan di atas berisi 2 blok untuk bekerja dengan stream audio, setiap blok memiliki jalur i2c sendiri untuk mengkonfigurasi dan mengatur parameter audio. Satu blok hanya dapat memiliki empat alamat, masing-masing, tidak mungkin untuk menghubungkan empat microcircuits tlv320aic34 ke satu antarmuka i2c, Anda perlu menggunakan dua antarmuka i2c (8 blok audio independen). Untuk setiap blok, jika Anda memulai mclk, blck, wclk, din / dout secara individual, Anda perlu menambahkan 40 garis sinyal secara total, yang tidak mungkin dan tidak rasional dari sudut pandang sirkuit untuk modul som yang kita pilih, karena selain sinyal-sinyal ini, Anda harus menghubungkan banyak jalur lain dan antarmuka.

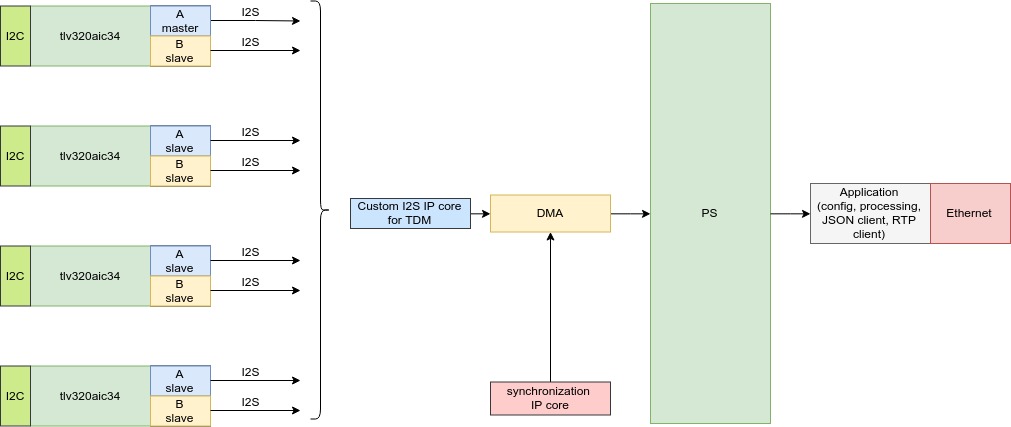

Sebagai hasilnya, kami memutuskan untuk mengganti kartu audio ke

mode TDM , di mana semua garis mclk, bclk, din, dout digabungkan, yang mengurangi jumlah total jalur komunikasi. Keputusan ini mempengaruhi pengoperasian axi-i2s-adi, karena fakta bahwa inti ip itu sendiri bekerja dalam mode master. Juga, perubahan ini tidak memungkinkan kami untuk menggunakan ip-core kami dalam mode TDM, dan keputusan yang berkemauan keras kami harus meninggalkan penggunaan ip-core yang dipilih. Saya harus menulis sebuah kernel ip untuk mendengarkan lalu lintas i2s dan mengirimkannya ke dma, solusi ini memungkinkan kami untuk membuat antarmuka umum untuk menerima data yang tidak akan tergantung pada jenis kartu untuk merekam panggilan (kartu analog dan digital).

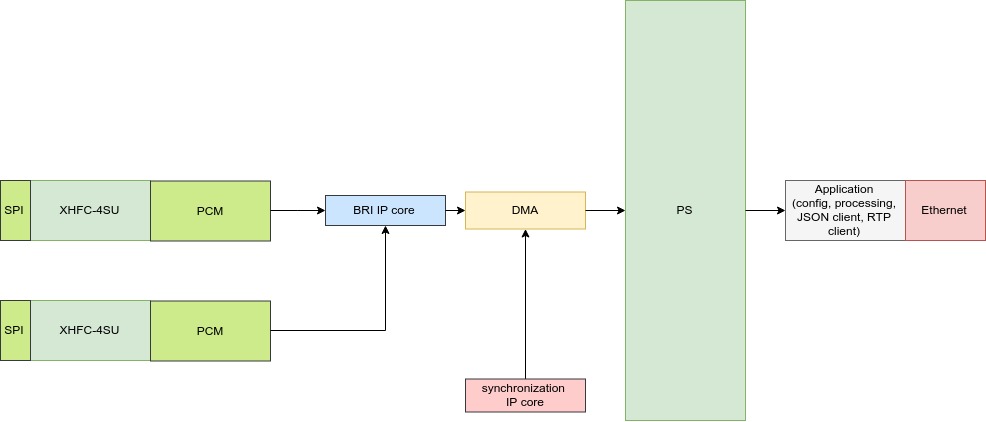

Arsitektur awal untuk menerima aliran audio dan pemrosesannya melalui antarmuka i2s:

Arsitektur terakhir untuk menerima aliran audio dan pemrosesannya melalui antarmuka i2s:

Arsitektur menerima aliran PRI dan pemrosesannya:

Arsitektur penerimaan dan pemrosesan aliran BRI:

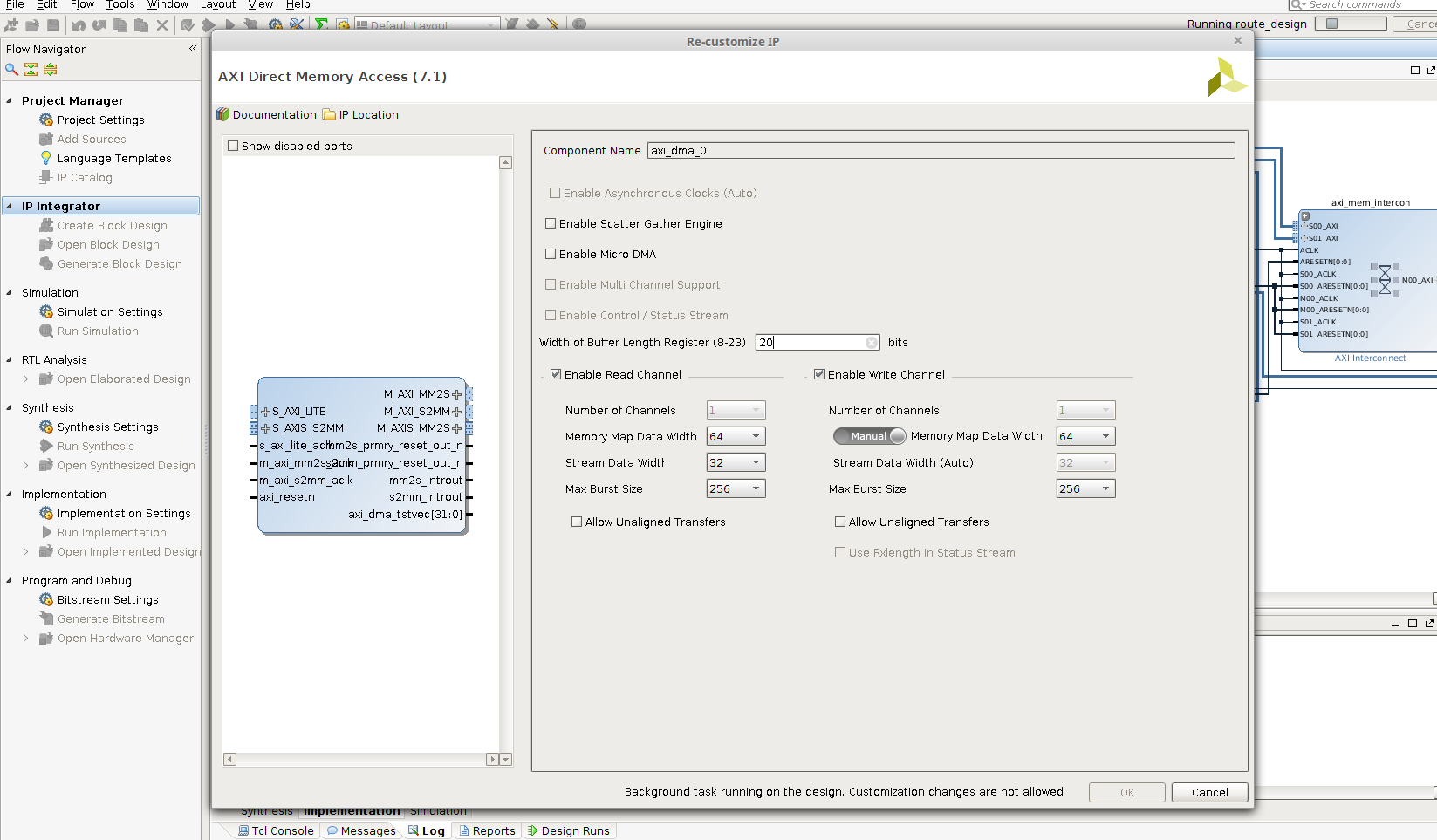

Axi dma

Ini adalah elemen penting dari sistem sinkronisasi data untuk dma.

Jendela Konfigurasi DMA AXI di Xilinx Vivado

Jendela Konfigurasi DMA AXI di Xilinx VivadoPada layar cetak, blok DMA AXI itu sendiri disajikan. Ini memiliki banyak parameter. Anda dapat mengkonfigurasi bus berapa banyak data untuk ditransfer. Data dapat disejajarkan atau dalam format apa pun. Deskripsi terperinci tentang operasi dan interaksi dengan axi dma dijelaskan

dalam dokumentasi teknis (dari versi ke versi ada tambahan dan koreksi ketidakakuratan dalam deskripsi, serta penyempurnaan kernel ip).

Verifikasi transfer data melalui AXI DMA, opsi tes AXI DMA

Ketika mengembangkan driver, kami memutuskan untuk mencari sumber terbuka dan menyesuaikannya dengan tugas kami. Sebagai hasilnya, kami memilih sumber-sumber

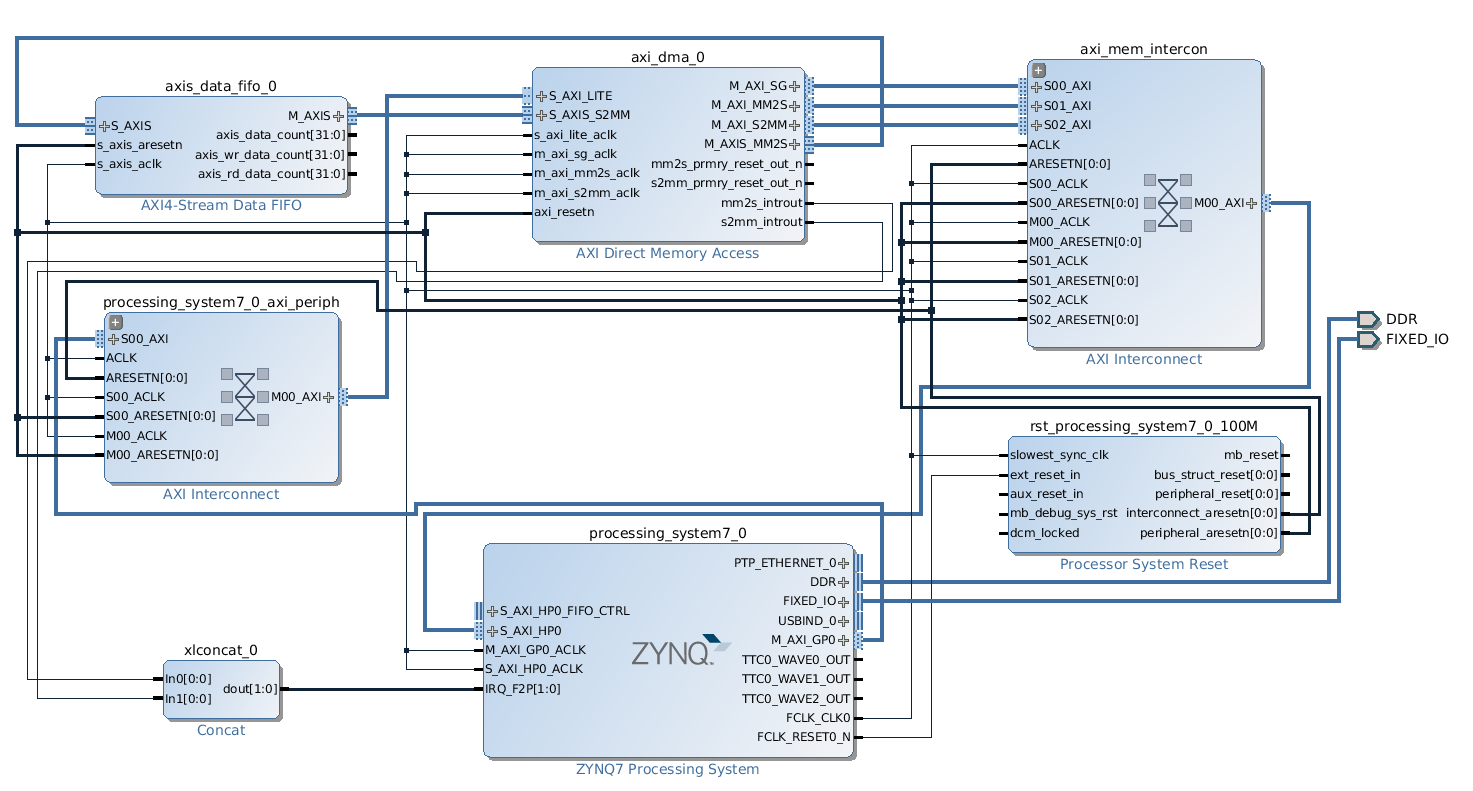

proyek ezdma github (pun, baca sebagai dma mudah).

Langkah selanjutnya adalah pengembangan driver tes, itu adalah tahap persiapan untuk mengantisipasi saat ketika ip core dengan fungsi siap pakai dari departemen pengembangan FPGA mendatangi kami (proses pengembangan yang dijelaskan dibentuk oleh embedded programmer). Sebelum saat ini kami memutuskan untuk mengambil AXI DMA, AXI DATA FIFO dan membuat loopback untuk memastikan terhadap kesalahan di masa mendatang. Kami mengulangi pengiriman dan penerimaan data, jadi kami memeriksa hasil pekerjaan kami dan kinerja pengemudi kami. Kami menyesuaikan fungsi sedikit, membawanya ke keinginan kami pada antarmuka interaksi dan sekali lagi memeriksa pengoperasian driver dan prinsip interaksi yang dipilih.

Desain blok look-back, cara pertama untuk menguji AXI DMA

Desain blok look-back, cara pertama untuk menguji AXI DMAContoh deskripsi DMA dan ezdma di bagan perangkat:

/ { amba_pl: amba_pl { #address-cells = <1>; #size-cells = <1>; compatible = "simple-bus"; ranges ; axi_dma_1: axi_dma { #dma-cells = <1>; compatible = "xlnx,axi-dma-1.00.a"; reg = <0x40400000 0x10000>; clock-names = "s_axi_lite_aclk", "m_axi_sg_aclk", "m_axi_mm2s_aclk", "m_axi_s2mm_aclk"; clocks = <&clkc 15>, <&clkc 15>, <&clkc 15>, <&clkc 15>; interrupt-parent = <&intc>; interrupts = <0 29 4 0 30 4>; xlnx,addrwidth = <0x20>; xlnx,include-sg; dma-channel@40400000 { compatible = "xlnx,axi-dma-mm2s-channel"; dma-channels = <0x1>; interrupts = <0 29 4>; xlnx,datawidth = <0x20>; xlnx,device-id = <0x0>; xlnx,include-dre ; }; dma-channel@40400030 { compatible = "xlnx,axi-dma-s2mm-channel"; dma-channels = <0x1>; interrupts = <0 30 4>; xlnx,datawidth = <0x20>; xlnx,device-id = <0x0>; xlnx,include-dre ; }; }; ezdma0 { compatible = "ezdma"; dmas = <&axi_dma_1 0 &axi_dma_1 1>; dma-names = "loop_tx", "loop_rx"; // used when obtaining reference to above DMA core using dma_request_slave_channel() ezdma,dirs = <2 1>; // direction of DMA channel: 1 = RX (dev->cpu), 2 = TX (cpu->dev) }; ... }; };

Anda dapat dengan mudah menghasilkan file dts / dtsi menggunakan alat

Device Tree Generator .

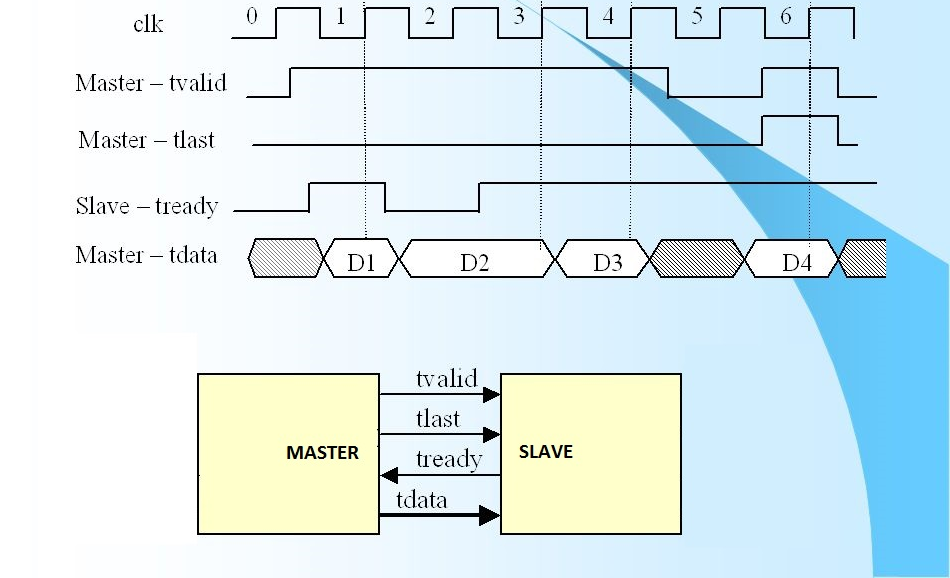

Langkah kedua dalam proses pengembangan kami adalah pembuatan ip-kernel test untuk memeriksa kinerja driver, hanya saja kali ini datanya akan bermakna, dengan transfer via AXIS ke AXI_DMA (karena itu akan menjadi versi final dari ip-kernel).

Alur kerja antarmuka AXIS

Alur kerja antarmuka AXISKami menerapkan dua varian ip-kernel untuk pembuatan data, versi yang diuji pertama kali dilaksanakan melalui Verilog, yang kedua - pada HLS (dalam konteks ini, HLS muncul di bawah slogan "fashion-fashion-youth").

Generator data Verilog (dan umumnya dalam bahasa keluarga hdl - Verilog, vhdl, dll.) Adalah solusi standar ketika mengembangkan ip-core jenis ini. Berikut ini beberapa cuplikan kode untuk kernel ip perantara:

module GenCnt ( …. assign HandsHake = m_axis_din_tready & m_axis_dout_tvalid; always @(posedge Clk) begin if (Rst) begin smCnt <= sIDLE; end else begin case (smCnt) sIDLE: begin smCnt <= sDATA; end sDATA: begin if (Cnt == cTopCnt - 1) begin smCnt <= sLAST; end end ... endmodule

Tidak perlu deskripsi yang lebih rinci, karena ini adalah tugas khas seorang desainer FPGA.

"Binatang buas" yang lebih menarik di sini adalah HLS.

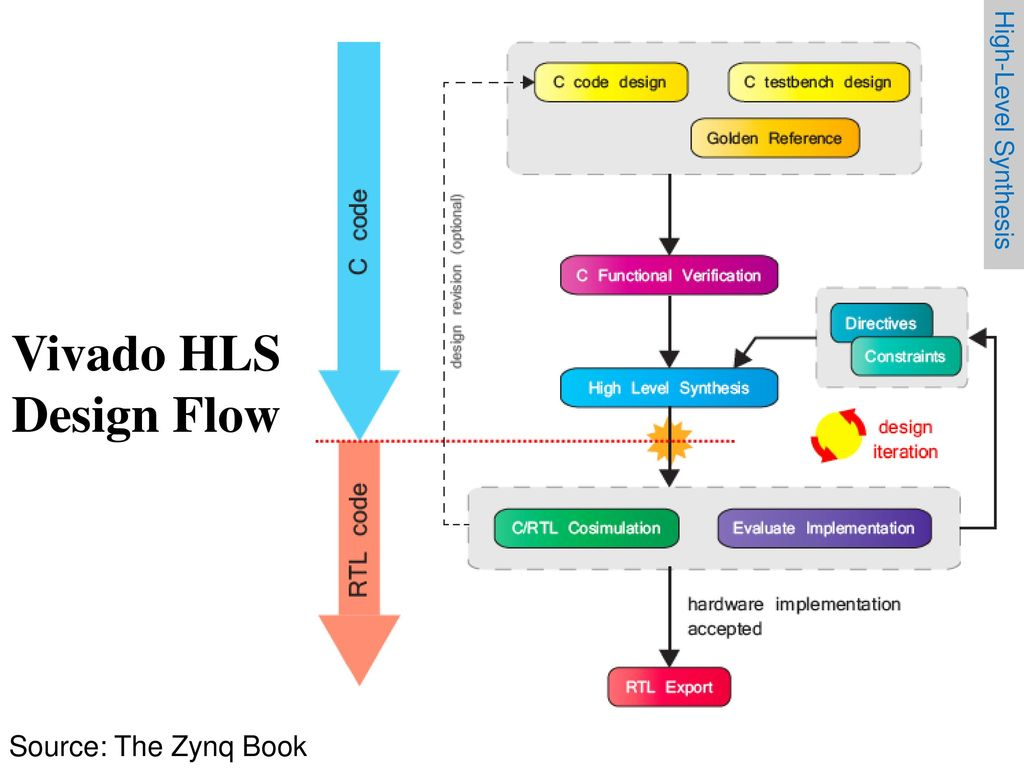

Vivado HLS (Sintesis Tingkat Tinggi) adalah perangkat lunak Xilinx CAD baru untuk membuat perangkat digital menggunakan bahasa tingkat tinggi seperti OpenCL, C atau C ++.

C / C ++ adalah bahasa utama untuk insinyur perangkat lunak tertanam, jadi menyelesaikan masalah dengan menggunakan bahasa ini lebih menarik dalam hal implementasi dan analisis komparatif untuk proyek-proyek masa depan.

Berikut adalah dua contoh kecil bekerja dengan HLS. Contoh pertama adalah generator data untuk AXI_DMA, contoh kedua adalah pertukaran data antara bagian prosesor dan logika yang dapat diprogram melalui antarmuka s_axilite.

Pertukaran data melalui antarmuka s_axilite (contoh kedua) diimplementasikan sehingga setiap saat di procfs dimungkinkan untuk mengurangi bitstream mana yang dimuat, dan sehingga dimungkinkan untuk melacak kebenaran pekerjaan dengan membuat versi untuk bagian PL dari SoC. Di sini poin yang sangat menarik muncul dengan s_axilite: Vivado HLS menghasilkan driver untuk Linux (driver, pada gilirannya, kami beradaptasi untuk bekerja melalui procfs untuk menjaga hereditas penulisan). Contoh kode yang dihasilkan untuk Linux di bawah ini (jalur ke sumber solution1 / impl / ip / drivers / name_xxx / src /).

Tahapan sintesis HLS dan pembuatan kode rtl

Tahapan sintesis HLS dan pembuatan kode rtlGenerator data HLS untuk memeriksa operasi dengan AXI_DMA:

#include <ap_axi_sdata.h> #include <hls_stream.h> #define SIZE_STREAM 1024 struct axis { int tdata; bool tlast; }; void data_generation(axis outStream[SIZE_STREAM]) { #pragma HLS INTERFACE axis port=outStream int i = 0; do{ outStream[i].tdata = i; outStream[i].tlast = (i == (SIZE_STREAM - 1)) ? 1 : 0; i++; }while( i < SIZE_STREAM); }

Contoh untuk mendapatkan versi dan jenis papan antarmuka:

#include <stdio.h> void info( int &aVersion, int &bSubVersion, int &cTypeBoard, int version, int subVersion, int typeBoard ){ #pragma HLS INTERFACE s_axilite port=aVersion #pragma HLS INTERFACE s_axilite port=bSubVersion #pragma HLS INTERFACE s_axilite port=cTypeBoard #pragma HLS INTERFACE ap_ctrl_none port=return aVersion = version; bSubVersion = subVersion; cTypeBoard = typeBoard; }

Seperti yang Anda perhatikan, untuk pengembangan pada hls, sangat penting untuk memahami pekerjaan dan penerapan berbagai pragma (pragma HLS), karena proses sintesis terkait langsung dengan pragma.

Driver yang dibuat untuk s_axilite:

File penting yang memberi tahu Anda lokasi variabel (register) di ruang alamat adalah file x # nama_anda # _hw.h. Anda selalu dapat memverifikasi kebenaran ip-kernel tertulis menggunakan alat devmem.

Isi file ini:

File ini menjelaskan alamat register, register sesuai dengan lokasi argumen dalam fungsi. Setelah sintesis proyek, Anda dapat melihat bagaimana proyek yang dibuat akan dieksekusi dalam siklus.

Contoh Ketukan Proyek

Contoh Ketukan ProyekBekerja dengan hls telah menunjukkan bahwa alat ini cocok untuk menyelesaikan tugas dengan cepat, terutama telah membuktikan dirinya untuk memecahkan masalah matematika penglihatan komputer, yang dapat dengan mudah dijelaskan dalam C ++ atau C, serta untuk membuat kernel ip kecil untuk interaksi dan pertukaran informasi dengan antarmuka FPGA standar.

Pada saat yang sama, HLS tidak cocok untuk mengimplementasikan antarmuka perangkat keras tertentu, misalnya, dalam kasus kami adalah I2S, dan kode rtl yang dihasilkan membutuhkan lebih banyak ruang pada FPGA daripada ditulis dalam bahasa hdl standar.

Langkah terakhir dalam pengujian driver adalah pengembangan generator traffic I2S. Ip-core ini mengulangi fungsionalitas dari ip-kernel sebelumnya, kecuali bahwa ia menghasilkan data tambahan (lalu lintas) yang sesuai dengan data I2S nyata dalam mode TDM.

Blokir desain untuk pengujian inti I2S kustom masa depan dan generator lalu lintas I2S

Blokir desain untuk pengujian inti I2S kustom masa depan dan generator lalu lintas I2SAkibatnya, kami mendapat hasil hls, axi dma dan s_axilite, memeriksa kinerja perangkat lunak dan driver kami.

Kesimpulan

Kami berhasil mengembangkan jenis kartu antarmuka yang diperlukan, serta ip-kernel untuk tdm, pri, bri. Kami telah secara signifikan meningkatkan pendekatan saat ini untuk pengembangan perangkat tersebut dan menciptakan solusi komprehensif yang dapat bersaing dengan papan antarmuka serupa dari

Asterick ,

patton , dan lainnya. Keuntungan dari solusi kami adalah bahwa pengembang tidak memerlukan tautan perantara antara PC dan PCI untuk transfer data, ia akan dapat secara langsung mengirimkan informasi yang diterima melalui Ethernet.