Pekan lalu, Intel mengumumkan akuisisi eASIC, yang sedang mengembangkan alat pengembangan berbasis FPGA untuk "ASIC struktural". ASIC Struktural adalah persilangan antara FPGA konvensional dan ASIC konvensional; mereka memungkinkan Anda untuk mengurangi waktu memasarkan produk dan mengurangi biayanya.

Intel telah menggunakan teknologi eASIC

sejak 2015 dalam versi khusus prosesor Xeon; eASIC (120 orang) sekarang akan menjadi bagian dari Intel Programmable Solutions Group (PSG).

Bahkan mereka yang sudah lama dan saling "berteman" dengan FPGA dan ASIC tidak akan menolak untuk menjelaskan apa "ASIC struktural" itu. Kekuatan komputasi komputer tidak terbatas pada CPU atau GPU, ada kelas-kelas prosesor lain, seperti, misalnya, FPGA - mereka dikembangkan oleh Altera, diakuisisi oleh Intel. Dalam FPGA, jutaan gerbang dapat diprogram secara fleksibel untuk mengimplementasikan fungsi yang diperlukan. Bahkan, sebagian besar CPU dan GPU awalnya disimulasikan pada FPGA untuk menguji kinerja. FPGA adalah cara sederhana untuk memodelkan sirkuit interkoneksi, dan cakupannya luas. FPGA juga dapat berisi unit perangkat keras yang tidak tersedia, seperti ARM core atau transceiver untuk komunikasi eksternal.

Contoh lain adalah ASIC (Application Specific Integrated Circuit), sebuah chip yang dirancang untuk melakukan serangkaian tugas yang terdefinisi dengan baik. ASIC dioptimalkan secara maksimal untuk tugas-tugasnya, dan logika kerjanya tidak dapat diubah. Seringkali, CPU dan GPU diklasifikasikan sebagai ASIC dalam arti bahwa arsitektur mikro mereka juga diperbaiki, tetapi mereka dirancang untuk menyelesaikan berbagai masalah dan bersifat universal, sementara ASIC dibuat untuk jenis perhitungan yang didefinisikan dengan jelas. Fitur ASIC: mereka cepat, ekonomis, tetapi relatif mahal dan sulit untuk diproduksi.

Struktural ASIC EASIC dapat disebut solusi setengah hati. Insinyur membuat prototipe menggunakan FPGA, tetapi jangan buang waktu untuk mengoptimalkan sirkuitnya, tetapi memproduksi chip dengan arsitektur tetap berdasarkan basisnya. Karena ini, ia bekerja lebih cepat daripada sampel dengan blok khusus, meskipun kehilangan manfaat efisiensi energi. Namun, waktu untuk pengembangannya sebanding dengan FPGA, bukan ASIC - menghemat hingga 6 bulan. Kontribusi eASIC adalah bahwa optimasi lapisan tunggal digunakan untuk menggantikan rute SRAM dengan ujung ke ujung, yang secara signifikan mengurangi biaya produksi. EASIC juga menyediakan pustaka sel yang tetap, juga satu lapis, yang selanjutnya mengurangi konsumsi, ukuran kristal dan waktu untuk memasarkan. Selain itu, desainer dapat melewati prosedur standar saat membuat ASIC, seperti sinkronisasi balancing, analisis integritas sinyal, uji redaman daya, dan lainnya. Dengan demikian, "ASIC struktural" dapat digambarkan sebagai FPGA yang tidak dapat diprogram lebih lanjut, yang memiliki kualitas terbaik dari FPGA dan ASIC.

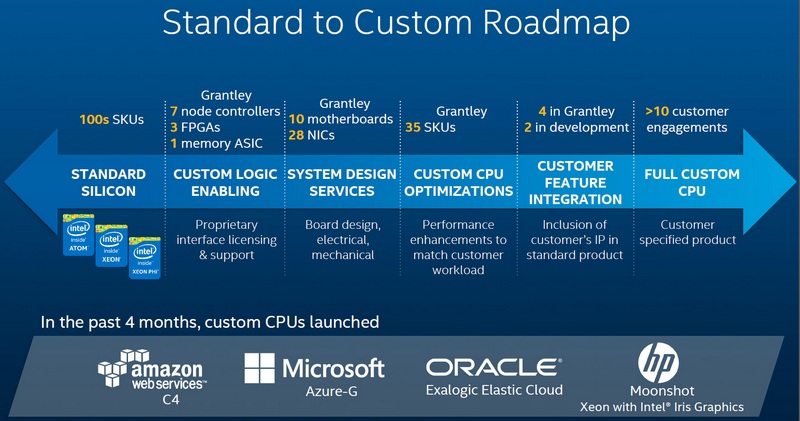

Grafik menunjukkan keadaan terkini dan prospek di bidang prosesor Intel Xeon khusus

Grafik menunjukkan keadaan terkini dan prospek di bidang prosesor Intel Xeon khususIntel membutuhkan teknologi eASIC untuk mengintegrasikan logika yang dapat diprogram ke dalam prosesor Xeon untuk meningkatkan kinerja, konsumsi daya, dan harga. Seiring dengan Xeon standar, Intel sekarang merilis opsi kustom untuk pelanggan terbesarnya. Seperti yang dapat kita lihat dari diagram, kedalaman kustomisasi akan meningkat. Dengan akuisisi eASIC, proses ini akan mempercepat dan berkembang. Tampaknya pendekatan "CPU as ASIC" dapat membawa kita banyak hal menarik.