1. Pendahuluan

Kita semua tahu masalah ayam dan telur: pengusaha tidak ingin mempekerjakan lulusan tanpa pengalaman kerja, tetapi di mana, kemudian, apakah lulusan bisa mendapatkan pengalaman kerja? Dalam mikroelektronika, masalah ini sangat akut mengingat besarnya jumlah pengalaman spesifik yang diperlukan. Sejak zaman Soviet, universitas kami terkenal dengan pelatihan teori terluas, yang seharusnya membantu lulusan dalam situasi sulit apa pun dalam kehidupan. Namun, industri modern membutuhkan pengalaman praktis. Kami menambahkan di sini kurangnya motivasi, yang mengarah pada fakta bahwa 15% lulusan bekerja di bidang khusus, dan kami mendapatkan kekurangan staf paling parah di industri, yang sangat menuntut kualitas personel. Tetapi jika setiap siswa dapat "mengedipkan bola lampu" dari kristal sendiri, situasinya dapat berkembang dengan cara yang sama sekali berbeda.

Gambar 1. KDPV

Apa yang mencegah raksasa seperti pelatihan mikroelektronika dalam negeri, seperti MEPhI dan MIET, dari bertindak serupa dengan rekan asing mereka (misalnya, MIT atau UZH), yaitu, dengan memungkinkan mahasiswa pascasarjana untuk mengeluarkan kristal mereka sendiri? Tentu saja, dapat diasumsikan bahwa produksi kristal sendiri adalah tugas yang sangat panjang, rumit dan mahal, dan karena itu mahal untuk sebuah lembaga dan tidak mungkin bagi seorang siswa. Namun, ini tidak benar. Mari kita lihat salah satu teknologi yang tersedia di pasar mikroelektronika dalam negeri, perkenalan yang akan memungkinkan siswa untuk menjadi jauh lebih menarik dalam hal pekerjaan di masa depan, dan tawaran yang bagi siswa akan memungkinkan universitas untuk secara signifikan meningkatkan peringkatnya di mata pelamar dan pengusaha.

2. Apa itu BMK?

BMK adalah kristal matriks dasar. Bukankah itu menjadi lebih jelas? Kemudian ambil langkah ke samping dan lihat siklus produksi custom-chip manufacturing (ASIC) yang sangat disederhanakan:

- Deskripsi Skema Pengembangan

- Penciptaan Topologi

- Mentransfer file teknologi ke pabrik dan menunggu kristal siap

- Pengukuran kristal yang diperoleh

- Casing

- Dijual

Ada dua poin yang sangat "panjang" di sini - pengembangan skema dan ekspektasi hasil pabrik. Berbagai metodologi digunakan untuk mengurangi waktu pengembangan, dan dalam lingkungan siswa solusi terbaik adalah kerja tim, tetapi kami tertarik pada poin kedua - jam kerja pabrik. Karena fakta bahwa pabrik mikroelektronik adalah produksi yang sangat lembam, semuanya harus sesuai dengan rencana. Tidak tepat waktu untuk tanggal peluncuran produksi? Upaya selanjutnya adalah melalui kuartal. Produksi itu sendiri, tergantung pada kompleksitas produk, dapat bertahan hingga enam bulan. Selain itu, enam bulan ini adalah siklus produksi yang disetujui pada mesin yang sangat otomatis, dan bukan kecerobohan personel. Bagaimana istilah-istilah ini dapat dikurangi? Dengan memperkenalkan dasar umum tertentu dalam semua skema yang diproduksi, sehingga tahap memperkenalkan perbedaan cepat.

Basis umum ini adalah BMK - kristal dengan transistor yang telah diatur sebelumnya, tujuan fungsionalnya ditentukan oleh lapisan metalisasi, yang memungkinkan transistor saling berhubungan. Interkoneksi ini membentuk fungsi unik kristal.

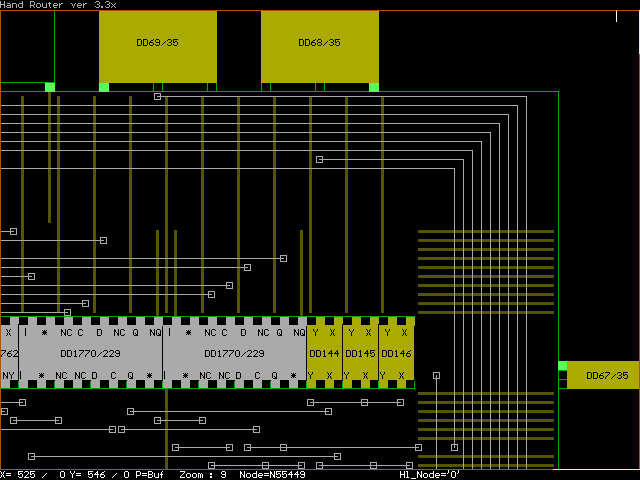

Gambar 2. Hand Router v3.3, berasal dari perut NICEVT, dibuat pada 1980-an-1990-an.

Pada satu BMK, menggunakan skema metalisasi yang berbeda, adalah mungkin untuk menghasilkan ratusan sirkuit mikro yang berbeda untuk berbagai organisasi. Dalam hal ini, BMK sendiri menjadi produk produksi massal untuk pabrik, dan tahap finishing - lapisan metalisasi, dapat dengan cepat diubah sesuai dengan kebutuhan pelanggan. Dengan demikian, kita lebih sering "meluncurkan" produk baru ke dalam produksi dan harga lebih rendah. Untuk pengembangan siswa, kedua poin ini sangat relevan.

3. Mengapa BMK?

Mari kita bandingkan manfaat menggunakan metode pelatihan yang berbeda dan lihat apa yang memberikan efek terbesar dengan biaya terendah.

Tabel 1. Perbandingan efek pendidikan dari pembelajaran menggunakan berbagai metode

Pengkodean header jika tidak, tidak sesuai dengan lebar tata letak.

A - pengembangan berorientasi FPGA

B - BMK tanpa menggunakan FPGA dan dengan rilis nyata

C - BMK menggunakan FPGA dan dengan rilis nyata

D - ASIC tanpa FPGA dan tanpa rilis nyata

E - ASIC dengan FPGA dan tidak ada rilis nyata

F - ASIC dengan FPGA dan rilis nyata

G - Program pelatihan saat ini di MEPhI, kaf. 27

| Komponen rute | A | B | C | D | E | F | G |

|---|

| Pernyataan masalah | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Pemrograman RTL | ■ | ■ | ■ | ■ | ■ | ■ | ■ |

| Pemrograman RTL berbasis ASIC | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Bekerja dengan CAD modern | ○ | ■ | ■ | ■ | ■ | ■ | ○ |

| Memahami kode spesifik FPGA | ■ | □ | ■ | □ | ■ | ■ | ○ |

| Memahami Synthesizer | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Memahami Persyaratan Membatasi | ○ | ■ | ■ | □ | □ | ■ | □ |

| Memahami pentingnya penempatan dan penelusuran | ○ | ■ | ■ | □ | □ | ■ | □ |

| Pengujian | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Pembuatan lingkungan verifikasi | ■ | ■ | ■ | □ | ■ | ■ | □ |

| Simulasi multi-sudut | ■ | ■ | ■ | ■ | ■ | ■ | □ |

| Pemodelan ekstraksi | □ | ■ | ■ | ■ | ■ | ■ | □ |

| Casing | □ | ■ | ■ | □ | □ | ■ | □ |

| Sirkuit analog | □ | ■ | ■ | ■ | ■ | ■ | ○ |

| Bekerja dengan mengukur instalasi | □ | ■ | ■ | □ | □ | ■ | ○ |

| Bekerja di laboratorium | ■ | ■ | ■ | □ | □ | ■ | ○ |

| Biaya | 1 | 2 | 3 | 0 | 1 | 4 | 0 |

■ - hadir dalam program;

□ - tidak ada dalam program;

○ - opsi dimungkinkan.

Tabel ini diisi semata-mata dari visi saya tentang bagaimana kehadiran tahap tertentu dalam proyek kelulusan bola dalam ruang hampa mempengaruhi ketekunan siswa. Pada kenyataannya, seseorang dapat menguasai seluruh rute tanpa bantuan pengajaran, sementara seseorang tidak dapat menulis multiplexer di Verilog. Garis "biaya" mencerminkan pemosisian di atas, tetapi dalam pengganda kasus apa pun. Juga, "biaya" tidak memperhitungkan biaya aktual CAD, karena sejumlah alasan berbeda.

Sekarang menjadi jelas bahwa dengan biaya tambahan yang lebih rendah, rute yang ditujukan untuk rilis BMK, menggunakan FPGA dan dengan rilis nyata mencakup set keterampilan yang sama persis yang diperlukan untuk rilis ASIC. Sisa dari rute, meskipun secara nominal mencakup berbagai keterampilan, dalam praktiknya, mereka tidak dilakukan dengan hati-hati oleh siswa karena kurangnya motivasi untuk menerapkan banyak upaya tanpa hasil yang terlihat.

4. Market Watch

Sampai saat ini, desain sirkuit mikro tingkat awal telah menjadi tugas yang cukup sederhana: semua orang telah mendengar tentang FPGA (sirkuit terintegrasi logika yang dapat diprogram), synthesizer dari kode, program untuk mengatur komponen dan jejak berikutnya dari rangkaian mikro. Pada saat yang sama, banyak pengembang pemula mengalami kesulitan membayangkan apa itu BMK, bagaimana bekerja dengannya, dan apa keuntungan yang diberikannya. Sayangnya untuk produsen BMK, situasi ini mengarah pada hasil berikut:

"Analisis 2009 menunjukkan arus keluar beberapa konsumen karena perluasan ruang lingkup aplikasi FPGA impor berdasarkan izin yang dikeluarkan." (C) laporan tahunan Anstrem OJSC untuk tahun 2009.

Ada banyak produsen BMK di pasar mikroelektronika modern: baik domestik maupun asing. Secara khusus, di Negara Uni Rusia dan Belarus ada setidaknya enam produsen chip yang menawarkan BMC mereka untuk pengembangan: Angstrem OJSC, IEC NN, Progress NIIMA JSC, Pusat Teknologi Ilmiah dan Produksi, Fisika NPO OJSC dan Integral Minsk ".

Biasanya, sistem CAD khusus perusahaan terkenal seperti Cadence, Sinopsis atau Mentor Graphics digunakan untuk pengembangan sirkuit mikro, tetapi dalam kasus BMC, semuanya agak lebih rumit. Perangkat lunak ini tidak memberikan dukungan resmi untuk BMK, sebagai jenis rangkaian mikro terpisah, tetapi dimungkinkan untuk membuatnya bekerja dalam mode yang tepat menggunakan berbagai trik. Dalam situasi ini, pengembang BMK harus mengembangkan rute desain unik mereka sendiri, yang terkadang menggunakan perangkat lunak OpenSource, misalnya, Yosis, bersama dengan perangkat lunak yang dikembangkan secara independen.

- Dalam kasus Angstrom OJSC, sangat sulit untuk menemukan informasi yang tepat dan CAD yang digunakan. Namun, ada prasyarat untuk percaya bahwa CAD mereka "Nevod" tidak lagi digunakan dan transisi ke penggunaan produk Cadence telah selesai.

- IEC NN, OJSC NPO Fizika, JSC NIIMA Kemajuan dan Integral tidak memberikan informasi tentang CAD yang digunakan, namun Integral memiliki PDK di bawah irama, sehingga kami dapat menyimpulkan bahwa sisa rute juga ada di sana.

- "Pusat Teknologi" NPK menggunakan CAD "Ark", yang mengimplementasikan hampir seluruh rute desain. Bagaimanapun, ini disetujui di situs web mereka.

5. Berapa banyak katup yang cukup untuk semua orang?

Alasan populer untuk keengganan untuk bekerja dengan BMK adalah ketidakpastian tentang apakah skema yang dikembangkan akan cocok dengan BMK ini dan pada kecepatan apa semua ini akan bekerja. Tentu saja, itu baik ketika ada seri BMK dengan perpustakaan desain tunggal, dan Anda dapat melompat ke kristal yang lebih luas atau lebih cepat jika diperlukan, tetapi ini tidak selalu memungkinkan. Di sini, misalnya, semuanya jelas tentang TSMC: ada banyak perusahaan yang secara terbuka menyatakan kecepatan sirkuit mereka dilakukan pada satu atau yang lain dari mereka. proses. Bagaimana dengan BMK kita? Di mana saya bisa mendapatkan daftar produk yang dibuat berdasarkan BMK dan melihat kinerjanya?

Beberapa contoh:

- BMK digital-ke-analog. Sekitar 300 gerbang + 8 transistor daya. Skema pengatur waktu selama 2 menit dengan dua tingkat perlindungan diterapkan. Pemantauan beban pada mirror saat ini, transistor daya untuk mengontrol beban. Pengurangan konsumsi daya, bekerja dengan kuarsa 32.768 kHz, kisaran tegangan pasokan dari 1.8V ke 9V.

- Digital senang. BMK persisten. 100.000 katup. Logika spesial. tujuan + NCO (osilator yang dikontrol secara numerik). Fase baterai 40 bit, sinus - 12 bit. Dua register mengontrol frekuensi sinus, paralel dan kontrol serial. Outputnya paralel.

- BMK digital-ke-analog. Sekitar 400 gerbang + DAC dari 10 kategori. Generator sinus 7-bit dengan output saat ini.

- BMK digital. Dari 1500 hingga 3000 katup. Berbagai terminal saluran multipleks GOST 26765.52-87.

- BMK digital. Sekitar 500 gerbang. Generator delapan saluran untuk mengendalikan belitan utama transformator.

- BMK digital. Sekitar 3000 gerbang. Sirkuit mayoritas untuk bus 8 bit.

Sayangnya, kekhasan pasar mengarah pada fakta bahwa sebagian besar perkembangan di BMK tetap tidak diketahui oleh masyarakat umum. Data publik tidak memberikan gagasan yang jelas tentang kecepatan, dan angka-angka yang tercantum dalam brosur terlihat ambigu. Namun, untuk tugas mengenal teknologi, banyak yang tidak diperlukan, dan sudah memiliki beberapa pengalaman di belakangnya, jauh lebih mudah untuk memberikan perkiraan perkiraan kerumitan skema tertentu.

6. Proses pengembangan

Mari kita beralih ke yang paling menarik. Kami memiliki: BMK untuk ~ 3k katup (1 katup = 2 transistor CMOS) dengan arsitektur saluran, kabel dalam satu lapisan logam dan sublapisan polisilikon; antusiasme; persetujuan manajemen perusahaan untuk pelatihan mandiri karyawan.

Gagasan kristal masa depan lahir dari kemalasan, yaitu dari membaca satu forum, di mana, khususnya, ada percakapan tentang solusi sirkuit-kompak untuk menghitung kode sinus. Topik ini sepertinya menarik bagi saya, dan saya memutuskan untuk melihat apa yang bisa dilakukan ke arah ini.

Sekarang mari kita lihat apa yang dilakukan, apa yang tidak, kesalahan apa dan kesimpulan apa yang dibuat.

6.1 Desain

Studi permukaan telah menunjukkan bahwa ada algoritma untuk menghitung nilai sinus, yang dari operasi matematika hanya membutuhkan penjumlahan, pengurangan dan pergeseran ke kanan. Ternyata ini bukan hanya sebuah algoritma, tetapi seluruh keluarga bernama CORDIC (Coordinate Rotation Digital Computer). Mereka yang tertarik dengan detail algoritma dapat merujuk ke daftar referensi di akhir artikel, tetapi saya hanya akan menjelaskan bahwa menggunakan algoritma ini Anda tidak hanya dapat menghitung sinus, tetapi juga kosinus, garis singgung, melipatgandakan dan membagi argumen, dan menghitung beberapa fungsi hiperbolik.

Setelah mempelajari banyak publikasi tentang algoritma ini, dan mensistematisasikan pengetahuan ini di kepala saya, saya pikir Anda dapat mencoba mengimplementasikan algoritma ini pada BMK dengan kapasitas sekitar 3k katup.

Jadi apa yang kita dapatkan dengan arsitektur sirkuit?

- Algoritma CORDIC pipelined yang diperluas untuk menghitung sinus.

- 4 bit tambahan dalam bus data internal untuk mengkompensasi kesalahan pembulatan.

- 11 bit penghitung akumulatif untuk nilai fase.

- Peningkatan fase diatur oleh bus paralel.

- Format data output: 7 bit + tanda, bus paralel.

Semuanya tampak baik-baik saja, tetapi apa yang terjadi jika Anda tidak mengganti kesalahan pembulatan? Dan inilah caranya (membandingkan bus internal 11bit dan 8bit):

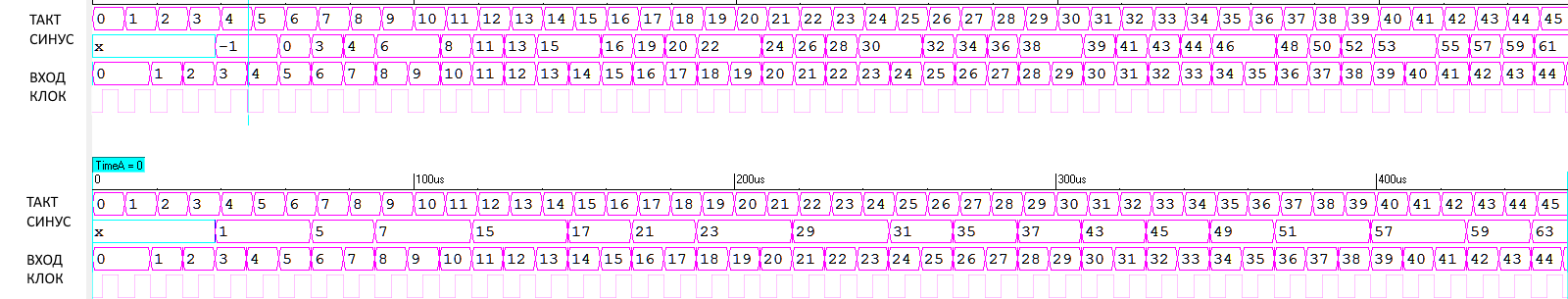

Gambar 3. Perbandingan output dari algoritma CORDIC saat menggunakan bus internal 11bit dan 8bit, masing-masing.

Jika Anda memperhatikan data baris kedua, Anda dapat melihat bahwa kesalahan pembulatan secara efektif dapat menurunkan kualitas perhitungan Anda.

Jika di masa depan kami pasang chip ini ke DAC 7-bit, kami mendapatkan generator sinus yang sangat cocok (DDS, menurut kami - sintesis digital langsung). Dalam hal ini, kita akan memiliki peluang untuk modulasi frekuensi sinus, tetapi tidak akan ada kemungkinan untuk modulasi fase.

Secara umum, rute untuk bekerja dengan BMC kecil agak berbeda dari rute desain saat ini. Jika Anda memikirkannya, perbedaannya menjadi jelas: dengan volume katup sekecil itu, perlu untuk menggunakan setiap katup dengan sangat efisien, dan paradigma utama dari desain modern tidak sama sekali. Dia mengatakan bahwa produk tersebut pada setiap tahap harus kompatibel secara arsitektur dengan sistem modern pengujian otomatis, verifikasi, pengukuran. Dalam hal ini, pertanyaan tentang efisiensi katup tetap berada di luar kurung, sebagai overhead yang diperlukan. Memang, dalam tahun-tahun perkembangan dinamis dari teknologi produksi, berpikir tentang efisiensi adalah berlebihan. Jadi ketika (dan jika) kita masih mencapai batas fisik dan berhenti meningkatkan kepadatan transistor pada kristal, maka masalah efisiensi penggunaan area akan mendatangi kita dalam pertumbuhan penuh. Nah, dengan BMK kecil mereka berdiri dengan ketinggian penuh, dan oleh karena itu, kesimpulannya: dalam BMK tank kecil Anda dapat dan harus menggunakan desain kompleks menggunakan berbagai skema pembuatan blok yang rumit, berbagai kait, umpan balik, dan hal-hal lain, untuk penggunaan di rute modern. seorang insinyur senior akan sobek tangannya.

Masalah utama dengan menggunakan hal-hal seperti itu adalah bahwa untuk menggunakannya, insinyur harus jelas menyadari apa yang dia lakukan dan mengapa. Namun, jika ada pemahaman, maka perolehannya bisa fantastis. Jika tidak ada pemahaman ... yah, Anda dapat menembak di kaki dengan jutaan cara efektif berbeda.

Seperti apa rupa rute desain dalam kasus saya:

- Pembuatan bagan manual sebagai bagan item perpustakaan

- Estimasi volume rangkaian yang dihasilkan

- Memproses sirkuit hingga volume rangkaian melebihi 80% dari kapasitas BMK

- Ini juga termasuk pekerjaan pada penciptaan elemen perpustakaan baru, pengujian dan integrasi mereka ke dalam rute desain

- Menyusun tes untuk sirkuit

- Pelacakan sirkuit manual

Desainer yang berpengalaman di sini mungkin langsung keberatan bahwa beberapa langkah penting telah terlewatkan, tetapi saya benar-benar lupa menyebutkan apa pun.

Desain manual menunjukkan dengan sangat baik betapa pentingnya pustaka komponen berkualitas. Varian pertama dari rangkaian tidak cocok dengan kristal hanya dengan volume logika, tetapi dalam kasus saluran BMC - yang mana kabel melewati saluran yang diletakkan di antara "baris" transistor - sekitar 30% dari volume sirkuit ditempati oleh interkoneksi. Oleh karena itu, saya harus memperluas perpustakaan, berdasarkan topologi yang diperoleh dalam proyek khusus ini. Pendekatan ini memungkinkan untuk menyelamatkan sejumlah besar gerbang dan bahkan lebih atau kurang leluasa meletakkan semua rute.

Pengisian kristal akhir adalah 72%, sepertiga dari kristal pergi ke kabel. Kemudian file-file itu dipindahkan ke pabrik, dan saya kembali ke proyek saya saat ini.

Dengan metode desain "manual", poin-poin berikut harus diingat:

- Anda tidak dapat menggunakan elemen pustaka tanpa berpikir berdasarkan fungsinya. Penting untuk mempelajari elemen apa yang tersusun pada level transistor, apakah itu digital atau analog. Apa kemampuannya menahan beban dalam hal input dan output, apakah ia murni logika CMOS, atau TG, atau yang lainnya.

- Penting untuk memperhitungkan dan mengoordinasikan kekuatan elemen dan muatannya.

- Jika Anda memiliki pemicu sinkron, maka Anda perlu mencocokkannya dengan sinyal dengan kekuatan yang sama.

- Jika Anda menggunakan beberapa jenis sinyal tanpa amplifikasi menengah, dan itu dimuat pada banyak konsumen, maka sinyalnya bisa sangat gagal. Ini mungkin tidak signifikan dalam kondisi normal, tetapi sangat penting ketika menguji WWF (faktor eksternal).

Tidak ada sistem pemodelan yang dapat menggantikan otak Anda sendiri. Secara umum, Anda tidak dapat menjalankan simulasi jika Anda sendiri tidak mengerti cara kerja rangkaian.

6.2 Pengukuran

Tahap yang sangat penting dalam bekerja dengan kristal adalah pengukurannya. Tiga jenis pengukuran dapat dibedakan: teknologi, fungsional, listrik. Yang pertama memverifikasi bahwa pabrik belum menarik dan bahwa kristal diproduksi secara teknologi. Yang terakhir memverifikasi bahwa teori (mis., Pemodelan) menyatu dengan praktik (kristal nyata). , : , , . , , . , - . , . — , — . , … , , . .

, . , Fairchild 80- USB, . FORMULA "", . HP - Unix' . National Instruments , , , (). Agilent, . , ?) .

, -, , . , , , , Fairchild, , NI. , . - , , .

, , :

- , .

- . , .

- "" .

- , , , .

- .

- :

- /, , . /.

- , .

- , – . .

- , «» , .

- , .

, , .

. 4 (!) . , , . , ?) " ".

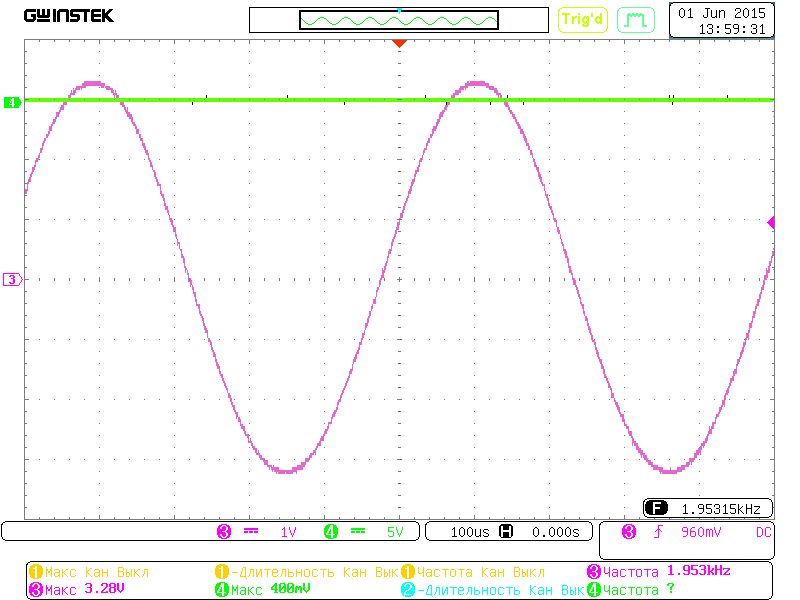

4. .

, . , , . 80 , , , , 8- .

, . :

5.

6.

, , .

, — . , . 8- . .

6.3

?

- ;

- NCO(numerically controlles oscillator);

- , , NCO ROM(cROM);

- ;

- :

- , ;

- ;

7. , HRT.

:

- — 83%.

- 14

- 11

- (sin & cos, 12 )

- 16

, , ? , . , - .

, . , . , — . .

7. ?

.

.

30 000 100 2. , " " . , , Setup&Hold, , Verilog' , , , — , , . , — , , , … . — , .

. .

-

MIT Massachusetts Institute of Technology

UZH Universität Zürich

ASIC Application specific integrated circuit

-- []

CORDIC Coordinate Rotation Digital Computer

-

NCO Numerically controlled oscillator

ROM Read-only memory

cROM Compressed ROM

- CORDIC IP Block Design, Vitaliy Kuhar, Stockholm, Sweden 2008

- CORDIC. , . . , . .

- Comparison of parallel and pipelined CORDIC algorithm using RCA and CSA, Guerrero, Meloni

- CORDIC for dummies.pdf

- Sine/Cosine using CORDIC Algorithm, Prof. Kris Gaj

- Lecture_cordic.pdf