Halo

Artikel ini mengulas arsitektur sistem memori virtual ARMv7.

Judul spoilerSeluk-beluk caching, DMA, LPAE dan sejenisnya tidak dipertimbangkan di sini. Untuk deskripsi yang lebih detail, bacalah literatur di akhir artikel.

Pendahuluan

Sistem memori virtual melakukan beberapa tugas. Pertama, ini memungkinkan Anda untuk menempatkan proses pengguna secara terpisah, terisolasi satu sama lain, ruang memori. Ini memungkinkan Anda untuk meningkatkan keandalan sistem, kesalahan satu proses tidak mempengaruhi operasi proses lainnya. Kedua, OS dapat menyediakan proses dengan lebih banyak memori daripada sistem. Halaman memori yang tidak digunakan didorong ke penyimpanan permanen, dan yang diperlukan dimuat dari sana, membentuk ilusi jumlah memori yang lebih besar daripada yang sebenarnya. Ketiga, ruang virtual terus menerus membuatnya lebih mudah untuk menulis perangkat lunak khusus. Semua proses dieksekusi dalam ruang yang sama, OS menyembunyikan darinya konfigurasi memori nyata dalam sistem.

Definisi

Definisi berikut digunakan dalam artikel:

Alamat Virtual - Alamat yang digunakan oleh inti prosesor. Penunjuk tumpukan, penghitung instruksi, register kembali menggunakan alamat virtual.

Alamat Fisik - Alamat keluaran pada bus prosesor.

Halaman adalah unit pengalamatan memori virtual.

Bagian - analog halaman, memiliki ukuran lebih besar.

Frame adalah unit pengalamatan memori fisik.

Tabel halaman - array catatan untuk menerjemahkan alamat.

ASID adalah pengidentifikasi ruang alamat.

TLB - buffer terjemahan alamat yang cepat.

MMU adalah unit manajemen memori.

TLB

TLB adalah buffer perangkat keras yang sangat cepat yang berisi hasil terjemahan alamat terbaru. Permintaan kernel untuk menerjemahkan alamat halaman dan ASID saat ini tiba di TLB. Jika ada entri yang valid di sana, maka izin untuk mengakses memori ini diperiksa, metode akses dan alamat bingkai yang sesuai dikembalikan ke MMU. Jika akses memori ditolak, pengecualian perangkat keras dilemparkan. Jika miss TLB terjadi (tidak ada catatan ditemukan), maka perilaku selanjutnya adalah case-sensitive oleh TTBCR. Pencarian dapat dilakukan di tabel halaman atau pengecualian dilemparkan.

Penting untuk dicatat bahwa ketika memanipulasi tabel halaman, Anda harus mengatur ulang TLB dengan benar, karena informasi yang tidak relevan dapat disimpan di sana.

Memperbarui entri di TLB transparan untuk programmer round-robin.

Dimungkinkan juga untuk mengunggah dan mengamankan beberapa entri di TLB untuk mencegah kepadatan mereka.

Gambar 1. TLB

Gambar 1. TLBTabel Halaman

ARMv7 adalah arsitektur 32-bit, jadi kami memiliki 4GB memori virtual yang dapat dialamatkan.

Tabel halaman dibagi menjadi 2 level - L1 dan L2.

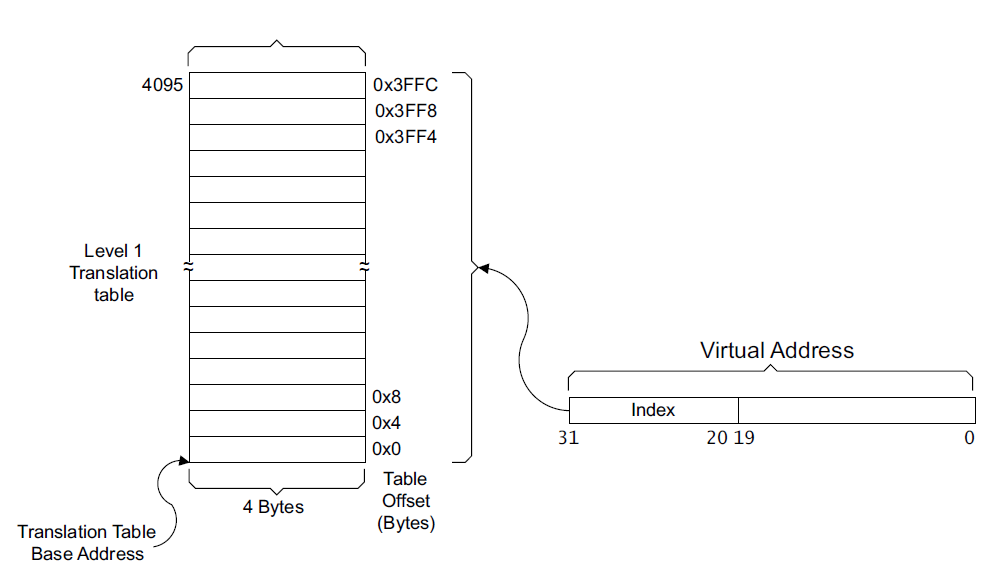

Tabel L1 menjelaskan semua ruang alamat 4GB. Ini terdiri dari 4096 catatan 32-bit, masing-masing menggambarkan 1 Mb. Entri dalam tabel dipilih oleh 12 bit tinggi dari alamat virtual.

Fig. 2 Cari entri pada tabel L1

Fig. 2 Cari entri pada tabel L1Tabel L1 terletak di memori fisik dan disejajarkan dengan batas 16KB. Ada 4 opsi untuk entri ini: untuk menggambarkan halaman, bagian, dan superseksi. Nah, catatan kosong, untuk memori yang belum dipetakan.

Fig. 3 Jenis entri di L1

Fig. 3 Jenis entri di L1Bits 0 dan 1 menunjukkan tipe record 00b-Fault, 01b adalah deskriptor halaman, 10b adalah deskriptor bagian (dan supersection).

Jika memori fisik paginasi, maka tabel L1 menyimpan alamat tabel L2 (fisik, sejajar dengan 1Kb). Bit 9 ditentukan oleh pabrikan (Implementasi ditentukan), bit [8: 5] - untuk mekanisme domain (Tidak berlaku dalam ARMv7), SBZ - nol.

Jika kita memutuskan untuk membagi memori menjadi beberapa bagian, maka di L1 perlu untuk menulis alamat fisik yang sesuai. Bagian ini secara langsung merujuk pada area memori fisik 1MB yang selaras. Tidak perlu untuk tabel L2. Supersection adalah kasus khusus dari partisi, entri dalam tabel L1 harus diulang 16 kali, keselarasan blok memori fisik dan virtual yang dialokasikan juga 16 MB.

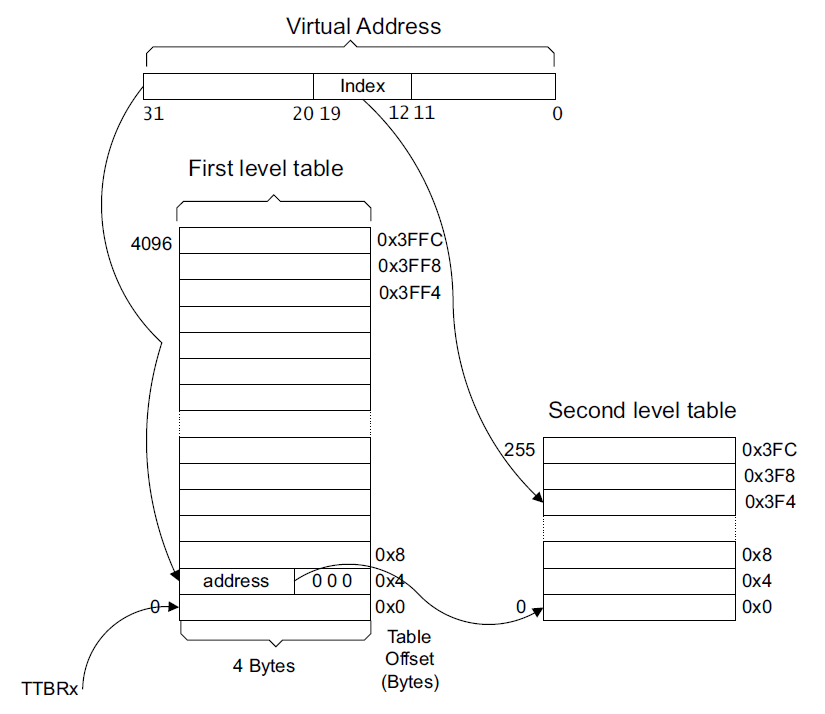

Tabel L2 terdiri dari 256 entri 32 bit. Itu harus disejajarkan dengan 1Kb.

Fig. 4 Cari entri dalam tabel L2

Fig. 4 Cari entri dalam tabel L2Indeks dalam tabel L2 dibentuk dari rata-rata 8 bit [19:12] dari alamat virtual. Setiap entri tabel berisi alamat bingkai.

Fig. 5 Jenis entri dalam L2

Fig. 5 Jenis entri dalam L2Halaman dapat terdiri dari dua ukuran: 64Kb (Halaman besar) dan 4Kb (Halaman kecil).

AP dan bit APX mengatur izin baca / tulis dalam mode privilege / unprivileged (kernel / pengguna). Bit TEX, C, B, S bertanggung jawab untuk jenis memori, caching, dan buffering baca-tulis. Bit nG - nonGlobal memungkinkan akses ke halaman untuk semua proses atau hanya untuk satu ASID tertentu.

Menggunakan halaman besar mengurangi jumlah entri dalam TLB. Alih-alih 16 entri (4Kb * 16 = 64Kb), hanya satu entri yang akan disimpan di sana. Namun, 16 entri identik harus dimasukkan dalam tabel L2.

Kemampuan untuk mengatasi berbagai ukuran blok memungkinkan, di satu sisi, untuk mengalokasikan memori dengan rincian yang diinginkan, di sisi lain, untuk mengurangi jumlah panggilan ke tabel halaman dalam memori yang relatif lambat.

Daftar

Untuk mengontrol sistem (termasuk MMU) dalam arsitektur ARM, coprocessor CP15 khusus dirancang. Untuk manajemen memori ada satu setengah lusin registernya. Kami tertarik pada beberapa di antaranya - Kontrol, TTBR0 / 1, TTBCR, ContextID.

Dalam register Kontrol, bit paling signifikan bertanggung jawab untuk mengaktifkan / menonaktifkan MMU, semuanya sederhana.

Pasangan register TTBR0 / 1 berisi alamat fisik dari tabel di tingkat pertama. Di alamat-alamat ini, MMU mulai mencari halaman yang diinginkan.

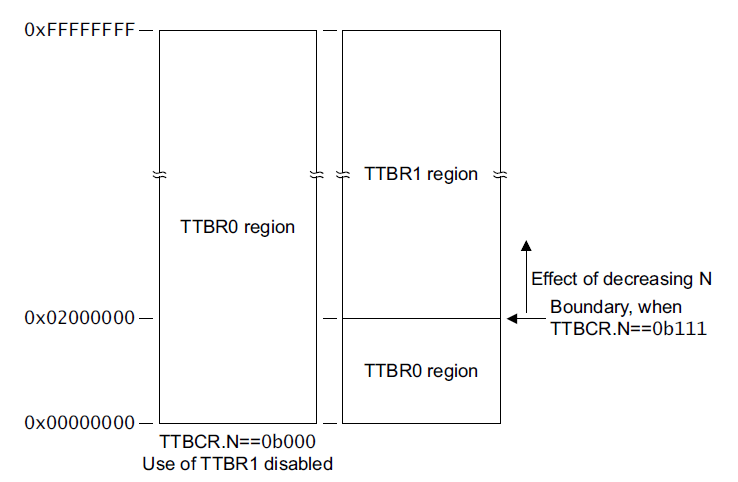

Register TTBCR memungkinkan Anda untuk membagi seluruh ruang alamat menjadi 2 bagian antara TTBR0 dan TTBR1. Masing-masing dari mereka akan menyiarkan bagian dari alamatnya. Bit [2: 0] digunakan untuk mengatur ukuran. Angka yang direkam (dari 0 hingga 7 desimal) menutupi bagian lama dari alamat virtual. Jika nilainya "0", semua alamat disiarkan melalui TTBR0. Jika "1", alamat 31bit disamarkan dan 2GB ruang virtual yang lebih rendah melewati TTBR0, yang atas melalui TTBR1. "2" - 31 dan 30 bit disamarkan dan pembagian menjadi 1GB dan 3GB masing-masing diperoleh. Dengan demikian, bagian bawah dari alamat dapat digunakan untuk aplikasi pengguna, overloading register TTBR0 untuk proses baru, dan bagian atas dapat dibiarkan untuk kebutuhan sistem.

Fig. 6 ruang alamat Split

Fig. 6 ruang alamat SplitBit [5: 4] bertanggung jawab atas perilaku miss TLB - mencari di tabel halaman atau pengecualian.

Register ContextID berisi bidang ASID untuk proses saat ini. Itu harus diubah bersama dengan isi register TTBR0 ketika mengubah konteks.

Terjemahan alamat

Algoritma untuk mengubah alamat virtual menjadi fisik adalah sebagai berikut:

- Cari alamat virtual yang diminta dan ASID di buffer TLB

- Jika TLB tidak memiliki alamat yang diperlukan, maka pencarian perangkat keras dilakukan pada tabel halaman

Jika kernel sebelumnya meminta halaman virtual, maka itu disimpan dalam TLB. Dalam hal ini, MMU mengeluarkannya dari cache dan tidak ada yang perlu dilakukan. Jika halaman diminta untuk pertama kalinya (atau dipaksa keluar dari sana - TLB tidak terlalu besar), maka pencarian di tabel L1-L2 dilakukan. Dengan demikian, pemetaan alamat virtual dan fisik adalah sebagai berikut:

- Dalam register TTBR0 \ TTBR1, alamat tabel L1 dicari.

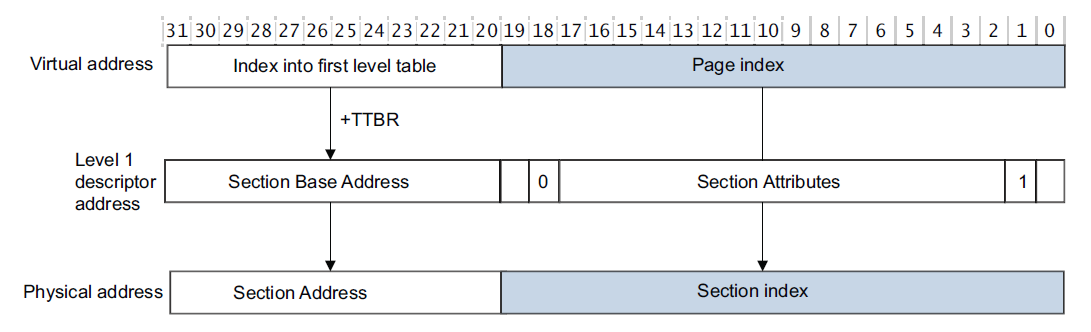

- 10 bit teratas dari alamat virtual membentuk indeks dalam tabel.

- a) Jika catatan sesuai dengan bagian (supersection), maka atribut dari bagian tersebut diperiksa dan, jika semuanya OK, alamat fisik yang dihasilkan terdiri dari alamat dasar bagian (supersection) dan 20 (24) bit lebih rendah dari alamat virtual.

Judul spoiler Fig. 7 Terjemahan alamat di supersection

Fig. 7 Terjemahan alamat di supersection

b) Jika catatan adalah tabel L2, maka pencarian berlanjut di dalamnya. Bagian tengah alamat virtual halaman membentuk indeks tabel.

Judul spoiler Fig. 8 Alamat Terjemahan pada Tabel L2

Fig. 8 Alamat Terjemahan pada Tabel L2

- Pembaruan TLB sedang berlangsung

Secara total, subsistem memori virtual terdiri dari bagian-bagian berikut:

- Beberapa Kontrol Kontrol CP15

- Tabel halaman berisi aturan terjemahan alamat

- TLB - cache dari siaran yang sukses

- MMU adalah unit terjemahan alamat.

Sastra

Manual Referensi Arsitektur ARM edisi ARMv7-A dan ARMv7-R

Panduan Programmer Seri ARM Cortex-A