Teknologi mikroelektronik modern - seperti "Sepuluh Orang India Kecil". Biaya pengembangan dan peralatan sangat besar sehingga setiap langkah maju, seseorang jatuh. Setelah berita tentang GlobalFoundries menolak untuk mengembangkan 7 nm, ada tiga dari mereka yang tersisa: TSMC, Intel dan Samsung. Dan apa sebenarnya "standar desain" dan di mana ukuran 7 nm yang sangat dihargai itu? Dan apakah dia ada di sana?

Gambar 1. Transistor Fairchild FI-100, 1964.Transistor MOS serial pertama memasuki pasar pada tahun 1964 dan, seperti yang dapat dilihat oleh pembaca canggih dari gambar, mereka

hampir tidak berbeda dari yang lebih atau kurang modern - kecuali untuk ukuran (lihat kawat untuk skala).

Mengapa mengurangi ukuran transistor? Jawaban yang paling jelas untuk pertanyaan ini disebut hukum Moore dan menyatakan bahwa setiap dua tahun jumlah transistor pada sebuah chip harus digandakan, yang berarti bahwa dimensi linear dari transistor harus berkurang dengan faktor dua. "Harus" - menurut pengamatan Gordon Moore (dan beberapa insinyur lainnya) pada tahun tujuh puluhan. Dari Hukum Moore, ada banyak faktor lain yang membentuk peta jalan mikroelektronika ITRS. Formulasi metode paling sederhana dan paling kasar untuk menerapkan hukum Moore (juga dikenal sebagai miniaturisasi hukum Dennard) adalah bahwa peningkatan jumlah transistor pada sebuah chip tidak boleh mengarah pada peningkatan kepadatan konsumsi daya, yaitu, dengan penurunan ukuran transistor, tegangan suplai dan arus operasi harus dikurangi secara proporsional.

Arus melalui transistor MOS sebanding dengan rasio lebar dan panjangnya, yang berarti bahwa kita dapat mempertahankan arus yang sama, secara proporsional mengurangi kedua parameter ini. Selain itu, mengurangi ukuran transistor, kami juga mengurangi kapasitansi gerbang (sebanding dengan produk dari panjang dan lebar saluran), membuat sirkuit lebih cepat. Secara umum, dalam sirkuit digital hampir tidak ada alasan untuk membuat transistor lebih besar dari ukuran minimum. Selanjutnya, nuansa mulai bahwa dalam logika p-channel transistor biasanya sedikit lebih lebar daripada n-channel untuk mengkompensasi perbedaan dalam mobilitas pembawa muatan, dan dalam memori, sebaliknya, transistor n-channel lebih lebar sehingga memori dapat ditulis secara normal melalui kunci non-komplementer, tetapi sebenarnya nuansa, dan secara global - semakin kecil ukuran transistor - semakin baik untuk sirkuit digital.

Itulah sebabnya panjang saluran selalu menjadi ukuran terkecil dalam topologi mikrokircuit, dan peruntukan penunjukan yang paling logis.

Perlu dicatat di sini bahwa alasan di atas tentang ukuran tidak berlaku untuk rangkaian analog. Sebagai contoh, sekarang di monitor kedua komputer saya ada sepasang transistor yang cocok menggunakan teknologi 150 nm, 32 buah masing-masing berukuran 8/1 mikron. Hal ini dilakukan untuk memastikan identitas kedua transistor ini, terlepas dari variasi teknologinya. Area ini memiliki kepentingan sekunder.Teknologi dan ahli topologi memiliki apa yang disebut lambda-sistem ukuran topologi khas. Sangat mudah untuk mempelajari desain (dan ditemukan di Universitas Berkeley, jika saya tidak salah) dan mentransfer desain dari pabrik ke pabrik. Sebenarnya, ini adalah generalisasi ukuran khas dan keterbatasan teknologi, tetapi agak kasar, sehingga bekerja persis di pabrik mana pun. Pada contohnya, akan lebih mudah untuk melihat ukuran tipikal elemen dalam chip. Prinsip-prinsip inti dari sistem lambda sangat sederhana:

- jika pergeseran elemen pada dua topeng photolithographic yang berbeda memiliki konsekuensi bencana (misalnya, korsleting), maka margin ukuran untuk mencegah inkonsistensi harus setidaknya dua lambda;

- jika pergeseran elemen memiliki konsekuensi yang tidak diinginkan, tetapi bukan merupakan bencana, margin ukuran harus setidaknya satu lambda;

- ukuran minimum yang diizinkan dari jendela topeng foto adalah dua lambda.

Dari paragraf ketiga berikut, khususnya, bahwa lambda dalam teknologi lama adalah setengah dari norma desain (lebih tepatnya, panjang saluran transistor dan norma desain adalah dua lambda).

Gambar 2. Contoh topologi yang dilakukan oleh sistem lambda.Sistem lambda bekerja dengan sempurna pada standar desain lama, memungkinkan Anda untuk dengan mudah mentransfer produksi dari pabrik ke pabrik, mengatur pemasok chip kedua dan melakukan banyak hal yang lebih berguna. Tetapi dengan meningkatnya persaingan dan jumlah transistor pada sebuah chip, pabrik-pabrik mulai berusaha untuk membuat topologi sedikit lebih kompak, jadi sekarang Anda tidak dapat memenuhi aturan desain yang berkaitan dengan sistem lambda "bersih", kecuali dalam situasi di mana pengembang secara mandiri mengencangkannya, dengan mempertimbangkan kemungkinan produksi chip di berbagai pabrik. Namun, selama bertahun-tahun, industri ini telah mengembangkan koneksi langsung "standar desain = panjang saluran transistor", yang berhasil ada hingga transistor mencapai puluhan nanometer.

Gambar 3. Bagian skematis dari transistor.Gambar ini menunjukkan bagian yang SANGAT disederhanakan dari transistor planar (flat) konvensional, menunjukkan perbedaan antara panjang saluran topologis (Ldrawn) dan panjang saluran efektif (Leff). Dari mana perbedaan itu berasal?

Berbicara tentang teknologi mikroelektronika, photolithography hampir selalu disebutkan, tetapi yang lebih jarang adalah operasi teknologi yang tidak kalah pentingnya: etsa, implantasi ion, difusi, dll. dll. Untuk percakapan kami dengan Anda, pengingat tentang bagaimana difusi dan implantasi ion bekerja tidak berlebihan.

Gambar 4. Perbandingan difusi dan implantasi ion.Dengan difusi, semuanya sederhana. Anda mengambil wafer silikon yang sebelumnya (dengan bantuan photolithography) gambar diterapkan, menutupi dengan silikon oksida tempat-tempat di mana pengotor tidak diperlukan, dan membuka tempat-tempat di mana ia diperlukan. Selanjutnya, Anda perlu menempatkan pengotor gas di ruang yang sama dengan kristal dan panas ke suhu di mana pengotor mulai menembus ke dalam silikon. Dengan menyesuaikan suhu dan durasi proses, dimungkinkan untuk mencapai jumlah dan kedalaman pengotor yang diinginkan.

Yang jelas minus dari difusi adalah bahwa pengotor menembus ke silikon ke segala arah dengan cara yang sama, ke bawah, sisi itu, sehingga mengurangi panjang saluran efektif. Dan sekarang kita berbicara tentang ratusan nanometer! Sementara standar desain diukur dalam puluhan mikron, semuanya baik-baik saja, tetapi tentu saja, keadaan ini tidak bisa bertahan lama, dan difusi digantikan oleh implantasi ion.

Selama implantasi ion, berkas ion pengotor berakselerasi dan diarahkan ke wafer silikon. Dalam hal ini, semua ion bergerak dalam satu arah, yang secara virtual menghilangkan penyebarannya ke sisi. Secara teori, tentu saja. Namun dalam praktiknya, ion-ion tersebut menyebar sedikit terpisah, walaupun pada jarak yang jauh lebih pendek daripada saat difusi.

Namun demikian, jika kita kembali ke pola transistor, kita akan melihat bahwa perbedaan antara panjang saluran topologis dan efektif dimulai justru karena creep kecil ini. Dia, pada prinsipnya, bisa diabaikan, tetapi dia bukan satu-satunya alasan perbedaan itu. Masih ada efek saluran pendek. Ada lima dari mereka, dan dalam berbagai cara mereka mengubah parameter transistor jika panjang saluran mendekati berbagai batasan fisik. Saya tidak akan menjelaskan semuanya, saya akan membahas yang paling relevan bagi kita - DIBL (Pengurangan Barrier yang Diinduksi Drain, penurunan yang diinduksi oleh drain dalam penghalang potensial).

Untuk masuk ke wastafel, sebuah elektron (atau lubang) harus mengatasi penghalang potensial dari persimpangan pn wastafel. Tegangan gerbang mengurangi penghalang ini, sehingga mengendalikan arus melalui transistor, dan kami ingin tegangan gerbang menjadi satu-satunya tegangan kontrol. Sayangnya, jika saluran transistor terlalu pendek, saluran drain pn mulai mempengaruhi transistor, yang, pertama, mengurangi tegangan pori (lihat gambar di bawah), dan kedua, tegangan melintasi transistor mulai tidak hanya mempengaruhi tegangan gerbang. , tetapi juga pada saluran pembuangan, karena ketebalan sambungan saluran pn meningkat secara proporsional dengan tegangan pada saluran pembuangan dan, karenanya, mempersingkat saluran.

Gambar 5. Efek Drain-Induced Barrier Lowering (DIBL).

Sumber - Wikipedia.Selain itu, penurunan panjang saluran mengarah pada fakta bahwa pembawa muatan mulai bebas beralih dari sumber ke saluran pembuangan, melewati saluran dan menghasilkan arus bocor (arus buruk pada gambar di bawah), yang juga merupakan konsumsi daya statis, yang tidak ada yang merupakan salah satu alasan penting bagi kesuksesan awal CMOS -Teknologi, agak penghambatan dibandingkan dengan pesaing bipolar saat itu. Faktanya, setiap transistor dalam teknologi modern memiliki resistor yang berdiri sejajar dengannya, nilainya adalah semakin kecil, semakin kecil panjang salurannya.

Gambar 6. Peningkatan konsumsi statis karena kebocoran teknologi saluran pendek.

Sumber - Sinopsis.Gambar 7. Proporsi konsumsi daya statis mikroprosesor pada standar desain yang berbeda.

Sumber - B. Dieny et. al., “Efek Pemindahan Spin dan Penggunaannya dalam Komponen Spintronik”, International Journal of Nanotechnology, 2010Sekarang, seperti yang Anda lihat pada gambar di atas, konsumsi statis secara signifikan melebihi dinamika dan merupakan penghambat penting untuk membuat sirkuit berdaya rendah, misalnya, untuk elektronik yang dapat dipakai dan internet. Sebenarnya, pada saat ini menjadi masalah penting, pemasaran muhlezh dengan standar desain dimulai, karena kemajuan dalam litografi mulai melampaui kemajuan dalam fisika.

Untuk mengatasi efek yang tidak diinginkan dari saluran pendek dengan standar desain 800-32 nanometer, banyak solusi teknologi diciptakan, dan saya tidak akan menjelaskan semuanya, jika tidak artikel tersebut akan tumbuh dengan ukuran yang sangat tidak senonoh, tetapi dengan setiap langkah baru saya harus memperkenalkan solusi baru - tambahan doping daerah yang berdekatan dengan persimpangan pn, doping dalam untuk mencegah kebocoran, transformasi silikon lokal dalam transistor menjadi silikon-germanium ... Tidak ada satu langkah pun dilakukan dalam mengurangi ukuran transistor. oh begitu.

Gambar 8. Panjang saluran efektif dalam teknologi 90 nm dan 32 nm. Transistor ditembak pada skala yang sama. Setengah lingkaran dalam gambar adalah bentuk tambahan saluran yang lemah (LDD, drainase yang diolah ringan), dibuat untuk mengurangi lebar persimpangan pn.

Sumber - Sinopsis.Ukuran metalisasi yang khas dan jarak antara elemen selama transisi dari 90 nm menjadi sekitar 28 nm menurun secara proporsional dengan penurunan dalam norma desain, yaitu, ukuran khas generasi berikutnya adalah 0,7 dari yang sebelumnya (sehingga, menurut hukum Moore, untuk mendapatkan penurunan dua kali lipat di area). Pada saat yang sama, panjang saluran menurun paling baik 0,9 dari generasi sebelumnya, dan panjang saluran efektif praktis tidak berubah sama sekali. Terlihat jelas dari gambar di atas bahwa dimensi linear dari transistor tidak berubah tiga kali sama sekali dari 90 nm menjadi 32 nm, dan semua permainan para teknologinya adalah mengurangi rana yang tumpang tindih dan area doping, serta di sekitar kontrol kebocoran statis, yang tidak diizinkan untuk dilakukan. salurannya lebih pendek.

Hasilnya, dua hal menjadi jelas:

- pergi di bawah 25-20 nm tanpa terobosan teknologi tidak berfungsi;

- semakin sulit bagi pemasar untuk melukiskan gambaran kemajuan teknologi dengan hukum Moore.

Hukum Moore umumnya merupakan topik kontroversial, karena itu bukan hukum alam, tetapi pengamatan empiris terhadap beberapa fakta dari sejarah satu perusahaan tertentu, diekstrapolasi untuk kemajuan masa depan seluruh industri. Sebenarnya, popularitas hukum Moore terkait erat dengan pemasar Intel, yang membuatnya menjadi panji mereka dan, pada kenyataannya, mendorong industri ke depan selama bertahun-tahun, memaksanya untuk mematuhi hukum Moore di mana, mungkin, mungkin perlu menunggu sebentar.Apa cara pemasar menemukan situasi? Sangat elegan.

Panjang saluran transistor bagus, tetapi bagaimana Anda bisa memperkirakan keuntungan di daerah itu, yang memberikan transisi ke standar desain baru? Beberapa waktu yang lalu, industri ini menggunakan area sel memori enam-transistor, blok pembangun mikroprosesor yang paling populer. Sel-sel inilah yang biasanya terdiri dari memori cache dan file register yang dapat menempati setengah kristal, dan itulah sebabnya skema dan topologi sel enam-transistor selalu dijilat dengan hati-hati hingga batasnya (seringkali orang-orang khusus yang melakukan hal itu), jadi ini adalah ukuran yang sangat bagus kepadatan pengepakan.

Gambar 9. Skema sel memori statis enam transistor.Gambar 10. Pilihan topologi yang berbeda untuk sel memori statis enam transistor. Sumber - G. Apostolidis et. al., “Desain dan Simulasi Arsitektur Sel 6T SRAM dalam Teknologi 32nm,” Journal of Engineering Science and Technology Review, 2016Jadi untuk waktu yang lama dalam deskripsi teknologi, jumlah standar desain disertai oleh gambar kedua - area sel memori, yang, secara teori, harus diturunkan dari panjang saluran. Dan kemudian ada substitusi konsep yang menarik. Pada saat penskalaan langsung berhenti bekerja, dan panjang saluran berhenti berkurang setiap dua tahun menurut hukum Moore, pemasar menyadari bahwa adalah mungkin untuk tidak mendapatkan area sel memori dari norma-norma desain, tetapi untuk menurunkan jumlah norma desain dari area sel memori!

Yaitu, “kita dulu memiliki panjang saluran 65 nm dan area sel memori X, dan sekarang panjang salurannya 54 nm, tapi kami memeras metalisasi, dan sekarang area sel telah menjadi X / 5, yang secara kasar berhubungan dengan transisi dari 65 menjadi 28 nm. Jadi, mari beri tahu semua orang bahwa kami memiliki standar desain 28 nm, dan kami tidak akan memberi tahu siapa pun tentang panjang saluran 54 nm? " Dalam keadilan, "metalisasi menyengat" juga merupakan pencapaian yang penting, dan untuk beberapa waktu setelah dimulainya masalah dengan miniaturisasi dari transistor itu sendiri, lebar metalisasi minimum, ukuran kontak ke transistor, atau angka lain pada topologi sesuai dengan standar desain yang dinyatakan. Tetapi kemudian tarian dimulai dengan transistor FinFET, di mana dimensi utama tidak ada hubungannya dengan resolusi litografi, tingkat miniaturisasi transistor dan segala sesuatu yang lain akhirnya menyimpang, dan area sel memori tetap menjadi satu-satunya angka normal, berdasarkan mana kita sekarang diberitahu tentang "10", " 7 "dan" 5 "nanometer.

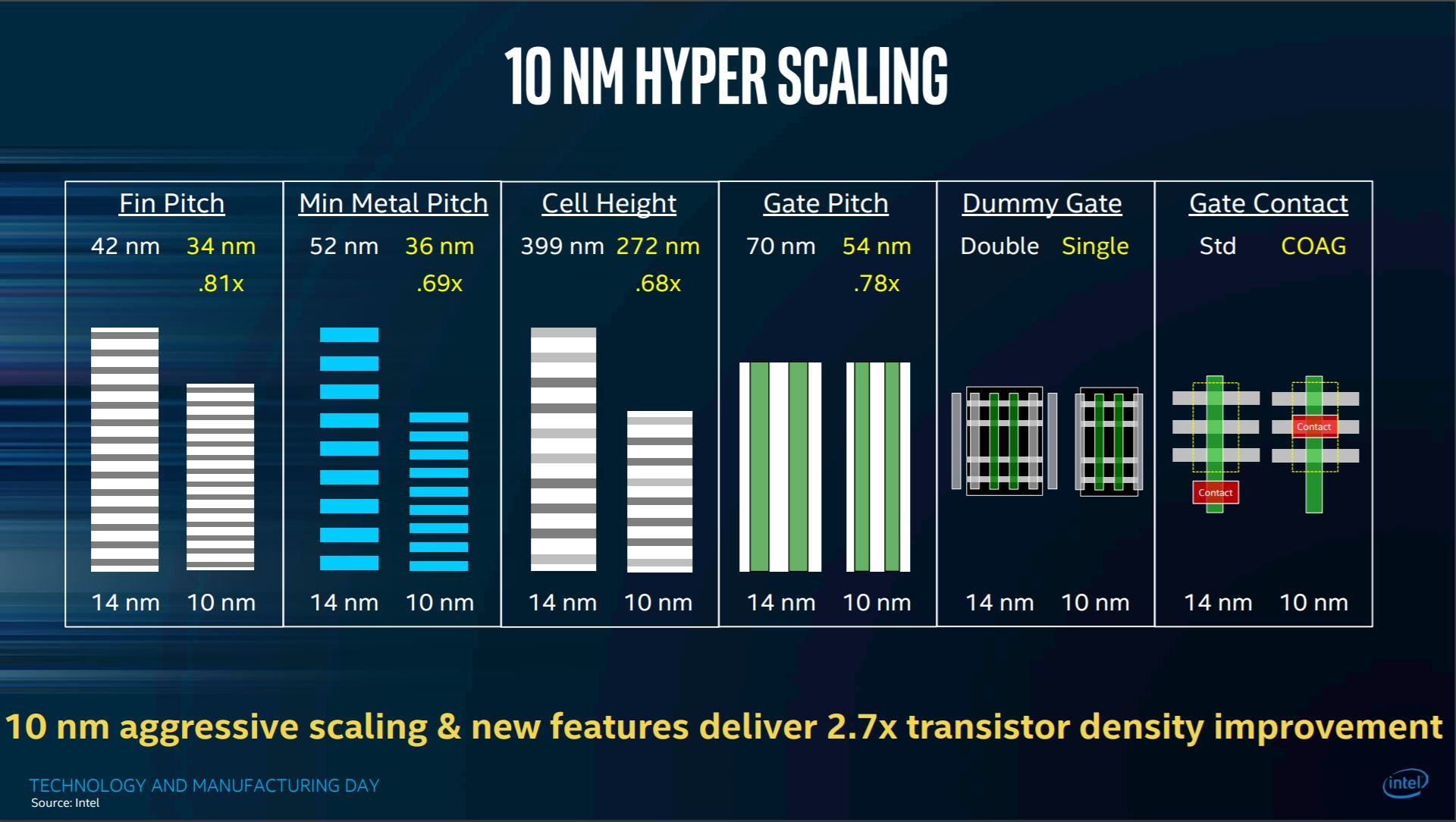

Sumber - Intel.Ini adalah contoh yang bagus dari "skala baru" ini. Kami diperlihatkan bagaimana ukuran karakteristik dalam sel memori telah berubah. Banyak parameter, tetapi tidak sepatah kata pun tentang panjang dan lebar saluran transistor!

Bagaimana mereka memecahkan masalah ketidakmungkinan mengurangi panjang saluran dan mengendalikan kebocoran teknologi?

Mereka menemukan dua cara. Yang pertama ada di dahi: jika penyebab kebocorannya adalah kedalaman implantasi yang besar, mari kita kurangi, lebih baik secara radikal. Teknologi Silicon on anulator (SIC) telah dikenal untuk waktu yang sangat lama (dan telah aktif digunakan selama bertahun-tahun, misalnya, dalam prosesor AMD 130-32 nm, prosesor set-top box Sony Playstation 3 90 nm, serta frekuensi radio, daya atau elektronik ruang angkasa), tetapi dengan penurunan standar desain, dia mendapat angin kedua.

Gambar 12. Perbandingan transistor yang dibuat dengan menggunakan teknologi volumetrik konvensional dan FDSOI (SOI sepenuhnya terkuras).

Sumber - ST Mikroelektronika .Seperti yang Anda lihat, idenya lebih dari anggun - oksida terletak di bawah lapisan aktif yang sangat tipis, menghilangkan arus bocor yang berbahaya pada pokok anggur! Pada saat yang sama, karena penurunan kapasitas persimpangan pn (empat dari lima sisi cube drain dihilangkan), kecepatan meningkat dan konsumsi daya berkurang. Itulah mengapa sekarang teknologi FDSOI 28-22-20 nm secara aktif diiklankan sebagai platform untuk hal-hal microchip Internet - konsumsi benar-benar berkurang beberapa kali, jika tidak dengan urutan besarnya. Namun pendekatan ini memungkinkan di masa depan untuk skala transistor datar konvensional ke tingkat 14-16 nm, yang teknologi volumetrik tidak lagi memungkinkan.

Namun demikian, FDSOI tidak jatuh di bawah 14 nm, dan teknologinya juga memiliki masalah lain (misalnya, mahalnya biaya substrat SOI), sehubungan dengan industri yang mencari solusi lain - transistor FinFET. Ide transistor FinFET juga cukup elegan. Apakah kita ingin sebagian besar ruang antara saluran dan sumber dikontrol oleh penutup? Jadi mari kita mengelilingi ruang ini dengan rana di semua sisi! Ya, tidak semua, tiga sudah cukup.

Gambar 13. Struktur FinFET.

Sumber - A. Tahrim et.al., "Desain dan Analisis Kinerja Sel Penambah Lengkap FinFET 1-Bit untuk Daerah Subthreshold pada Teknologi Proses 16 nm", Journal of Nanomaterials, 2015Gambar 14. Perbandingan konsumsi daya dari opsi adder berbeda yang dibuat pada transistor planar dan pada FinFET.

Sumber - A. Tahrim et.al., "Desain dan Analisis Kinerja Sel Penambah Lengkap FinFET 1-Bit untuk Daerah Subthreshold pada Teknologi Proses 16 nm", Journal of Nanomaterials, 2015Dalam FinFET, saluran tidak rata dan terletak tepat di bawah permukaan media, tetapi membentuk sirip vertikal (Sirip adalah sirip), menonjol di atas permukaan dan dikelilingi oleh rana di tiga sisi. Dengan demikian, seluruh ruang antara saluran dan sumber dikendalikan oleh rana, dan kebocoran statis sangat berkurang. FinFET pertama yang diproduksi secara massal adalah Intel dengan standar desain 22 nm, sisanya ditarik oleh pabrikan top lainnya, termasuk apologis KNI seperti Global Foundries (bekas AMD).

Vertikalitas saluran di FinFET, antara lain, memungkinkan Anda untuk menghemat area sel, karena FinFET dengan saluran lebar dalam proyeksi yang cukup sempit, dan ini, pada gilirannya, sekali lagi membantu pemasar dengan cerita mereka tentang luas sel memori dan penurunan dua kali lipat pada setiap sel baru. langkah "standar desain", tidak lagi terikat pada dimensi fisik transistor.Gambar 15. Topologi berbagai opsi untuk sel memori (5T-9T) dalam teknologi dengan FinFET. Sumber - M. Ansari et. al., “Sel SRAM 7T hampir ambang batas dengan margin tulis dan baca tinggi dan waktu tulis rendah untuk teknologi FinFET sub-20 nm”, Jurnal VLSI tentang Integrasi, Volume 50, Juni 2015.Berikut adalah contoh opsi berbeda untuk sel memori dalam teknologi tersebut. dengan FinFET. Lihat bagaimana lebar geometrik saluran jauh lebih kecil dari panjangnya? Anda juga dapat melihat bahwa, terlepas dari semua gangguan, sistem lambda di antara para ahli topologi masih digunakan untuk perkiraan kuantitatif. Dan bagaimana dengan angka absolut?Gambar 16. Beberapa ukuran transistor dalam teknologi 14-16 nm.

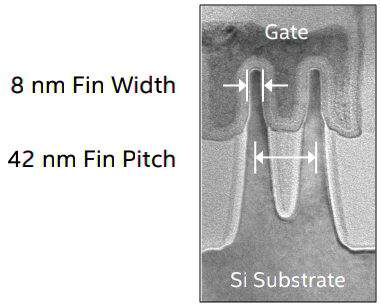

Sumber - proses konferensi ConFab 2016.Seperti dapat dilihat dari gambar, panjang saluran topologis dalam teknologi FinFET 16 nm masih lebih besar dari 20-25 nm, yang disebutkan di atas. Dan ini logis, karena fisika tidak bisa dibodohi. Tetapi kesimpulan lain yang lebih menarik dapat diambil dari gambar yang sama: jika Anda perhatikan lebih dekat, menjadi jelas bahwa ukuran minimum yang tersedia dalam transistor bukanlah panjang saluran, tetapi lebar sirip. Dan di sini penemuan lucu menunggu kita: lebar sirip dalam teknologi proses Intel 16 nm adalah (drum roll!) DELAPAN nanometer. Gambar 17. Dimensi sirip dalam teknologi proses Intel 14 nm.

Gambar 17. Dimensi sirip dalam teknologi proses Intel 14 nm.

Sumber - wikichip.orgSeperti yang Anda lihat, di sini pemasar, yang terikat pada ukuran sel memori, menipu diri mereka sendiri, dan sekarang dipaksa untuk menyuarakan angka itu lebih dari yang mereka bisa. Bahkan, tentu saja, dalam kondisi perubahan mendasar dalam struktur transistor dan harapan pengguna untuk mendengar semacam metrik, penggunaan metrik yang mencerminkan kerapatan pengepakan mungkin merupakan satu-satunya keputusan yang tepat, dan pemasar pada akhirnya benar, meskipun hal ini kadang-kadang menyebabkan situasi lucu ketika standar desain yang sama di perusahaan yang berbeda dipanggil secara berbeda. Misalnya, membaca berita bahwa TSMC telah meluncurkan 7 nm, dan Intel lagi-lagi menunda dimulainya produksi 10 nm, perlu diingat bahwa 7 nm TSMC dan 10 nm Intel sebenarnya standar desain yang sama dalam hal dan kepadatan pengepakan, dan ukuran masing-masing transistor.Apa selanjutnya Padahal, tidak ada yang tahu. Hukum Moore telah kehabisan tenaga beberapa waktu yang lalu, dan jika sepuluh tahun yang lalu jawaban untuk pertanyaan "apa selanjutnya?" dapat ditemukan dalam laporan pusat penelitian, sekarang semakin terdengar bahwa perkembangan yang menjanjikan harus ditinggalkan, karena ternyata terlalu sulit untuk diimplementasikan. Ini telah terjadi dengan wafer dengan diameter 450 milimeter, ini sebagian merupakan kasus dengan litografi EUV (yang digunakan para ilmuwan untuk berjalan sekitar dua puluh tahun), dan ini mungkin akan terjadi dengan transistor pada graphene dan carbon nanotube. Diperlukan terobosan teknologi lain, tetapi sayangnya, jalan ke sana belum terlihat. Begitu banyak sehingga, bahwa direktur baru TSMC Mark Liu disebutArah paling menjanjikan dalam pengembangan teknologi mikroelektronik bukanlah pengurangan ukuran transistor, tetapi integrasi 3D. Integrasi 3D "benar", daripada menggabungkan beberapa chip dalam satu paket, memang akan menjadi tonggak besar dalam pengembangan mikroelektronika, tetapi hukum Moore, sebagai hukum pengurangan ukuran transistor, tampaknya telah mati sepenuhnya.