Quad Data Rate (QDR-IV) adalah standar memori berkinerja tinggi untuk aplikasi jaringan dan sangat ideal untuk perangkat jaringan, peralatan komunikasi, dan sistem komputasi generasi mendatang.

QDR-IV SRAM memiliki unit deteksi kesalahan dan koreksi (ECC) bawaan untuk memastikan integritas data. Unit ini mampu memproses semua kesalahan memori bit tunggal, termasuk yang disebabkan oleh sinar kosmik dan partikel alfa. Akibatnya, modul memori akan memiliki tingkat kesalahan program (SER) tidak lebih dari 0,01 kegagalan / MB. QDR-IV dilengkapi dengan fungsi parity address yang dapat diprogram yang memastikan integritas data pada bus alamat.

Fitur khas memori QDR SRAM:

- Modul koreksi kesalahan terintegrasi memastikan integritas data dan menghilangkan kesalahan perangkat lunak

- Modul tersedia dalam dua versi: QDR-IV HP (data rate 1334 Mtrans / s) dan QDR-IV XP (data rate 2132 Mtrans / s)

- Dua port data memori DDR1 dua arah yang independen

- Fungsi pembalikan bus untuk mengurangi kebisingan saat menghubungkan jalur input dan output

- Skema Negosiasi Terintegrasi (ODT) mengurangi kompleksitas papan

- Pelatihan miring untuk meningkatkan waktu penangkapan sinyal

- Kekuatan Sinyal I / O: 1.2V hingga 1.25V (Logika Transceiver Berkecepatan Tinggi (HSTL) / Terminated Logic (SSTL)), 1.1V hingga 1.2V (POD2)

- Paket FCBGA3 361 pin

- Lebar Bus: x18, x36 bit

Pendahuluan

DDRx Wizard adalah alat yang mudah digunakan dalam HyperLynx yang memungkinkan Anda untuk mengontrol gelombang temporal dan menganalisa integritas sinyal protokol DDR JEDEC standar. DDRx Wizard dapat diluncurkan baik pada tahap analisis pra-topologi sesuai dengan skenario "bagaimana jika", dan pada papan yang sepenuhnya ditelusuri. Selain itu, alat ini memungkinkan Anda untuk mengimpor sebagian besar format model yang dibuat oleh pemasok chip utama.

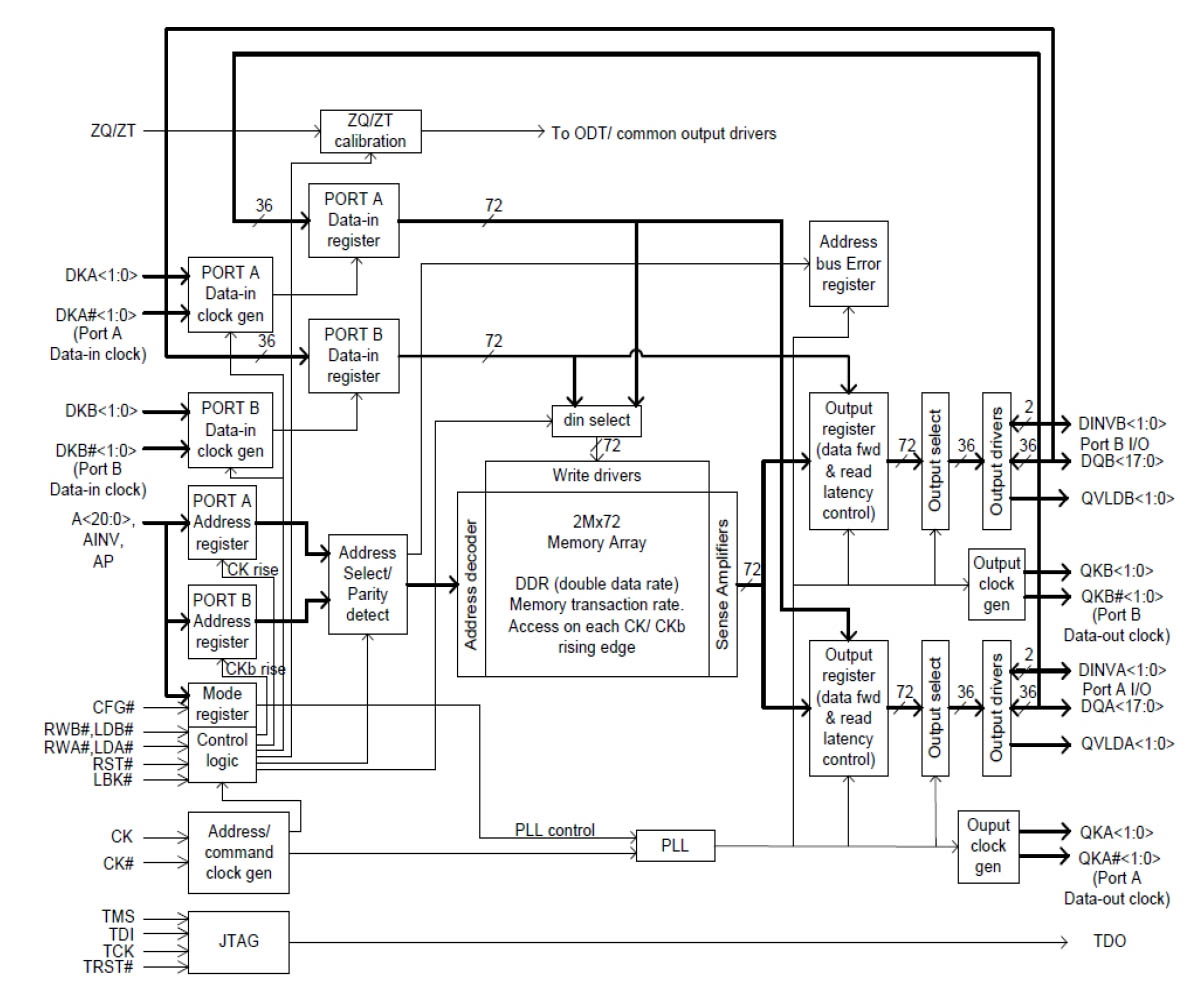

DDRx Wizard memungkinkan Anda untuk memeriksa semua bit bus memori untuk kesesuaian dengan integritas sinyal, serta untuk memenuhi persyaratan sinkronisasi antara sinyal. Artikel ini akan merinci penggunaan asisten interaktif untuk menganalisis proyek yang menerapkan protokol QDR4 (Gbr. 1).

Fig. 1. Arsitektur internal QDR pada contoh modul CY7C4142KV13 (dapat diklik)

Fig. 1. Arsitektur internal QDR pada contoh modul CY7C4142KV13 (dapat diklik)Pertama lihat QDR-IV di HyperLynx DDRx WIZARD

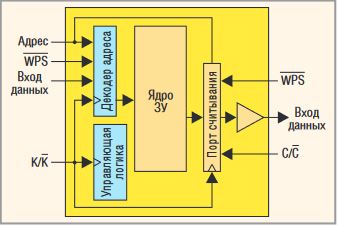

Protokol QDR-IV mendefinisikan dua pasangan searah dari sinyal data strobo: satu untuk membaca data, yang lain untuk menulis, yang mendukung independen dari satu sama lain operasi dan operasi membaca dan menulis secara simultan, dan port dapat beroperasi pada frekuensi yang berbeda (Gbr. 2). Dengan demikian, risiko kerusakan sepenuhnya dihilangkan.

Fig. 2. Ketersediaan port baca dan tulis terpisah dalam arsitektur QDR SRAM

Fig. 2. Ketersediaan port baca dan tulis terpisah dalam arsitektur QDR SRAMUntuk protokol ini, DDRx Wizard akan menggunakan gerbang terpisah untuk membaca dan menulis data. QDR IV biasanya diimplementasikan menggunakan bus bit x36 atau x18 (lihat Gambar 3a dan 3b).

Wizard DDRx mengaktifkan simulasi QDR-IV dalam tiga langkah:

- Verifikasi Baca Data

- Pemeriksaan Catatan Data

- Alamat / Kontrol Bus Periksa

Karena pemeriksaan bus alamat / kontrol dapat dilakukan secara independen dari pemeriksaan baca / tulis data, ini dapat menghemat waktu Anda dengan menggabungkan langkah ini dengan salah satu langkah pengujian data. Berikut ini menjelaskan ketiga skenario untuk tes ini.

Fitur teknologi

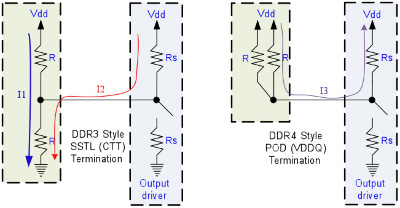

QDR-IV mendukung teknologi pseudo open drain (POD) dan logika penghentian Seri Terminated Logic (SSTL) (Gambar 4).

Fig. 4. Perbedaan antara POD dan SSTL

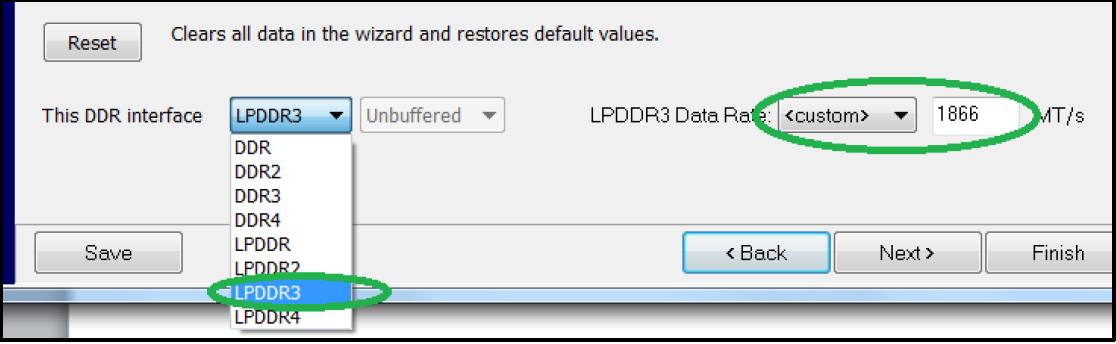

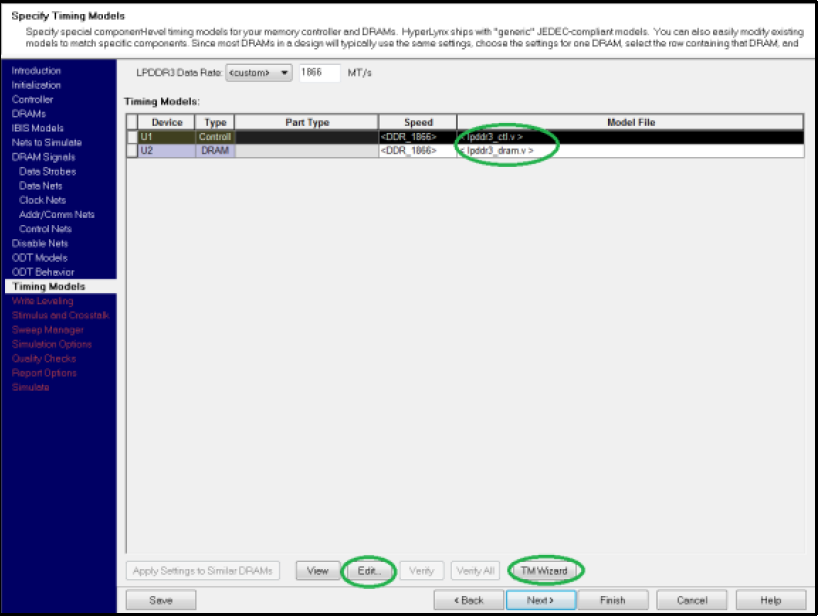

Fig. 4. Perbedaan antara POD dan SSTLTerlepas dari standar logika yang digunakan, pilih

LPDDR3 sebagai teknologinya (Gbr. 5), karena tidak ada dukungan untuk

pelatihan Vref , seperti halnya dengan modul POD DDR4. Sebaliknya, nilai-nilai tetap Vref dan Vinh / Vinl digunakan, mirip dengan DDR3 dan LPDDR3. Karena QDR-IV menggunakan laju data ganda untuk sinyal alamat seperti LPDDR3, Anda disarankan untuk memilih opsi ini. Selanjutnya, masukkan laju transfer data pengguna, misalnya, 1866 MT / s atau 2133 MT / s, di mana MT / s adalah jumlah megatransfers per detik (megatransfers per detik).

Fig. 5. Pilihan logika standar

Fig. 5. Pilihan logika standarSinyal Data: Baca Operasi

Untuk operasi pembacaan sinyal data, DRAM akan mengontrol sinyal DQ bersamaan dengan sinyal QK strobo diferensial. Dengan demikian, pengaturan berfokus pada operasi pembacaan data, dan menetapkan sirkuit (sinyal) yang diperlukan ke gerbang QK yang sesuai.

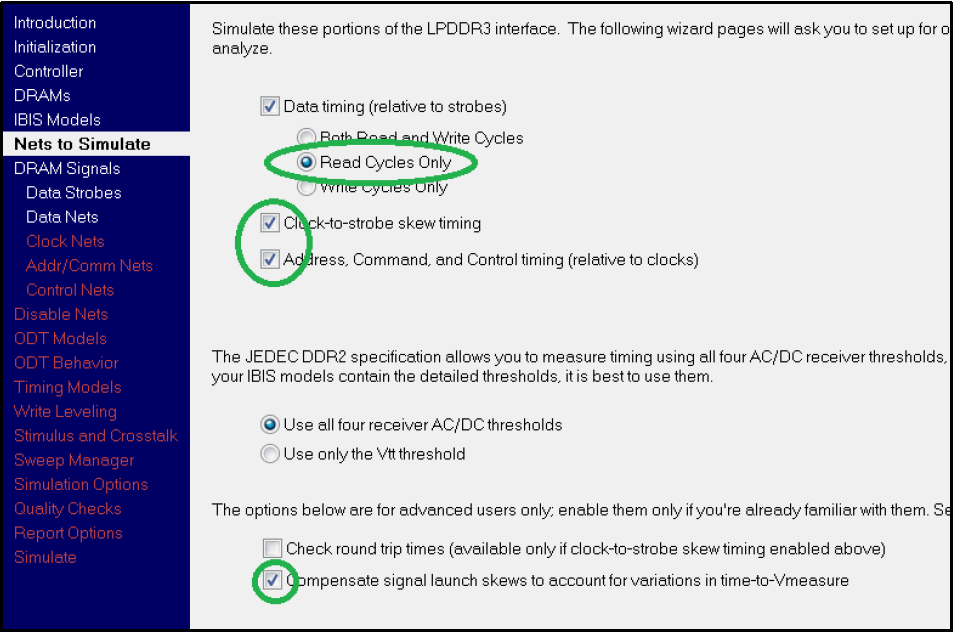

Di bagian

Jaring untuk Mensimulasikan (Gambar 6), centang kotak "

Hanya Baca Siklus ".

Kotak centang Jam-ke-strobo dan Alamat cek adalah opsional.

Juga, periksa pemasangan

peluncuran sinyal Kompensasi condong ke akun untuk variasi dalam kotak centang Time-to-Vmeasure .

Fig. 6. Membaca data

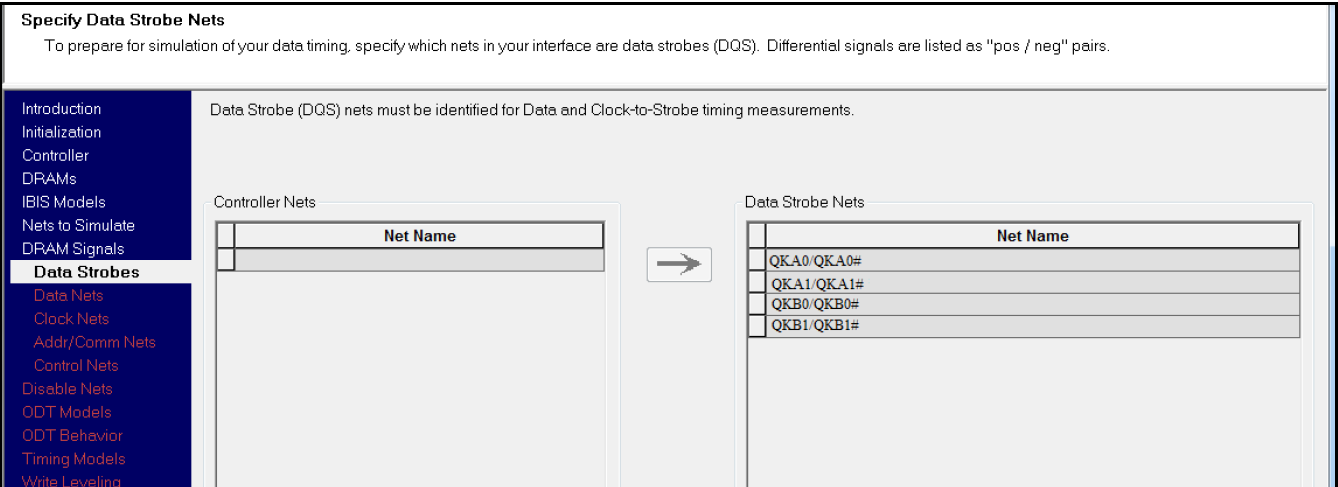

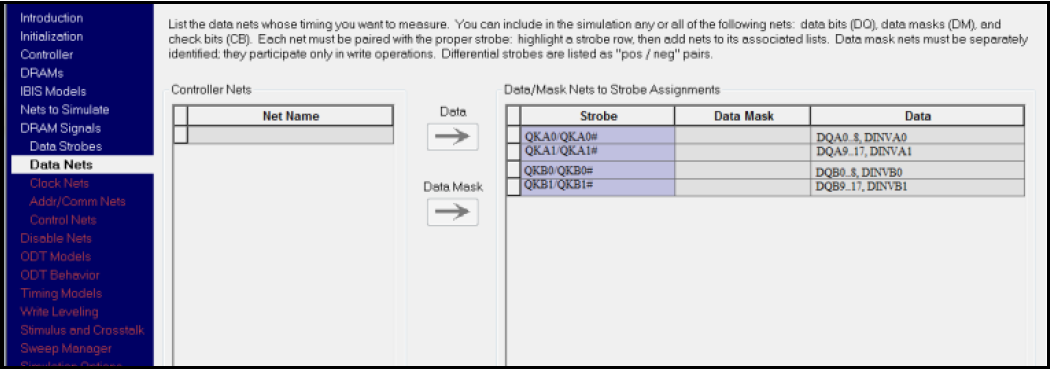

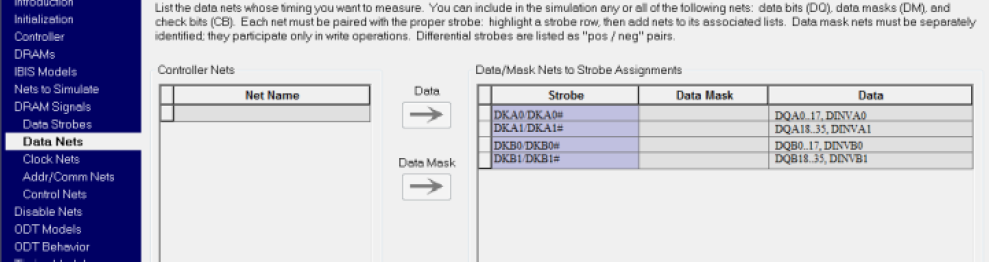

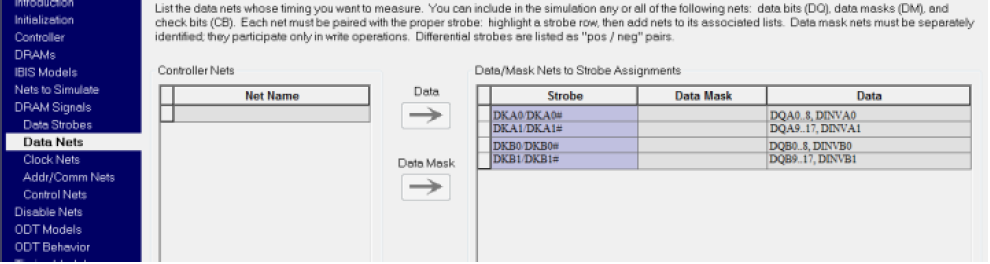

Fig. 6. Membaca dataPastikan semua strobe data yang diperlukan dipilih (Gambar 7).

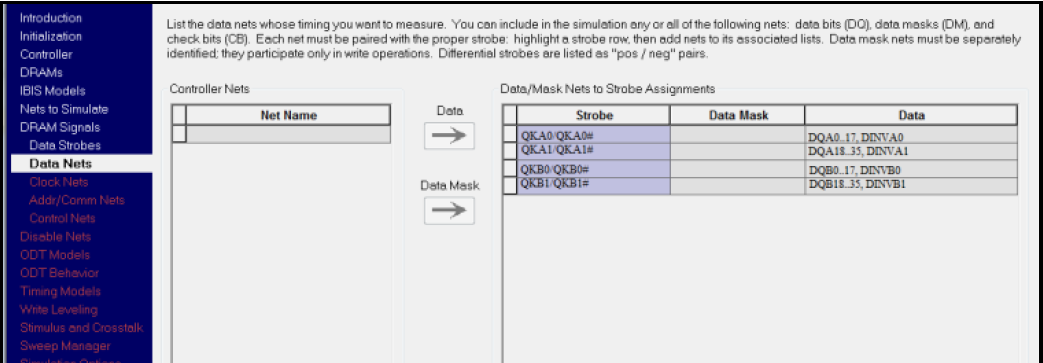

Di bagian

Jaring Data , pastikan setiap sinyal cocok dengan masing-masing gerbang dengan benar. Harap perhatikan bahwa sinyal berbeda untuk bus bit x18 dan x36, jadi pastikan pinout tepat untuk kasus khusus Anda (Gbr. 8a dan 8b).

Fig. 7. Membaca data strobo

Fig. 7. Membaca data strobo Fig. 8a. Grup Sinyal untuk Bus 36-bit

Fig. 8a. Grup Sinyal untuk Bus 36-bit Fig. 8b. Grup sinyal untuk bus 18-bit

Fig. 8b. Grup sinyal untuk bus 18-bitTes bus paralel biasanya dilakukan dengan mengatur / menahan waktu antara strobo dan sinyal. Semua persyaratan ini, selain nilai sementara lainnya, diwajibkan oleh DDRx Wizard untuk memverifikasi hasil. Nilai-nilai ini mungkin berbeda dari microchip ke microchip, oleh karena itu, disarankan agar Anda memasukkan nilai yang berlaku untuk perangkat memori tertentu. Selain itu, informasi waktu default untuk LPDDR3 tidak kompatibel dengan QDR-IV. Jadi, semua informasi waktu untuk QDR-IV harus dimasukkan dan cocok dengan dokumentasi untuk chip Anda.

Ini dapat dilakukan baik dengan menggunakan

Timing Wizard (Gbr. 9), yang meminta pengguna untuk mengisi beberapa formulir untuk pembuatan nilai temporer selanjutnya, atau Anda dapat mengedit file sinkronisasi .V yang sesuai dengan controller dan DRAM Anda.

Fig. 9. Mengatur nilai waktuHarap dicatat

Fig. 9. Mengatur nilai waktuHarap dicatat : karena simulasi dilakukan dalam mode

LPDDR3 , hasilnya harus ditafsirkan sesuai.

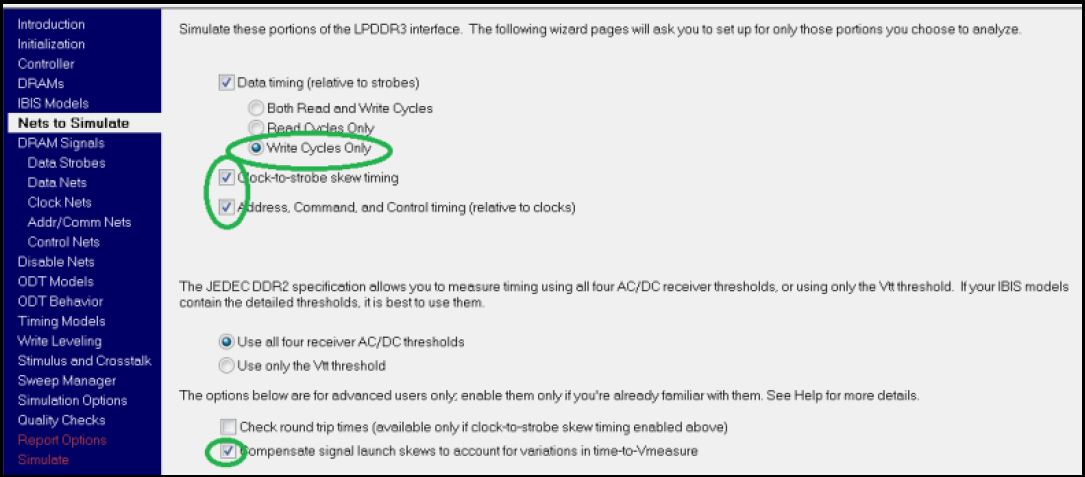

Sinyal data: operasi tulis

Operasi penulisan data dan analisisnya mirip dengan analisis untuk operasi baca yang dijelaskan di atas. Tetapi ada dua perbedaan utama yang sekarang akan kita pertimbangkan. Dengan pengecualian dari dua nuansa ini, langkah-langkah yang diambil untuk operasi pembacaan data dapat diulang untuk mensimulasikan penulisan data.

Di bagian

Jaring untuk Mensimulasikan (Gambar 10), pastikan

Write Cycles Only dipilih.

Dimungkinkan juga untuk mensimulasikan

Operasi penulisan Sinyal Alamat . Dan jangan lupa untuk memastikan bahwa

Peluncuran Skew Kompensasi ke akun untuk variasi centang centang waktu-ke-Vmeureure dicentang .

Fig. 10. Perekaman Data

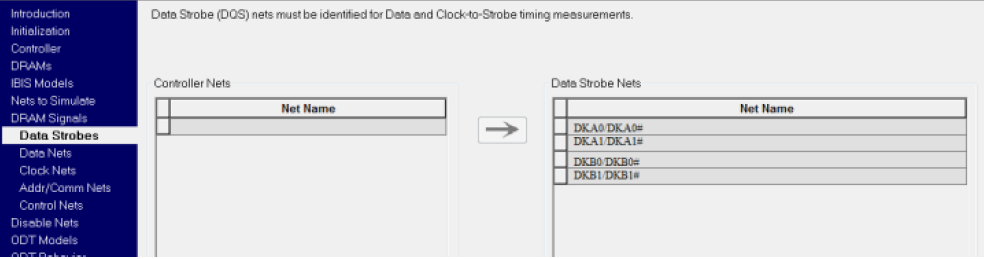

Fig. 10. Perekaman DataPastikan bahwa gerbang yang benar dipilih di bagian

Data Strobe (Gambar 11). Perbedaan utama antara transaksi baca dan transaksi tulis adalah strobo yang digunakan untuk menyinkronkan data, strobo ini berbeda dari strobo yang digunakan untuk operasi baca data (Gbr. 12 dan 13).

Fig. 11. Gerbang data catatan

Fig. 11. Gerbang data catatan Fig. 12. Grup sinyal sinyal strobo (bus 36-bit)

Fig. 12. Grup sinyal sinyal strobo (bus 36-bit) Fig. 13. Grup sinyal sinyal strobo (bus 18-bit)

Fig. 13. Grup sinyal sinyal strobo (bus 18-bit)Alamat, perintah, dan kontrol bus

QDR-IV menggunakan kunci diferensial CK / CK # untuk memilih sinyal kontrol, alamat, dan sinyal perintah. Tepi depan sinyal CK digunakan untuk memasukkan informasi tentang port A, dan trailing edge digunakan untuk memilih informasi tentang port B.

Mempertimbangkan integritas sinyal, bentuk gelombang untuk jalur alamat harus memenuhi persyaratan pemasangan dan penundaan baik ujung depan maupun ujung sinyal jam. Ini sangat mirip dengan perilaku LPDDR3.

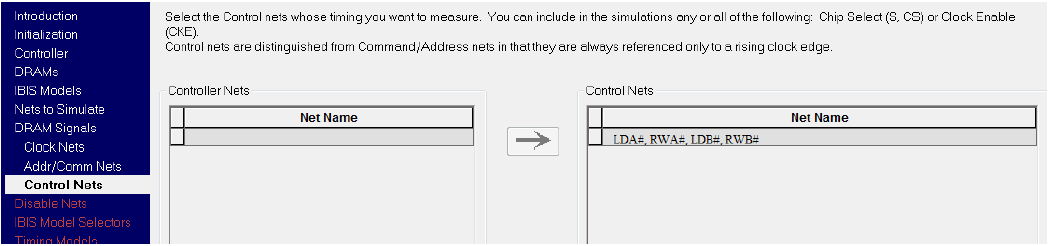

Sinyal

LDA #, LDB #, RWA # dan RWB # disinkronkan pada kecepatan data yang sama (laju data tunggal). Ini berarti bahwa sinyal-sinyal ini hanya disinkronkan pada salah satu dari dua sisi pulsa clock. Sinyal LDA # dan RWA # disinkronkan di tepi naik jam, dan sinyal LDB # dan RWB # berada di tepi jatuh.

Balok sebagian besar simetris - depan diferensial depan tidak jauh berbeda dari belakang. Ini berarti bahwa untuk memastikan integritas sinyal, nilai waktu untuk

LDB # dan RWB # harus hampir sama, jika tidak sama, saat pengambilan sampel pada tepi naik atau

turun jam. Sinyal kontrol LPDDR3 juga disinkronkan hanya pada sisi yang naik.

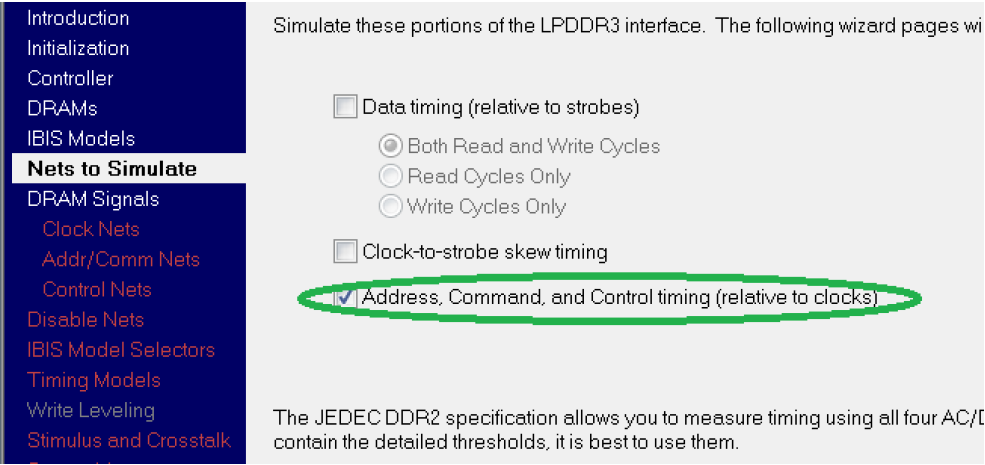

Langkah-langkah berikut khusus untuk bus alamat, perintah, dan simulasi kontrol bus menggunakan QDR-IV.

Pastikan bahwa di bagian

Jaring untuk Mensimulasikan kotak waktu

Alamat, Perintah dan Kontrol (relatif terhadap jam) dipilih (Gbr. 14).

Fig. 14. Centang kotak Alamat, Waktu perintah dan Kontrol

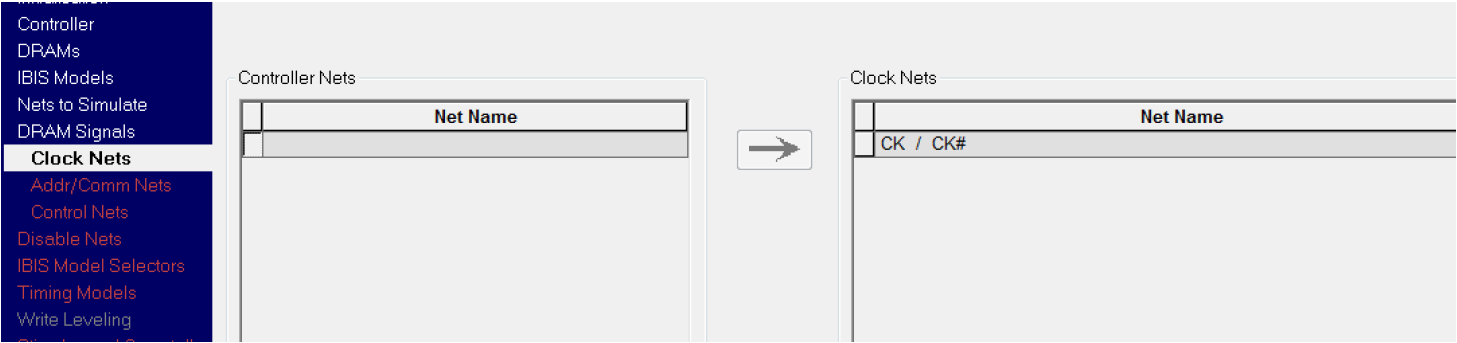

Fig. 14. Centang kotak Alamat, Waktu perintah dan KontrolPada bagian

Clock Nets , pastikan pasangan diferensial sinyal CK / CK # dipilih (Gbr. 15).

Fig. 15. Pilihan jam diferensial

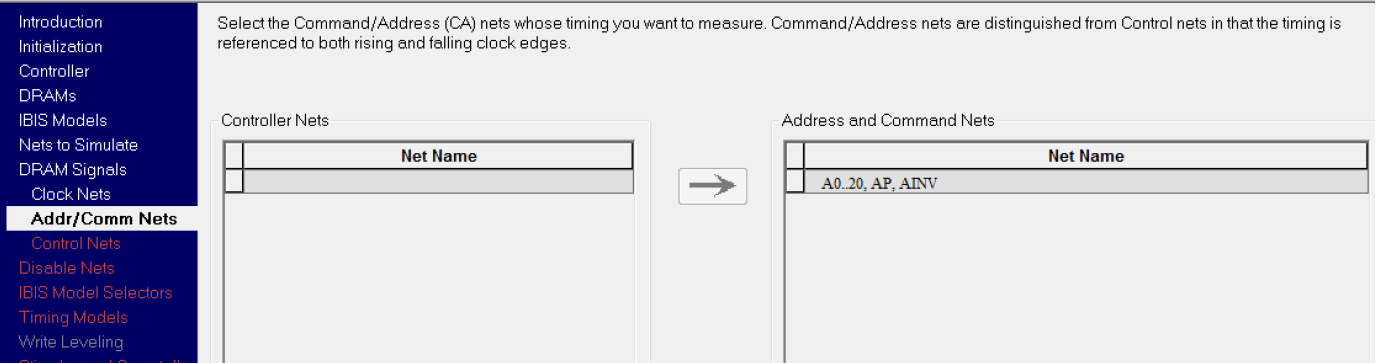

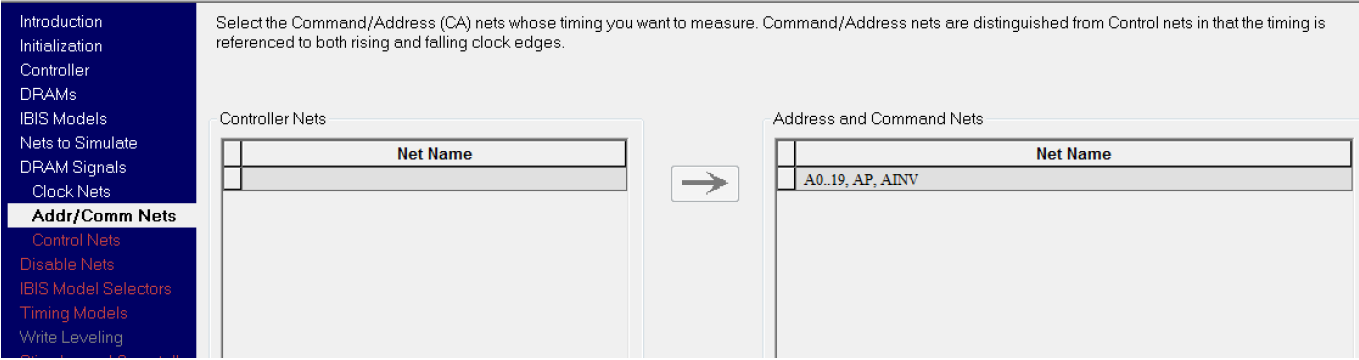

Fig. 15. Pilihan jam diferensialDi bagian

Addr / Comm Nets , pastikan bit

A [20: 0] dipilih untuk perangkat dengan x36 bit dan bit

A [19: 0] dipilih untuk perangkat dengan bit x18. Selain itu, atur

sinyal AP dan AINV (Gbr. 16 dan 17).

Fig. 16. Pengaturan untuk bus x36-bit

Fig. 16. Pengaturan untuk bus x36-bit Fig. 17. Pengaturan untuk bus x18-bit

Fig. 17. Pengaturan untuk bus x18-bitDi bagian

Jaring Kontrol , pilih sinyal LDA #, LDB #, RWA # dan RWB # (Gambar 18).

Fig. 18. Kontrol sinyal

Fig. 18. Kontrol sinyalSeperti memodelkan sinyal data, pastikan Anda menggunakan file yang benar dengan parameter timing. Sisa pemodelan dan evaluasi hasilnya mirip dengan LPDDR3.

“Menafsirkan Hasil Laporan HyperLynx DDRx”Kesimpulan

Dengan mengikuti instruksi sederhana dalam artikel ini, Anda bisa mendapat manfaat dari dan menggunakan paket pembantu DDRx Wizard untuk mensimulasikan dan menguji bus QDR-IV.

Semoga panduan ini bermanfaat bagi seseorang.

Hormat kami, Filipov Bogdan (

pbo ).

Juga mengambil kesempatan ini, saya ingin mengundang para pengembang REU ke seminar yang diselenggarakan oleh Nanosoft dan Mentor Graphics:

“Generasi Baru Solusi Desain Perangkat Elektronik dari Mentor Graphics”