Salam, Habr! Nama saya Daniil Smirnov, saya belajar di sekolah pascasarjana Universitas ITMO, di mana tim kami terlibat dalam elektronik yang dapat diprogram untuk proyek yang berkaitan dengan sensor serat optik di laboratorium pemodelan dan pemodelan. Sebagai basis perangkat keras untuk sensor, FPGA digunakan - Field Programmable Gate Array. Beberapa tahun yang lalu, kami mengetahui bahwa pabrikan FPGA sedang mengadakan kompetisi di kalangan mahasiswa pengembangan. Sejak itu, setiap tahun sebuah tim dibentuk dari kami untuk berpartisipasi dalam acara ini, dan sejak tahun ini ternyata menjadi istimewa, kami memutuskan untuk berbagi bagaimana semuanya dari dalam.

Entri

Saat itu Oktober 2017, saya melakukan pemeriksaan rutin mingguan: analisis konferensi yang sedang berlangsung tentang topik yang sedang dilaksanakan di departemen kami. Pada satu titik, saya menerima buletin dari Terasic:

kompetisi baru dimulai

pada pengembangan proyek menggunakan papan debug di FPGA , sekarang di seluruh dunia. Pengalaman kompetisi yang sama tahun lalu melintas di benak saya dan mengingatkan: menunda sampai dua minggu terakhir dalam sebulan, debugging panjang dan penyetelan algoritma dan mengeluarkan semua saluran ke monitor dan janji untuk tidak menundanya sampai hari terakhir.

Itu adalah pengalaman yang keren, di mana kami belajar banyak tentang platform seperti SoC FPGA - interkoneksi berbagai elemen logika dan prosesor Cortex-A9, serta interaksi mereka satu sama lain dan dengan periferal pada papan debug.

Persaingan baru - aturan baru, persyaratan baru, tingkat baru. Sekarang kompetisi diadakan dalam beberapa tahap: pertama, tahap regional diadakan, dan kemudian final di San Jose; papan dikirim ke semua peserta yang sama,

DE10-Nano , dan selain itu sekarang Anda dapat memilih tidak hanya tiga modul dasar, tetapi juga versi besar papan dari Perangkat Analog! Namun, tidak seperti kompetisi pada tahun-tahun sebelumnya, kali ini diperlukan untuk menandatangani jaminan proyek, dan dalam hal tidak terpenuhinya, peserta harus mengembalikan biaya. Ini cukup adil, dengan mempertimbangkan statistik tahun-tahun terakhir:

<...> 71 tim dari 20 negara Eropa mendaftarkan kontes <...> 25 juri dari Industry (ALTERA) dan Academia (CNFM) di Perancis meninjau 32 proyek [1].

Penasihat ilmiah, seperti siswa yang ingin terlibat dalam pekerjaan ini, sudah berada di bawah beban yang berat pada berbagai proyek, tetapi kegembiraan selama kompetisi dan motivasi untuk belajar banyak hal baru menjadi argumen yang berat untuk berpartisipasi dalam kompetisi lagi. Tetap dengan proyek yang dapat Anda terapkan.

Gagasan untuk sebuah proyek

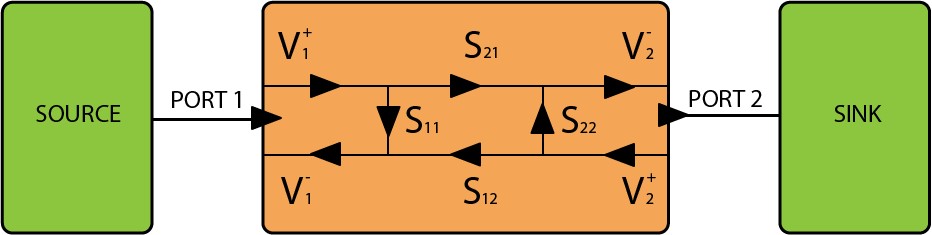

Agar proyek tidak berdiri sendiri, diputuskan untuk mengimplementasikan perangkat yang berguna untuk departemen, yang nantinya dapat dengan mudah dikembangkan dan ditingkatkan. Berdasarkan bidang kegiatan departemen, ada berbagai pilihan: reflektometer optik, osiloskop stroboskopik, dll. Dengan cepat melihat aplikasi yang ada dan papan tambahan yang tersedia, terungkap bahwa reflektometer sudah diumumkan, tetapi osiloskop stroboskopik tidak dapat dipasang pada elemen tersebut. Satu-satunya ide yang tetap hidup adalah penganalisa jaringan vektor. Suatu hari beberapa gulungan dibawa ke laboratorium, yang tidak ada dokumentasi. Tugasnya adalah untuk menentukan setidaknya perkiraan karakteristik kumparan ini. Diketahui bahwa rangkaian osilasi dirakit di dalamnya, jadi tugas utamanya adalah mencari tahu frekuensi resonansi. Dalam tugas-tugas seperti itu, penganalisa jaringan vektor (VAC atau VNA - Vector Network Analyzer) hanya dapat menemukan aplikasi. VNA memungkinkan Anda untuk mendefinisikan matriks dispersi, juga dikenal sebagai matriks S-parameter. Dalam metode ini, elemen yang diteliti dianggap sebagai kotak hitam, di mana insiden dan sinyal pantulan dari porta perangkat ini dianalisis. Jadi, untuk sistem dua-port, matriksnya adalah sebagai berikut:

Di mana V1 + V2 + adalah gelombang elektromagnetik yang tiba di pelabuhan;

V1- V2- - gelombang elektromagnetik meninggalkan port;

Sij adalah elemen dari matriks hamburan multipath. [2]

Skema pengukuran S-parameter dari sebuah multipole

Skema pengukuran S-parameter dari sebuah multipoleKami gagal memeriksa komponen dan sirkuit menggunakan sinar-X (setidaknya oleh sinar-X kereta bawah tanah), sehingga sirkuit berikut dipasang pada lutut: frekuensi diatur secara bergantian dengan langkah melalui sirkulator ke input koil menggunakan generator, port kedua dari sirkulator terhubung ke input koil, dan input ketiga ke osiloskop yang memiliki dalam perangkat lunaknya mode analisis frekuensi-amplitudo. Sirkuit seperti itu memungkinkan untuk mengukur parameter S11, yaitu. refleksi. Pada akhirnya, setelah banyak kesusahan dan kalibrasi, saya berhasil menghilangkan karakteristik ini - tetapi berapa biayanya? Departemen telah lama mengharapkan akuisisi penganalisa jaringan vektor untuk tugas-tugas seperti itu (mengukur AFC perangkat elektronik), tetapi pembelian ini entah bagaimana selalu tertunda.

Setelah ribut dengan kumparan, diputuskan untuk merakit penganalisis sirkuit Anda sendiri dengan visualisasi dan penyetelan yang nyaman. Tidak sulit untuk menemukan kegembiraan dan keinginan untuk belajar sesuatu yang baru untuk diri Anda sendiri dari mahasiswa dan mahasiswa pascasarjana yang bekerja di departemen, sehingga tim dengan cepat dikumpulkan dari seorang insinyur elektronik, seorang programmer-pengembang sistem pada sebuah chip, saya dan dua mentor.

Tidak lebih cepat dikatakan daripada dilakukan! Setelah banyak diskusi tentang pita frekuensi, pemrosesan algoritma dan parameter lain dari proyek, aplikasi berisi hal-hal berikut:

- Proyek yang diklaim adalah penganalisa rangkaian vektor berdasarkan SoC FPGA pada papan DE10-Nano;

- Papan tambahan yang diminta: papan dengan generator frekuensi yang dapat diprogram, mixer frekuensi tinggi dan papan dengan ADC;

- Rentang frekuensi pengoperasian: sesuai dengan parameter papan tambahan yang disajikan;

- Kemungkinan perluasan cepat jumlah port yang terhubung;

- Output dari komponen amplitudo dan fase ke layar;

- Fungsi input / output dasar lainnya untuk penganalisa jaringan vektor.

Untuk lolos ke tahap berikutnya, perlu bahwa halaman proyek memperoleh jumlah "suka" yang cukup dari pengguna yang mendaftar di situs. Pada awalnya, semuanya berjalan dengan baik, tetapi kemudian beberapa proyek yang meragukan mulai mendapatkan nilai suka dan pandangan yang tidak realistis dan berbeda dibandingkan dengan proyek lain. Ternyata situs kontes itu terlalu rentan terhadap kecurangan.

Setelah beberapa waktu, panitia menginformasikan bahwa majelis hakim masih akan memilih finalis, sehingga suka dari pengguna, pada kenyataannya, kehilangan berat badan mereka. Pada tanggal 31 Januari, tim kami muncul dalam daftar orang-orang yang pergi ke tahap berikutnya dan kami mulai memikirkan proyek kami lebih terinci untuk mengantisipasi debugging.

Realitas yang keras

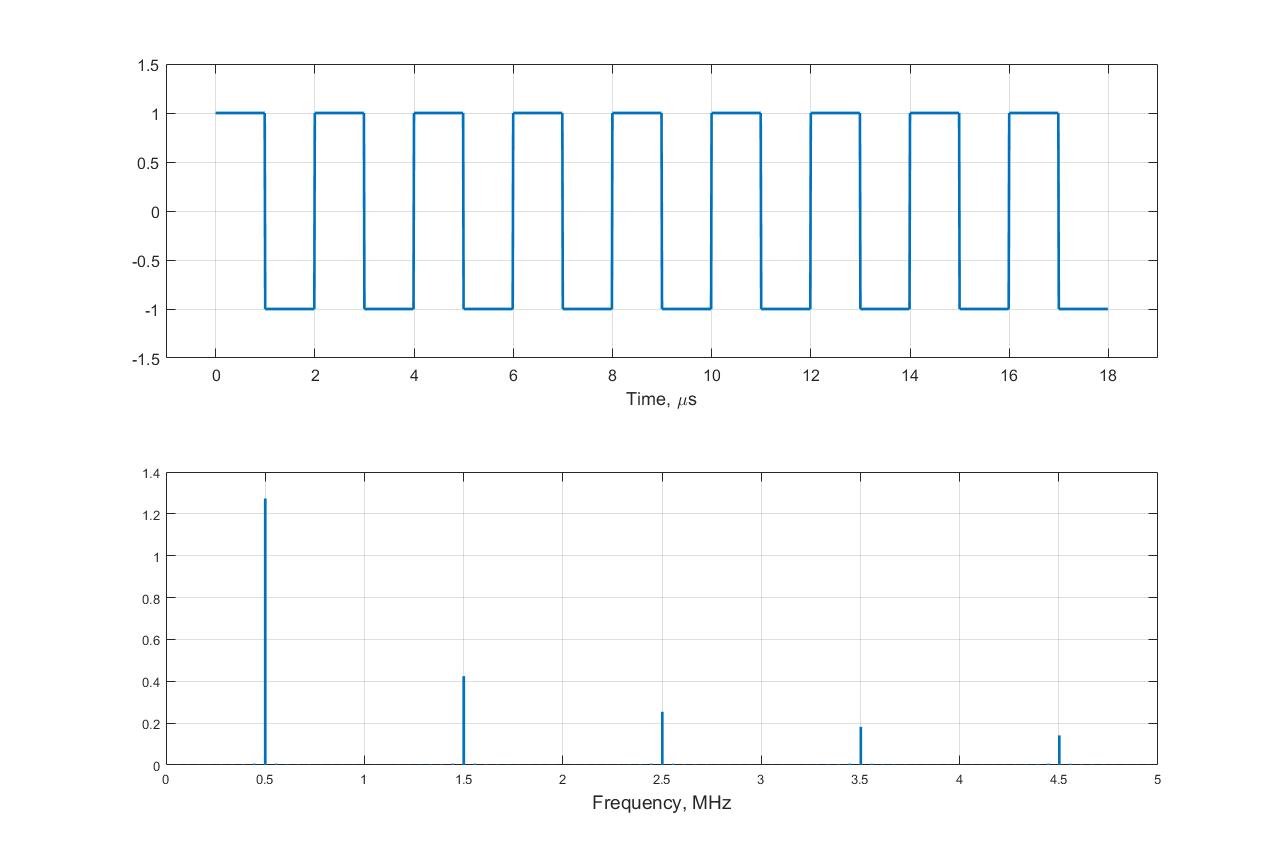

Yang pertama adalah papan DE10-Nano. Menyenangkan, tetapi sedikit aneh: mereka berharap papan akan datang bersama-sama. Beberapa hari kemudian, panggilan datang dari bea cukai: biaya datang, semuanya bersama-sama melebihi ambang harga, jadi Anda perlu membayar bea cukai dengan jumlah yang kira-kira sama dengan biaya biaya ini. Situasi seperti itu membuat kami kesal, tetapi tidak cocok dengan kami: kami menolak papan. Di hadapan mixer dan generator yang tidak kami miliki, perlu mencari solusi baru. Apa yang harus dilakukan Hal pertama yang terlintas dalam pikiran bukanlah solusi yang paling akurat, tetapi agak tidak biasa: menggunakan kaki GPIO biasa dan menghasilkan berliku-liku dari itu. Filter low-pass analog dipasang pada output foot ini dengan cut-off band yang sedikit lebih besar dari frekuensi berliku-liku maksimum. Sebagai permulaan, diusulkan untuk memulai analisis dari 1 MHz (misalnya): kemudian setelah filter kita akan mendapatkan lebih atau kurang sinus murni (harmonik tertinggi akan terputus oleh filter), dan seterusnya hingga frekuensinya turun ke frekuensi di mana sinyal setelah filter. akan ada dua harmonisa. Berliku-liku adalah jumlah dari harmonik aneh, dan kontribusi proporsional dari masing-masing harmonik diketahui sebelumnya [3].

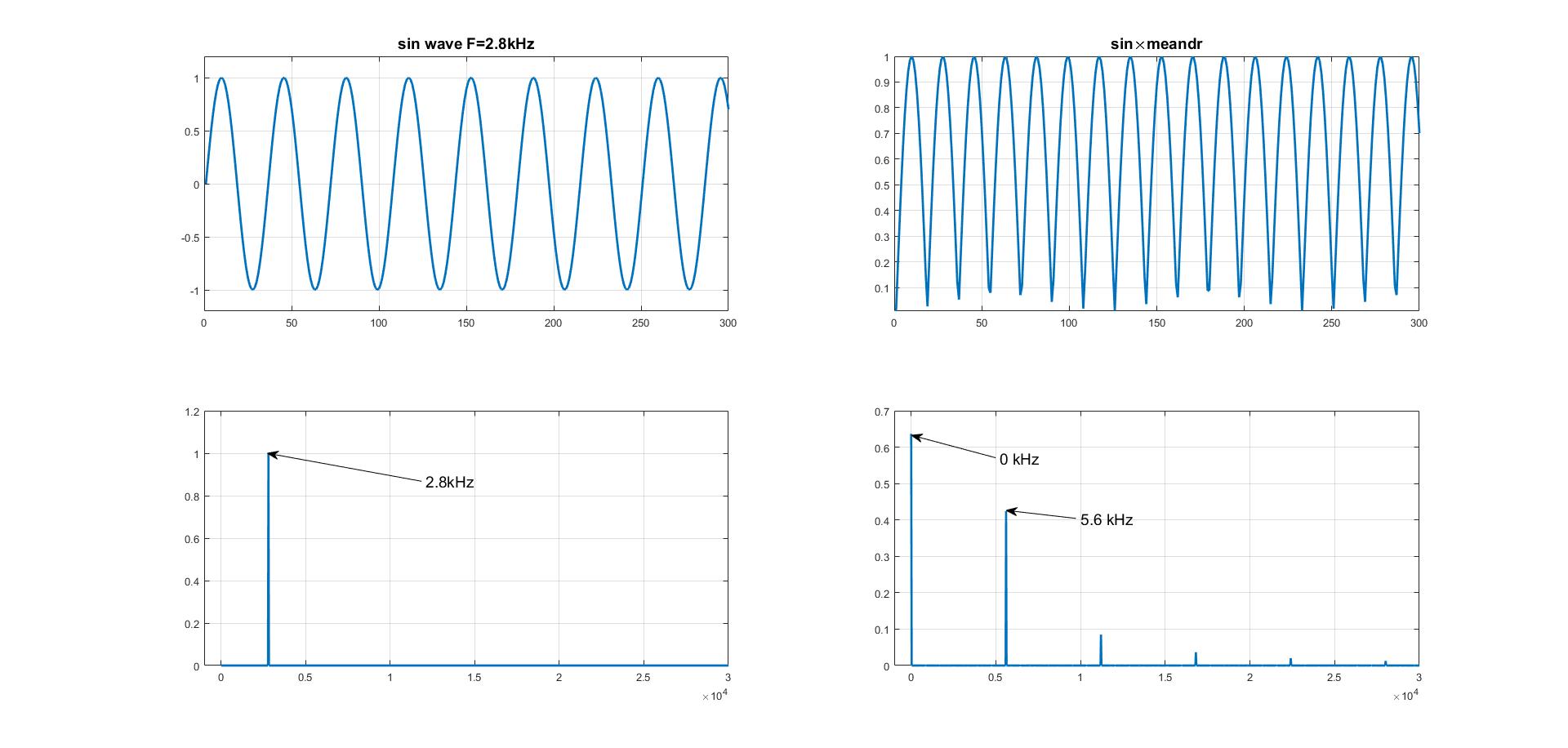

Contoh berliku-liku dalam domain waktu dan frekuensi: komponen sinyal harmonik pada 500 kHz, 1,5 MHz, dll terlihat pada spektrum.

Contoh berliku-liku dalam domain waktu dan frekuensi: komponen sinyal harmonik pada 500 kHz, 1,5 MHz, dll terlihat pada spektrum.Dengan filter dengan frekuensi cutoff 1 MHz, Anda bisa turun ke 33. (3) kHz. Setelah frekuensi ini, kita harus mendapatkan jumlah dua sinus di belakang filter. Rasio proporsional amplitudo mereka diketahui (fungsi-fungsi), respons perangkat yang diukur terhadap frekuensi 1 MHz (harmonik ganjil pertama), juga, jadi kita perlu menyusun persamaan dengan yang tidak diketahui dan menghitung karakteristik respons dengan frekuensi 33, (3) kHz! Pada awalnya, solusi ini tampak terlalu sederhana, jadi sebagai permulaan, ini diberitahukan kepada semua orang dengan harapan seseorang akan menemukan kesalahan. Tidak ada kesalahan yang ditemukan, tetapi sejumlah keterbatasan ditemukan saat diskusi berlangsung:

- Kaki GPIO bukan sumber terbaik dari berliku-liku, terutama dengan meningkatnya frekuensi;

- Menyolder filter kompak pada komponen yang tersedia akan menjadi tugas yang tidak sepele;

- Bahkan jika keterbatasan ini dapat diatasi, masalah sinkronisasi muncul untuk deteksi fase.

Misalkan kita telah menyelesaikan semua masalah di sisi analog; secara pemrograman, dua lainnya muncul:

- Dengan penurunan frekuensi, kesalahan dari setiap deteksi dan perhitungan sebelumnya akan berkontribusi pada pengukuran selanjutnya;

- Dengan berkurangnya frekuensi, waktu untuk menghitung karakteristik akan meningkat secara signifikan.

Dan akhirnya, yang terakhir tapi tidak kalah pentingnya. Rangkaian yang dijelaskan dapat digunakan jika elemen yang diukur dapat dijelaskan oleh fungsi transfer linier. Namun, jika kita mengukur kotak hitam dengan karakteristik non-linear - idenya memiliki lebih banyak masalah daripada yang baik. Tidak ada banyak waktu tersisa (hasil pertama harus ditunjukkan dua bulan setelah papan tiba), oleh karena itu, setelah beberapa pertimbangan, kami memutuskan untuk memeriksa ulang stok kami dengan papan debug yang ada - dan menemukan

DAC 14-bit pada 125 Msps ! Bukan solusi yang paling elegan, tetapi tidak ada pilihan, kami menggunakannya sebagai generator sinyal output.

Konsep pertama

DAC yang dipilih sebagai generator menerima data pada input bus paralel dan mengaitkannya dengan sinyal clock yang berasal dari FPGA. Sirkuit seperti itu sangat ideal untuk sinkronisasi di sirkuit kami. Namun, pertanyaan tetap dengan deteksi.

Ya, di papan yang sama ada ADC 14-bit pada 65 Msps. Tetapi hanya kemampuan generator yang berpotensi lebih tinggi, dan menurut teorema Kotelnikov, ADC ini tidak akan lagi berfungsi pada frekuensi maksimum.

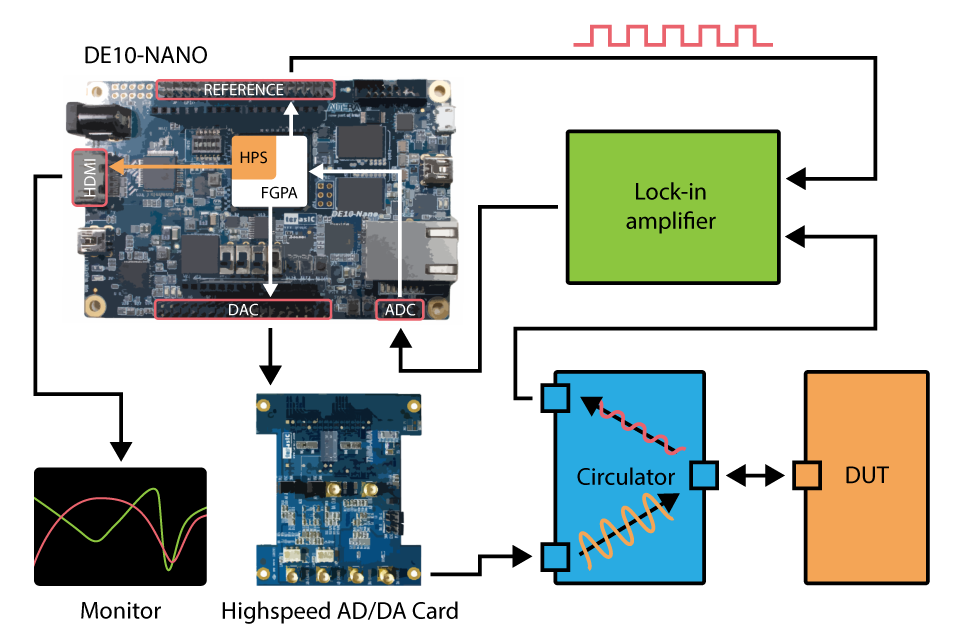

Solusinya ditemukan selama diskusi tentang masalah ini dengan insinyur elektronik yang berpengalaman. Ternyata untuk tugas kita, kita dapat menggunakan sirkuit penguat penguncian: output dari detektor semacam itu adalah dua nilai konstan, komponen fase dan quadrature, dari mana Anda bisa mendapatkan amplitudo dan fase sinyal, dan karena mereka konstan, mereka dapat dideteksi bahkan dengan ADC lambat yang diinstal pada DE10-Nano! Diputuskan untuk pertama memodelkan rangkaian di LTSpice, dan hanya kemudian memilih komponen dan merakit sirkuit, dengan mempertimbangkan bahwa input detektor adalah sinyal dari sirkulator, dan output terhubung ke ADC pada papan DE10-Nano.

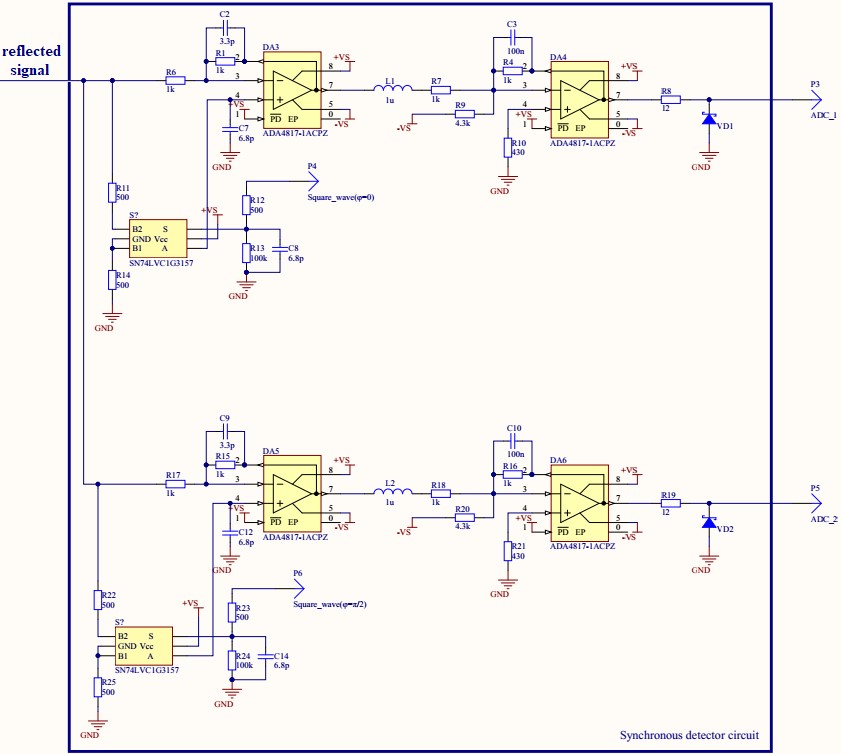

Tentang detektor dan sirkulator sinkronDetektor sinkron juga digunakan dalam pemrosesan sinyal digital untuk mendeteksi berbagai sinyal dengan latar belakang kebisingan. Instrumen Zurich memiliki deskripsi yang baik [4], dalam kasus kami deteksi adalah sebagai berikut: sinyal yang dipantulkan dari frekuensi yang diketahui dikalikan oleh berliku-liku menggunakan saklar frekuensi tinggi dan penguat operasional:

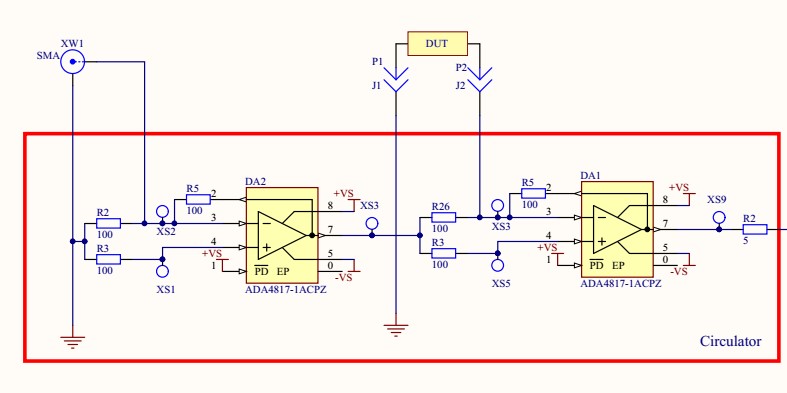

Sirkuit deteksi refleksi

Sirkuit deteksi refleksiBahkan, perkalian diimplementasikan sebagai beralih mode operasi dari penguat operasional, dan switching dikendalikan oleh dua meander yang berasal dari papan DE10-Nano: salah satunya adalah dalam fase dengan sinyal asli (diterima pada input perangkat), dan yang lainnya dengan fase penundaan 90 derajat.

Hasil penggandaan adalah transfer sinyal yang berguna ke komponen DC, dan semua frekuensi di atas tidak lagi menarik dan karenanya dapat disaring:

Spektrum sinyal sebelum dan sesudah penggandaan: pada output dari penguat operasional, Anda dapat memasang filter low-pass sederhana untuk mengisolasi hanya komponen DC

Spektrum sinyal sebelum dan sesudah penggandaan: pada output dari penguat operasional, Anda dapat memasang filter low-pass sederhana untuk mengisolasi hanya komponen DCSirkulator pada penguat operasional (op amp) adalah rangkaian sambungan rangkaian penguat operasional yang ditutup dalam sebuah cincin. Sirkulator OA digunakan untuk berbagai keperluan, khususnya untuk antena tala, amplifier, generator, gigabit Ethernet, dll. dalam rentang frekuensi hingga ratusan megahertz. Saat membuat VAC, sirkuit sirkulator yang dibuat berdasarkan dua amplifier operasional digunakan [5].

Diagram sirkuit untuk menghubungkan perangkat yang diukur

Diagram sirkuit untuk menghubungkan perangkat yang diukur  Konsep proyek yang diperbarui

Konsep proyek yang diperbaruiSinyal sinusoid dengan frekuensi 1 Hz hingga 1 MHz dengan langkah-langkah yang diatur ke beberapa Hz diumpankan ke port pertama dari sirkulator. Perangkat yang diteliti terhubung ke port kedua, tergantung pada respon frekuensi yang koefisien pantulan dari sinyal berubah. Sinyal yang dipantulkan diumpankan ke port 3, di mana rangkaian detektor sinkron dipasang untuk menentukan karakteristik frekuensi dan fase. Untuk operasi yang benar, port-port sirkulator disesuaikan dengan impedans 100 Ohm, yang dikaitkan dengan resistansi keluaran DAC dan pilihan perangkat yang diteliti.

Kurang dari satu bulan tersisa sebelum proyek selesai, dan pada akhir tenggat waktu diperlukan untuk menyiapkan bahan pelaporan: deskripsi rinci tentang proyek di halaman kontes, proyek yang diposting di GitHub di domain publik dan laporan video tentang pekerjaan yang dilakukan.

Karena kami sekarang mengerti data apa yang akan masuk ke input dan output, kami mulai bekerja pada proyek untuk SoC FPGA. Kami melihat proyek sedang dilaksanakan sebagai berikut: pengguna menetapkan rentang frekuensi di mana pengukuran direncanakan, FPGA mulai menghasilkan harmonik dalam interval yang ditentukan pada gilirannya menggunakan DAC, ADC menerima komponen quadrature dan fase pada input, mengubahnya menjadi amplitudo dan nilai fase pada frekuensi saat ini , nilai yang diperoleh ditampilkan secara real time pada monitor yang terhubung ke papan debug. Sudah ada prestasi dalam menampilkan informasi pada monitor, jadi bagian utamanya adalah rendering data yang benar secara real time dan output gambar ke HDMI. Kami tidak dikelompokkan. Kelompok pertama mengambil tugas pada program untuk prosesor, untuk memahami secara lebih rinci inisialisasi yang diperlukan, pertanyaan tentang visualisasi data. Kami juga meminta mereka untuk meningkatkan resolusi layar ke 1024x768 [6]. Kelompok kedua meninggalkan perincian tentang implementasi bagian pada FPGA, yang kemudian harus dipasok ke prosesor melalui bus antarmuka mild_h2f, serta uji operabilitas detektor sinkron prototipe prototipe pertama. Setelah menghilangkan kekurangan dan berhasil mengukur karakteristik beberapa elemen, tidak ada banyak waktu yang tersisa, jadi dua hari berikutnya dikhususkan untuk menghubungkan sistem bersama, menambahkan laporan dan mengedit video.

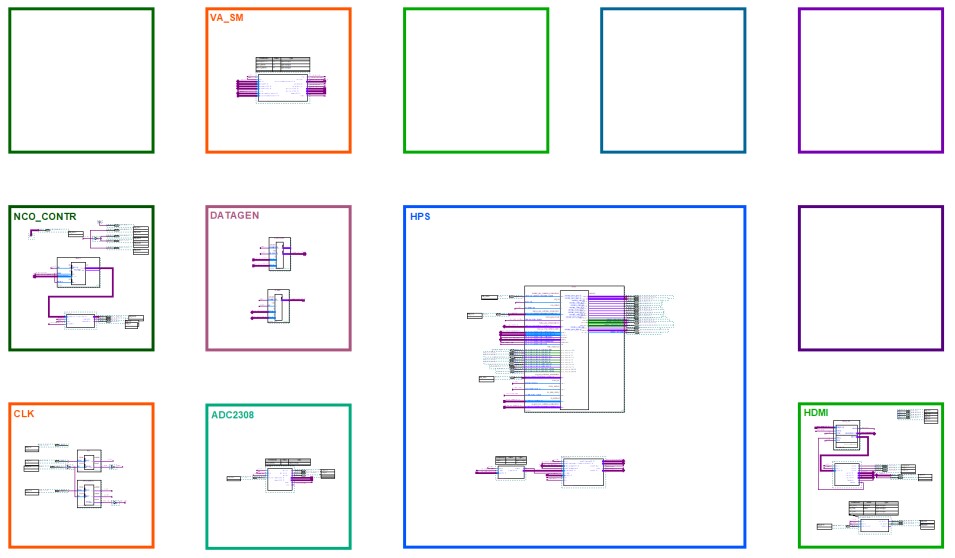

Penampilan file tingkat atas di Quartus II

Penampilan file tingkat atas di Quartus IIMenit terakhir

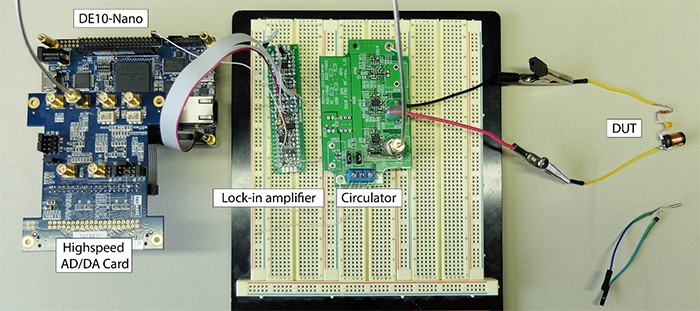

Setelah menghabiskan lebih dari satu hari libur di laboratorium, kami mengumpulkan seluruh sistem. Itu tidak bekerja untuk seluruh rentang frekuensi potensial, hanya mengukur parameter S11 dan mencerminkan fase diukur dan karakteristik amplitudo dari perangkat yang terhubung pada monitor. Perangkat yang dirakit secara eksternal masih tidak terlihat terlalu menarik - tiga papan terpisah yang dihubungkan oleh kabel inti tunggal, tetapi ini adalah prototipe yang

berfungsi , dan Anda dapat memakai marafet pada tahap berikutnya. Kami menulis teks, menggambarkan tahapan implementasi, merekam video, semua diunggah ke situs dan mulai menunggu.

Tentu saja, kami mengirim beberapa teman tautan ke materi ini untuk sedikit menambah tampilan. Namun, dalam satu hari, pandangan mulai tumbuh sendiri, seolah-olah seseorang telah menggabungkan ini menjadi promosi. Setelah sedikit analisis ternyata: proyek kami diperhatikan di hackaday.io [7] dan sebagian besar pandangan berasal dari sana. Sangat menarik melihat tanggapan pertama terhadap proyek kami. Terinspirasi, kami mulai menunggu hasilnya.

Namun demikian

Ini bukan tahun pertama partisipasi kami dalam kompetisi. Bagi kami, proyek ini adalah yang paling bijaksana di antara pekerjaan siswa yang diterapkan sebelumnya. Tapi itu tidak tumbuh bersama: kami tidak pergi ke tahap berikutnya. Mungkin ini karena kesalahpahaman antara kami dan para hakim. Mungkin proyek tidak sepenuhnya memasuki area tren saat ini untuk FPGA (kriptografi, komputasi paralel, jaringan saraf, dll). Tetapi bagi kami, ini adalah langkah besar dalam pengembangan SoC FPGA, cabang pengembangan baru dan, yang paling penting, pengalaman.

Ps

Selamat kepada perwakilan Rusia yang menempati posisi kedua di final kontes!

Saya berterima kasih kepada kolega-kolega proyek saya Danila Nikiforovsky dan

Yevgeny Vostrikov dan para pemimpin

Ivan Deineku ,

Philipp Shuklin dan Artem Aleinik atas partisipasi dan dukungan aktif mereka.

Referensi

[1] Kontes Innovate Europe 2015

www.innovateeurope.org/eu/2015winner.html[2] Panduan Insinyur Untuk Pengujian Otomatis Antarmuka Berkecepatan Tinggi, Jose Moreira, Hubert Wekmann, 2010, Lampiran F hal. 503

[3] Spektrum urutan berkala pulsa persegi panjang,

en.dsplib.org/content/fourier_series_pimp/fourier_series_pimp.html[4] Prinsip deteksi terkunci dan canggih, Instrumen Zurich

www.zhinst.com/applications/principles-of-lock-in-detection[5]

Sirkulator / insulator frekuensi rendah tanpa ferit dan magnet

www.cqham.ru/oth9.htm[6] Proyek VAC untuk papan

DE10 -Nano

github.com/tvShushtov/em078_vector_analyzer[7] Artikel tentang VAC di Hackaday

hackaday.com/2018/05/09/vector-network-analyzer-uses-soc-fpga